# EM6580

## **Ultra Low Power 8-pin Flash Microcontroller**

#### Features

True Low Power:

5.8  $\mu$ A active mode 3.3  $\mu$ A standby mode 0.32  $\mu$ A sleep mode

- □ Large Supply Voltage 2.0 V to 5.5 V

- Large Supply Voltage 2.0 V to 5.3

No external component needed

- Available in SO-8/14 packages and die

- 4-bit ADC or 12 levels Supply Voltage Level Detector (SVLD)

- □ Unique ID code of 52bits + 16bits CRC

- □ Max 4 (5\*) outputs with 2 high drive outputs of 10mA

- □ Max. 5 (6\*) inputs

- Sleep Counter Reset (automatic wake-up from sleep mode (EM patent))

- □ Flash memory 4096 × 16 bits

- □ RAM 80 × 4 bits

- □ Internal RC oscillator 32kHz 800kHz

- 2 clocks per instruction cycle

- 72 basic instructions

- External CPU clock source possible

- □ Watchdog timer (2 sec)

- Power-On-Reset with Power-Check on start-up

- □ 3 wire serial port , 8 bit, master and slave mode

- □ Universal 10-bit counter, PWM, event counter

- Prescaler down to 1 Hz (freq. = 32kHz)

- Frequency output 1Hz, 2048 Hz, CPUClk, PWM

6 internal interrupt sources (2×10-bit counter, 2×

- prescaler, SVLD, Serial Interface)

2 external interrupt sources (port A)

#### Description

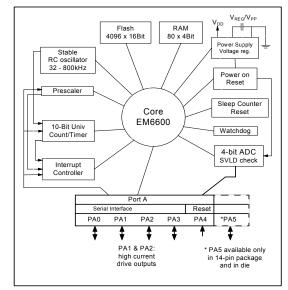

The EM6580 is a low power Flash 4-bit microcontroller coming in a small 8-pin SO package and working up to 0.4 MIPS. It comes with an integrated 4-bit ADC and 2 high current drive outputs of 10mA and it requires no external component. It has a sleep counter reset allowing automatic wake-up from sleep mode. It is designed for use in battery-operated and field-powered applications requiring an extended lifetime. A high integration level make it an ideal choice for cost sensitive applications.

The EM6580 contains the equivalent of 8kB of Flash memory and a RC oscillator with frequencies between 32 to 800kHz. It also has a power-on reset, watchdog timer, 10 bit up/down counter, PWM and several clock functions.

Development tools include windows-based simulator program debugger, assembler and real time emulator.

#### Figure 1. Architecture

#### Figure 2. Pin Configuration

| SO-8  | PA0 1 • 8 V <sub>DD</sub><br>PA1 2 PA2 3 • 7 V <sub>REG</sub> /V <sub>PP</sub><br>6 PA4<br>PA3 4 5 V <sub>SS</sub>                                                                                      |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SO-14 | NC     1     ■       PA0     2     13       VDD     13     VDD       PA1     3     12       PA2     4     EM6580       PA3     5     10       PA4     0     9       NC     6     9       NC     7     8 |

#### **Typical Applications**

- Household appliances

- Safety and security devices

- Automotive controls

- Sensor interfaces

- □ Watchdog

- □ Intelligent ADC

- Driver (LED, triac)

## EM6580 at a glance

#### Power Supply

- Low voltage low power architecture including internal voltage regulator

- 2.0V to 5.5V supply voltage

- 5.8 µA in active mode

- 3.3 µA in standby mode

- 0.32  $\mu A$  in sleep mode

#### RAM

- 80 x 4 bit, directly addressable

#### FLASH

- 4096 x 16 bit (8k Byte),

## CPU

- 4-bit RISC architecture

- 2 clock cycles per instruction (CPI=2)

- 72 basic instructions

## Main Operating Modes and Resets

- Active mode (CPU is running)

- Standby mode (CPU in halt, peripherals running)

- Sleep mode (no clock, data kept)

- Initial Power-On-Reset with Power-Check

- Watchdog reset (logic)

- Reset terminal (software option on PA[3/4])

- Sleep Counter reset from Sleep mode

- Wakeup on change from Sleep mode

## Prescaler

- Divider (4 stages) to best fit CPU clock (32kHz 1MHz to 32kHz system clock to keep peripherals timing close to specification

- 15 stage system clock divider from 32kHz down to 1Hz

- 2 Interrupt requests (3 different frequencies)

- Prescaler reset (4kHz to 1Hz)

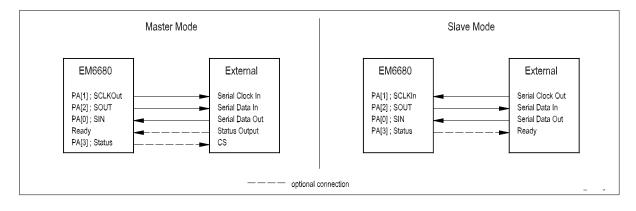

## Bit Serial Interface

- 3 wire (Clock, DataIn , DataOut) master/slave mode

- READY output during data transfer

- Maximum shift clock is equal to the main system clock

- Interrupt request to the CPU after 8 bit data transfer

- Supports different serial formats

- pins shared with general 4 bit PA[3:0] I/O port

## Oscillator

- RC Oscillator range: 32kHz up to 800kHz

- No external components are necessary

- Temperature compensated

- External clock source possible from PA[1]

## 4(5)-Bit I/O PA[3:0] & PA[4] / PA[5]\*

- Direct input read on the port terminals

- 2 debounced function available muxed on 4 inputs

- 2 Interrupt request on positive or negative edge

- Pull-up or pull-down or none selectable by register

- 2 Test variables (software) for conditional jumps

- PA[1] and PA[3/4] are inputs for the event counter

- PA[3/4] Reset input (register selectable)

- All outputs can be put tri-state (default)

Selectable pull-downs in input mode

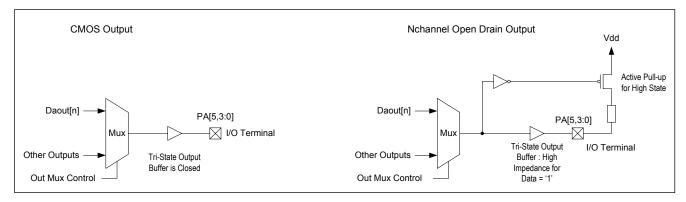

- CMOS or Nch. open drain outputs

- Weak pull-up selectable in Nch. open drain

- mode

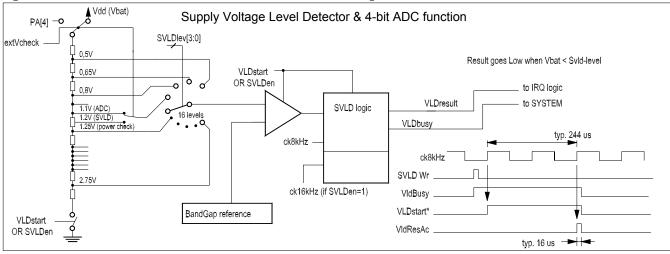

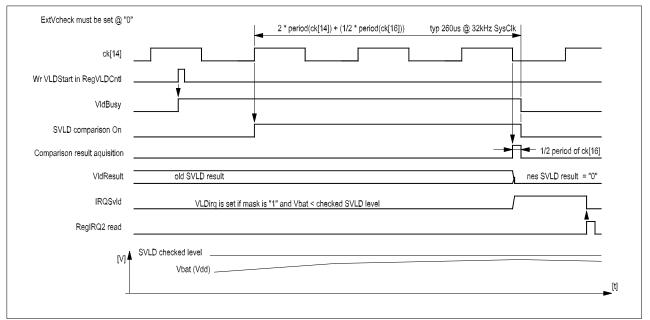

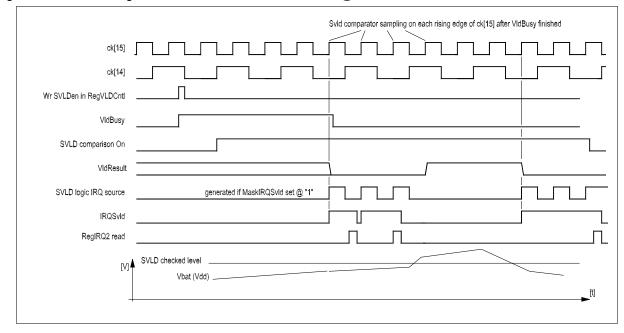

## a 4-bit ADC & Voltage Level Det. (SVLD)

- External voltage compare from PA[4] input possible (low resolution 4 bit AD converter)

- -7 different levels from 2 V to 3.0 V for SVLD

- Used for Power Check after POR (2.0V check)

- Busy flag during measure

- Interrupt generated if SVLD measurement low

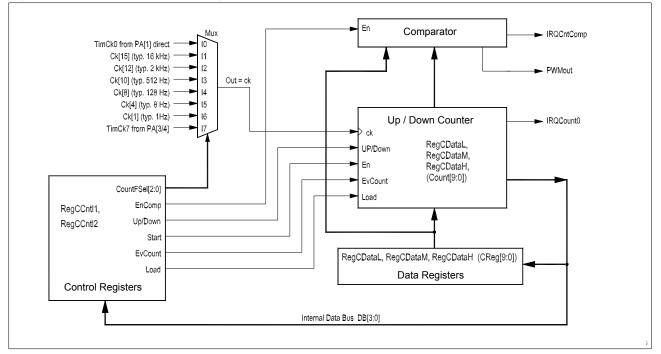

## 10-Bit Universal Counter

- 10, 8, 6 or 4 bit up/down counting

- Parallel load

- Event counting (PA[1] or PA[3/4])

- 8 different input clocks

- Full 10 bit or limited (8, 6, 4 bit) compare function

- 2 interrupt requests (on compare and on 0)

- Hi-frequency input on PA[1] and PA[3/4] or CPUCIk

- Pulse width modulation (**PWM**) output

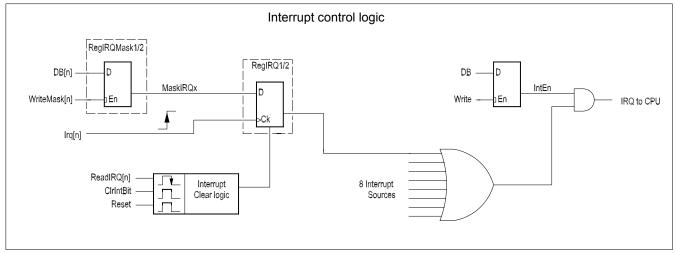

## Interrupt Controller

- 2 external and 6 internal interrupt request sources

- Each interrupt request can individually be masked

- Each interrupt flag can individually be reset

- Automatic reset of each interrupt request after read

- General interrupt request to CPU can be disabled

- Automatic enabling of general interrupt request flag when going into HALT mode

## Sleep Counter Reset (SCR)

- wake up the EM6580 from sleep mode

- 4 timings selectable by register

- Inhibit SCR by register

## Package form available

- SO-8/14

- Die form (9 pin possible due to additional I/O pin)

#### NB: All frequencies written in this document are related to a typical system clock of 32 kHz !

## **Table of Contents**

R

| FEAT          | URES                                                      | _ 1        |

|---------------|-----------------------------------------------------------|------------|

| DESC          | RIPTION                                                   | _ 1        |

| EM65          | 80 AT A GLANCE                                            | 2          |

| 1.            | PIN DESCRIPTION FOR EM6580                                |            |

| 2.            | OPERATING MODES                                           | _          |

| 2.1           | ACTIVE MODE                                               | 5          |

| 2.2           | STANDBY (HALT) MODE                                       | _ 5        |

| 2.3           | SLEEP MODE                                                | _ 5        |

| 3.            | POWER SUPPLY                                              | _ 7        |

| 4.            | RESET                                                     | _ 8        |

| 4.1           | POR WITH POWER-CHECK RESET                                | _ 9        |

| 4.2<br>4.3    | INPUT PORT A RESET<br>DIGITAL WATCHDOG TIMER RESET        | 10<br>10   |

| 4.3<br>4.4    | SLEEP COUNTER RESET                                       | 11         |

| 4.5           | Wake-Up on Change                                         | 11         |

| 4.6           | WAKE-UP ON CHANGE<br>THE CPU STATE AFTER RESET            | 11         |

| 5.            | OSCILLATOR AND PRESCALER                                  |            |

| 5.1           |                                                           | 12         |

| 5.2           | SPECIAL 4 STAGE FREQUENCY DIVIDER                         | 13         |

| 5.3           | PRESCALER                                                 | 13         |

| 6.            | INPUT AND OUTPUT PORT A                                   | 15         |

| 6.1           |                                                           | 15         |

|               |                                                           | 16         |

| 6.2.<br>6.2.2 |                                                           | 10         |

| 6.2.3         | 3 Pull-up/down                                            | 17         |

|               | Software test variables                                   | _18        |

| 6.2.5         | 5 Port A for 10-Bit Counter<br>6 Port A Wake-Up on change | _18<br>_18 |

| 6.2.7         | 7 Port A for Serial Interface                             | 18         |

| 6.2.8         | B Port A for External Reset                               | _18        |

| 6.2.9         | Port PA[4] as Comparator Input                            | _18        |

| 6.2.          | Reset and Sleep on Port A      Port A Blocked Inputs      | 18         |

| 6.3           | PORTA AS OUTPUT AND ITS MULTIPLEXING                      | 19         |

| 6.3.1         | 1 CMOS / Nch. Open Drain Output                           | _19        |

| 6.4           | Port A registers                                          | 20         |

| 7.            | SERIAL PORT                                               | 22         |

| 7.1           | GENERAL FUNCTIONAL DESCRIPTION                            | 23         |

| 7.2<br>7.2.   | DETAILED FUNCTIONAL DESCRIPTION<br>1 Output Modes         | 23<br>24   |

| 7.3           | 1 Output Modes<br>SERIAL INTERFACE REGISTERS              | 26         |

| 8.            | 10-BIT COUNTER                                            | 27         |

| 8.1           | Full and Limited Bit Counting                             | 27         |

| 8.2           | FREQUENCY SELECT AND UP/DOWN COUNTIN                      |            |

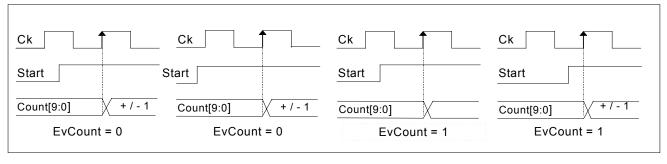

| 8.3           | EVENT COUNTING                                            | 29         |

| 8.4           | PULSE WIDTH MODULATION (PWM)                              | 29         |

| 8.4.1         | 1 How the PWM Generator works.                            | _30        |

|      | 2 PWM Characteristics                                              |                  |

|------|--------------------------------------------------------------------|------------------|

| 8.5  |                                                                    | _31              |

|      | 10-BIT COUNTER REGISTERS                                           |                  |

|      | SUPPLY VOLTAGE LEVEL DETECTOR                                      | :/<br>34         |

|      | ADCADC/SVLD COMPARATOR                                             | _ 34             |

|      | ADC/SVED COMPARATOR<br>RACTERISTICS                                | 37               |

|      |                                                                    |                  |

|      |                                                                    |                  |

|      | INTERRUPT CONTROLLER                                               |                  |

|      |                                                                    |                  |

|      |                                                                    |                  |

|      |                                                                    |                  |

| 14.1 | PORT A METAL OPTIONS<br>RC OSCILLATOR FREQUENCY OPTION             | _43<br>_/3       |

| 14.2 | DEBOUNCER FREQUENCY OPTION                                         | $-\frac{43}{11}$ |

| 14.0 | Power-Check Level Option                                           | - 44             |

| 14.5 | ADC/SVLD VOLTAGE LEVEL #15                                         | 44               |

| 14.6 | Counter Update option                                              | 44               |

| 14.7 | VOLTAGE REGULATOR LEVEL OPTION                                     |                  |

| 14.8 |                                                                    |                  |

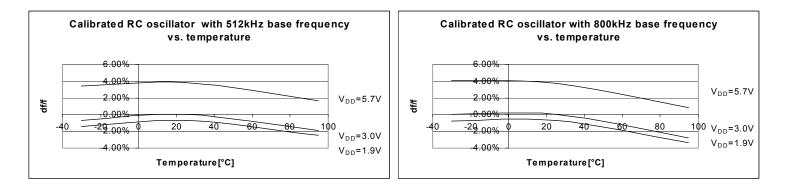

| 15.  | RC OSCILLATOR                                                      | 46               |

| 15.1 | FREQUENCY SELECTION                                                |                  |

| 15.2 | FREQUENCY SELECTION         OSCILLATOR TRIMMING                    | _47              |

| 16.  | UNIQUE ID CODE / SERIAL NUMBER _                                   | _48              |

| 17.  | TEMPERATURE AND VOLTAGE                                            |                  |

|      | AVIOUR                                                             | _49              |

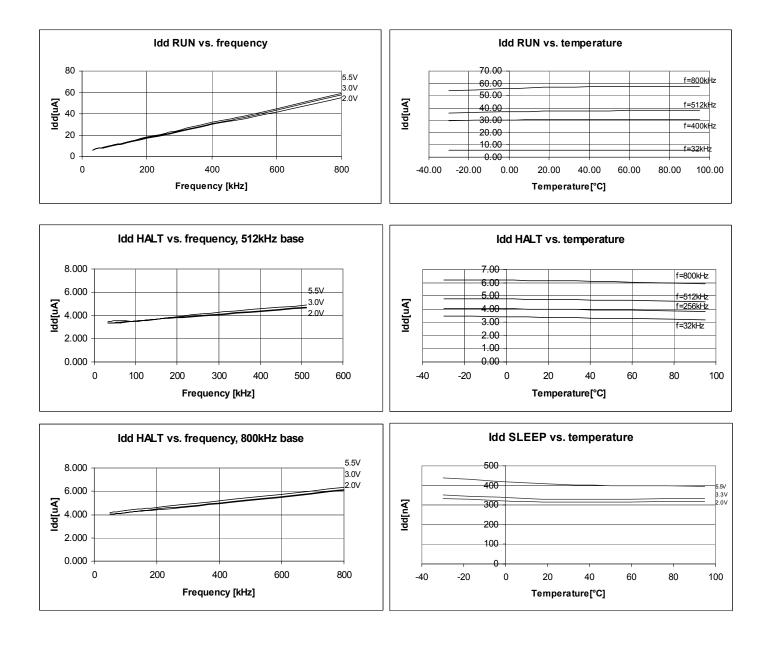

| 17.1 | IDD CURRENT (TYPICAL)                                              | _49              |

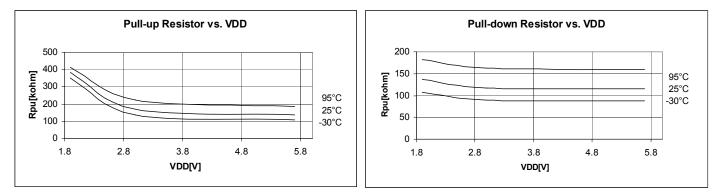

| 17.2 | PULL-UP AND PULL-DOWN RESISTORS                                    |                  |

| 47.0 | (TYPICAL)                                                          | _50              |

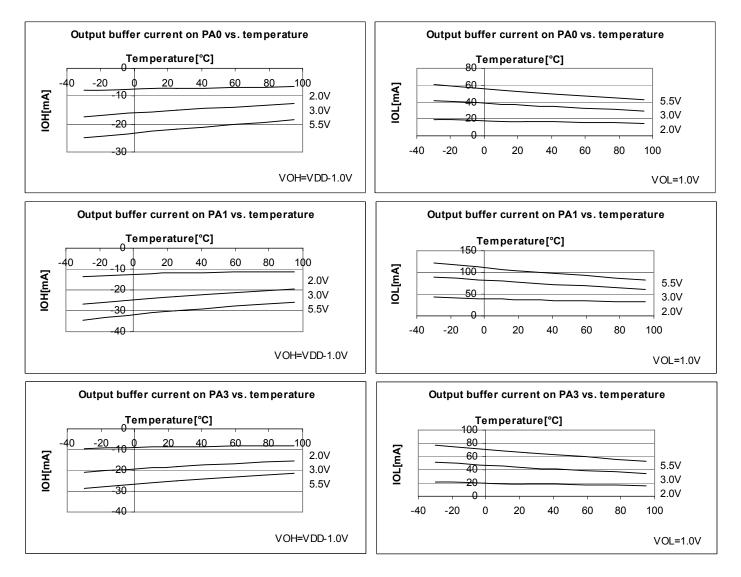

| 17.3 |                                                                    | _50              |

|      | OSCILLATOR FREQUENCY (TYPICAL)                                     |                  |

| 18.  | ELECTRICAL SPECIFICATION                                           | _52              |

| 18.1 | ABSOLUTE MAXIMUM RATINGS                                           | -52              |

| 18.2 | HANDLING PROCEDURES                                                | -52              |

| 10.3 | STANDARD OPERATING CONDITIONS<br>DC CHARACTERISTICS - POWER SUPPLY | -52              |

|      | SUPPLY VOLTAGE LEVEL DETECTOR                                      |                  |

| 18.6 | DC CHARACTERISTICS - I/O PINS                                      | -53              |

| 18.7 | RC OSCILLATOR FREQUENCY                                            | _00<br>54        |

| 18.8 | SLEEP COUNTER RESET - SCR                                          | 54               |

|      | PAD LOCATION DIAGRAM                                               |                  |

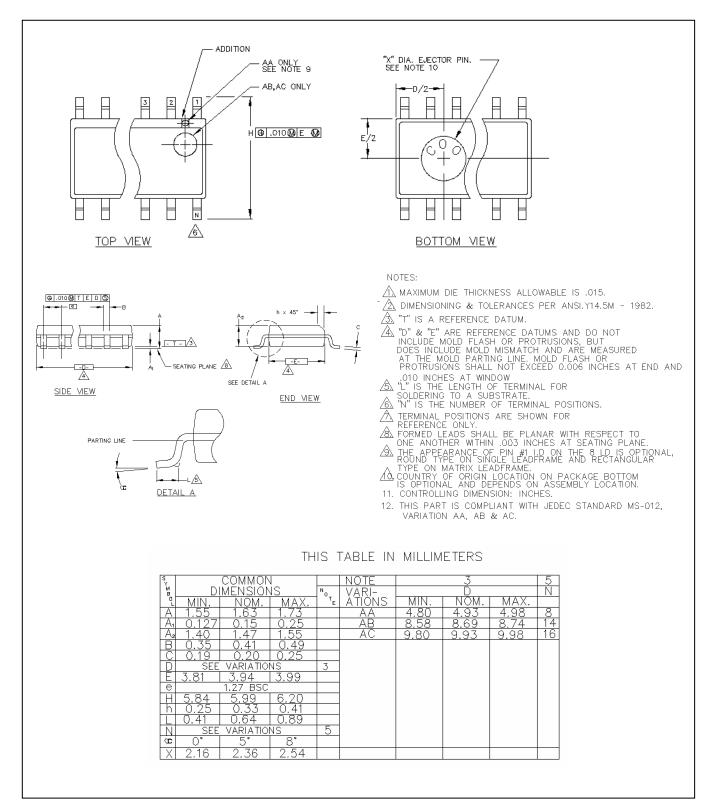

|      | PACKAGE DIMENSIONS                                                 |                  |

|      | SO-8/14                                                            |                  |

|      |                                                                    |                  |

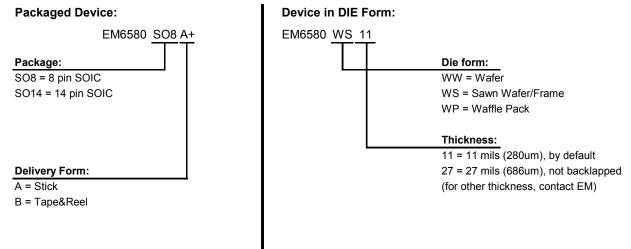

| 21   | ORDERING INFORMATION                                               |                  |

## 1. Pin Description for EM6580

| # On<br>Chip | SO-8 | Signal<br>Name   | Description                                                                  |  |

|--------------|------|------------------|------------------------------------------------------------------------------|--|

| 1            | 1    | PA0              | general I/O, serial In, Wake-Up on Change, IRQ source                        |  |

| 2            | 2    | PA1              | general I/O, serial CLK, timer source, external clock                        |  |

| 3            | 3    | PA2              | general I/O, serial Out, freq., CPU reset status output,                     |  |

| 4            | 4    | PA3              | general I/O, serial Rdy/Cs, Interrupt source, reset                          |  |

| 5            | 5    | V <sub>ss</sub>  | ground – negative supply pin                                                 |  |

| 6            | 6    | PA4              | general I, Reset, timer source, Interrupt source, Wake-Up, Compare I         |  |

| 7*           | NC   | PA5              | general I/O, Wake-Up on Change, IRQ source                                   |  |

| 8            | 7    | V <sub>REG</sub> | regulated voltage supported by 470nF tw. V <sub>ss</sub>                     |  |

|              |      |                  | High Voltage pin for Flash programming                                       |  |

| 9            | 8    | V <sub>DD</sub>  | positive supply pin – capacitance tw. $V_{DD}$ (C depends on $V_{DD}$ noise) |  |

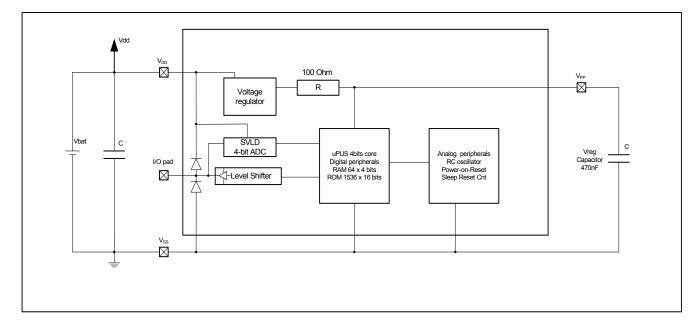

Figure 3. Typical configuration for  $V_{dd}$  > 2.0V

On I/O pins there are protective diodes towards  $V_{\text{DD}}$  and  $V_{\text{SS}}.$

## 2. Operating modes

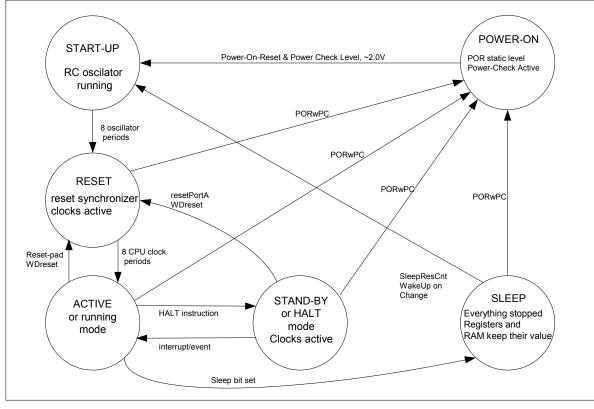

The EM6580 can operate in three different modes of which 2 are low-power dissipation modes (Stand-By and Sleep). The modes and transitions between them are shown in Figure 5.

- 1.) Active mode

- 2.) Stand-By mode

- 3.) Sleep mode

#### Figure 4. EM6580 operating mode transitions

## 2.1 ACTIVE Mode

The active mode is the actual CPU running mode. Instructions are read from the internal ROM and executed by the CPU. Leaving the active mode: via the halt instruction to go into standby mode, writing the **SLEEP** bit to go into Sleep mode or detecting the reset to go into reset mode.

## 2.2 STANDBY (Halt) Mode

Executing a HALT instruction puts the EM6580 into standby mode. The voltage regulator, oscillator, watchdog timer, interrupts, timers and counters are operating. However, the CPU stops since the clock related to instruction execution stops. Registers, RAM and I/O pins retain their states prior to STANDBY mode. STANDBY is cancelled by a RESET or an Interrupt request if enabled.

## 2.3 SLEEP Mode

Writing to the **Sleep** bit in the **<u>RegSysCntl1</u>** register puts the EM6580 in sleep mode. The oscillator stops and most functions of the EM6580 are inactive. To be able to write to the **Sleep** bit, the **SleepEn** bit in **<u>RegSysCntl2</u>** must first be set to "1". In SLEEP mode only the voltage regulator is active to maintain the RAM data integrity, the peripheral functions are stopped and the CPU is reset.all other functions are in reset state. SLEEP mode may be cancelled by Wake/Up on change, external reset or by Sleep Reset Counter if any of them is enabled.

Waking up from sleep mode may takes some time to guarantee stable oscillation. Coming back from sleep mode puts the EM6681 in reset state and as such reinitializes all registers to their reset value. During sleep mode and the following start up the EM6580 is in reset state. Waking up from sleep mode clears the **Sleep** flag but not the **SleepEn** bit. Inspecting the **SleepEn** allows to determine if the EM6580 was powered up (**SleepEn** = "0") or woken from sleep mode (SleepEn = "1").

# EM6580

| Peripheral /// EM6580 mode      | ACTIVE mode      | STAND-BY mode            | SLEEP mode            |

|---------------------------------|------------------|--------------------------|-----------------------|

| POR (static)                    | On               | On                       | On                    |

| Voltage regulator               | On               | On                       | On (Low-Power)        |

| RC-oscillator                   | On               | On                       | Off                   |

| Clocks (Prescaler & RC divider) | On               | On                       | Off                   |

| CPU                             | Running          | In HALT – Stopped        | Stopped               |

| Peripheral register             | "On"             | "On" retain value        | retain value          |

| RAM                             | "On"             | retain value             | retain value          |

| Timer/Counter                   | "On"             | "On" if activated before | stopped               |

| Supply Voltage Level Det.=SVLD  | can be activated | can not be activated     | Off                   |

| PortA / Reset pad debounced     | Yes              | Yes                      | No                    |

| Interrupts / events             | Yes - possible   | Yes - possible           | No – not possible     |

| Watch-Dog timer                 | On / Off (soft   | On / Off (soft           | No                    |

| -                               | selectable)      | selectable)              |                       |

| Wake Up on Change PortA         | No               | No                       | On/Off (soft select.) |

| Sleep Reset Counter             | Off              | Off On/Off (soft sele    |                       |

Table 2.3.1 Shows the Status of different EM6580 blocks in these three main operating modes.

## 3. Power Supply

The EM6580 is supplied by a single external power supply between  $V_{DD}$  ( $V_{BAT}$ ) and  $V_{ss}$  (ground). A built-in voltage regulator generates  $V_{REG}$  providing regulated voltage for the oscillator and the internal logic. The output drivers are supplied directly from the external supply  $V_{DD}$ . Internal power configuration is shown in Figure 3.

The internal voltage regulator is chosen for high voltage systems. It saves power by reducing the internal core logic's power supply to an optimum value. However, due to the inherent voltage drop over the regulator the minimal  $V_{\text{DD}}$  value is restricted to 2.0V.

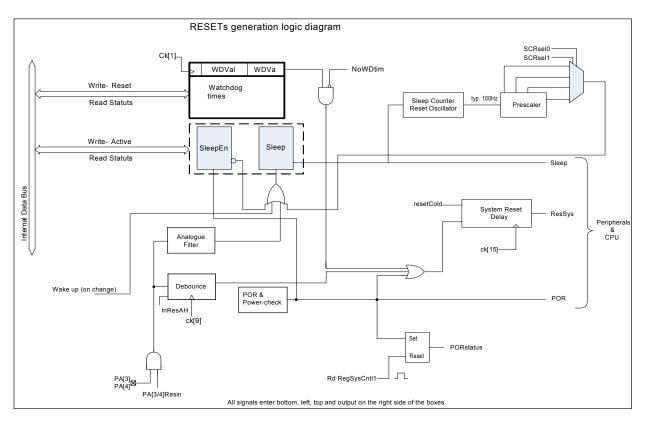

## 4. Reset

Figure 6. illustrates the reset structure of the EM6580. One can see that there are five possible reset sources :

- (1) Internal initial Power On Reset (POR) circuitry with Power-Check. → POR, ResetCold, System Reset, Reset CPU

- (2) External reset from PA[3/4] if software enabled

- (3) Internal reset from the Digital Watchdog.

- (4) Internal reset from the Sleep Counter Reset.

- (5) Wake-Up on change from PA[0/5] or PA[3/4] if software enabled.

- → System Reset, Reset CPU

Table 4.1 Reset sources that can be used in different Operating modes

| Reset Sources                     | ACTIVE mode       | STAND-BY mode     | SLEEP mode          |

|-----------------------------------|-------------------|-------------------|---------------------|

| POR (static) with Power Check     | Yes               | Yes               | Yes                 |

| Software enabled reset on PA[3/4] | XS dig. debounced | XS dig. debounced | XS analog debounced |

| Digital Watch-Dog Timer           | XS                | XS                | No                  |

| Sleep Counter Reset               | No                | No                | XS                  |

| Wake Up on Change from Sleep      | No                | No                | XS                  |

| Going in Sleep mode               | Yes               | No                | No                  |

**XS** = software enable

#### Figure 4. EM6580 Reset Structure

All reset sources activate the System Reset (ResSys). The 'System Reset Delay' ensures that the system reset remains active long enough for all system functions to be reset (active for 12 system clock cycles. CPU is reset by the same reset

As well as activating the system reset, the POR also resets all bits in registers marked '**p**' and the sleep enable (**SleepEn**) latch. System reset <u>does not</u> reset these register bits, nor the sleep enable latch.

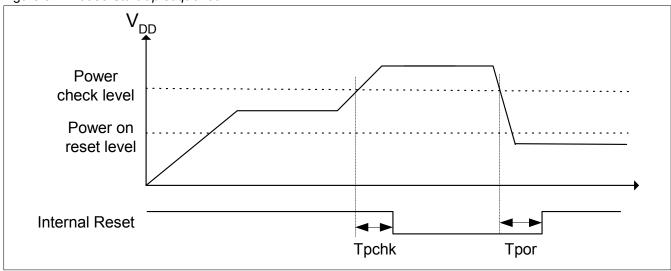

## 4.1 POR with Power-Check Reset

An on chip detection circuit generates a power-on reset (POR). The POR is generated whenever VDD is below the detection level defined in section 17.4. A second detection circuit circuitry, power check level, ensures a proper start-up of the microcontroller if VDD is higher than this level. This level is higher than POR and defined in section 17.4.

If VDD drops below the static POR level, the chip goes in reset state.

To distinguish between POR reset and all other types of reset, the **PORstatus** bit in <u>RegSysCntl2</u> is set on at every POR and is cleared by writing the <u>RegSysCntl1</u> register.

Figure 5. EM6580 Start-up sequence

## 4.2 Input Port A Reset

By writing the **PA[3/4]ResIn** in <u>**RegFreqRst**</u> registers the PA[3] or PA[4] input becomes dedicated for external reset. This bit is cleared by POR only. Which input is selected is set by **IrqPA[3I/4h]** bit from <u>**RegPACntl2**</u> register which is described in Chapter 6.

Bit **InResAH** in the <u>**RegFreqRst**</u> register selects the PA[3/4] reset function in Active and standby (Halt) mode. If set to '0' the PA[3/4] reset is inhibited. If Set to '1' than PA[3/4] input goes through a debouncer and needs to respect timing associated with the debounce clock selection made by **DebSel** bit in <u>**RegPresc** register.</u>

This **InResetAH** bit has no action in sleep mode, where a Hi pulse on PA[3/4] always immediately triggers a system reset (only small analogue debouncer is attached to filter 1 or 2  $\mu$ s spikes).

Overview of control bits and possible reset from PA[3] or PA[4] is specified in table 4.2.1 below.

| PA[3/4]ResIn | InResAH | ACTIVE or STAND-BY mode             | SLEEP mode                     |

|--------------|---------|-------------------------------------|--------------------------------|

| 0            | Х       | NO reset from PA[3] or PA[4]        | NO reset from PA[3] or PA[4]   |

| 1            | 0       | NO reset from PA[3] or PA[4]        | Reset with small analog filter |

| 1            | 1       | Debounce reset with debck of        | Reset with small analog filter |

|              |         | * Ck[14]/ Ck[11]/ Ck[8] needing     | _                              |

|              |         | 0.25 ms / 2 ms / 16ms Hi pulse typ. |                                |

Table 4.2.1 Possible Reset from PA[3] or PA[4]

\* Ck[14]/ Ck[11]/ Ck[8] are explained in chapter 5.2 Prescaler.

## 4.3 Digital Watchdog Timer Reset

The Digital Watchdog is a simple, non-programmable, 2-bit timer, that counts on each rising edge of Ck[1]. It will generate a system reset if it is not periodically cleared. The watchdog timer function can be inhibited by activating an inhibit digital watchdog bit (**NoWDtim**) located in <u>**RegVLDCntl**</u>. At power up, and after any system reset, the watchdog timer is activated.

If for any reason the CPU stops or stays in a loop where watchdog timer is not periodically cleared, it activates the system reset signal. This function can be used to detect program overrun, endless loops, etc. For normal operation, the watchdog timer must be reset periodically by software at least every 2.5 seconds (system clock = 32 KHz), or a system reset signal is generated.

The watchdog timer is reset by writing a '1' to the **WDReset** bit in the timer. This resets the timer to zero and timer operation restarts immediately. When a '0' is written to **WDReset** there is no effect. The watchdog timer also operates in standby mode and thus, to avoid a system reset, standby should not be active for more than 2.5 seconds.

From a System Reset state, the watchdog timer will become active after 3.5 seconds. However, if the watchdog timer is influenced from other sources (i.e. prescaler reset), then it could become active after just 2.5 seconds. It is therefore recommended to use the Prescaler **IRQHz1** interrupt to periodically reset the watchdog every second.

It is possible to read the current status of the watchdog timer in **RegSysCntl2**. After watchdog reset, the counting sequence is (on each rising edge of CK[1]) : '00', '01', '10', '11', {WDVal1 WDVal0}). When reaching the '11' state, the watchdog reset will be active within  $\frac{1}{2}$  second. The watchdog reset activates the system reset which in turn resets the watchdog. If the watchdog is inhibited it's timer is reset and therefore always reads '0'.

| Bit | Name      | Reset | R/W | Description                                       |  |  |

|-----|-----------|-------|-----|---------------------------------------------------|--|--|

| З   | WDReset   | 0     | W   | Reset the Watchdog (The Read value is always '0') |  |  |

|     |           |       |     | 1 → Resets the Logic Watchdog                     |  |  |

|     |           |       |     | $0 \rightarrow$ no action                         |  |  |

| 2   | SleepEn   | 0     | R/W | See Operating modes (sleep)                       |  |  |

| 1   | WDVal1    | 0     | R   | Watchdog timer data 1/4 ck[1]                     |  |  |

| 0   | WDVal0    | 0     | R   | Watchdog timer data 1/2 ck[1]                     |  |  |

| З   | PORstatus | 1 P*  | R   | Power-On-Reset status                             |  |  |

|     |           |       |     |                                                   |  |  |

Table 4.3.1 Watchdog timer register **<u>RegSysCntl2</u>**

**1 P\*** POR sets the PORstatus bit which is cleared by writing register **RegSysCntl1**

## 4.4 Sleep Counter Reset

To profit the most from Low Power Sleep Mode and still supervise the circuit surrounding, one can enable the Sleep Counter Reset which only runs in Sleep mode and periodically wakes up the EM6580. Four (4) different Wake-Up periods are possible as seen in table below.

Control bits **SleepCntDis** which is set to default '0'by POR enables the Sleep Counter when the circuit goes into Sleep mode. The **SCRsel1**, **SCRsel0** bits that are used to determine Wake-Up period are in the **RegSleepCR** register. To disable the Sleep Counter in Sleep mode **SleepCntDis** must be set to '1'.

Bit Name R/W Description Reset NoPullPA[4] Remove pull-up/down from PA[4] input 3 0 por R/W 2 SleepCntDis 0 por R/W Disable Sleep Reset Counter when Hi SCRsel1 Selection bit 1 for Sleep RCWake-Up period 1 0 por R/W 0 SCRsel0 0 por R/W Selection bit 0 for Sleep RCWake-Up period

Table 4.4.2 Register RegSleepCR

Table 4.4.3 Wake-Up period from Sleep selection

| SCRsel1 | SCRsel0 | Sleep Reset Counter periods                |  |  |

|---------|---------|--------------------------------------------|--|--|

| 0       | 0       | 1.5 internal low speed RC clock periods    |  |  |

| 0       | 1       | 15.5 internal low speed RC clock periods   |  |  |

| 1       | 0       | 127.5 internal low speed RC clock periods  |  |  |

| 1       | 1       | 1023.5 internal low speed RC clock periods |  |  |

Refer to table 18.8 or the actual SCR timeout period timings

Sleep Counter Reset (SCR) uses the same prescaler (see chapter 5.3) as the System Clock in Active and StandBy mode. Prescaler reset is made automatically just before going into Sleep mode if SCR is enable. This causes the Sleep Reset Counter to have its specified period.

## 4.5 Wake-Up on Change

By writing the **WUchEn[0/5]** and/or **WUchEn[3/4]** bit in <u>RegPaCntl2</u> registers the PA[0] or PA[5] and/or PA[3] or PA[4] can generate a reset from sleep on any polarity change on a selected pin. The port selection is defined with bits **IrqPA[0I/5h]** and **IrqPA[3I/4h]**. See chapter 6 and Figure 10 for more details.

## 4.6 The CPU State after Reset

Reset initializes the CPU as shown in Table 4.6.1 below.

| Name                 | Bits | Symbol | Initial Value                 |

|----------------------|------|--------|-------------------------------|

| Program counter 0    | 12   | PC0    | \$000 (as a result of Jump 0) |

| Program counter 1    | 12   | PC1    | Undefined                     |

| Program counter 2    | 12   | PC2    | Undefined                     |

| Stack pointer        | 2    | SP     | SP[0] selected                |

| Index register       | 7    | IX     | Undefined                     |

| Carry flag           | 1    | CY     | Undefined                     |

| Zero flag            | 1    | Z      | Undefined                     |

| Halt                 | 1    | HALT   | 0                             |

| Instruction register | 16   | IR     | Jump 0                        |

|                      |      |        |                               |

| Periphery registers  | 4    | Reg    | See peripheral memory map     |

Table 4.6.1 Initial CPU value after Reset

## 5. Oscillator and Prescaler

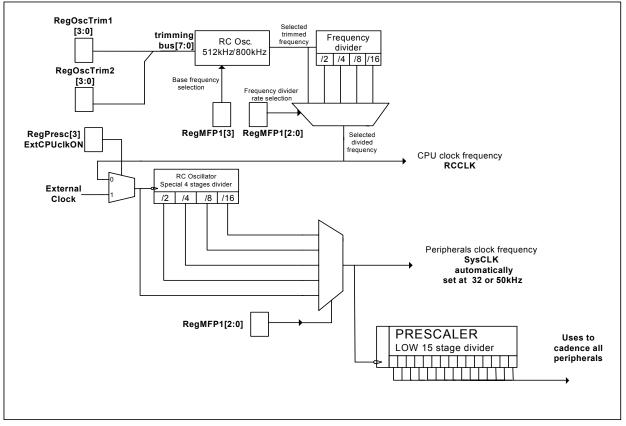

## 5.1 RC Oscillator or external Clock

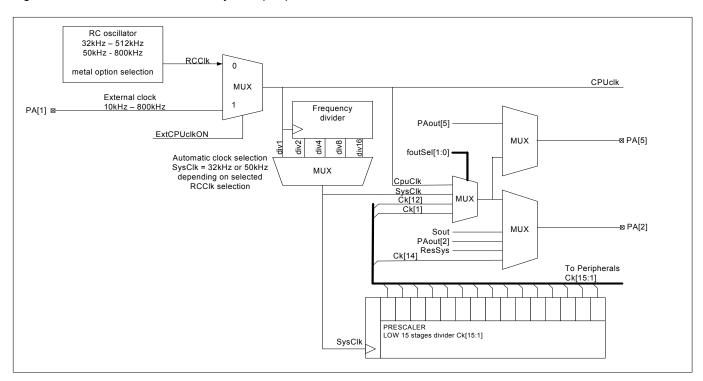

EM6580 can use the internal RC oscillator or external clock source for its operation.

The built-in RC oscillator without external components generates the system operating clock for the CPU and peripheral blocks. The RC oscillator is supplied by the regulated voltage.

The RC oscillator frequency can be chosen from 5 possibilities with a register with 2 basic frequencies.

These are typically 32kHz, 64kHz, 128kHz, 256kHz or 500kHz for 32kHz basic frequency or 50kHz, 100kHz, 200kHz, 400kHz or 800kHz for 50kHz basic frequency. Depending on the selected RC frequency. A special 4 stage freq. divider is available to be able to deliver to Prescaler which generates all System clock except CPU clock, a frequency close to 32 or 50 kHz to keep the peripheral timing as close as possible to specifications.

After POR the circuit always starts with the internal RC oscillator, but it can be switched to the external clock by setting the **ExtCPUcIkON** bit in the register <u>RegPresc.</u> The external clock is input at PA[1] and must be in range from min. 10Khz to max. 1MHz. With this external frequency input all timing for peripherals change and the special 4 stage freq. divider **must** be adapted to best suit the applied external frequency to keep 32/50kHz System clock as close as possible. The system clock **must** be less than 64kHz. The external clock source must be a square wave with full amplitude from V<sub>ss</sub> to V<sub>dd</sub>. See Table 5.2.2 for advised special divisions depending on the external clock frequency.

Switching from internal RC oscillator to External clock or back from External clock to RC oscillator is made without generating a glitch on the internal clock. Once the circuit is running on the external Clock one can disable the RC oscillator by setting the **RCoscOff** bit in **RegSCntl2** to '1'.

In sleep mode the oscillator is stopped. It can be stopped also by setting the **RCoscOff** bit. This bit can be set only if **ExtCPUCIkOn** was set before, indicating that the CPUck was switched from the internal RC oscillator to the external clock which MUST be present. If the External Clock stops without going into Sleep mode first the EM6580 can block and only POR can reset it.

Figure 8. below shows the connection of the RC oscillator and external clock and generation of CPUclk and System clock = SysClk which is divided by the special 4 stage Freq. Divider if needed as described in 5.2 and prescaler described in 5.3.

Figure 6. Clock source for CPU or system peripherals

## 5.2 Special 4 stage Frequency Divider

If an internal RC clock or external frequency higher than 32 kHz or *50* kHz is selected, then the special 4 stage Frequency Divider must be used to select a frequency close to 32 kHz or *50* kHz for the SysClk - system clock used by the Prescaler. This is done by register option.(Refer to RegMFP1 table chapter 14.8)

If the external clock will be used, the same register option used to select the division for SysClk. Table below shows recommended divisions in this 4 stage divider.

| Ext. clock        | RC frequency |          | RC frequency or External freq. | Typical Obtained SysClk     |  |  |

|-------------------|--------------|----------|--------------------------------|-----------------------------|--|--|

|                   | (1)base      | (2) base | MUST be divided by             | Min typ. If RC - Max. [kHz] |  |  |

| 10 kHz – 50 kHz   | 32           | 50       | No Division to SysClk          | 10 - 32 - 50                |  |  |

| 55 kHz – 100 kHz  | 64           | 100      | Divided by 2                   | 27.5 - 32 - 50              |  |  |

| 110 kHz – 200 kHz | 128          | 200      | Divided by 4                   | 27.5 - 32 - 50              |  |  |

| 220 kHz – 400 kHz | 256          | 400      | Divided by 8                   | 27.5 - 32 - 50              |  |  |

| 400 kHz – 1 MHz   | 500          | 800      | Divided by 16                  | 10 - 32 - 62.5              |  |  |

Table 5.2.1 PA[1] I/O status depending on its RegPACntl3 and RegPa0OE registers

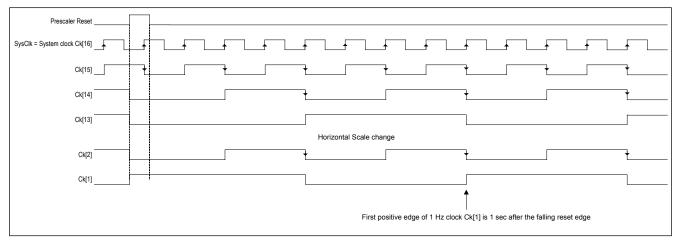

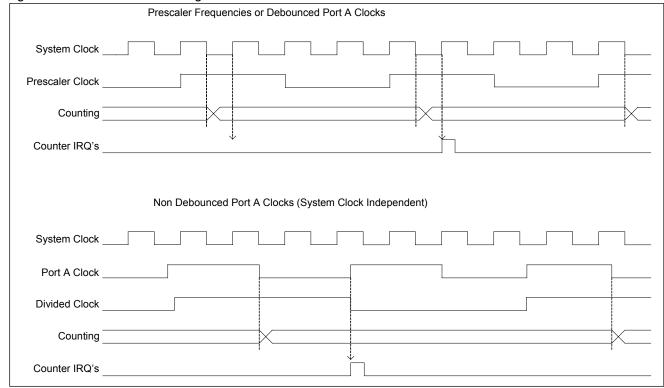

## 5.3 Prescaler

The prescaler consists of a fifteen element divider chain which delivers clock signals for the peripheral circuits such as timer/counter, debouncer and edge detectors, as well as generating prescaler interrupts. The input to the prescaler is the system clock signal closest to 32 kHz or *50* kHz which comes from the RC oscillator or external clock as divided by the preceding divider. Power on initializes the prescaler to Hex(0001).

| Function           | Name   | 32 KHz   | 50 KHz   |

|--------------------|--------|----------|----------|

| i anotion          | Namo   | SysClk   | SysClk   |

| System clock       | Ck[16] | 32768 Hz | 50000 Hz |

| System clock / 2   | Ck[15] | 16384 Hz | 25000 Hz |

| System clock / 4   | Ck[14] | 8192 Hz  | 12500 Hz |

| System clock / 8   | Ck[13] | 4096 Hz  | 6250 Hz  |

| System clock/ 16   | Ck[12] | 2048 Hz  | 3125 Hz  |

| System clock / 32  | Ck[11] | 1024 Hz  | 1562 Hz  |

| System clock / 64  | Ck[10] | 512 Hz   | 781 Hz   |

| System clock / 128 | ck [9] | 256 Hz   | 390 Hz   |

| Function             | Name  | 32 KHz<br>SysClk | 50 KHz<br>SysClk |

|----------------------|-------|------------------|------------------|

| System clock / 256   | Ck[8] | 128 Hz           | 195 Hz           |

| System clock / 512   | Ck[7] | 64 Hz            | 97 Hz            |

| System clock / 1024  | Ck[6] | 32 Hz            | 49 Hz            |

| System clock / 2048  | Ck[5] | 16 Hz            | 24 Hz            |

| System clock / 4096  | Ck[4] | 8 Hz             | 12 Hz            |

| System clock / 8192  | Ck[3] | 4 Hz             | 6 Hz             |

| System clock / 16384 | Ck[2] | 2 Hz             | 3 Hz             |

| System clock / 32768 | Ck[1] | 1 Hz             | 1.5 Hz           |

| Bit | Name        | Reset | R/W | Description                                                                     |

|-----|-------------|-------|-----|---------------------------------------------------------------------------------|

| 3   | ExtCPUclkON | р     | R/W | Ext. Clock selection instead of RC oscillator for CPUClk.                       |

| 2   | ResPresc    | 0     | R/W | Write Reset prescaler                                                           |

|     |             |       |     | $1 \rightarrow$ Reset the divider chain from Ck[14] to Ck[2], sets Ck[1].       |

|     |             |       |     | $0 \rightarrow$ No action. The Read value is always '0'                         |

| 1   | PrIntSel    | 0     | R/W | Prescaler Interrupt select. $0 \rightarrow$ Interrupt from Ck[4] (typ. 8/12 Hz) |

|     |             |       |     | $1 \rightarrow$ Interrupt from Ck[7] (typ. 64/97 Hz)                            |

| 0   | DebSel      | 0     | R/W | Debouncer clock select. $0 \rightarrow$ Debouncer with Ck[8]                    |

|     |             |       |     | 1 → Debouncer with Ck[11] or Ck[14]                                             |

#### Table 5.3.2 Control of Prescaler Register **<u>RegPresc</u>**

p\* reset to '0' by POR only.

With DebSel = 1 one may choose either the Ck[11] or Ck[14] debouncer frequency by selecting the corresponding register mask option. (Refer to RegMFP1 table chapter 14.8) Relative to 32kHz the corresponding max. debouncer times are then 2 ms or 0.25 ms. For the register option selection refer to chapter 14.8

Switching the **PrIntSel** may generate an interrupt request. Avoid it with **MaskIRQ64/8** = 0 selection during the switching operation.

The prescaler contains 2 interrupt sources:

- IRQ64/8 ; this is Ck[7] or Ck[4] positive edge interrupt, the selection is depending on bit PrIntSel.

- IRQHz1 ; this is Ck[1] positive edge interrupt

There is no interrupt generation on reset.

The first IRQHz1 Interrupt occurs typically. 1 sec (if SysClk = 32kHz) after reset. (0.65 sec if SysClk is 50kHz).

#### NOTE: If not written explicitly all timing in peripherals is calculated for 32 kHz System Clock !

## 6. Input and Output port A

#### The EM6580 has:

- port PA[3:0], one 4-bit input/output port

- port PA[4], one 1 bit input port.

- port PA[5], one 1 bit input/output. (not available in 8-pin package).

Pull-up and Pull-down resistors can be added to all these ports with register options.

## 6.1 Input / Output Port Overview

Table 6.1.1 Input and Output port overview

|                              | PA[0]  | PA[1]    | PA[2]  | PA[3]    | PA[4]  | PA[5]* |

|------------------------------|--------|----------|--------|----------|--------|--------|

| Pin in 8pin package          | 1      | 2        | 3      | 4        | 6      | NC*    |

| General I/O                  | I/O    | I/O      | I/O    | I/O      | I      | I/O    |

| Serial interface             | Sin I  | Sclk I/O | Sout O | Rdy/CS O |        |        |

| WakeUp on change             | yes* I |          |        | yes* I   | yes* I | yes* I |

| Softw. pullUp/Down           | Yes    | yes      | yes    | yes      | yes    | yes    |

| Register option pullUp/Down  |        |          |        |          | yes    |        |

| Timer input                  |        | yes I    |        | yes* I   | yes* I |        |

| Irq debounce & edge select.  | yes* I |          |        | yes* I   | yes* I | yes* I |

| CPU soft. variable input     | yes* I |          |        | yes* I   | yes* I | yes* I |

| Analogue compare Input       |        |          |        |          | yes I  |        |

| External reset input         |        |          |        | yes* I   | yes* I |        |

| External CPU clock input     |        | yes I    |        |          |        |        |

| PWM timer out                | yes O  | yes O    |        |          |        |        |

| freq. Output (RC, 2kHz, 1Hz) |        |          | yes* O |          |        | yes* O |

| CPU reset condition          |        |          | yes O  |          |        |        |

$NC^{\star}$  – Pad PA[5] is Not Connected in 8-pin package, available on 14-pin and in die form Register option – Refer to RegMFP1 table chapter 14.8

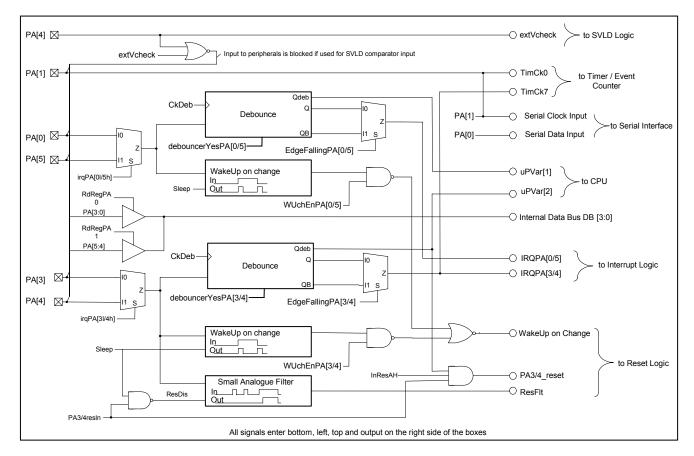

As shown in Figure 10, Logic for the Wake up on change reset which is possible only from Sleep mode, Debouce and IRQ function on Rising or falling edge are implemented only twice but can be attached and configured by registers to 4 different pads when used as inputs.

Ports PA[0] and PA[5] can be configured to have wakeup on Change, and debounced or non-debounced IRQ on the falling or rising edge. The same function is available on ports PA[3] or PA[4] which in addition can be dedicated to input reset. Registers **RegPACntl1** and **RegPACntl2** make this selection.

#### Table 6.1.2 Register RegPACntl1

| Bit | Name                                              | POR | R/W | Description                                        |  |  |

|-----|---------------------------------------------------|-----|-----|----------------------------------------------------|--|--|

| 3   | DebounceNoPA[3/4]                                 | 0   | R/W | Debounce on when Low for PA[3/4] input             |  |  |

| 2   | DebounceNoPA[0/5]                                 | 0   | R/W | Debounce on when Low for PA[0/5] input             |  |  |

| 1   | EdgeFallingPA[3/4]                                | 0   | R/W | IRQ edge selector for interrupt from PA[3/4] input |  |  |

| 0   | EdgeFallingPA[0/5]                                | 0   | R/W | IRQ edge selector for interrupt from PA[0/5] input |  |  |

|     | * Default is debouncer On and Rising edge for IRQ |     |     |                                                    |  |  |

#### Table 6.1.3 Register RegPACntl2

| Bit | Name          | POR | R/W | Description                                 |

|-----|---------------|-----|-----|---------------------------------------------|

| 3   | WUchEnPA[3/4] | 0   | R/W | Wake/Up on change EN on PA[3] or PA[4]      |

| 2   | WUchEnPA[0/5] | 0   | R/W | Wake/Up on change EN on PA[0] or PA[5]      |

| 1   | lrqPA[3l/4h]  | 0   | R/W | PA[3] if Low / PA[4] if High for IRQ source |

| 0   | IrqPA[0l/5h]  | 0   | R/W | PA[0] if Low / PA[5] if High for IRQ source |

\* Default: No wake Up on change and IRQ source, or reset and timer input, would be PA[3], PA[0]

## 6.2 PortA as Input and its Multiplexing

The EM6580 can have up to 6 1-bit general purpose CMOS input ports. The port A input can be read at any time, pull-up or pull-down resistors can be chosen by software.

Figure 10 explains how the inputs are treated with control signals and how they are distributed to different peripherals and the CPU. This is also listed in Table 6.1.1 Input and Output ports overview.

Figure 8. EM6580 Multiplexed Inputs diagram

Some Input functions are explained below.

## 6.2.1 Debouncer

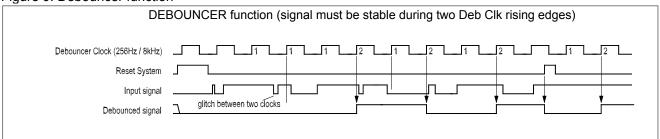

The debouncer is clocked with one of the possible debouncer clocks (Ck[14] / Ck[11] / Ck[8] and can be used only in Active or StandBy mode (as only in these two modes clocks are running). The input signal has to be stable on two successive debouncer rising clock edges and must not change between them.

#### Figure 9. Debouncer function

## 6.2.2 IRQ on Port A

For interrupt request generation (IRQ) one can choose direct or debounced input and rising or falling edge IRQ triggering. With the debouncer selected **debounceYesPA[x/y]**, the input must be stable for two rising edges of the selected debouncer clock CkDeb. This means a worst case of 16ms(default) or 2ms (0.25ms by metal mask) with a system clock of 32kHz.

Either a rising or falling edge on the port A inputs - with or without debouncing - can generate an interrupt request. This selection is done by **edgeFallingPA[x/y]**.

PortA can generate max 2 different interrupt requests. Each has its own interrupt mask bit in the **<u>RegIRQMask1</u>** register. When an IRQ occurs, inspection of the <u>**RegIRQ1**</u> and <u>**RegIRQ2**</u> registers allow the interrupt to be identified and treated.

At power on or after any reset the **<u>RegIRQMask1</u>** is set to 0, thus disabling any input interrupt. A new interrupt is only stored with the next active edge after the corresponding interrupt mask is cleared. See also the interrupt chapter 9.

It is recommended to mask the port A IRQ's while one changes the selected IRQ edge. Otherwise one may generate an unwanted IRQ (Software IRQ). I.e. if a bit PA[0/5] is '0' then changing from positive to negative edge selection on PA[0/5] will immediately trigger an **IRQPA[0/5]** if the IRQ was not masked.

#### 6.2.3 Pull-up/down

On Each terminal of PA[3:0] and PA[5] an internal pull-up (metal mask MAPU[n]) or pull-down (metal mask MAPD[n]) resistor can be connected per metal mask option. By default the two resistors are in place. In this case one can choose by software to have either a pull-up, a pull-down or no resistor.

See below for better understanding. If the port is used also as output please check Chapter 6.3.1 CMOS / Nch. Open Drain Output.

PA[4] can have only strong Pull-up or Pull-down resistor which can be removed by the software register **NoPullUpDown[4]**.

PA[4] can have only strong Pull-up or Pull-down resistor. This resistor can be disconnected by software in register RegSleepCR bit **NoPullPA[4]**.

For Metal mask selection and available resistor values refer to chapter 13.

| Pull-down ON: | MAPD[n] must be in place ,     | with n=0, 1, 2, 3, 5 |

|---------------|--------------------------------|----------------------|

|               | AND bit NoPdPA[n] must be '0'. |                      |

- Pull-down OFF: MAPD[n] is not in place, OR if MAPD[n] is in place NoPdPA[n] = '1' cuts off the pull-down. OR selecting NchOpDrPA[n] = '1' cuts off the pull-down.

- Pull-up ON : MAPU[n] must be in place, AND bit NchOpDrPA[n] must be '1', AND (bit OEnPA[n] = '0' (input mode) OR if OEnPA[n] = '1' while PAData[n] = 1.)

- Pull-up OFF :

MAPU[n] is not in place,

OR if MAPU[n] is in place NchOpDrPA[n] = '0' cuts off the pull-up,

OR if MAPU[n] is in place and if NchOpDrPA[n] = '1' then PAData[n] = 0 cuts off the pull-up.

Never pull-up and pull-down can be active at the same time.

Any port A input must never be left open (high impedance state, not connected, etc.) unless the internal pull resistor is in place (mask option) and switched on (register selection). Any open input may draw a significant cross current which adds to the total chip consumption.

<u>Note:</u> The mask settings\_MAPU[n]) and MAPD[n] do not define the default pull direction, but the pull possibilities. It is the software which defines the pull direction (pull-up or pull-down). The only exception is on PA[4] where the user must decide if he wants pull-up or pull-down. For this input the selected pull direction will always be valid unless the software disconnects the pull resistor.

## 6.2.4 Software test variables

As shown in Figure 10 PA[0/5] or PA[3/4] are also used as input conditions for conditional software branches. These CPU inputs are always debounced and non-inverted.

- debounced PA[0/5] is connected to CPU TestVar1

- debounced PA[3/4] is connected to CPU TestVar2

CPU TestVar3 is connected to Ground and can not be used in Software.

## 6.2.5 Port A for 10-Bit Counter

The PA[1] and PA[3/4] inputs can be used as the clock input terminal for the 10 bit counter

- PA[1] is at counter clock selection 0. The input is direct ( no debouncer is possible

- PA[3/4] is at counter clock selection 7. As for the IRQ generation, debounced or input directly and non-inverted or inverted input is possible. This is defined with the register **RegPaCntl1**. Debouncing the input is always recommended.

## 6.2.6 Port A Wake-Up on change

In sleep mode if configured port PA[0/5] or PA[3/4] inputs are continuously monitored to wake up on change, which will immediately wake up the EM6580.

## 6.2.7 Port A for Serial Interface

When the serial interface is used in slave mode, PA[0] is used for serial data input and PA[1] for the serial clock.

## 6.2.8 Port A for External Reset

In Active and Stand-by (Halt) mode a positive debounced pulse on PA[3/4] can be the source of a reset when **PA[3/4]ResIn** and **InResAH** are set at '1'. When **IrqPA[3I/4h]** is '0' than PA[3] is selected for Reset source and when **IrqPA[3I/4h]** is '1' than PA[4] is selected for Reset source.

## 6.2.9 Port PA[4] as Comparator Input

When using the PA[4] as an input to the internal SVLD comparator NO pull resistor should be connected on this terminal. Otherwise the device may draw excessive current.

First PA[4] pull-up/down resistor should be disconnected by software and the **ExtVcheck** bit can be set to '1'. This dedicates PA[4] as SVLD resistor divider input to the SVLD comparator.

At this point the measurements respect the same timing as any other SVLD measurements as explained in Chapter Supply Voltage Detector. It can also generate an IRQ if the input voltage is lower as Comparator level. Thus configured a direct read of PA[4] will result in reading '0'.

## 6.2.10 Reset and Sleep on Port A

During circuit initialisation, all Control registers are reset by Power On Reset and therefore all pull-ups are off and all pull-downs are on.

During Sleep mode, the circuit retains its register values. As such the PA configurations remain active also during Sleep.Sleep mode is cancelled with any Reset. However the Reset State does not reset the Control registers bits which are specifically marked to be initialised by POR only. (Pull, Nch Open drain, Freq out, etc configurations).

however Sleep mode is cancelled with a Reset and all system register will be reinitialized at this point. (the circuit is in Reset State. and pull-downs, if previously turned on. After any reset the serial interface parameters are reset to : Slave mode, Start and Status = 0, LSB first, negative edge shift , PA[3:0] tri-state.

## 6.2.11 Port A Blocked Inputs

In sleep mode if PortA inputs are not used and prepared for Wake-Up on Change or Reset these inputs are blocked. At that time port can be undefined from external and this will not generate an over-consumption.

- PA[0] : Blocked if Sleep bit set and no IRQ or Wake-up defined on this input

- PA[1] : Blocked if Sleep bit set

- PA[2] : Blocked if Sleep bit set

- PA[3] : Blocked if Sleep bit set and no IRQ or Wake-up defined on this input

- PA[4] : Blocked if Sleep bit set and no IRQ or Wake-up defined on this input Also blocked if External VLD check enabled

- PA[5] : Never blocked

## 6.3 PortA as Output and its Multiplexing

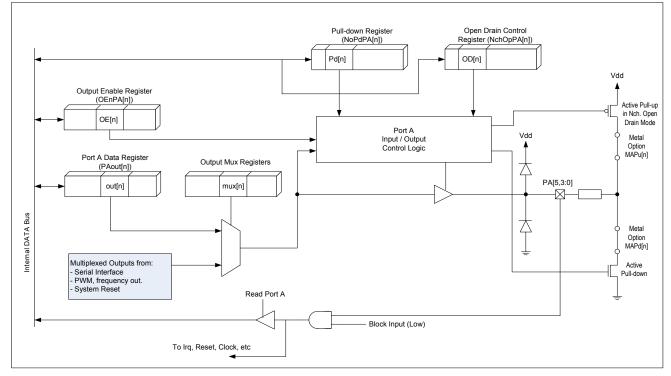

The EM6580 can have up to 4 (5 in Die form or 14-pin package) bit general purpose CMOS or N-channel Open Drain Output ports. Table 6.1.1 Input and Output ports overview shows all the possibilities. Figure 12 shows the output architecture and possible output signals together with software controlled pull-up and pull-down resistors which are disconnected when the port is an output and in a defined state, to preclude additional consumption.

The output multiplexing registers are **<u>RegPACntl3</u>** and **<u>RegPACntl4</u>**.

#### Figure 10. Port A Architecture (Outputs)

## 6.3.1 CMOS / Nch. Open Drain Output

The port A outputs can be configured as either CMOS or Nch. open drain outputs. In CMOS both logic '1' and '0' are driven out on the terminal. In Nch. Open Drain only the logic '0' is driven on the terminal, the logic '1' value is defined by the internal pull-up resistor (if implemented), or high impedance.

## NOTE: State of I/O pads may not be defined until $V_{reg}$ reaches typ. 0.8V and Power-On-Reset logic supplied by $V_{reg}$ clears them to Inputs.

This time depends on how fast capacitor on  $V_{reg}$  is charged and typ. it can be in range of couple of ms.

## 6.4 Port A registers

The two Control registers for Input control, <u>**RegPACntl1**</u> and <u>**RegPACntl2**</u>, were already shown in chapter 6; Input / Output Ports Overview.

#### Table 6.4.1 Register RegPA0

| Bit | Name      | Reset | R/W   | Description                     |

|-----|-----------|-------|-------|---------------------------------|

| 3   | PAData[3] | 0     | R* /W | PA[3] input and PAout[3] output |

| 2   | PAData[2] | 0     | R* /W | PA[2] input and PAout[2] output |

| 1   | PAData[1] | 0     | R* /W | PA[1] input and PAout[1] output |

| 0   | PAData[0] | 0     | R* /W | PA[0] input and PAout[0] output |

#### \* Direct read on Port A terminals

#### Table 6.4.2 Register **RegPa0OE**

| Bit | Name     | Reset        | R/W | Description                                       |

|-----|----------|--------------|-----|---------------------------------------------------|

| 3   | OEnPA[3] | 0            | R/W | I/O control for PA[3], output when OEnPA[3] = Hi  |

| 2   | OEnPA[2] | <b>0</b> P** | R/W | I/O control for PA[2], output when OEnPA[2] = Hi  |

| 1   | OEnPA[1] | 0            | R/W | I/O control for PA[1] , output when OEnPA[1] = Hi |

| 0   | OEnPA[0] | 0            | R/W | I/O control for PA[0] , output when OEnPA[0] = Hi |

P\*\* On Reset PA[2] is forced to output if ( PA[0]='0', PA[1]='1', PA[4]='1', Sout/RstPA[2]='1' and freqOutPA[2]='1') until System reset is finished. Refer also to Table 6.4.11.

After Reset is finished and circuit starts to execute instructions PA[2] becomes tri-state input. Bit OEnPA[2] is reset to '0' with every Reset.

#### Table 6.4.3 Register Pa0noPDown

| Name      | POR*                                             | R/W                                                                                                           | Description                                                                                                                                                   |

|-----------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NoPdPA[3] | 0                                                | R/W                                                                                                           | No pull-down on PA[3]                                                                                                                                         |

| NoPdPA[2] | 0                                                | R/W                                                                                                           | No pull-down on PA[2]                                                                                                                                         |

| NoPdPA[1] | 0                                                | R/W                                                                                                           | No pull-down on PA[1]                                                                                                                                         |

| NoPdPA[0] | 0                                                | R/W                                                                                                           | No pull-down on PA[0]                                                                                                                                         |

|           | NoPdPA[3]<br>NoPdPA[2]<br>NoPdPA[1]<br>NoPdPA[0] | NoPdPA[3]         0           NoPdPA[2]         0           NoPdPA[1]         0           NoPdPA[0]         0 | NoPdPA[3]         0         R/W           NoPdPA[2]         0         R/W           NoPdPA[1]         0         R/W           NoPdPA[0]         0         R/W |

POR\* Reset only with Power On Reset

#### Table 6.4.4 Register Pa0NchOpenDr

| Bit | Name                            | POR* | R/W | Description              |

|-----|---------------------------------|------|-----|--------------------------|

| 3   | NchOpDrPA[3]                    | 0    | R/W | Nch. Open Drain on PA[3] |

| 2   | NchOpDrPA[2]                    | 0    | R/W | Nch. Open Drain on PA[2] |

| 1   | NchOpDrPA[1]                    | 0    | R/W | Nch. Open Drain on PA[1] |

| 0   | NchOpDrPA[0]                    | 0    | R/W | Nch. Open Drain on PA[0] |

|     | * Deceterationalises with Deces |      |     |                          |

\* Reset only with Power On Reset, Default "0" is: CMOS on PA[3..0]

#### Table 6.4.5 Register RegPA1

| Bit | Name                              | Reset | R/W   | Description                                       |  |  |  |  |

|-----|-----------------------------------|-------|-------|---------------------------------------------------|--|--|--|--|

| 3   | NchOpDrPA[5]                      | p**   | R* /W | Nch. Open Drain on PA[5]                          |  |  |  |  |

| 2   | OEnPA[5]                          | 0     | R* /W | I/O control for PA[5] , output when OEnPA[5] = Hi |  |  |  |  |

| 1   | PAData[5]                         | 0     | R* /W | PA[5] input and PAout[5] output                   |  |  |  |  |

| 0   | PAData[4]*                        | 0     | R*    | PA[4] input                                       |  |  |  |  |

|     | * Direct read on Dart A terminale |       |       |                                                   |  |  |  |  |

\* Direct read on Port A terminals

p\*\* reset to '0' by POR only

#### Table 6.4.6 Register RegFreqRst

| Bit | Name       | POR | R/W | Description                                     |

|-----|------------|-----|-----|-------------------------------------------------|

| 3   | InResAH    | р   | R/W | Input reset On in Active and StandBy mode       |

| 2   | PA3/4resIn | р   | R/W | PA3/4 dedicated for Input reset when set at '1' |

| 1   | foutSel[1] | х   | R/W | Output Frequency selection (foutSel[1:0])       |

| 0   | foutSel[0] | Х   | R/W | (11)CPUClk, (10) SysClk, (01) 2kHz, (00) 1Hz    |

Interrupt PortA Control bits **MaskIRQPA[0/5]** and **MaskIRQPA[3/4]** used to enable (Mask) the Interrupt ReQuest IRQ from PortA are in register <u>RegIRQMask1</u>.

Interrupt status bits **IRQPA[0/5]** and **IRQPA[3/4]** used to signal the Interrupt from PortA are in register **<u>RegIRQ1</u>**. They are both shown in Chapter Interrupt Controller.

Note: CPUClk = RCClk if no external clock used.

In case of external clock, CPUClk is equal to the PA[1] input clock.

Output multiplexing registers are shown below.

#### Table 6.4.7 Register RegPACntl3

|     | <u> </u>      |     |     |                                        |

|-----|---------------|-----|-----|----------------------------------------|

| Bit | Name          | POR | R/W | Description                            |

| 3   | SerialStPA[3] | 0   | R/W | Output selection for PA[3] when output |

| 2   | SerialCkPA[1] | 0   | R/W | Output selection for PA[1] when output |

| 1   | PWMoutPA[1]   | 0   | R/W | Output selection for PA[1] when output |

| 0   | PWMoutPA[0]   | 0   | R/W | Output selection for PA[0] when output |

#### Table 6.4.8 Register RegPACntl4

| Bit | Name          | POR | R/W | Description                            |

|-----|---------------|-----|-----|----------------------------------------|

| 3   | NoPdPA[5]     | 0   | R/W | No pull-down on PA[5]                  |

| 2   | freqOutPA[5]  | 0   | R/W | Output selection for PA[5] when output |

| 1   | Sout/rstPA[2] | 1   | R/W | Output selection for PA[2] when output |

| 0   | freqOutPA[2]  | 1   | R/W | Output selection for PA[2] when output |

#### Table 6.4.9 PA[0] I/O status depending on its RegPACntl3 and RegPa0OE registers

| OEnPA[0] | PWMoutPA[0] | Description of PA[0] terminal      |

|----------|-------------|------------------------------------|

| 0        | X           | Input                              |

| 1        | 0           | PAout[0] general Output            |

| 1        | 1           | PWM Output from the 10-Bit Counter |

#### Table 6.4.10 PA[1] I/O status depending on its RegPACntl3 and RegPa0OE registers

| OEnPA[1] | SerialCkPA[1] | PWMoutPA[1] | Description of PA[1] terminal        |

|----------|---------------|-------------|--------------------------------------|

| 0        | X             | X           | Input                                |

| 1        | 0             | 0           | PAout[1] general Output              |

| 1        | 0             | 1           | PWM Output from the 10-Bit Counter   |

| 1        | 1             | X           | Sclk (Serial interface clock output) |

#### Table 6.4.11 PA[2] I/O status depending on its RegPACntl4 and RegPa0OE registers

| OEnPA[2]                                       | Sout/rstPA[2] | freqOutPA[2] | Description of PA[2] terminal                                                                                                   |

|------------------------------------------------|---------------|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| 0                                              | Х             | Х            | Input                                                                                                                           |

| 1                                              | 0             | 0            | PAout[2] general Output                                                                                                         |

| 1                                              | 0             | 1            | Freq. Output (CPUClk,SysClk, 2kHz, 1Hz)                                                                                         |

| 1                                              | 1             | 0            | Sout (Serial interface data output)                                                                                             |

| 1                                              | 1             | 1            | High level '1' during Reset state output<br>8kHz frequency output while out of reset state<br>Low level '0' output during sleep |

| 0<br>PA[0] = '1'<br>PA[4] = '1'<br>PA[1] = '0' | 1             | 1            | Output: high level during Reset state<br>Input: out of reset state and during sleep                                             |

Frequency output is selected in 6.4.6 Register RegFreqRst

#### Table 6.4.12 PA[3] I/O status depending on its **<u>RegPACntl3</u>** and **<u>RegPa0OE</u>** registers

| OEnPA[3] | SerialStPA[3] | Description of PA[3] terminal           |

|----------|---------------|-----------------------------------------|

| 0        | X             | Input                                   |

| 1        | 0             | PAout[3] general Output                 |

| 1        | 1             | Rdy/CS (Serial interface status output) |

#### Table 6.4.13 PA[5] I/O status depending on its RegPACntl4 and RegPA1 registers

| OEnPA[5] | freqOutPA[5] Description of PA[5] terminal |                                         |

|----------|--------------------------------------------|-----------------------------------------|

| 0        | X                                          | Input                                   |

| 1        | 0                                          | PAout[5] general Output                 |

| 1        | 1                                          | Freq. Output (CPUClk,SysClk, 2kHz, 1Hz) |

Frequency output is selected in 6.4.6 Register RegFreqRst

#### **Note:** CPUClk = RCClk if no external clock used.

In case of external clock, CPUClk is equal to the PA[1] input clock.

## 7. Serial Port

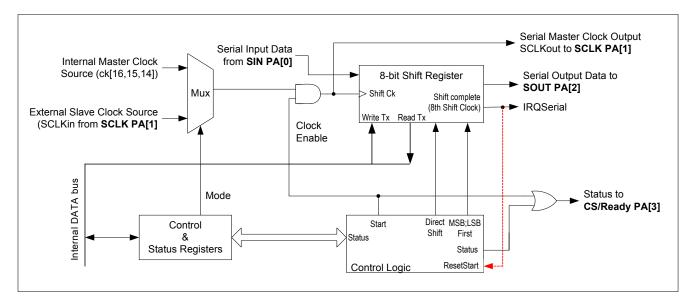

The EM6580 contains a simple, half duplex three wire synchronous type serial interface., which can be used to program or read an external EEPROM, ADC, ... etc. Its I/O are multiplexed on Port A.

For data reception, a shift-register converts the serial input data on the SIN(PA[0]) terminal to a parallel format, which is subsequently read by the CPU in registers **<u>RegSDataL</u>** and **<u>RegSDataH</u>** for low and high nibble. To transmit data, the CPU loads data into the shift register, which then serializes it on the SOUT(PA[2]) terminal. It is possible for the shift register to simultaneously shift data out on the SOUT terminal and shift data in on the SIN terminal. In Master mode, the shifting clock is supplied internally by the Prescaler : one of three prescaler frequencies are available, Ck[16], Ck[15] or Ck[14]. In Slave mode, the shifting clock is supplied externally on the SCLKIn(PA[1]) terminal. In either mode, it is possible to program : the shifting edge, shift MSB first or LSB first and direct shift output. All these selection are done in register <u>**RegSCnt11**</u> and <u>**RegSCnt12**</u>.

The PA[3..0] terminal configuration is shown in Figure 10 and 12. When the Serial Interface is used then care should be taken not to use inputs and outputs needed for Serial Interface for other peripherals !:

- \* PA[0] {SIN} must be dedicated to Serial input if needed and can not be used for IRQ, Software Variable jumps or Output. It can be still used for Wake-Up on Change

- \* PA[1] {SCLK} is an output for Master mode {SCLKOut} and an input for Slave mode {SCLKIn}. But different functions can be Switched On/Off with care as they are needed.

- \* PA[2] {SOUT} must be dedicated to Serial Data Output if needed and can not be used for Analogue input, or other Output.

- \* PA[3] {CS/ Ready } if used for serial Interface status output. When used for Serial Interface it should not be used for IRQ, Software Variable jumps or Output. It can be still used for Wake-Up on Change.

Note:

Before using the serial interface, the corresponding circuit terminals must be configured accordingly.

## 7.1 General Functional Description

After power on or after any reset the serial interface is in serial slave mode with **Start** and **Status** set to 0, LSB first, negative shift edge and all outputs are in high impedance state.

When the **Start** bit is set, the shift operation is enabled and the serial interface is ready to transmit or receive data, eight shift operations are performed: 8 serial data values are read from the data input terminal into the shift register and the previous loaded 8-bits are send out via the data output terminal. After the eight shift operation, an interrupt is generated, and the **Start** bit is reset.

#### Parallel to serial conversion procedure (master mode example).

Setup the circuit IO's accordingly.

Write to RegSCntl1 serial control (clock freq. in master mode, edge and MSB/LSB select).

Write to **<u>RegSDataL</u>** and **<u>RegSDataH</u>** (shift out data values).

Write to **<u>RegSCntl2</u>** (Start=1, mode select, status).  $\rightarrow$  Starts the shift out

After the eighth clock an interrupt is generated, Start becomes low. Then, interrupt handling

Serial to parallel conversion procedure (slave mode example).

Setup the circuit IO's accordingly. Write to <u>RegSCntl1</u> (slave mode, edge and MSB/LSB select). Write to <u>RegSCntl2</u> (Start=1, mode select, status). After eight serial clocks an interrupt is generated, **Start** becomes low. Interrupt handling. Shift register <u>RegSDataL</u> and <u>RegSDataH</u> read. A new shift operation can be authorized.

## 7.2 Detailed Functional Description

Master or Slave mode is selected in the control register RegSCntl1.

In Slave mode, the serial clock comes from an external device and is input via the PA[1] terminal as a synchronous clock (SCLKIn) to the serial interface. The serial clock is ignored as long as the **Start** bit is not set. After setting **Start**, only the eight following active edges of the serial clock input PA[1] are used to shift the serial data in and out. After eight serial clock edges the **Start** bit is reset. The PA[3] terminal is a copy of the (**Start OR Status**) bit values, it can be used to indicate to the external master, that the interface is ready to operate or it can be used as a chip select signal in case of an external slave.

In Master mode, the synchronous serial clock is generated internally from the system clock. The frequency is selected from one out of three sources (**MS0** and **MS1** bits in <u>RegSCntl1</u>). The serial shifting clock is only generated during **Start** = high and is output to the SCLK terminal as the Master Clock (SCLKOut). When **Start** is low, the serial clock output on PA[1] is 0.

An interrupt request **IRQSerial** is generated after the eight shift operations are done. This signal is set by the last negative edge of the serial interface clock on PA[1] (master or slave mode) and is reset to 0 by the next write of **Start** or by any reset. This interrupt can be masked with register **<u>RegIRQMask2</u>**. For more details about the interrupt handling see chapter 11.

Serial data input on PA[0] is sampled by the positive or negative serial shifting clock edge, as selected by the Control Register **POSnNeg** bit. Serial data input is shifted in LSB first or MSB first, as selected by the Control Register **MSBnLSB** bit.

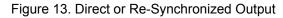

## 7.2.1 Output Modes

Serial data output is given out in two different ways. Refer also to Figures 15 and 16.

#### • **OM[0] =** 0 :

The serial output data is generated with the selected shift register clock (**POSnNeg**). The first data bit is available <u>directly</u> after the **Start** bit is set.

#### • **OM[0]** = 1 :

The serial output data is <u>re-synchronized</u> by the positive serial interface clock edge, independent of the selected clock shifting edge. The first data bit is available on the first positive serial interface clock edge after Start='1'.

#### Table 7.2.1 Output Mode Selection in RegSCntl2

| OM[0] Output mode |                     | Description                                  |

|-------------------|---------------------|----------------------------------------------|

| 0                 | Serial-Direct       | Direct shift pos. or neg. edge data out      |

| 1                 | Serial-Synchronized | Re-synchronized positive edge data shift out |

| SCLK = SerCk = Sys  |                 | Active Edge = N           | leg. Edge,          | Sense = MSB Fir  | st |     |     |          |

|---------------------|-----------------|---------------------------|---------------------|------------------|----|-----|-----|----------|

| Clock Source        |                 |                           |                     |                  |    |     |     |          |

| Shift SerCk         |                 |                           |                     |                  |    |     |     |          |

| Start               |                 |                           |                     |                  |    |     |     |          |

| IRQSerial           | . <u> </u>      |                           |                     |                  |    |     |     |          |

| Shift Register      | 10010011        | X                         | X                   | X                | X  | X   | X   | 01001100 |

| SIN                 | 0               | 1                         | 0                   | 0                | 1  | 1   | 0   | 0        |

| OM[0] = 1 :         | RE-SYNCHRON     | IZED on positive S        | CLK clock edge data | out (SOUT)       |    |     |     |          |

| SOUT                | 1               | 0                         | 0                   | 1                | 0  | 0   | 1   | 1        |

| OM[0] = 0 :<br>SOUT | DIRECT data out | t on pos.(+) or neg.<br>0 | -) SerCk clock edge | depending on bit |    | ) 1 | . 1 |          |

|                     |                 |                           |                     |                  |    |     |     |          |

Figure 14. Shift Operation and IRQ Generation

**Note :** A write operation in the control registers or in the data registers while **Start** is high will change internal values and may cause an error condition. The user must take care of the serial interface status before writing internal registers. In order to read the correct values on the data registers, the shift operation must be halted during the read accesses.

## 7.3 Serial Interface Registers

#### Table 7.3.1 Register RegSCntl1

|     | •                     |          |     |                                                               |

|-----|-----------------------|----------|-----|---------------------------------------------------------------|

| Bit | Name                  | Reset    | R/W | Description                                                   |

| 3   | MS1                   | 0        | R/W | Frequency selection                                           |

| 2   | MS0                   | 0        | R/W | Frequency selection                                           |

| 1   | POSnNeg               | 0        | R/W | Positive or negative clock edge selection for shift operation |

| 0   | MSBnLSB               | 0        | R/W | Shift MSB or LSB value first (0=LSB first)                    |

| •   | Default "0" in: Clave | mada avt |     | c pogetive edge I SD first                                    |

Default "0" is: Slave mode external clock, negative edge, LSB first

#### Table 7.3.2 Frequency and Master Slave Mode Selection

| MS1 | MS0 | Description                          |

|-----|-----|--------------------------------------|

| 0   | 0   | Slave mode: Clock from external      |

| 0   | 1   | Master mode Ck[14]: System clock / 4 |

| 1   | 0   | Master mode Ck[15]: System clock / 2 |

| 1   | 1   | Master modeCk[16]: System clock      |

#### Table 7.3.3 Register RegSCntl2

| Bit | Name     | Reset | R/W | Description                                             |

|-----|----------|-------|-----|---------------------------------------------------------|

| 3   | Start    | 0     | R/W | Enabling the interface,                                 |

| 2   | Status   | 0     | R/W | Ready or Chip Select output on PA[3]                    |

| 1   | RCoscOff | 0     | R/W | RC oscill. disable when set @ '1' if ExtCPUclkOn is '1' |

| 0   | OM[0]    | 0     | R/W | '0': Direct shift Output,                               |

|     |          |       |     | '1': Output resynchronized                              |

Default "0" is: Interface disabled, status 0, direct shift output.

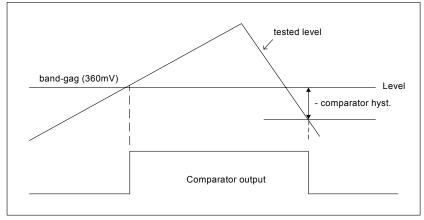

#### Table 7.3.4 Register RegSDataL