- 12-Bit ADC With 4-Multiplexed Inputs

- Wide Supply Voltage Range 2.6 V to 5.5 V

- Low Power Consumption Typical at V<sub>DD</sub> = 3 V

- 0.1 μA in OFF Mode

- 4 µA in DONE Mode

- 80 μA in ACTIVE Mode Without A/D Conversions

- 300 μA in ACTIVE Mode With A/D Conversions

- Onboard 4-MUX 56-Segment LCD Driver

- Onboard Ratiometric Current Source Programmable From 0.15 mA × (SV<sub>DD</sub>/V) to 2.4 mA × (SV<sub>DD</sub>/V)

- Two Independent Crystal Controlled Timers (32.768 kHz)

- Internal MOS Oscillator Serves as System Clock

- Programmable Microcontroller

- Simple and Easy Programming With SMPL™ Macro Language

# • Onboard 4-MUX 56-Segment LC

# description

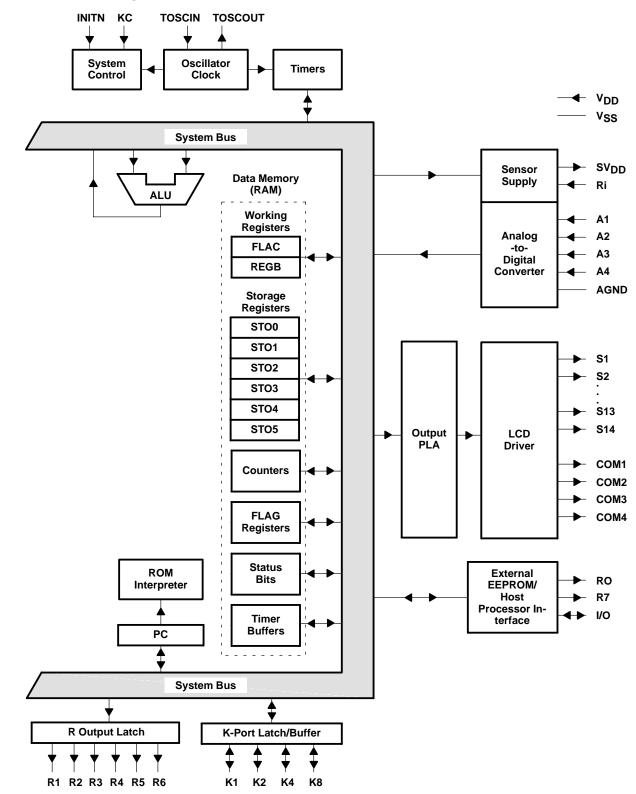

The TSS400 Standard (TSS400-S1) sensor signal processor is an ultra-low power, intelligent, 12-bit A/D converter (ADC) that has been preprogrammed with the Sensor Macro Programming Language (SMPL™) interpreter. This language allows fast, easy, and economical customization of the TSS400-S1 to a wide range of sensor signal processing applications. The application specific programs that customize the operation of the TSS400-S1 are stored in external EEPROMs along with any additional data required by the application. The main components of the TSS400-S1 are a four-input multiplexed 12-bit ADC, a programmable constant current source, an LCD driver capable of driving 56 segments using a 4-MUX drive scheme, two crystal controlled independent timers, an on-board RAM, six output-only pins (R1 to R6), a 4-bit programmable I/O port (K1, K2, K4, K8), and I²C serial EEPROM communications. Operation of the TSS400-S1 is very adaptive because it is controlled by a SMPL language program. These programs can be stored in an external EEPROM (standalone mode) or stored in a host computer (slave mode). The SMPL language is a powerful, easy to learn, and easy to use macro language. Some of the SMPL language features are single-command EEPROM read and EEPROM write operations, three levels of subroutines, a single-command A/D conversion instruction that specifies the number of conversions and the type of conversion (either compensated or noncompensated) to be made, and two reduced power consumption modes (DONE and OFF).

## AVAILABLE OPTIONS

| т.             | PACKAGE          |

|----------------|------------------|

| TA             | 44-PIN PLCC (FN) |

| 0°C to 70°C    | TSS400CFN-S1     |

| -40°C to 125°C | TSS400AFN-S1     |

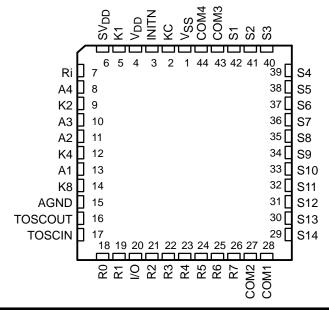

FN PACKAGE (TOP VIEW)

SMPL is a trademark of Texas Instruments Incorporated.

Texas VI

Copyright © 1993, Texas Instruments Incorporated

## **Terminal Functions**

| SIGNAL NAME               | PIN NUMBER                | 1/0 | DESCRIPTION                                                                                                                                              |  |

|---------------------------|---------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1, A2, A3, A4            | 13, 11, 10, 8             | I   | Analog input for the ADC                                                                                                                                 |  |

| AGND                      | 15                        |     | Analog ground                                                                                                                                            |  |

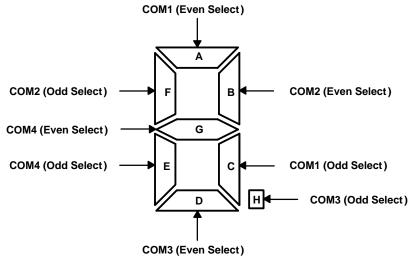

| COM1, COM2, COM3,<br>COM4 | 28, 27, 43, 44            | 0   | LCD commons                                                                                                                                              |  |

| I/O                       | 20                        | I/O | Communication input/output                                                                                                                               |  |

| INITN                     | 3                         | I   | Initialization. INITN is normally tied to $V_{DD}$ and held high. If INITN is held low for more than 10 $\mu s$ , the TSS400-S1 will begin a warm start. |  |

| K1, K2, K4, K8            | 5, 9, 12, 14              | I/O | 4-bit programmable input/output port                                                                                                                     |  |

| KC                        | 2                         |     | Test. This pin must be tied to VSS during normal operation.                                                                                              |  |

| R0 <sup>†</sup>           | 18                        | 0   | EEPROM clock. Controls the EEPROM clock.                                                                                                                 |  |

| R1, R2, R3, R4,<br>R5, R6 | 19, 21, 22, 23,<br>24, 25 | 0   | Digital outputs                                                                                                                                          |  |

| R7 <sup>†</sup>           | 26                        | 0   | Controls EEPROM power switch                                                                                                                             |  |

| Ri                        | 7                         |     | Current source ( programming resistor connection )                                                                                                       |  |

| S1 — S14                  | 42 — 29                   | 0   | LCD segments                                                                                                                                             |  |

| SV <sub>DD</sub>          | 6                         |     | Switchable V <sub>DD</sub>                                                                                                                               |  |

| TOSCIN                    | 17                        | I   | Oscillator input. Input connection for crystal oscillator (32.768 kHz).                                                                                  |  |

| TOSCOUT                   | 16                        | 0   | Oscillator output. Output connection for crystal oscillator (32.768 kHz).                                                                                |  |

| $V_{DD}$                  | 4                         |     | Power supply                                                                                                                                             |  |

| V <sub>SS</sub>           | 1                         |     | Ground                                                                                                                                                   |  |

<sup>†</sup> Not directly accessible by the user's program.

## functional block diagram

# TSS400-S1 μPOWER PROGRAMMABLE HIGH-PRECISION SENSOR SIGNAL PROCESSOR

SLMS001 - D4071, JANUARY 1993

### description (continued)

The TSS400-S1 is designed to meet a wide variety of sensor systems applications including those that require short time-to-market and rapid and/or frequent programming updates. Since the TSS400-S1 does not require mask programming, it can be purchased in any quantity. Some typical applications include:

- measurements of temperature, pressure, acceleration, gas content, magnetic field, relative humidity, speed, direction, and volume

- measurements requiring calculation, control, and/or warning functions

- measurements where temperature compensation is required for accuracy

- measurements where software calibration and linearization is desirable

These sensor systems can be found in many types of applications including home appliances, industrial control subsystems, HVAC systems and instrumentation, portable instrumentation, consumer products, automotive products, or anywhere precise (12-bit), ultra-low power (12  $\mu$ A – 15  $\mu$ A, TYP), intelligent A/D conversion is essential.

The TSS400-S1 is available in two temperature ranges. The TSS400CFN-S1 is characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C. The TSS400AFN-S1 is characterized for operation from  $-40^{\circ}$ C to  $125^{\circ}$ C.

## initialization and power up

Initialization is started by hardware in two ways:

- Power up: The voltage V<sub>DD</sub> is switched on (cold start). The CPU starts to work at PC 000 after the internal oscillator has started operation. This may take from 1 to 6 seconds.

- INITN pin: If the INITN pin is held low (switched to ground) for more than 10 μs (when this occurs during program execution it is called a warm start). The CPU starts operation at PC 000 when the INITN pin is released to V<sub>DD</sub> potential.

Table 1 lists the TSS400-S1 register contents after a power up or an INITN pin initialization.

**Table 1. Register Contents**

| REGISTER                       | POWER UP<br>(COLD START) | INITN PIN<br>(WARM START) |

|--------------------------------|--------------------------|---------------------------|

| Program Counter (PC)           | 000                      | 000                       |

| Status bits POS, NEG, and ZERO | undefined                | unchanged                 |

| RAM contents†                  | reset to 0               | unchanged                 |

| Digit Latches (DLn)            | reset to 0               | reset to 0                |

| K-Line's Latches Contents      | undefined                | unchanged                 |

| Timers                         | 0                        | unchanged                 |

| ADC Voltage SV <sub>DD</sub>   | switched off             | switched off              |

| LCD Segment Latches            | undefined                | unchanged                 |

| Subroutine Stack               | level 0                  | level 0                   |

<sup>†</sup> Despite the RAM remaining unchanged during a warm start, the memory addressed when INITN is activated may be destroyed by a write cycle.

### initialization and power up (continued)

If the TSS400-S1 system is battery powered and contains calibration factors or other important data in RAM, it is advisable to distinguish between cold start and warm start. The reason is the possibility of initializations caused by electromagnetic inductance (EMI). If such an erroneous initialization is not tested for legality, EMI influence could destroy the RAM contents by clearing the RAM with the initialization software routine. The TSS400-S1 compares two reserved RAM nibbles to see if they contain  $A5_{16}$  after each initialization:

- If the RAM nibbles contain the expected information (A5<sub>16</sub>), initialization continues at PC 000. The RAM contents are not changed. This means that a spurious signal caused the initialization (warm start).

- If the RAM nibbles differ from A5<sub>16</sub>, the RAM is cleared and the program continues at PC 000. This means that the TSS400-S1 supply voltage was switched on (cold start).

The short timer and the long timer are not stopped by a warm start. This means that they remain active and must be stopped by a STPTIMx instruction, if necessary.

### operating conditions

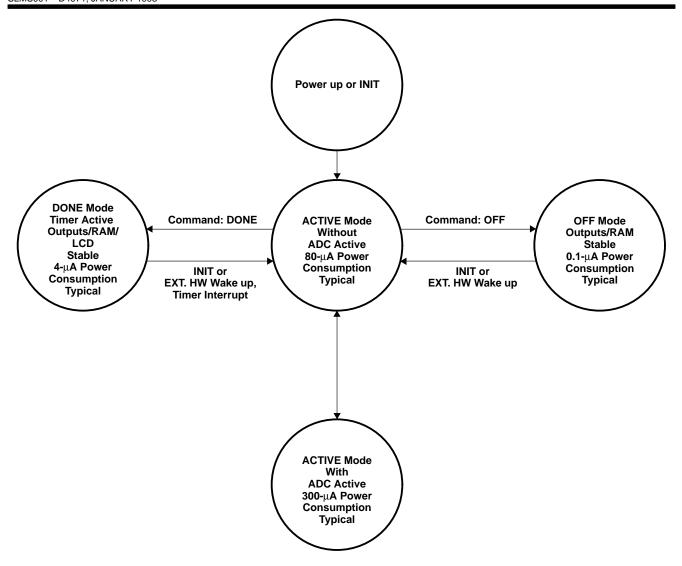

The TSS400-S1 has four different modes of operation: OFF, DONE, ACTIVE without A/D conversion, and ACTIVE with A/D conversion. The OFF mode conserves the most power. In this mode, only the RAM and the outputs (I/O, R outputs, and K lines) are maintained. The TSS400-S1 enters OFF mode with a software command and is awakened via the K lines or by initialization. Table 2 lists the conditions needed for the K lines to awaken the processor.

DL15 K8 K4 K2 K1 CONDITION .AND. .AND. .AND. 0 0 0 0 0 condition before wake up .OR. .OR. .OR. 1 1 1 1 1 condition to wake up processor 0 1 AND. 0 .AND. 0 .AND. 0 condition before wake up 0 OR. .OR. OR. condition to wake up processor

Table 2. K-Line Wake-Up Conditions

The DONE mode is also a low-power mode. In the DONE mode, the RAM, the outputs, and the display are maintained and the timekeeping circuits remain active. The device enters DONE mode with a software command and is awakened via the K lines, initialization, or with a wake up by internal timers.

When the TSS400-S1 is executing instructions, it is in the ACTIVE mode. This mode can be broken into two separate states; with A/D conversion and without A/D conversion. All portions of the TSS400-S1 are fully operational in the ACTIVE with A/D conversion mode, only the A/D conversion circuitry is powered down in the ACTIVE without A/D conversion mode. See Figure 1 for a state diagram of the TSS400-S1 operational modes.

Figure 1. State Diagram for TSS400-S1 Operational Modes

Check current supply voltage against value in FLAC

Set minimum supply voltage point

SLMS001 - D4071, JANUARY 1993

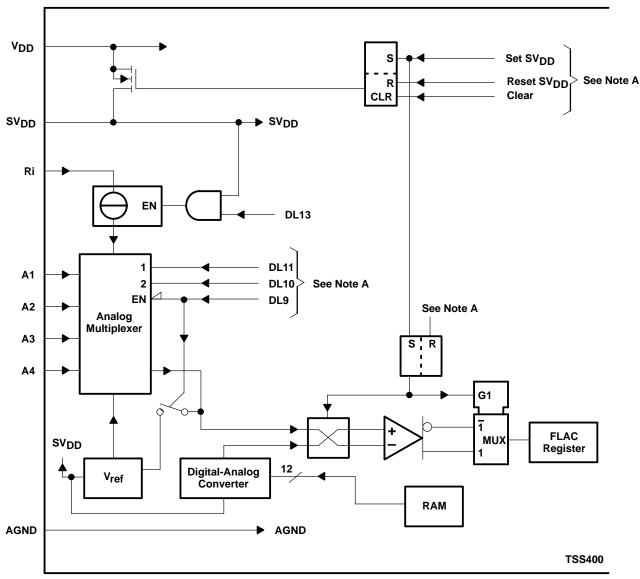

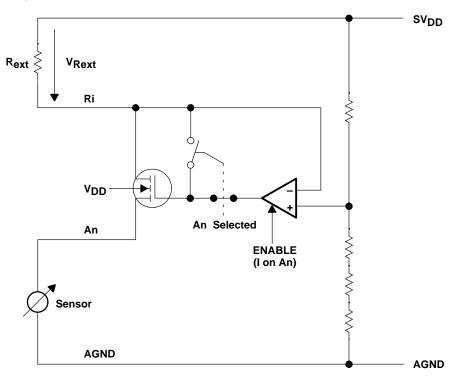

### analog-to-digital converter (ADC) (see Figure 2)

Χ

Χ

1

1

**CHKBATT**

**ADJBATT**

The TSS400-S1 offers a 12-bit ratiometric successive approximation ADC. Sensors are interfaced to this converter via the 4-multiplexed (4-MUX) analog inputs (A1 – A4). The analog conversion operation is executed with the MEASR instruction. The SMPL interpreter automatically switches the internal digit latches DL9, DL10, and DL11 such that the ADC is connected to the analog input line specified by the MEASR operand. Table 3 lists the instructions required to access all four analog inputs.

OPERAND DL10 INSTRUCTION DL9 DL11 **ACTION MEASR** 0 Connect A1 to the ADC **MEASR** 1 0 0 0 Connect A2 to the ADC 2 **MEASR** 0 1 1 Connect A3 to the ADC **MEASR** 3 0 0 1 Connect A4 to the ADC

Χ

Х

**Table 3. Instructions Required to Access Analog Inputs**

The interpreter automatically switches on the switched-sensor supply voltage ( $SV_{DD}$ ) just prior to making the A/D conversion and switches it off immediately after the conversion is complete. The MEASR instruction is followed by a BYTE instruction. The operand of the BYTE instruction specifies the number of conversions to be made and whether the conversions are to be compensated or noncompensated. A noncompensated measurement is a single A/D conversion. A compensated measurement is defined as a measurement where two conversions are made, one conversion with the ADC comparator connected normally and the other conversion with the comparator inputs reversed. The two results are added together so any comparator offsets cancel. The interpreter automatically takes care of all required switching to perform the specified type of conversion.

Χ

Χ

Absolute measurements are possible if  $SV_{DD}$  is held constant. This requires a stable  $V_{DD}$  during the conversion and constant loading of  $SV_{DD}$ . The ADC measures the ratio of the input voltage at the analog input  $(V_{DD})$  to the switched-sensor supply voltage  $(SV_{DD})$  and not absolute voltages. This ensures that the measurement of the sensors is independent of the supply voltage.

NOTE A: These signals are automatically controlled by the interpreter during A/D conversion.

Figure 2. ADC Functional Block Diagram

## measurement range and conversion formulas

The analog input range is the same for all four analog outputs, A1 to A4. The nominal properties of the ADC range and the equations associated with them are listed below:

$$V_I = (A + B \times N) \times SV_{DD}$$

where

V<sub>I</sub> = unknown analog input voltage

A = converter count for  $V_I = 0$

= 0.1012113203 for the TSS400-S1

B = delta in  $\mu V/SV_{DD}$  for a 1-bit difference in conversion result

= 0.000096090233 for the TSS400-S1

N = A/D conversion result for a single measurement

SV<sub>DD</sub> = Switched sensor supply voltage

For the TSS400-S1, the analog input voltage is:

$$V_1 = (0.1012113203 + 0.000096090233 \times N) \times SV_{DD}$$

For multiple measurements, the V<sub>I</sub> equation becomes:

$$V_{I} = (A + \frac{B \times N}{M}) \times SV_{DD}$$

$$= \frac{(0.1012113203 \times SV_{DD}) + (0.000096090233 \times N \times SV_{DD})}{M}$$

where M = the number of measurements taken

Since a conversion result of 0 is used to indicate an under-range input and FFF<sub>16</sub> is used to indicate an over-range input, the allowable range for N (in a single measurement) is:

$$1_{16} \le N \le FFF_{16}$$

or in decimal format:

$$1 \le N \le 4094$$

The minimum measurable analog input voltage to SV<sub>DD</sub> ratio is:

$$\begin{aligned} V_{l} min &= \frac{V_{l}}{SV_{DD}} \text{ when } N = 1 \\ &= \frac{(0.1012113203 + 0.00009609023) \times SV_{DD}}{SV_{DD}} \end{aligned}$$

= 0.101309

The maximum measurable analog input voltage to SV<sub>DD</sub> ratio is:

$$V_{I}$$

max =  $\frac{V_{I}}{SV_{DD}}$  when N = 4094

=  $\frac{(0.1012113203 + 0.000096090233 \times 4094) \times SV_{DD}}{SV_{DD}}$

= 0.494605

So the allowable analog input voltage range for  $V_I$  is:

$$0.101307 \times SV_{DD} \le V_{I} \le 0.494605 \times SV_{DD}$$

If the input voltage is below the lower limit,  $V_I$ min, the value  $000_{16}$  is returned. If the input voltage is above the upper limit,  $V_I$ max, the value FFF<sub>16</sub> is returned. The NEG status bit is set in both cases. The ZERO status bit is set if  $000_{16}$  is returned.

#### battery check

Since the TSS400-S1 is ideal for battery applications, an internal supply voltage check is available. This operation is executed by the instructions ADJBATT and CHKBATT. ADJBATT measures the internal reference voltage and puts the results in the FLAC register. By setting the supply voltage at a minimum acceptable level and executing the ADJBATT instruction, a representative value will be placed in the FLAC register. Saving this number in a storage register or EEPROM location will enable it to be recalled for use by the CHKBATT instruction when the current supply voltage needs to be checked against the preset acceptable minimum. To perform these operations, an internal stable reference is connected to the input of the ADC and a measurement is made. Due to the ratiometric nature of the conversion, the measured value is an indication of the TSS400-S1 supply voltage. The ADJBATT instruction performs this operation and stores the result in the FLAC register. The CHKBATT instruction performs the same operation, but compares the resulting measurement to the number in the FLAC register and sets the positive (POS) and negative (NEG) status bits according to the result.

### programmable current source

A switchable ratiometric (to  $SV_{DD}$ ) current source is available for supplying a fixed amount of current to the analog sensors. When turned on, the current source sends a constant current out of the addressed analog input (An). The voltage generated by the external sensor is measured with the same An input. The voltage used for A/D conversions and the reference voltage ( $V_{ref}$ ) used to set the current of the current source are both proportional to  $SV_{DD}$  and have a fixed ratio to each other. This ensures optimum tracking. The current source is activated by digit latch DL13. When DL13 is set to 1 and  $SV_{DD}$  is on, the current source is on. When DL13 is set to 0, the current source is off. Figure 3 shows a diagram of the programmable current source.

The current I is programmed by an external resistor  $R_{ext}$ , which is connected between  $SV_{DD}$  and Ri. This current is given by the following equation:

$$I_{An} = \frac{V_{Rext}}{R_{ext}}$$

Vrext is approximately 0.24 × SV<sub>DD</sub>

The programmable current range that the current source can supply to the ADC input is: 0.15 mA to 2.4 mA  $\times$  (SV<sub>DD</sub>/V)

$$V_{I} = I_{An} \times R_{I}$$

with  $R_{I} = Sensor Resistance$

$V_{I} = V_{Rext} \times \frac{R_{I}}{R_{ext}}$

Figure 3. Programmable Current Source Diagram

#### timers

There are two independent crystal-controlled timers available on the TSS400-S1. The required crystal is a 32.768 kHz crystal. This allows very accurate time measurements and clock functions to be performed. These timers function at 1 Hz and 16 Hz and can be used as a wake-up signal from the DONE mode of operation in addition to the other timing functions. The crystal is also used to control the LCD driver circuitry.

#### counters

Two decimal counters, Counter 1 and Counter 2, are available for use on the TSS400-S1. The individual counters range from 0 to 99 or they can be cascaded together for a range of 0 to 9999. Counter 1 is the least significant part of the combined counter. After the counters are incremented or decremented, the ZERO status bit is set when the counter reaches zero or reset if counter is not zero.

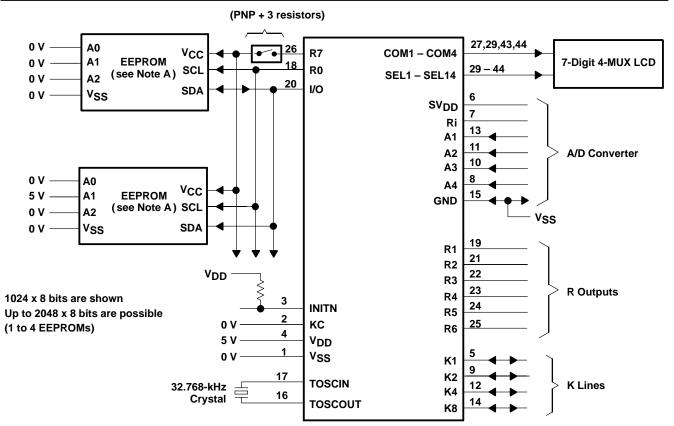

#### **EEPROM addressing**

The TSS400-S1 interpreter reads each SMPL instruction from the external EEPROM using the I<sup>2</sup>C serial communications, interprets the opcode, and performs the required operation. A TSS400-S1 complete system requires two devices (plus sensors) for a minimum configuration (the TSS400-S1 and an EEPROM). The TSS400-S1 interpreter uses the 11-bit wide program counter (PC) to address up to 2K-bytes of EEPROM (the maximum length for a user's program). Table 4 lists the hardware addresses of the four EEPROMs as defined by the logic levels of pins A1 and A2.

**Table 4. EEPROM Hardware Addresses**

| EEPRO | M PINS | ADDRESS SPACE                                        |

|-------|--------|------------------------------------------------------|

| A2    | A1     | ADDRESS SPACE                                        |

| 0     | 0      | 0 — 511 (0 <sub>16</sub> —1FF <sub>16</sub> )        |

| 0     | 1      | 512 — 1023 (200 <sub>16</sub> —3FF <sub>16</sub> )   |

| 1     | 0      | 10242 — 1535 (400 <sub>16</sub> —5FF <sub>16</sub> ) |

| 1     | 1      | 15362 — 2047 (600 <sub>16</sub> —7FF <sub>16</sub> ) |

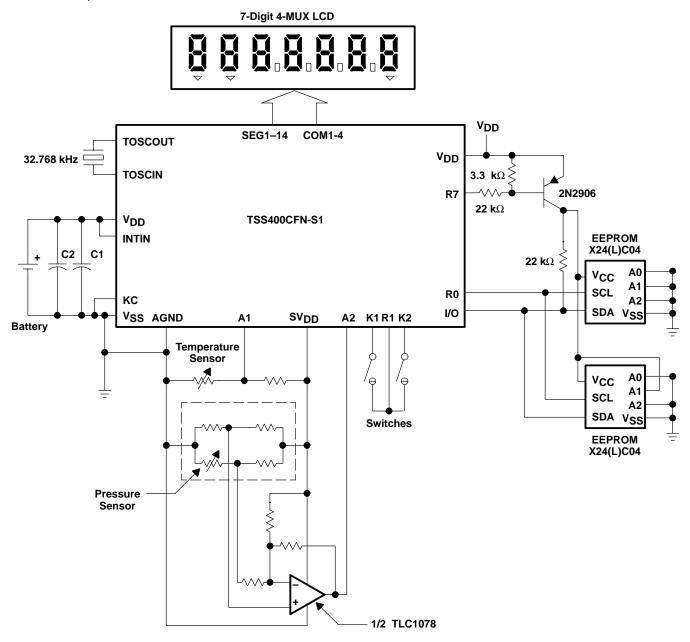

Figure 4 shows the TSS400-S1, two EEPROMs, a 32.768-kHz crystal, and a 7-digit LCD connected in a typical system configuration.

NOTE A: The EEPROM shown is a Xicor X24(L)C04. Other manufacturers of I<sup>2</sup>C EEPROMs include Thompson CFS and Phillips/Signetics.

Figure 4. Typical System Configuration

## RAM usage

The TSS400-S1 RAM is organized into several registers. Some of these registers are used for system purposes and some are available to the user. These available registers and their usages are described in the following sections.

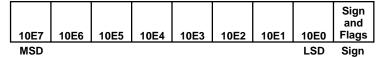

#### **FLAC** register

The FLAC register is the main working register of the TSS400-S1. It consists of 8 nibbles for the number, 1 nibble for the sign, and two flags that are used internally by arithmetic routines. The sign bit is set to zero for positive numbers and one for negative numbers. The following diagram shows the format of the FLAC register:

The FLAC register is used for:

- receiving the results of an A/D conversion

- storing the results of all arithmetic and logic operations

- holding the first operand for arithmetic and logic operations

- containing the result of a hexadecimal to decimal conversion

- holding the information for transfer to the EEPROM

- holding the information to be displayed on the LCD

### **REGB** register

The REGB register is the second working register. It consists of 8 nibbles for the number and 1 nibble for the sign. The format of the REGB register is the same as the FLAC register. The REGB register is used for:

- holding the second operand for arithmetic and logic operations

- holding the constants read from the EEPROM

- holding the contents after transfers from the counters

#### storage registers

The TSS400-S1 has six general-purpose storage registers. These storage registers have the same format as the FLAC register, each with 8 nibbles for the number and 1 nibble for the sign. These storage registers are addressable by using the names STO0 to STO5. Use of the STO0 register is restricted since it is also used by the device during multiplication, division, and hexadecimal-to-decimal conversions. After multiplication and hexadecimal-to-decimal conversion operations, the contents of STO0 are set to 0 and after a division STO0 contains the remainder of the operation. This remainder can be used in conversions (e.g., minutes to hours).

#### flag registers

Two general-purpose flag register groups, each with 16 flags, have been set aside. They are named Group 1 and Group 2. The selection of the groups is made with the SMPL instructions SELGRP1 and SELGRP2. The group selected is in use until the other group is selected. Each of the 16 flags in each group may be set, reset, and tested. The contents of the flags can then be used to control the program flow, define the action of jumps, indicate errors in hardware function, and any other user defined purpose. The use of some of the flags is restricted since their operation has been predefined. Table 5 lists the assigned use of each flag.

|      | GROUP               | 1 FLAGS |             | GROUP 2 FLAGS |            |      |            |

|------|---------------------|---------|-------------|---------------|------------|------|------------|

| FLAG | DEFINITION          | FLAG    | DEFINITION  | FLAG          | DEFINITION | FLAG | DEFINITION |

| 0    | Arbitrary           | 8       | Arbitrary   | 0             | Arbitrary  | 8    | Arbitrary  |

| 1    | Seg. H1 information | 9       | Arbitrary   | 1             | Arbitrary  | 9    | Arbitrary  |

| 2    | Seg. H2 information | 10      | Long Timer  | 2             | Arbitrary  | 10   | Arbitrary  |

| 3    | Seg. H3 information | 11      | Short Timer | 3             | Arbitrary  | 11   | Arbitrary  |

| 4    | Seg. H4 information | 12      | K1 Buffer   | 4             | Arbitrary  | 12   | Arbitrary  |

| 5    | Seg. H5 information | 13      | K2 Buffer   | 5             | Arbitrary  | 13   | Arbitrary  |

| 6    | Seg. H6 information | 14      | K4 Buffer   | 6             | Arbitrary  | 14   | Arbitrary  |

| 7    | Seg. H7 information | 15      | K8 Buffer   | 7             | Arbitrary  | 15   | Arbitrary  |

**Table 5. Flag Assignment**

## R outputs and digit latches

Outputs R1 through R6 are available as general-purpose outputs. They can be used for scanning keyboards or switches, for controlling relays, lamps, LCDs, etc., or for digital communications using buffers, multiplexers, etc. as required by the designer. The R0 and R7 outputs cannot be addressed by the software. They are used by the interpreter when the EEPROM reads or writes are performed. R0 performs as the clock connection and R7 switches the supply voltage to the EEPROM as required to conserve system power.

The TSS400-S1 contains 14 one-bit digit latches (DL0 through DL13) that (except for DL0 and DL7) can be set and reset independently with software. These digit latches can be separated into two distinct groups, those with external outputs (DL0 through DL7) and those without external outputs (DL8 through DL13).

The digit latches without external outputs (DL8 through DL13) each control a unique hardware function. Table 6 gives the digit-latch names and the hardware functions they control.

**Table 6. Digit Latch Names and Hardware Functions**

| DIGIT LATCH |                                          | HARDWARE FUNCTION                                       |                |                                                |  |  |

|-------------|------------------------------------------|---------------------------------------------------------|----------------|------------------------------------------------|--|--|

| DL0         | Not user add                             | dressable (R0)                                          | , clock for EE | PROM                                           |  |  |

| DL1 — DL6   | 6 R outputs                              | (R1–R6) for g                                           | eneral use     |                                                |  |  |

| DL7         | Not user add                             | dressable (R7)                                          | , power switc  | ch for EEPROM                                  |  |  |

| DL8         | 0                                        | 0 Sets K port to input                                  |                |                                                |  |  |

| DLO         | 1 Sets K port to output                  |                                                         |                |                                                |  |  |

|             | DL9                                      |                                                         | DL11           | Addressed Analog Input<br>Connected to the ADC |  |  |

|             | 0                                        | 0                                                       | 0              | A1                                             |  |  |

| DL9 — DL11† | 0                                        | 1                                                       | 0              | A2                                             |  |  |

|             | 0                                        | 0                                                       | 1              | A3                                             |  |  |

|             | 0                                        | 1                                                       | 1              | A4                                             |  |  |

|             | 1                                        | Х                                                       | Х              | Battery check functions                        |  |  |

| DL12        | 0                                        | 1-Hz timer input into the ALU for timer instructions    |                |                                                |  |  |

| DLIZ        | 1                                        | 1 16-Hz timer input into the ALU for timer instructions |                |                                                |  |  |

| DL13        | 0 Constant current source of the ADC off |                                                         |                | of the ADC off                                 |  |  |

| DLIS        | 1                                        | Constant cur                                            | rent source o  | of the ADC on, if SV <sub>DD</sub> is on       |  |  |

<sup>†</sup> It is not normally necessary to change these digit latches with software since the interpreter controls them automatically.

#### **K Port**

The K port is a 4-bit programmable I/O port with individual lines labeled K1, K2, K4, and K8. The direction of data flow through the K lines is controlled by digit latch DL8. Data to be output through the K lines is first stored in the 4-bit K-lines latch. The K-port output structure is open source. For data input, the K lines are read via Schmitt triggers into the ALU. If the TSS400-S1 has been placed in either the OFF or DONE mode, it is possible to use the K lines to generate a wake-up signal.

#### status logic

The status logic consists of 3 bits that are modified after the execution of specific instructions. The status bits are checked by conditional jumps that are executed or not executed depending on the state of the tested status bit. Please note that not every instruction rewrites the status bits. If an instruction does not affect the status bits, the status of the last instruction to rewrite the status bits is preserved. The following diagram shows the 3 bits making up the status logic.

| POS | NEG | ZERO |

|-----|-----|------|

#### **POS** bit

The POS bit is set after an arithmetic instruction if the result of the operation has a positive sign. If the result is negative, the POS bit is reset. Other instructions will set the POS bit if no error occurred making it possible to use the POS bit status as an error indicator. If the A/D measurement is within range, the POS bit is set.

#### **NEG** bit

The NEG bit is set after an arithmetic instruction if the result of the operation has a negative sign. If the result is positive, the NEG bit is reset. Other instructions will set the NEG bit if an error occurred making it possible to use the NEG bit status as an error indicator. If the A/D measurement is out of range, the NEG bit is set.

#### **ZERO** bit

The ZERO bit is set to one if the result of the last instruction is zero or if a comparison results in equality. If the result is not zero or the comparison is not equal, the ZERO bit is cleared. If the A/D measurement is under range, ZERO bit is set.

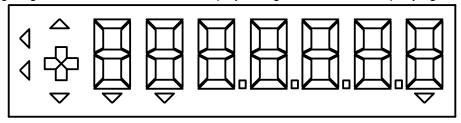

#### LCD driver

The TSS400-S1 contains LCD-driver circuitry that is designed to get the best results for a wide range of applications. From a software point of view, the LCD 4-MUX 56-segment driver looks very simple:

No timing problems exist with multiplexing for getting a quiet, stable display. The LCD-driver hardware outputs display information automatically without any software burden during the ACTIVE and DONE modes of operation.

Software has only to decide which segment information is to be displayed and in which digit to display it.

NOTE: LCDs are available for prototype development. Contact the nearest TI sales office for more information.

#### digit addressing

The following diagram shows the TSS400-S1 display configuration and accompanying FLAC nibbles.

| FLAC<br>NIBBLE | 10E7 | 10E6  | 10E5  | 10E4  | 10E3  | 10E2   | 10E1    | 10E0    |

|----------------|------|-------|-------|-------|-------|--------|---------|---------|

| SELECTS        | _    | S1/S2 | S3/S4 | S5/S6 | S7/S8 | S9/S10 | S11/S12 | S13/S14 |

| DIGIT n        | _    | 1     | 2     | 3     | 4     | 5      | 6       | 7       |

The FLAC's MSD (10E7) cannot be displayed because of the 7-digit configuration of the display driver. If it is necessary to display the MSD, a shift right (SHIFTR) with decimal correction of the FLAC contents will have to be done.

#### segment addressing

The OPLA terms definition is based on the following hardware configuration.

|                    | SELECT LINES |    |    |    |     |     |     |   | COM | MON |   |

|--------------------|--------------|----|----|----|-----|-----|-----|---|-----|-----|---|

|                    | SELECT LINES |    |    |    |     |     | 1   | 2 | 3   | 4   |   |

| ODD SELECT         | S1           | S3 | S5 | S7 | S9  | S11 | S13 | С | F   | Н   | Е |

| <b>EVEN SELECT</b> | S2           | S4 | S6 | S8 | S10 | S12 | S14 | Α | В   | D   | G |

Caution: The shown common/select definition can not be modified and any display chosen to be used with the TSS400-S1 must conform to it.

The chosen common/select configuration is designed to be fail safe. This means that no valid numbers or characters are displayed when a segment or common signal failure occurs. Instead meaningless segment combinations are displayed that cannot be mistaken as valid data.

The TSS400-S1 LCD driver contains a gate-level output PLA (OPLA) that is of a  $64 \times 7$  bit configuration. The 7 bits represent the segment information A through G for 64 predefined combinations (the H segment is independent from the OPLA and is given with the display instructions). Each of the predefined characters can be used with the display command. Table 7 gives the segments displayed and the character for each.

**Table 7. Segment Display and Character**

| CHARACTER<br>NUMBER | SEGMENTS   | CHARACTER | DISPLAYED<br>SEGMENTS |

|---------------------|------------|-----------|-----------------------|

| 0                   | ABCDEF     | 0 or O    | 0                     |

| 1                   | ВС         | 1 or      | 1                     |

| 2                   | ABDEG      | 2         | 2                     |

| 3                   | ABCDG      | 3         | 3                     |

| 4                   | BCFG       | 4         | 4                     |

| 5                   | ACDFG      | 5 or S    | 5                     |

| 6                   | ACDEFG     | 6         | 6                     |

| 7                   | ABC        | 7         | ٦                     |

| 8                   | ABCDEFG    | 8 or B    | 8                     |

| 9                   | ABCDFG     | 9         | 9                     |

| 10                  | ABCEFG     | A or R    | R                     |

| 11                  | CDEFG      | b         | Ь                     |

| 12                  | ADEF       | C or [    | ם -                   |

| 13                  | BCDEG      | d         | E                     |

| 14                  | ADEFG E    |           |                       |

| 15                  | AEFG       | F         | F                     |

| 16                  | None       | Blank     |                       |

| 17                  | BCD        | J         | ١-                    |

| 18                  | DEF L      |           | L                     |

| 19                  | ABEFG      | Р         | P                     |

| 20                  | 20 BCDEF U |           | U                     |

| 21                  | DEG        | С         | _                     |

| 22                  | CEFG       | h         | h                     |

| 23                  | DE         | I         | L                     |

| 24                  | CEG        | n         | С                     |

| 25                  | CDEG       | 0         | 0                     |

| 26                  | EG         | r         | ٦                     |

| 27                  | DEFG       | t         | Т                     |

| 28                  | CDE        | V         | U                     |

**Table 7. Segment Display and Character (Continued)**

| CHARACTER<br>NUMBER | SEGMENTS | CHARACTER  | DISPLAYED<br>SEGMENTS |

|---------------------|----------|------------|-----------------------|

| 29                  | BCDFG    | Y          | 7                     |

| 30                  | BCEFG    | Н          | X                     |

| 31                  | BCG      | -1         | 7                     |

| 32                  | None     | Blank      |                       |

| 33                  | Α        |            | _                     |

| 34                  | F        |            | 1                     |

| 35                  | AF       |            | ٦                     |

| 36                  | В        |            | '                     |

| 37                  | АВ       |            | ٦                     |

| 38                  | BF       |            | 11                    |

| 39                  | ABF      |            | О                     |

| 40                  | G        | Minus Sign | -                     |

| 41                  | A G      |            | -                     |

| 42                  | FG       |            | L                     |

| 43                  | AFG      |            | C                     |

| 44                  | BG       |            | ٦                     |

| 45                  | ABG      |            |                       |

| 46                  | BFG      |            | U                     |

| 47                  | ABFG     | Degree     | 0                     |

| 48                  | E        |            | ı                     |

| 49                  | ΑE       |            | -                     |

| 50                  | EF       |            | - 1                   |

| 51                  | AEF      |            | ۲                     |

| 52                  | ВE       |            | , '                   |

| 53                  | ABE      |            | ٦-                    |

| 54                  | BEF      |            | '                     |

| 55                  | ABEF     |            | Ĺ                     |

| 56                  | EG       |            | ١                     |

| 57                  | AEG      |            | ال                    |

| 58                  | EFG      |            | Τ                     |

| 59                  | AEFG     | F          | Ļ                     |

| 60                  | С        |            | ı                     |

| 61                  | D        |            | _                     |

| 62                  | ABCD     | ]          |                       |

| 63                  | ABCDE    | J          | ני                    |

# TSS400-S1 μPOWER PROGRAMMABLE HIGH-PRECISION SENSOR SIGNAL PROCESSOR

SLMS001 - D4071, JANUARY 1993

### sensor macro programming language (SMPL)

The TSS400-S1 features a processor that is programmed with an easy-to-use macro language, SMPL. The internal ROM is pre-programmed with optimized calibration, display, A/D conversion routines, the SMPL macro interpreter, and EEPROM communications protocol. The TSS400-S1 SMPL language is an optimized 75-instruction language that is much easier to use than assembly language. Each SMPL instruction is equivalent, on average, to six or seven assembly language instructions. This greatly reduces the amount of memory space required to store a given program and eases programming tasks.

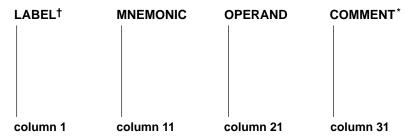

#### SMPL interpreter instruction coding format

The following rules should be followed in writing a program:

- Label fields are a maximum of eight alphanumeric characters starting with an alphabetic character. The label field must begin in column one.

- The mnemonic is to the right of a label, separated by at least one blank space. If no label is used, the mnemonic begins after the first column (second column or further right).

- The operand is to the right of the mnemonic and separated by at least one blank.

- A comment is to the right of the operand and separated by at least one blank. If a comment occupies a separate line, it must begin with an asterisk (\*) in column one.

For legibility, it is recommended that fields begin in the following columns:

- label fields must begin in column 1

- mnemonic should begin in column 11

- operands should begin in column 21

- comments to an instruction should begin in column 31

- full line comments must begin with an asterisk (\*) in column 1

† Labels are 8 characters, max, and must start in column 1.

\* Asterisk in column 1 reserves the entire line for a comment.

Table 8 lists the SMPL language programming instructions in each of the following major categories:

- Register-to-register instructions

- Arithmetic instructions

- Arithmetic compare instructions

- Bit manipulation instructions

- Counter instructions

- Display instructions

- Miscellaneous instructions

- Constant transfer instructions

- Timer instructions

- Input/output instructions

- Program flow control instructions

- A/D conversion instructions

# TSS400-S1 μPOWER PROGRAMMABLE HIGH-PRECISION SENSOR SIGNAL PROCESSOR SLMS001 – D4071, JANUARY 1993

## **Table 8. SMPL Programming Instructions**

| FUNCTION GROUP                   | SMPL INSTR | UCTION | DESCRIPTION                                                                                         |

|----------------------------------|------------|--------|-----------------------------------------------------------------------------------------------------|

|                                  | MOVFLSTO   | n      | Move FLAC to storage register n                                                                     |

|                                  | MOVSTOFL   | n      | Move storage register n to FLAC                                                                     |

|                                  | MOVRBSTO   | n      | Move REGB to storage register n                                                                     |

|                                  | MOVSTORB   | n      | Move storage register n to REGB                                                                     |

| Register-to-Register<br>Transfer | EXCHRBFL   |        | Exchange REGB and FLAC registers                                                                    |

| Transier                         | MOVFLRB    |        | Move FLAC register to REGB register                                                                 |

|                                  | MOVRBFL    |        | Move REGB register to FLAC register                                                                 |

|                                  | MOVFLPRM   | label  | Move FLAC to EEPROM starting at address label                                                       |

|                                  | MOVPRMRB   | label  | Move EEPROM contents starting at address label to REGB                                              |

|                                  | ADD        |        | Add REGB to FLAC decimally                                                                          |

|                                  | SUB        |        | Subtract REGB from FLAC decimally                                                                   |

|                                  | MPY        |        | Multiply FLAC and REGB decimally                                                                    |

|                                  | DIV        |        | Divide FLAC by REGB decimally                                                                       |

|                                  | ADDH       |        | Add REGB to FLAC hexadecimally                                                                      |

| Arithmetic                       | SUBH       |        | Subtract REGB from FLAC hexadecimally                                                               |

|                                  | HEXDEC     |        | Hexadecimal to decimal conversion                                                                   |

|                                  | ROUND n    |        | Round FLAC n times (0 <n<5)< td=""></n<5)<>                                                         |

|                                  | SHIFTR n   |        | Shift right FLAC n times (0 <n<3)< td=""></n<3)<>                                                   |

|                                  | SHIFTL n   |        | Shift left FLAC n times (0 <n<3)< td=""></n<3)<>                                                    |

|                                  | CMPFLRB    |        | Compare FLAC and REGB then set status flags                                                         |

| Arithmetic Compare               | TSTRB      |        | Test contents of REGB then set status flags                                                         |

|                                  | SBIT       | n      | Set flag bit n $(0 \le n < 16)$                                                                     |

|                                  | RBIT       | n      | Reset flag bit n $(0 \le n < 16)$                                                                   |

|                                  | TBIT       | n      | Test flag bit (0 ≤ n<16)                                                                            |

| Bit Manipulation                 | SELGRP n   |        | Select flag bits group n (0 <n<3)< td=""></n<3)<>                                                   |

|                                  | OR         |        | Logical OR FLAC and REGB with result to FLAC                                                        |

|                                  | AND        |        | Logical AND FLAC and REGB with result to FLAC                                                       |

|                                  | DECCNT n   |        | Decrement counter n decimally                                                                       |

|                                  | INCCNT n   |        | Increment counter n decimally                                                                       |

|                                  | DECDBL     |        | Decrement double counter decimally                                                                  |

| Counter                          | INCDBL     |        | Increment double counter decimally                                                                  |

|                                  | LDCNT n    | >NN    | Load counter n decimally with constant >NN                                                          |

|                                  | MOVCNT n   |        | Move counter n to REGB                                                                              |

|                                  | MOVDBL     |        | Move combined counters to REGB                                                                      |

|                                  | DISPLDG n  | >NN    | Display information of operand NN in digit n                                                        |

| Dianloy                          | DISPLCLR   |        | Clear display                                                                                       |

| Display                          | DISPLFL    | >MN    | Display FLAC from digit M to digit N and append (M–N+1) bytes containing information for each digit |

|                                  | DONE       |        | Enter DONE mode                                                                                     |

|                                  | OFF        |        | Enter OFF mode                                                                                      |

| Miscellaneous                    | NOP        |        | No operation                                                                                        |

|                                  | SLV        | >NN    | Host control instruction                                                                            |

# TSS400-S1 μPOWER PROGRAMMABLE HIGH-PRECISION SENSOR SIGNAL PROCESSOR SLMS001 - D4071, JANUARY 1993

## **Table 8. SMPL Programming Instructions (Continued)**

| FUNCTION GROUP       | SMPL INSTR | UCTION | DESCRIPTION                                                                                          |  |  |  |  |

|----------------------|------------|--------|------------------------------------------------------------------------------------------------------|--|--|--|--|

|                      | LDFLPOS    | n      | Load FLAC with a positive constant (BCD format) contained in the n following bytes (n = 0 : 4 Bytes) |  |  |  |  |

|                      | LDFLNEG    | n      | Load FLAC with a negative constant (BCD format) contained in the n following bytes (n = 0 : 4 Bytes) |  |  |  |  |

| Constant Transfer    | LDRBPOS    | n      | Load REGB with a positive constant (BCD format) contained in the n following bytes (n = 0 : 4 Bytes) |  |  |  |  |

|                      | LDRBNEG    | n      | Load REGB with a negative constant (BCD format) contained in the n following bytes (n = 0 : 4 Bytes) |  |  |  |  |

|                      | CLRFL      |        | Clear FLAC register                                                                                  |  |  |  |  |

|                      | CLRRB      |        | Clear REGB                                                                                           |  |  |  |  |

|                      | LDTIML     | NNN    | Load long timer with constant NNN                                                                    |  |  |  |  |

|                      | LDTIMS     | NNN    | Load short timer with constant NNN                                                                   |  |  |  |  |

| Timer                | ACTTIM     |        | Actualize timers                                                                                     |  |  |  |  |

|                      | STPTIML    |        | Stop long timer                                                                                      |  |  |  |  |

|                      | STPTIMS    |        | Stop short timer                                                                                     |  |  |  |  |

|                      | SETR       | n      | Set output Rn (DLn)                                                                                  |  |  |  |  |

|                      | RSTR       | n      | Reset output Rn (DLn)                                                                                |  |  |  |  |

|                      | TSTKEY     | >NN    | Test keyboard like described by operand                                                              |  |  |  |  |

| Input/Output         | KINTIM     |        | Actualize K input and timers                                                                         |  |  |  |  |

|                      | KIN        |        | Read K inputs to FLAC (LSD) and FLAG 12 thru 15                                                      |  |  |  |  |

|                      | FLKOUT     |        | Output LSD of FLAC to K lines                                                                        |  |  |  |  |

|                      | KOUT       | n      | Output constant n to K lines                                                                         |  |  |  |  |

|                      | JMP        | label  | Jump to label unconditionally                                                                        |  |  |  |  |

|                      | JZ         | label  | Jump to label if zero (STATUS BIT ZERO = 1)                                                          |  |  |  |  |

|                      | JEQ        | label  | Jump to label if equal (STATUS BIT ZERO = 1)                                                         |  |  |  |  |

|                      | JNZ        | label  | Jump to label if not zero (STATUS BIT ZERO = 0)                                                      |  |  |  |  |

| Program Flow Control | JNE        | label  | Jump to label if not equal (STATUS BIT ZERO = 0)                                                     |  |  |  |  |

|                      | JP         | label  | Jump to label if positive (STATUS BIT POS = 1)                                                       |  |  |  |  |

|                      | JN         | label  | Jump to label if negative (STATUS BIT NEG = 1)                                                       |  |  |  |  |

|                      | CALL       | label  | Call subroutine label                                                                                |  |  |  |  |

|                      | RETN       |        | Return from subroutine                                                                               |  |  |  |  |

|                      | SVDDON     |        | Set converter supply voltage                                                                         |  |  |  |  |

|                      | SVDDOFF    |        | Reset converter supply voltage                                                                       |  |  |  |  |

|                      | MEASR      | а      | Measure addressed A/D input a+1 and following byte contains number of conversions and mode           |  |  |  |  |

| A/D Conversion       | ADJBATT    |        | Measure battery voltage and put result in FLAC                                                       |  |  |  |  |

|                      | CHKBATT    |        | Check battery voltage                                                                                |  |  |  |  |

|                      | ADJCOMP    |        | Measure A/D input and put result in FLAC                                                             |  |  |  |  |

|                      | CHKCOMP    |        | Compare A/D input with value in FLAC                                                                 |  |  |  |  |

|                      |            |        | · · · · · · · · · · · · · · · · · · ·                                                                |  |  |  |  |

# TSS400-S1 μPOWER PROGRAMMABLE HIGH-PRECISION SENSOR SIGNAL PROCESSOR SLMS001 – D4071, JANUARY 1993

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>DD</sub> (see Note 1) | 0.3 V to 7 V                                        |

|----------------------------------------------------|-----------------------------------------------------|

| Input voltage range, V <sub>I</sub>                | $V_{SS} = 0.3 \text{ V to } V_{DD} + 0.3 \text{ V}$ |

| Diode current                                      | ±2 mA                                               |

| Operating free-air temperature range, TA: TS       | SS400CFN-S1 0°C to 70°C                             |

| TS                                                 | SS400AFN-S1 –40°C to 125°C                          |

| Storage temperature range                          | –50°C to 150°C                                      |

| STE 4. The contract of the first section of the M  |                                                     |

NOTE 1: The voltage value is measured with respect to VSS.

## recommended operating conditions

|                                                |              | MIN | NOM    | MAX | UNIT |

|------------------------------------------------|--------------|-----|--------|-----|------|

| Supply voltage, V <sub>DD</sub>                |              | 2.6 |        | 5.5 | V    |

| Supply voltage, V <sub>SS</sub>                |              | 0   |        | 0   | V    |

| Timer frequency (XTAL)                         |              |     | 32.768 |     | kHz  |

| Operating free-air temperature, T <sub>A</sub> | TSS400CFN-S1 | 0   |        | 70  | °C   |

| Operating nee-an temperature, 14               | TSS400AFN-S1 | -40 |        | 125 | °C   |

# electrical characteristics, $T_A = 0$ °C to 70°C

## total device supply current

|             | PARAMETER     |                   | TEST CONDITIONS       | MIN | TYP | MAX  | UNIT |  |

|-------------|---------------|-------------------|-----------------------|-----|-----|------|------|--|

|             |               | With              | $V_{DD} = 3 V$        |     | 300 | 500  |      |  |

|             | ACTIVE mode   | A/D†              | $V_{DD} = 5 V$        |     | 800 | 1100 | μΑ   |  |

| IDD(ACTIVE) | ACTIVE IIIode | Without           | V <sub>DD</sub> = 3 V |     | 80  | 140  |      |  |

|             |               | A/D†              | $V_{DD} = 5 V$        |     | 400 | 500  | μΑ   |  |

|             | DONE made     | C4 a m alla cat   | $V_{DD} = 3 V$        |     | 4   | 8    |      |  |

| IDD(DONE)   | DONE mode     | Standby†          | V <sub>DD</sub> = 5 V |     | 10  | 18   | μΑ   |  |

| lan (0==)   | OFF mode      | Halt <sup>†</sup> | $V_{DD} = 3 V$        |     | 0.1 | 1    | μА   |  |

| IDD(OFF)    | OFF mode      | Tiaiti            | V <sub>DD</sub> = 5 V |     | 0.1 | 1    | μΑ   |  |

<sup>†</sup> Current values are for input levels in the range of 0 to 0.3 V for  $V_{KL}$ ,  $V_{IOL}$ ; and  $V_{DD} = 0.3$  V for  $V_{KH}$ ,  $V_{IOH}$  (all outputs open).

## K and I/O inputs (schmitt trigger)

| PARAMETER        |                                           | TEST CO                   | TEST CONDITIONS    |      | MAX | UNIT |

|------------------|-------------------------------------------|---------------------------|--------------------|------|-----|------|

| \/_              | Desitive gaing threehold valtege          | V <sub>DD</sub> = 3 V     |                    | 1.2  | 2.0 |      |

| V <sub>T+</sub>  | Positive-going threshold voltage          | $V_{DD} = 5 V$            |                    | 2.2  | 3.8 | V    |

| \/_              | No matical main at the scale and contains | V <sub>DD</sub> = 3 V     |                    | 0.8  | 1.5 | V    |

| V <sub>T</sub> – | Negative-going threshold voltage          | $V_{DD} = 5 V$            |                    | 1.2  | 2.6 |      |

|                  |                                           | $V_{DD} = 3.8 \text{ V},$ | V <sub>I</sub> = 0 | -0.1 | 0.1 |      |

| 1.               | Input current                             | $V_{DD} = 5.5 V$          | $V_{IN} = 0$       | -0.1 | 0.1 | μA   |

| 11               | ij input current                          | $V_{DD} = 3.8 \text{ V},$ | $V_{IN} = V_{DD}$  | -0.1 | 0.1 | μΑ   |

|                  |                                           | $V_{DD} = 5.5 \text{ V},$ | VIN = VDD          | -0.1 | 0.1 |      |

## K outputs

| PARAMETER                     |                               | TEST CO                    | MIN                        | MAX                   | UNIT     |   |

|-------------------------------|-------------------------------|----------------------------|----------------------------|-----------------------|----------|---|

| VOH High-level output voltage | $V_{DD} = 3 V$ ,              | $I_{OH} = -0.1 \text{ mA}$ | V <sub>DD</sub> – 0.2      | $V_{DD}$              | V        |   |

| VOH                           | H Tilgit level output voltage | $V_{DD} = 5 V$ ,           | $I_{OH} = -0.5 \text{ mA}$ | V <sub>DD</sub> – 0.6 | $V_{DD}$ | V |

# TSS400-S1 μPOWER PROGRAMMABLE HIGH-PRECISION SENSOR SIGNAL PROCESSOR

SLMS001 - D4071, JANUARY 1993

# electrical characteristics, $T_A = 0$ °C to 70°C (continued)

# I/O output

|      | PARAMETER                 | T                | EST CONDITIONS              | MIN                  | MAX                   | UNIT |

|------|---------------------------|------------------|-----------------------------|----------------------|-----------------------|------|

| Vall | High lovel output voltage | $V_{DD} = 3 V$ , | $I_{OH} = -0.1 \text{ mA}$  | V <sub>DD</sub> −0.2 | $V_{DD}$              | V    |

| VOH  | High-level output voltage | $V_{DD} = 5 V$ , | $I_{OH} = -0.75 \text{ mA}$ | V <sub>DD</sub> −0.2 | $V_{DD}$              | V    |

| VOL  | Low-level output voltage  | $V_{DD} = 3 V$ , | $I_{OL}$ = 0.5 mA           | VSS                  | V <sub>SS</sub> + 0.4 | V    |

| VOL  | Low-level output voltage  | $V_{DD} = 5 V$ , | I <sub>OL</sub> = 1 mA      | V <sub>SS</sub>      | V <sub>SS</sub> +0.4  | V    |

## R outputs

| PARAMETER                        | TEST CONDITIONS                                         | MIN                  | MAX      | UNIT |

|----------------------------------|---------------------------------------------------------|----------------------|----------|------|

|                                  | $V_{DD} = 3 \text{ V}, \qquad I_{OH} = -0.1 \text{ mA}$ | V <sub>DD</sub> -0.2 | $V_{DD}$ |      |

| VOH(R) High-level output voltage | $V_{DD} = 3 \text{ V}, \qquad I_{OH} = -0.3 \text{ mA}$ | V <sub>DD</sub> -0.6 | $V_{DD}$ | V    |

|                                  | $V_{DD} = 5 \text{ V}, \qquad I_{OH} = -0.3 \text{ mA}$ | V <sub>DD</sub> -0.4 | $V_{DD}$ |      |

| VOL(R) Low-level output voltage  | $V_{DD} = 3 \text{ V}, \qquad I_{OL} = 0.3 \text{ mA}$  | V <sub>SS</sub> V    | SS +0.4  | V    |

| VOL(R) Low-level output voltage  | $V_{DD} = 5 \text{ V}, \qquad I_{OL} = 0.3 \text{ mA}$  | V <sub>SS</sub> V    | SS +0.4  | , v  |

## **INITN** input

| PARAMETER                                   | TEST CONI                                   | MIN                | MAX  | UNIT |    |

|---------------------------------------------|---------------------------------------------|--------------------|------|------|----|

|                                             | $V_{DD} = 3 V$ ,                            | V <sub>I</sub> = 0 | -0.2 | -1   |    |

| I <sub>I</sub> (INITN) Input current, INITN | $V_{DD} = 5 V$ ,                            | V <sub>I</sub> = 0 | -0.5 | -2.2 | μΑ |

|                                             | $V_{DD} = 3.8 \text{ V to } 5.5 \text{ V},$ | $V_I = V_{DD}$     | -0.1 | 0.1  |    |

# ${\rm SV}_{\rm DD}$ output

| PARAMETER                                | TEST CONDIT                                 | MIN                         | MAX                  | UNIT     |    |

|------------------------------------------|---------------------------------------------|-----------------------------|----------------------|----------|----|

| Output voltage awitched Von              | $V_{DD} = 2.6 V,$                           | $I_{SVDD} = 2 \text{ mA}$   | V <sub>DD</sub> -0.2 | $V_{DD}$ | V  |

| Output voltage, switched V <sub>DD</sub> | $V_{DD} = 2.6 V,$                           | $I_{SVDD} = 6.5 \text{ mA}$ | V <sub>DD</sub> -0.3 | $V_{DD}$ | V  |

| Output current, switched V <sub>DD</sub> | $V_{DD} = 3.8 \text{ V to } 5.5 \text{ V},$ | SV <sub>DD</sub> off (0 V)  | -0.1                 | 0.1      | μΑ |

## LCD lines common, segment (1/4 duty cycle)

|                                      | PARAMETER                                 | TEST C                 | CONDITIONS                   | MIN                            | TYP                   | MAX                            | UNIT |

|--------------------------------------|-------------------------------------------|------------------------|------------------------------|--------------------------------|-----------------------|--------------------------------|------|

| V211/2218                            | High-level output voltage (COM1 – COM4)   | $V_{DD} = 3 V$ ,       | I <sub>OH</sub> = -50 μA     | V <sub>DD</sub> −0.4           |                       | $V_{DD}$                       | V    |

| VOH(COM)                             | Tilgri-level output voltage (COWT = COW4) | $V_{DD} = 5 V$ ,       | $I_{OH} = -100  \mu A$       | V <sub>DD</sub> −0.4           |                       | $V_{DD}$                       | V    |

|                                      | Output voltage, 2/3-Hz (COM1 – COM4)      |                        | $I_{OZ} = \pm 10 \text{ nA}$ | (2/3) V <sub>DD</sub><br>-0.04 | (2/3) V <sub>DD</sub> | (2/3) V <sub>DD</sub><br>+0.04 | V    |

|                                      |                                           |                        | $I_{OZ} = \pm 10 \text{ nA}$ | (2/3) V <sub>DD</sub><br>-0.04 | (2/3) V <sub>DD</sub> | (2/3) V <sub>DD</sub><br>+0.04 | V    |

|                                      | Output voltage 1/2 Hz (COM1 COM4)         | V <sub>DD</sub> = 3 V, | $I_{OZ} = \pm 10 \text{ nA}$ | (1/3) V <sub>DD</sub><br>-0.04 | (1/3) V <sub>DD</sub> | (1/3) V <sub>DD</sub><br>+0.04 | V    |

| Output voltage, 1/3-Hz (COM1 – COM4) |                                           | V <sub>DD</sub> = 5 V, | $I_{OZ} = \pm 10 \text{ nA}$ | (1/3) V <sub>DD</sub><br>-0.04 | (1/3) V <sub>DD</sub> | (1/3) V <sub>DD</sub><br>+0.04 | V    |

| Vol.(com)                            | Low-level output voltage (COM1 – COM4)    | $V_{DD} = 3 V$ ,       | I <sub>OL</sub> = 50 μA      | VSS                            |                       | V <sub>SS</sub> +0.4           | V    |

| VOL(COM)                             | 2011 10101 001.put 101.ugo (00111 001114) | $V_{DD} = 5 V$ ,       | I <sub>OL</sub> = 100 μA     | $V_{SS}$                       |                       | V <sub>SS</sub> +0.4           | ľ    |

# electrical characteristics, $T_A = 0$ °C to 70°C (continued)

# ADC current source, V<sub>Rext</sub> = V<sub>SVDD</sub> - V<sub>Ri</sub> (unless otherwise noted)

|                       | PARAMETER                        | TE                       | ST CONDITIONS             | 3                     | MIN                            | TYP                            | MAX                            | UNIT   |

|-----------------------|----------------------------------|--------------------------|---------------------------|-----------------------|--------------------------------|--------------------------------|--------------------------------|--------|

| \/ <b>-</b>           | Voltage (across                  | V <sub>DD</sub> = 3.5 V, | I <sub>Ri</sub> = 1.3 mA, | T <sub>A</sub> = 25°C | 0.240737<br>× SV <sub>DD</sub> | 0.244403<br>× SV <sub>DD</sub> | 0.248069<br>× SV <sub>DD</sub> | V      |

| VRext                 | programming resistor)†           | V <sub>DD</sub> = 5 V,   | I <sub>Ri</sub> = 1.3 mA, | T <sub>A</sub> = 25°C | 0.241959<br>× SV <sub>DD</sub> | 0.244403<br>× SV <sub>DD</sub> | 0.246847<br>× SV <sub>DD</sub> | V      |

| ь.                    | External programming             | $V_{DD} = 3.5 V,$        |                           | T <sub>A</sub> = 25°C | 0.10                           |                                | 1.6                            | kΩ     |

| R <sub>ext</sub>      | resistor                         | $V_{DD} = 5 V$ ,         |                           | T <sub>A</sub> = 25°C | 0.10                           |                                | 1.6                            | K22    |

| dN/dT                 | Tomporature atability            | $V_{DD} = 5 V$ ,         | V <sub>Rext</sub> /R      | ext = 1.3 mA          |                                | 0.03                           |                                | LSB/°C |

| div/d i               | Temperature stability            | $V_{DD} = 5 V$ ,         | V <sub>Rext</sub> /R      | ext = 1.3 mA          |                                | 0.06                           |                                | LSB/ C |

| dN/dSV <sub>DD</sub>  | SV <sub>DD</sub> rejection ratio | $V_{DD} = 5 V$ ,         |                           | T <sub>A</sub> = 25°C | -3                             | -1.5                           | 1                              | LSB/V  |

| art/dev <sub>DD</sub> | GVDD rejection ratio             | $V_{DD} = 5 V$           |                           | T <sub>A</sub> = 25°C | -6                             | -3                             | 2                              | LOD/ V |

#### **ADC**

| PARAMETER       |                                                    | TEST CONDITIONS <sup>‡</sup> |                       | MIN                            | TYP                            | MAX                            | UNIT |  |

|-----------------|----------------------------------------------------|------------------------------|-----------------------|--------------------------------|--------------------------------|--------------------------------|------|--|

| I <sub>IB</sub> | Input bias current (all inputs) <sup>†</sup>       | $V_I = V_{SS}$ to $V_{DD}$ , | Current source off    |                                |                                | ±30                            | nA   |  |

| VIH             | High-level analog input voltage for A/D conversion | V <sub>DD</sub> = 3.5 V,     | N = EB9 <sub>16</sub> | 0.486055<br>× SV <sub>DD</sub> | 0.487977<br>× SV <sub>DD</sub> | 0.489899<br>× SV <sub>DD</sub> | V    |  |

|                 |                                                    | V <sub>DD</sub> = 5 V,       | N = FD4 <sub>16</sub> | 0.488649<br>× SV <sub>DD</sub> | 0.490571<br>× SV <sub>DD</sub> | 0.492493<br>× SV <sub>DD</sub> | V    |  |

| VIL             | Low-level analog input voltage for A/D conversion  | V <sub>DD</sub> = 3.5 V,     | N = 046 <sub>16</sub> | 0.106017<br>× SV <sub>DD</sub> | 0.107939<br>× SV <sub>DD</sub> | 0.109861<br>× SV <sub>DD</sub> | V    |  |

|                 |                                                    | V <sub>DD</sub> = 5 V,       | $N = 02B_{16}$        | 0.103423<br>× SV <sub>DD</sub> | 0.105345<br>× SV <sub>DD</sub> | 0.107267<br>× SV <sub>DD</sub> | V    |  |

<sup>†</sup> This range is available only for V<sub>DD</sub> ≥ 3.5 V. The A/D range is limited due to the offset of the comparator. The range can be larger, if the comparator offset is made smaller.

# operating characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                |                                      |                                  | TEST CONDITIO                                                             | NS                     | MIN  | TYP | MAX | UNIT |  |

|--------------------------|--------------------------------------|----------------------------------|---------------------------------------------------------------------------|------------------------|------|-----|-----|------|--|

|                          |                                      |                                  | V <sub>DD</sub> = 3 V, Delta digital value ≤ 120 LSB                      |                        | -1   |     | 1   |      |  |

|                          |                                      |                                  | V <sub>DD</sub> = 3 V, 120 LSB < DDV ≤ 240 LSB                            |                        | -1.5 |     | 1.5 | LSB  |  |

| Linearity for all ranges |                                      |                                  | $V_{DD} = 3 \text{ V}, 240 \text{ LSB} < \text{DDV} \le 2600 \text{ LSB}$ |                        | -2.5 |     | 2.5 | LSB  |  |

|                          |                                      |                                  | V <sub>DD</sub> = 3 V, DDV > 2600 LSB                                     |                        | -4.5 |     | 4.5 |      |  |

|                          |                                      |                                  | V <sub>DD</sub> = 5 V, Delta digital value ≤ 120 LSB                      |                        | -1   |     | 1   |      |  |

|                          |                                      |                                  | V <sub>DD</sub> = 5 V, 120 LSB < DDV                                      | ′ ≤ 240 LSB            | -1.5 |     | 1.5 | LSB  |  |

|                          |                                      |                                  | V <sub>DD</sub> = 5 V, 240 LSB < DDV ≤ 2600 LSB                           |                        | -2.5 |     | 2.5 | LSB  |  |

|                          |                                      |                                  | V <sub>DD</sub> = 5 V, DDV > 2600 LSB                                     |                        | -4.5 |     | 4.5 |      |  |

| V <sub>DD(BC)</sub>      | DD(BC) Supply voltage, battery check |                                  | 000 <sub>16</sub> < conversion result > FFF <sub>16</sub>                 |                        |      |     | 4.8 | V    |  |

|                          | Drift                                |                                  | N of ADC at $V_{DD} = 2.7 \text{ V}$ ,                                    | $T_A = 25^{\circ}C$    | -0.1 | 2.7 | 0.1 | V    |  |

|                          | Clock frequency, internal MOS        |                                  | $V_{DD} = 3 V$ ,                                                          | T <sub>A</sub> = 25 °C |      | 650 |     | kHz  |  |

|                          |                                      |                                  | $V_{DD} = 5 V$ ,                                                          | T <sub>A</sub> = 25 °C |      | 840 |     | KITZ |  |

| t <sub>conv</sub>        | Conversion time                      | Single-compensated measurement   | V <sub>DD</sub> = 3.5 V                                                   |                        |      | 1.2 |     | ms   |  |

|                          |                                      | Single-uncompensated measurement | V <sub>DD</sub> = 3.5 V                                                   |                        |      | 1   |     |      |  |

|                          |                                      | ADJCOMP                          | V <sub>DD</sub> = 3.5 V                                                   |                        |      | 1   |     |      |  |

<sup>‡</sup> N = A/D conversion result for a single measurement. See measurement range and conversion formulas.

#### **APPLICATION INFORMATION**

Figure 5 shows all the components that are necessary to run a TSS400-S1 and the connected sensors for a temperature-calibrated pressure application. In this case, a 3-V lithium battery is used as a power supply. The pressure application could be an altimeter, a pressure gauge, or a manometer. This example uses simple uncalibrated silicon sensors. It is assumed that a simple, easy to perform software calibration routine is used to get accurate results. This temperature-compensation software calibration and the 12-bit ADC ensures a high degree of accuracy can be realized with this application.

All of the analog circuitry in Figure 5 is connected to the  $SV_{DD}$  (switchable  $V_{DD}$ ) terminal. By doing this, the sensor network is only powered when it is needed for A/D conversion. This is done to reduce total system power consumption.

Figure 5. Temperature-Compensated Pressure Application

#### **APPLICATION INFORMATION**

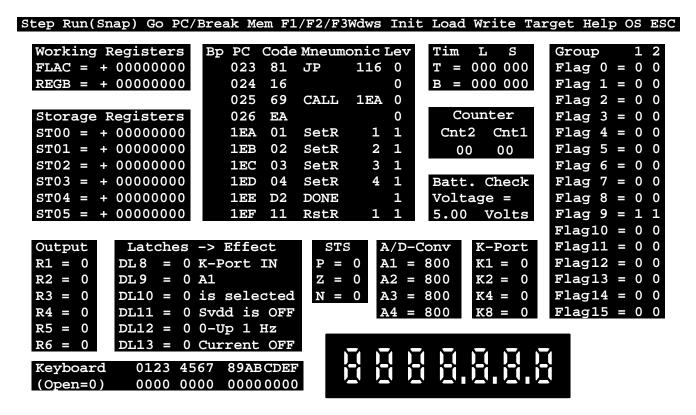

## SDT-400 development tool

The SDT-400 is an inexpensive software development tool used for development of TSS400-S1 applications. It consists of three basic parts: