# 56F8365/56F8165

**Data Sheet**

Preliminary Technical Data

**56F8300 16-bit Digital Signal Controllers**

MC56F8365 Rev. 7 01/2007

## **Document Revision History**

| Version History | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 0           | Pre-release, Alpha customers only                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Rev 1.0         | Initial Public Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Rev 2.0         | Added output voltage maximum value and note to clarify in <b>Table 10-1</b> ; also removed overall life expectancy note, since life expectancy is dependent on customer usage and must be determined by reliability engineering. Clarified value and unit measure for Maximum allowed P <sub>D</sub> in <b>Table 10-3</b> . Corrected note about average value for Flash Data Retention in <b>Table 10-4</b> . Added new RoHS-compliant orderable part numbers in <b>Table 13-1</b> . |

| Rev 3.0         | Corrected Data Flash on page 5                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Rev 4.0         | Deleted RSTO from Pin Group 2 (listed after <b>Table 10-1</b> ). Deleted formula for Max Ambient Operating Temperature (Automotive) and Max Ambient Operating Temperature (Industrial) in <b>Table 10-4</b> . Added RoHS-compliance and "pb-free" language to back cover.                                                                                                                                                                                                             |

| Rev 5.0         | Added information/corrected state during reset in <b>Table 2-2</b> . Clarified external reference crystal frequency for PLL in <b>Table 10-14</b> by increasing maximum value to 8.4MHz.                                                                                                                                                                                                                                                                                              |

| Rev 6.0         | Replaced "Tri-stated" with an explanation in State During Reset column in Table 2-2.                                                                                                                                                                                                                                                                                                                                                                                                  |

| Rev. 7          | <ul> <li>Added the following note to the description of the TMS signal in Table 2-2: Note: Always tie the TMS pin to V<sub>DD</sub> through a 2.2K resistor. </li> <li>Added the following note to the description of the TRST signal in Table 2-2: Note: For normal operation, connect TRST directly to V<sub>SS</sub>. If the design is to be used in a debugging environment, TRST may be tied to V<sub>SS</sub> through a 1K resistor. </li> </ul>                                |

Please see http://www.freescale.com for the most current data sheet revision.

# 56F8365/56F8165 General Description

**Note:** Features in italics are NOT available in the 56F8165 device.

- Up to 60 MIPS at 60MHz core frequency

- DSP and MCU functionality in a unified, C-efficient architecture

- · 512KB Program Flash

- 4KB Program RAM

- 32KB Data Flash

- 32KB Data RAM

- · 32KB Boot Flash

- Up to two 6-channel PWM modules

- Four 4-channel, 12-bit ADCs

- Temperature Sensor

- Up to two Quadrature Decoders

- Up to two FlexCAN modules

- Optional On-Chip Regulator

- Two Serial Communication Interfaces (SCIs)

- Up to two Serial Peripheral Interface (SPIs)

- Up to four general-purpose Quad Timers

- Computer Operating Properly (COP)/Watchdog

- JTAG/Enhanced On-Chip Emulation (OnCE<sup>TM</sup>) for unobtrusive, real-time debugging

- Up to 49 GPIO lines

- 128-pin LQFP Package

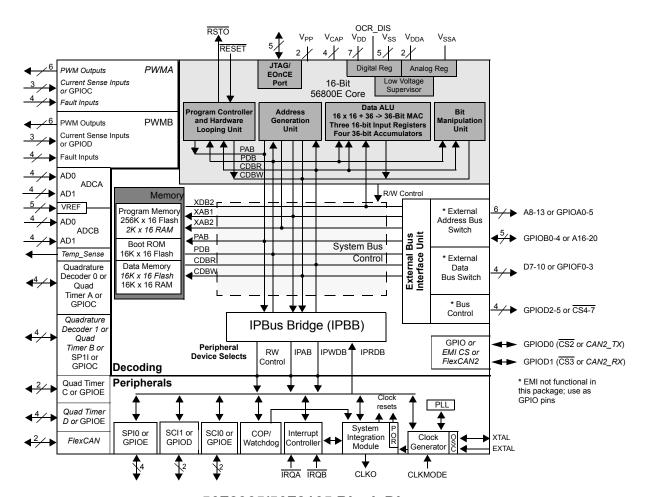

56F8365/56F8165 Block Diagram

# **Table of Contents**

| Part 1: Overview 5                           | Part 8: General Purpose Input/Output              |

|----------------------------------------------|---------------------------------------------------|

| 1.1. 56F8365/56F8165 Features 5              | (GPIO)                                            |

| 1.2. Device Description                      | 8.1. Introduction                                 |

| 1.3. Award-Winning Development Environment 9 | 8.2. Memory Maps                                  |

| 1.4. Architecture Block Diagram 10           | 8.3. Configuration                                |

| 1.5. Product Documentation                   | · ·                                               |

| 1.6. Data Sheet Conventions                  | Part 9: Joint Test Action Group (JTAG) 138        |

| D (0.0) 1/0 (1. D ) (1. AF                   | 9.1. JTAG Information                             |

| Part 2: Signal/Connection Descriptions 15    |                                                   |

| 2.1. Introduction                            | Part 10: Specifications                           |

| 2.2. Signal Pins                             | 10.1. General Characteristics                     |

| D ( 0 0 0); 01 10 (1 ; (0000) 0.5            | 10.2. DC Electrical Characteristics 144           |

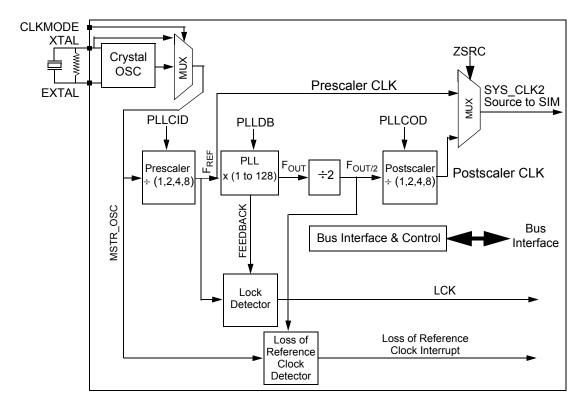

| Part 3: On-Chip Clock Synthesis (OCCS) . 35  | 10.3. AC Electrical Characteristics148            |

| 3.1. Introduction                            | 10.4. Flash Memory Characteristics149             |

| 3.2. External Clock Operation                | 10.5. External Clock Operation Timing 149         |

| 3.3. Registers                               | 10.6. Phase Locked Loop Timing 150                |

|                                              | 10.7. Crystal Oscillator Timing                   |

| Part 4: Memory Map37                         | 10.8. Reset, Stop, Wait, Mode Select,             |

| 4.1. Introduction                            | and Interrupt Timing 151                          |

| 4.2. Program Map                             | 10.9. Serial Peripheral Interface (SPI) Timing153 |

| 4.3. Interrupt Vector Table 40               | 10.10. Quad Timer Timing                          |

| 4.4. Data Map 44                             | 10.11. Quadrature Decoder Timing 157              |

| 4.5. Flash Memory Map 44                     | 10.12. Serial Communication Interface             |

| 4.6. EOnCE Memory Map 46                     | (SCI) Timing                                      |

| 4.7. Peripheral Memory Mapped Registers 47   | 10.13. Controller Area Network (CAN) Timing .158  |

| 4.8. Factory Programmed Memory 79            | 10.14. JTAG Timing                                |

|                                              | 10.15. Analog-to-Digital Converter                |

| Part 5: Interrupt Controller (ITCN) 79       | (ADC) Parameters 160                              |

| 5.1. Introduction                            | 10.16. Equivalent Circuit for ADC Inputs 163      |

| 5.2. Features 80                             | 10.17. Power Consumption                          |

| 5.3. Functional Description 80               |                                                   |

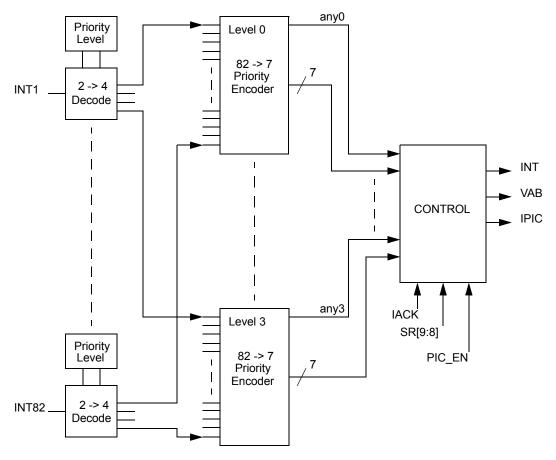

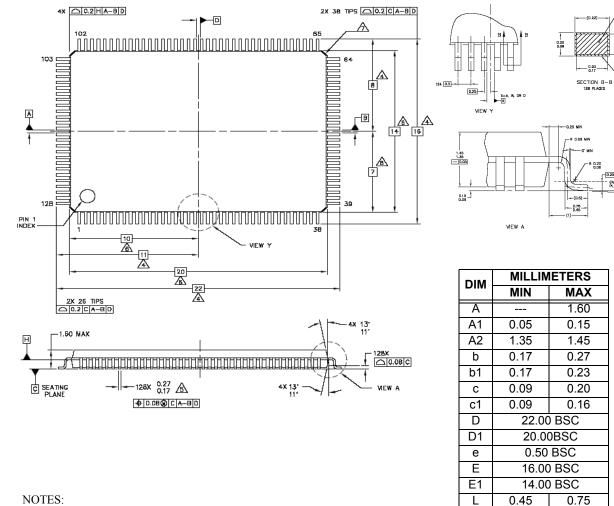

| 5.4. Block Diagram 82                        | Part 11: Packaging                                |

| 5.5. Operating Modes 82                      | 11.1. 56F8365 Package and Pin-Out                 |

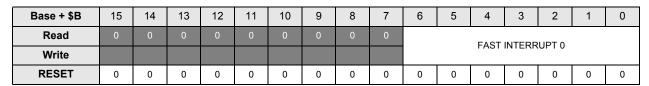

| 5.6. Register Descriptions 83                | Information                                       |

| 5.7. Resets 110                              | 11.2. 56F8165 Package and Pin-Out                 |

|                                              | Information                                       |

| Part 6: System Integration Module (SIM). 111 |                                                   |

| 6.1. Introduction                            | Part 12: Design Considerations 171                |

| 6.2. Features                                | 12.1. Thermal Design Considerations 171           |

| 6.3. Operating Modes 111                     | 12.2. Electrical Design Considerations 171        |

| 6.4. Operating Mode Register 112             | 12.3. Power Distribution and I/O Ring             |

| 6.5. Register Descriptions                   | Implementation 171                                |

| 6.6. Clock Generation Overview 128           | ·                                                 |

| 6.7. Power-Down Modes Overview 128           | Part 13: Ordering Information 171                 |

| 6.8. Stop and Wait Mode Disable Function 129 |                                                   |

| 6.9. Resets                                  |                                                   |

|                                              |                                                   |

| Part 7: Security Features 130                |                                                   |

| 7.1. Operation with Security Enabled 130     |                                                   |

| 7.2. Flash Access Blocking Mechanisms 130    |                                                   |

#### Part 1 Overview

#### 1.1 56F8365/56F8165 Features

#### 1.1.1 Core

- Efficient 16-bit 56800E family controller engine with dual Harvard architecture

- Up to 60 Million Instructions Per Second (MIPS) at 60MHz core frequency

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Four 36-bit accumulators, including extension bits

- Arithmetic and logic multi-bit shifter

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Three internal address buses

- Four internal data buses

- Instruction set supports both DSP and controller functions

- Controller-style addressing modes and instructions for compact code

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/EOnCE debug programming interface

#### 1.1.2 Differences Between Devices

Table 1-1 outlines the key differences between the 56F8365 and 56F8165 devices.

**Table 1-1 Device Differences**

| Feature            | 56F8365       | 56F8165       |

|--------------------|---------------|---------------|

| Guaranteed Speed   | 60MHz/60 MIPS | 40MHz/40MIPS  |

| Program RAM        | 4KB           | Not Available |

| Data Flash         | 32KB          | Not Available |

| PWM                | 2 x 6         | 1 x 6         |

| CAN                | 2             | Not Available |

| Quad Timer         | 4             | 2             |

| Quadrature Decoder | 2 x 4         | 1 x 4         |

| Temperature Sensor | 1             | Not Available |

#### **1.1.3 Memory**

**Note:** Features in italics are NOT available in the 56F8165 device.

- Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Flash security protection feature

- On-chip memory, including a low-cost, high-volume Flash solution

- 512KB of Program Flash

- 4KB of Program RAM

- 32KB of Data Flash

- 32KB of Data RAM

- 32KB of Boot Flash

- EEPROM emulation capability

#### 1.1.4 Peripheral Circuits

**Note:** Features in italics are NOT available in the 56F8165 device.

- Pulse Width Modulator module:

- In the 56F8365, two Pulse Width Modulator modules, each with six PWM outputs, three Current Sense inputs, and four Fault inputs; fault-tolerant design with dead time insertion; supports both center-aligned and edge-aligned modes

- In the 56F8165, one Pulse Width Modulator module with six PWM outputs, three Current Sense inputs and three Fault inputs; fault-tolerant design with dead time insertion; supports both center-aligned and edge-aligned modes

- Four 12-bit, Analog-to-Digital Converters (ADCs), which support four simultaneous conversions with quad, 4-pin multiplexed inputs; ADC and PWM modules can be synchronized through Timer C, channels 2 and 3

- Quadrature Decoder:

- In the 56F8365, two four-input Quadrature Decoders or two additional Quad Timers

- In the 56F8165, one four-input Quadrature Decoder, which works in conjunction with Quad Timer A

- Temperature Sensor can be connected, on the board, to any of the ADC inputs to monitor the on-chip temperature

- Ouad Timer:

- In the 56F8365, four dedicated general-purpose Quad Timers totaling six dedicated pins: Timer C with two pins and Timer D with four pins

- In the 56F8165, two Quad Timers; Timer A and Timer C both work in conjunction with GPIO

- Optional On-Chip Regulator

- Up to two FlexCAN (CAN Version 2.0 B-compliant) modules with 2-pin port for transmit and receive

- Two Serial Communication Interfaces (SCIs), each with two pins (or four additional GPIO lines)

- Up to two Serial Peripheral Interfaces (SPIs), both with configurable 4-pin port (or eight additional GPIO lines); SPI1 can also be used as Quadrature Decoder 1 or Quad Timer B

- Computer Operating Properly (COP)/Watchdog timer

- Two dedicated external interrupt pins

- 49 General Purpose I/O (GPIO) pins; 28 pins dedicated to GPIO

- External reset input pin for hardware reset

- External reset output pin for system reset

- Integrated low-voltage interrupt module

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, processor speed-independent, real-time debugging

- Software-programmable, Phase Lock Loop (PLL)-based frequency synthesizer for the core clock

#### 1.1.5 Energy Information

- Fabricated in high-density CMOS with 5V-tolerant, TTL-compatible digital inputs

- On-board 3.3V down to 2.6V voltage regulator for powering internal logic and memories; can be disabled

- On-chip regulators for digital and analog circuitry to lower cost and reduce noise

- Wait and Stop modes available

- ADC smart power management

- Each peripheral can be individually disabled to save power

#### 1.2 Device Description

The 56F8365 and 56F8165 are members of the 56800E core-based family of controllers. Each combines, on a single chip, the processing power of a Digital Signal Processor (DSP) and the functionality of a microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because of their low cost, configuration flexibility, and compact program code, the 56F8365 and 56F8165 are well-suited for many applications. The devices include many peripherals that are especially useful for motion control, smart appliances, steppers, encoders, tachometers, limit switches, power supply and control, *automotive* control (56F8365 only), engine management, noise suppression, remote utility metering, industrial control for power, lighting, and automation applications.

The 56800E core is based on a Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C/C++ Compilers to enable rapid development of optimized control applications.

The 56F8365 and 56F8165 support program execution from internal memories. Two data operands can be accessed from the on-chip data RAM per instruction cycle. These devices also provide two external dedicated interrupt lines and up to 49 General Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

#### 1.2.1 56F8365 Features

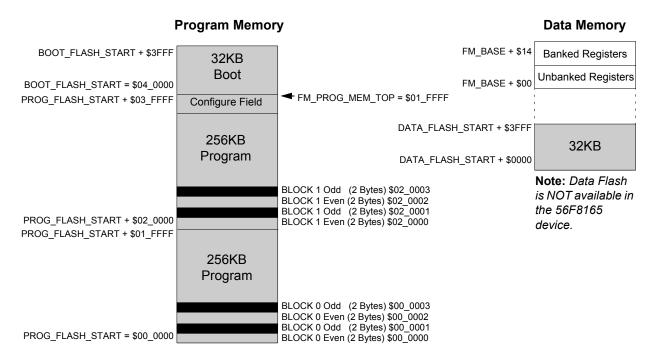

The 56F8365 controller includes 512KB of Program Flash and 32KB of Data Flash (each programmable through the JTAG port) with 4KB of Program RAM and 32KB of Data RAM. A total of 32KB of Boot Flash is incorporated for easy customer inclusion of field-programmable software routines that can be used

to program the main Program and Data Flash memory areas. Both Program and Data Flash memories can be independently bulk erased or erased in pages. Program Flash page erase size is 1KB. Boot and Data Flash page erase size is 512 bytes. The Boot Flash memory can also be either bulk or page erased.

A key application-specific feature of the 56F8365 is the inclusion of two Pulse Width Modulator (PWM) modules. These modules each incorporate three complementary, individually programmable PWM signal output pairs (each module is also capable of supporting six independent PWM functions, for a total of 12 PWM outputs) to enhance motor control functionality. Complementary operation permits programmable dead time insertion, distortion correction via current sensing by software, and separate top and bottom output polarity control. The up-counter value is programmable to support a continuously variable PWM frequency. Edge-aligned and center-aligned synchronous pulse width control (0% to 100% modulation) is supported. The device is capable of controlling most motor types: ACIM (AC Induction Motors); both BDC and BLDC (Brush and Brushless DC motors); SRM and VRM (Switched and Variable Reluctance Motors); and stepper motors. The PWMs incorporate fault protection and cycle-by-cycle current limiting with sufficient output drive capability to directly drive standard optoisolators. A "smoke-inhibit", write-once protection feature for key parameters is also included. A patented PWM waveform distortion correction circuit is also provided. Each PWM is double-buffered and includes interrupt controls to permit integral reload rates to be programmable from 1 to 16. The PWM modules provide reference outputs to synchronize the Analog-to-Digital Converters through two channels of Quad Timer C.

The 56F8365 incorporates two Quadrature Decoders capable of capturing all four transitions on the two-phase inputs, permitting generation of a number proportional to actual position. Speed computation capabilities accommodate both fast- and slow-moving shafts. An integrated watchdog timer in the Quadrature Decoder can be programmed with a time-out value to alert when no shaft motion is detected. Each input is filtered to ensure only true transitions are recorded.

This controller also provides a full set of standard programmable peripherals that include two Serial Communications Interfaces (SCIs); two Serial Peripheral Interfaces (SPIs); and four Quad Timers. Any of these interfaces can be used as General Purpose Input/Outputs (GPIOs) if that function is not required. Two Flex Controller Area Network (FlexCAN) interfaces (CAN Version 2.0 B-compliant) and an internal interrupt controller are also a part of the 56F8365.

#### 1.2.2 56F8165 Features

The 56F8165 hybrid controller includes 128KB of Program Flash, programmable through the JTAG port, and 8KB of Data RAM. A total of 8KB of Boot Flash is incorporated for easy customer inclusion of field-programmable software routines that can be used to program the main Program Flash memory area. The Program Flash memory can be independently bulk erased or erased in pages; Program Flash page erase size is 1KB. The Boot Flash page erase size is 512 bytes; Boot Flash memory can also be either bulk or page erased.

A key application-specific feature of the 56F8165 is the inclusion of one Pulse Width Modulator (PWM) module. This module incorporates three complementary, individually programmable PWM signal output pairs and can also support six independent PWM functions to enhance motor control functionality. Complementary operation permits programmable dead time insertion, distortion correction via current sensing by software, and separate top and bottom output polarity control. The up-counter value is

programmable to support a continuously variable PWM frequency. Edge-aligned and center-aligned synchronous pulse width control (0% to 100% modulation) is supported. The device is capable of controlling most motor types: ACIM (AC Induction Motors); both BDC and BLDC (Brush and Brushless DC motors); SRM and VRM (Switched and Variable Reluctance Motors); and stepper motors. The PWM incorporates fault protection and cycle-by-cycle current limiting with sufficient output drive capability to directly drive standard optoisolators. A "smoke-inhibit", write-once protection feature for key parameters is also included. A patented PWM waveform distortion correction circuit is also provided. The PWM is double-buffered and includes interrupt controls to permit integral reload rates to be programmable from 1 to 16. The PWM module provides reference outputs to synchronize the Analog-to-Digital Converters through two channels of Quad Timer C.

The 56F8165 incorporates a Quadrature Decoder capable of capturing all four transitions on the two-phase inputs, permitting generation of a number proportional to actual position. Speed computation capabilities accommodate both fast- and slow-moving shafts. An integrated watchdog timer in the Quadrature Decoder can be programmed with a time-out value to alert when no shaft motion is detected. Each input is filtered to ensure only true transitions are recorded.

This controller also provides a full set of standard programmable peripherals that include two Serial Communications Interfaces (SCIs); two Serial Peripheral Interfaces (SPIs); and two Quad Timers. Any of these interfaces can be used as General Purpose Input/Outputs (GPIOs) if that function is not required. An internal interrupt controller is also a part of the 56F8165.

### 1.3 Award-Winning Development Environment

Processor Expert<sup>TM</sup> (PE) provides a Rapid Application Design (RAD) tool that combines easy-to-use component-based software application creation with an expert knowledge system.

The CodeWarrior Integrated Development Environment is a sophisticated tool for code navigation, compiling, and debugging. A complete set of evaluation modules (EVMs) and development system cards will support concurrent engineering. Together, PE, CodeWarrior and EVMs create a complete, scalable tools solution for easy, fast, and efficient development.

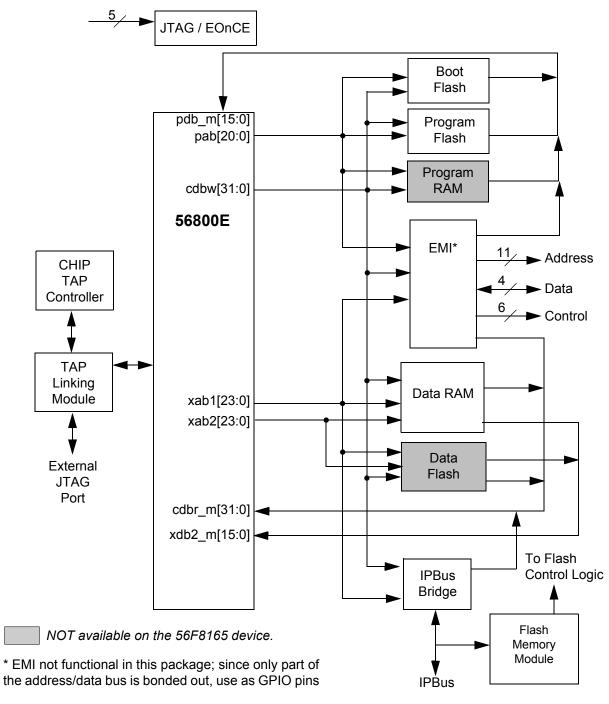

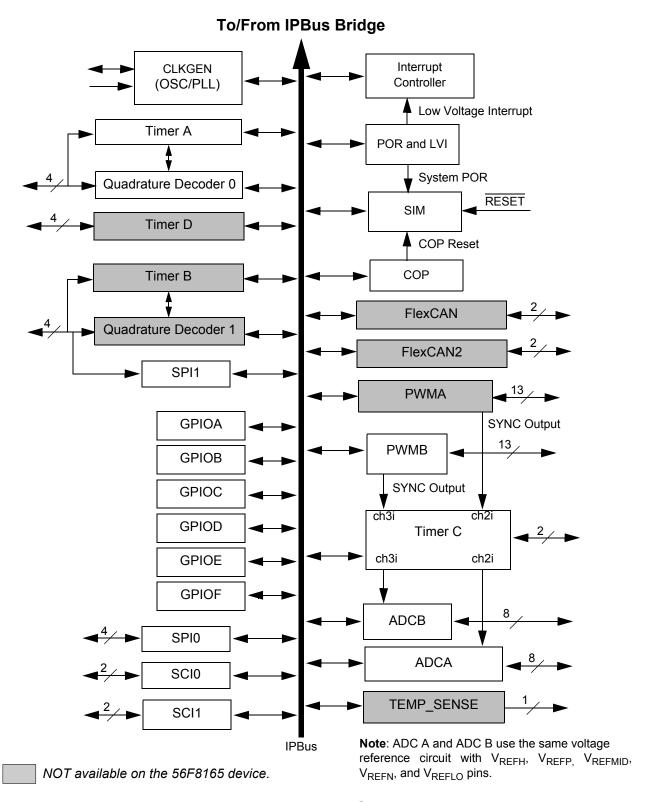

### 1.4 Architecture Block Diagram

**Note:** Features in italics are NOT available in the 56F8165 device and are shaded in the following figures.

The 56F8365/56F8165 architecture is shown in **Figure 1-1** and **Figure 1-2**. **Figure 1-1** illustrates how the 56800E system buses communicate with internal memories and the IPBus Bridge. **Table 1-2** lists the internal buses in the 56800E architecture and provides a brief description of their function. **Figure 1-2** shows the peripherals and control blocks connected to the IPBus Bridge. The figures do not show the on-board regulator and power and ground signals. They also do not show the multiplexing between peripherals or the dedicated GPIOs. Please see **Part 2**, **Signal/Connection Descriptions**, to see which signals are multiplexed with those of other peripherals.

Also shown in **Figure 1-2** are connections between the PWM, Timer C and ADC blocks. These connections allow the PWM and/or Timer C to control the timing of the start of ADC conversions. The Timer C channel indicated can generate periodic start (SYNC) signals to the ADC to start its conversions. In another operating mode, the PWM load interrupt (SYNC output) signal is routed internally to the Timer C input channel as indicated. The timer can then be used to introduce a controllable delay before generating its output signal. The timer output then triggers the ADC. To fully understand this interaction, please see the **56F8300 Peripheral User Manual** for clarification on the operation of all three of these peripherals.

Figure 1-1 System Bus Interfaces

**Note:** Flash memories are encapsulated within the Flash Memory (FM) Module. Flash control is accomplished by the I/O to the FM over the peripheral bus, while reads and writes are completed between the core and the Flash memories.

**Note:** The primary data RAM port is 32 bits wide. Other data ports are 16 bits.

Figure 1-2 Peripheral Subsystem

## **Table 1-2 Bus Signal Names**

| Name                     | Function                                                                                                                                                                                                                                                          |  |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                          | Program Memory Interface                                                                                                                                                                                                                                          |  |  |  |  |  |

| pdb_m[15:0]              | Program data bus for instruction word fetches or read operations.                                                                                                                                                                                                 |  |  |  |  |  |

| cdbw[15:0]               | Primary core data bus used for program memory writes. (Only these 16 bits of the cdbw[31:0] bus are used for writes to program memory.)                                                                                                                           |  |  |  |  |  |

| pab[20:0]                | Program memory address bus. Data is returned on pdb_m bus.                                                                                                                                                                                                        |  |  |  |  |  |

|                          | Primary Data Memory Interface Bus                                                                                                                                                                                                                                 |  |  |  |  |  |

| cdbr_m[31:0]             | Primary core data bus for memory reads. Addressed via xab1 bus.                                                                                                                                                                                                   |  |  |  |  |  |

| cdbw[31:0]               | Primary core data bus for memory writes. Addressed via xab1 bus.                                                                                                                                                                                                  |  |  |  |  |  |

| xab1[23:0]               | Primary data address bus. Capable of addressing bytes <sup>1</sup> , words, and long data types. Data is written on cdbw and returned on cdbr_m. Also used to access memory-mapped I/O.                                                                           |  |  |  |  |  |

|                          | Secondary Data Memory Interface                                                                                                                                                                                                                                   |  |  |  |  |  |

| xdb2_m[15:0]             | Secondary data bus used for secondary data address bus xab2 in the dual memory reads.                                                                                                                                                                             |  |  |  |  |  |

| xab2[23:0]               | Secondary data address bus used for the second of two simultaneous accesses. Capable of addressing only words. Data is returned on xdb2_m.                                                                                                                        |  |  |  |  |  |

| Peripheral Interface Bus |                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| IPBus [15:0]             | Peripheral bus accesses all on-chip peripherals registers. This bus operates at the same clock rate as the Primary Data Memory and therefore generates no delays when accessing the processor. Write data is obtained from cdbw. Read data is provided to cdbr_m. |  |  |  |  |  |

<sup>1.</sup> Byte accesses can only occur in the bottom half of the memory address space. The MSB of the address will be forced to 0.

#### 1.5 Product Documentation

The documents listed in **Table 1-3** are required for a complete description and proper design with the 56F8365/56F8165 devices. Documentation is available from local Freescale distributors, Freescale semiconductor sales offices, Freescale Literature Distribution Centers, or online at **http://www.freescale.com**.

**Table 1-3 Chip Documentation**

| Topic                                        | Description                                                                                                                             | Order Number             |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| DSP56800E<br>Reference Manual                | Detailed description of the 56800E family architecture, 16-bit controller core processor, and the instruction set                       | DSP56800EERM             |

| 56F8300 Peripheral<br>User Manual            | Detailed description of peripherals of the 56F8300 family of devices                                                                    | MC56F8300UM              |

| 56F8300 SCI/CAN<br>Bootloader User<br>Manual | Detailed description of the SCI/CAN Bootloaders 56F8300 family of devices                                                               | MC56F83xxBLUM            |

| 56F8365/56F8165<br>Technical Data Sheet      | Electrical and timing specifications, pin descriptions, device specific peripheral information and package descriptions (this document) | MC56F8365                |

| Errata                                       | Details any chip issues that might be present                                                                                           | MC56F8365E<br>MC56F8165E |

#### 1.6 Data Sheet Conventions

This data sheet uses the following conventions:

| OVERBAR | This is used to indicate a signal that is active when pulled low. For example, the RESET pin is |

|---------|-------------------------------------------------------------------------------------------------|

|         | active when low.                                                                                |

"asserted" A high true (active high) signal is high or a low true (active low) signal is low.

"deasserted" A high true (active high) signal is low or a low true (active low) signal is high.

| Examples: | Signal/Symbol | Logic State | Signal State | Voltage <sup>1</sup>             |

|-----------|---------------|-------------|--------------|----------------------------------|

|           | PIN           | True        | Asserted     | $V_{IL}/V_{OL}$                  |

|           | PIN           | False       | Deasserted   | $V_{IH}/V_{OH}$                  |

|           | PIN           | True        | Asserted     | $V_{IH}/V_{OH}$                  |

|           | PIN           | False       | Deasserted   | V <sub>IL</sub> /V <sub>OL</sub> |

<sup>1.</sup> Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

# Part 2 Signal/Connection Descriptions

#### 2.1 Introduction

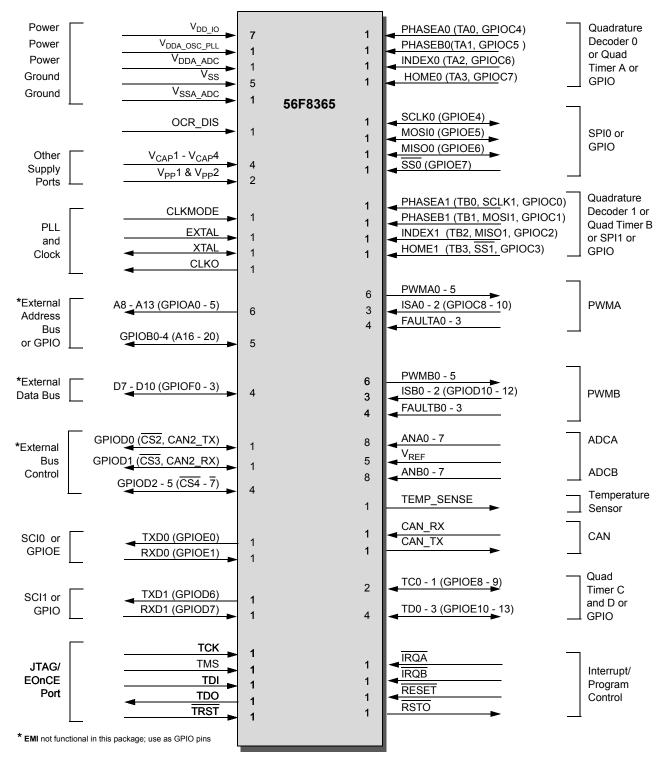

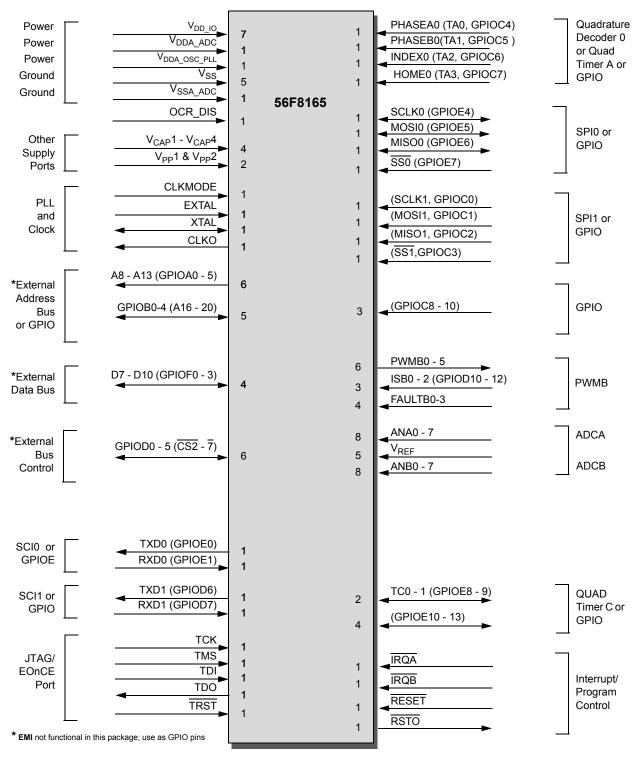

The input and output signals of the 56F8365 and 56F8165 are organized into functional groups, as detailed in **Table 2-1** and as illustrated in **Figure 2-1**. In **Table 2-2**, each table row describes the signal or signals present on a pin.

**Table 2-1 Functional Group Pin Allocations**

| Fire skip and Consum                                           | Number of Pins in Package |         |  |  |

|----------------------------------------------------------------|---------------------------|---------|--|--|

| Functional Group                                               | 56F8365                   | 56F8165 |  |  |

| Power (V <sub>DD</sub> or V <sub>DDA</sub> )                   | 9                         | 9       |  |  |

| Power Option Control                                           | 1                         | 1       |  |  |

| Ground (V <sub>SS</sub> or V <sub>SSA</sub> )                  | 6                         | 6       |  |  |

| Supply Capacitors <sup>1</sup> & V <sub>PP</sub>               | 6                         | 6       |  |  |

| PLL and Clock                                                  | 4                         | 4       |  |  |

| Bus Control                                                    | 6                         | 6       |  |  |

| Interrupt and Program Control                                  | 4                         | 4       |  |  |

| Pulse Width Modulator (PWM) Ports                              | 26                        | 13      |  |  |

| Serial Peripheral Interface (SPI) Port 0                       | 4                         | 4       |  |  |

| Serial Peripheral Interface (SPI) Port 1                       | _                         | 4       |  |  |

| Quadrature Decoder Port 0 <sup>2</sup>                         | 4                         | 4       |  |  |

| Quadrature Decoder Port 1 <sup>3</sup>                         | 4                         | _       |  |  |

| Serial Communications Interface (SCI) Ports                    | 4                         | 4       |  |  |

| CAN Ports                                                      | 2                         | _       |  |  |

| Analog-to-Digital Converter (ADC) Ports                        | 21                        | 21      |  |  |

| Timer Module Ports                                             | 6                         | 4       |  |  |

| JTAG/Enhanced On-Chip Emulation (EOnCE)                        | 5                         | 5       |  |  |

| Temperature Sense                                              | 1                         | _       |  |  |

| Dedicated GPIO ( Address Bus = 11; Data Bus = 4 <sup>4</sup> ) | 28                        | 28      |  |  |

<sup>1.</sup> If the on-chip regulator is disabled, the  $V_{CAP}$  pins serve as 2.5V  $V_{DD}$  CORE power inputs

Note: See Table 1-1 for 56F8165 functional differences.

<sup>2.</sup> Alternately, can function as Quad Timer pins or GPIO

<sup>3.</sup> Pins in this section can function as Quad Timer, SPI 1, orGPIO

<sup>4.</sup> EMI not functional in these packages; use as GPIO pins.

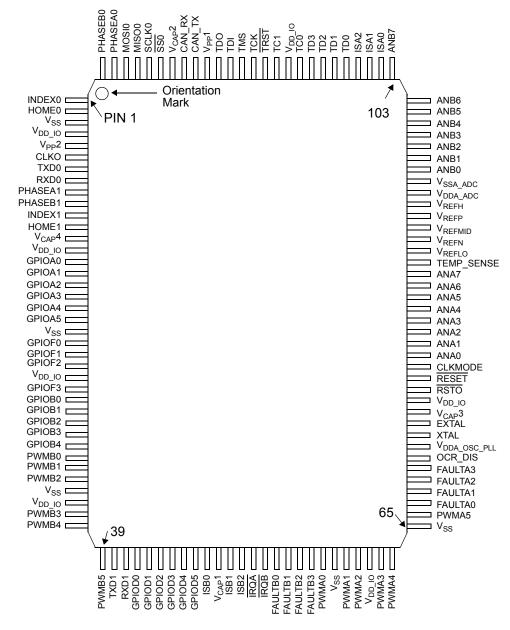

Figure 2-1 56F8365 Signals Identified by Functional Group<sup>1</sup> (128-Pin LQFP)

<sup>1.</sup> Alternate pin functionality is shown in parenthesis; pin direction/type shown is the default functionality.

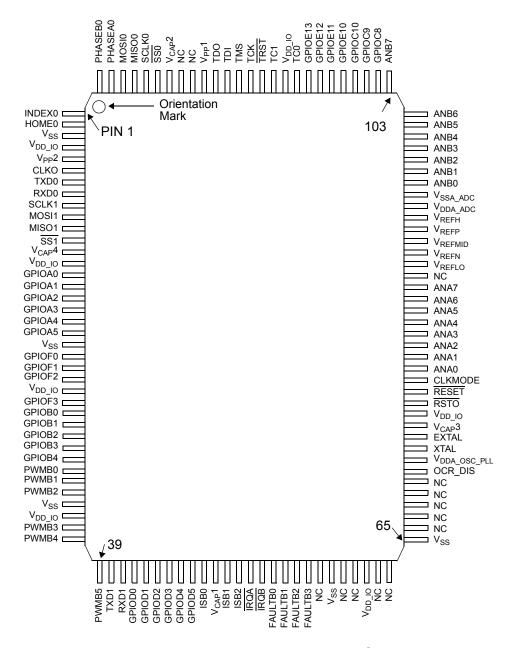

Figure 2-2 56F8165 Signals Identified by Functional Group<sup>1</sup> (128-Pin LQFP)

<sup>1.</sup> Alternate pin functionality is shown in parenthesis; pin direction/type shown is the default functionality.

### 2.2 Signal Pins

After reset, each pin is configured for its primary function (listed first). Any alternate functionality must be programmed.

EMI is not functional in this package; since only part of the address/data bus is bonded out, use as GPIO pins.

**Note:** Signals in italics are NOT available in the 56F8165 device.

If the "State During Reset" lists more than one state for a pin, the first state is the actual reset state. Other states show the reset condition of the alternate function, which you get if the alternate pin function is selected without changing the configuration of the alternate peripheral. For example, the A8/GPIOA0 pin shows that it is tri-stated during reset. If the GPIOA\_PER is changed to select the GPIO function of the pin, it will become an input if no other registers are changed.

Table 2-2 Signal and Package Information for the 128-Pin LQFP

| Signal<br>Name        | Pin No. | Туре   | State<br>During<br>Reset | Signal Description                                                                                                                                                                                 |

|-----------------------|---------|--------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD_IO</sub>    | 4       | Supply |                          | I/O Power — This pin supplies 3.3V power to the chip I/O interface and also the Processor core throught the on-chip voltage                                                                        |

| V <sub>DD_IO</sub>    | 14      |        |                          | regulator, if it is enabled.                                                                                                                                                                       |

| V <sub>DD_IO</sub>    | 25      |        |                          |                                                                                                                                                                                                    |

| V <sub>DD_IO</sub>    | 36      |        |                          |                                                                                                                                                                                                    |

| V <sub>DD_IO</sub>    | 62      |        |                          |                                                                                                                                                                                                    |

| V <sub>DD_IO</sub>    | 76      |        |                          |                                                                                                                                                                                                    |

| V <sub>DD_IO</sub>    | 112     |        |                          |                                                                                                                                                                                                    |

| V <sub>DDA_ADC</sub>  | 94      | Supply |                          | ADC Power — This pin supplies 3.3V power to the ADC modules. It must be connected to a clean analog power supply.                                                                                  |

| V <sub>DDA_OSC_</sub> | 72      | Supply |                          | Oscillator and PLL Power — This pin supplies 3.3V power to the OSC and to the internal regulator that in turn supplies the Phase Locked Loop. It must be connected to a clean analog power supply. |

| V <sub>SS</sub>       | 3       | Supply |                          | Ground — These pins provide ground for chip logic and I/O drivers.                                                                                                                                 |

| V <sub>SS</sub>       | 21      |        |                          | uliveis.                                                                                                                                                                                           |

| V <sub>SS</sub>       | 35      |        |                          |                                                                                                                                                                                                    |

| V <sub>SS</sub>       | 59      |        |                          |                                                                                                                                                                                                    |

| V <sub>SS</sub>       | 65      |        |                          |                                                                                                                                                                                                    |

Table 2-2 Signal and Package Information for the 128-Pin LQFP (Continued)

| Signal<br>Name       | Pin No. | Туре             | State<br>During<br>Reset | Signal Description                                                                                                                                                                                                                                                                      |

|----------------------|---------|------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SSA_ADC</sub> | 95      | Supply           |                          | ADC Analog Ground — This pin supplies an analog ground to the ADC modules.                                                                                                                                                                                                              |

| OCR_DIS              | 71      | Input            | Input                    | On-Chip Regulator Disable — Tie this pin to V <sub>SS</sub> to enable the on-chip regulator Tie this pin to V <sub>DD</sub> to disable the on-chip regulator  This pin is intended to be a static DC signal from power-up to shut down. Do not try to toggle this pin for power savings |

|                      |         |                  |                          | during operation.                                                                                                                                                                                                                                                                       |

| V <sub>CAP</sub> 1   | 49      | Supply           | Supply                   | V <sub>CAP</sub> 1 - 4 — When OCR_DIS is tied to V <sub>SS</sub> (regulator enabled),                                                                                                                                                                                                   |

| V <sub>CAP</sub> 2   | 122     |                  |                          | connect each pin to a $2.2\mu F$ or greater bypass capacitor in order to bypass the core logic voltage regulator, required for proper chip operation. When OCR_DIS is tied to $V_{DD}$ (regulator disabled),                                                                            |

| V <sub>CAP</sub> 3   | 75      |                  |                          | these pins become V <sub>DD_CORE</sub> and should be connected to a                                                                                                                                                                                                                     |

| V <sub>CAP</sub> 4   | 13      |                  |                          | regulated 2.5V power supply.                                                                                                                                                                                                                                                            |

|                      |         |                  |                          | Note: This bypass is required even if the chip is powered with an external supply.                                                                                                                                                                                                      |

| V <sub>PP</sub> 1    | 119     | Input            | Input                    | V <sub>PP</sub> 1 - 2 — These pins should be left unconnected as an open circuit for normal functionality.                                                                                                                                                                              |

| V <sub>PP</sub> 2    | 5       |                  |                          | circuit for normal functionality.                                                                                                                                                                                                                                                       |

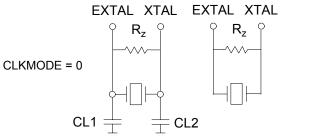

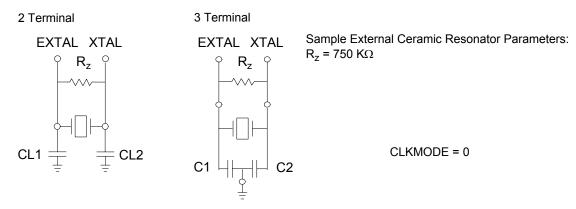

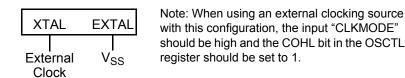

| CLKMODE              | 79      | Input            | Input                    | Clock Input Mode Selection — This input determines the function of the XTAL and EXTAL pins.                                                                                                                                                                                             |

|                      |         |                  |                          | 1 = External clock input on XTAL is used to directly drive the input clock of the chip. The EXTAL pin should be grounded.                                                                                                                                                               |

|                      |         |                  |                          | 0 = A crystal or ceramic resonator should be connected between XTAL and EXTAL.                                                                                                                                                                                                          |

| EXTAL                | 74      | Input            | Input                    | External Crystal Oscillator Input — This input can be connected to an 8MHz external crystal. Tie this pin low if XTAL is driven by an external clock source.                                                                                                                            |

| XTAL                 | 73      | Input/<br>Output | Chip-driven              | Crystal Oscillator Output — This output connects the internal crystal oscillator output to an external crystal.                                                                                                                                                                         |

|                      |         |                  |                          | If an external clock is used, XTAL must be used as the input and EXTAL connected to GND.                                                                                                                                                                                                |

|                      |         |                  |                          | The input clock can be selected to provide the clock directly to the core. This input clock can also be selected as the input clock for the on-chip PLL.                                                                                                                                |

Table 2-2 Signal and Package Information for the 128-Pin LQFP (Continued)

| Signal<br>Name  | Pin No. | Туре                        | State<br>During<br>Reset                                     | Signal Description                                                                                                                                                                                                                                                                                                         |

|-----------------|---------|-----------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СЬКО            | 6       | Output                      | In reset,<br>output is<br>disabled                           | Clock Output — This pin outputs a buffered clock signal. Using the SIM CLKO Select Register (SIM_CLKOSR), this pin can be programmed as any of the following: disabled, CLK_MSTR (system clock), IPBus clock, oscillator output, prescaler clock and postscaler clock. Other signals are also available for test purposes. |

|                 |         |                             |                                                              | See Part 6.5.7 for details.                                                                                                                                                                                                                                                                                                |

| A8              | 15      | Output                      | In reset,<br>output is<br>disabled,<br>pull-up is<br>enabled | Address Bus — A8 - A13 specify six of the address lines for external program or data memory accesses. Depending upon the state of the DRV bit in the EMI bus control register (BCR), A8 - A13 and EMI control signals are tri-stated when the external bus is inactive.                                                    |

| (GPIOA0)        |         | Schmitt<br>Input/           |                                                              | Port A GPIO — These six GPIO pins can be individually programmed as input or output pins.                                                                                                                                                                                                                                  |

| A9<br>(GPIOA1)  | 16      | Output                      |                                                              | After reset, these pins default to address bus functionality and                                                                                                                                                                                                                                                           |

| A10<br>(GPIOA2) | 17      |                             |                                                              | must be programmed as GPIO.  To deactivate the internal pull-up resistor, clear the appropriate                                                                                                                                                                                                                            |

| A11<br>(GPIOA3) | 18      |                             |                                                              | GPIO bit in the GPIOA_PUR register.  Example: GPIOA0, clear bit 0 in the GPIOA_PUR register.                                                                                                                                                                                                                               |

| A12<br>(GPIOA4) | 19      |                             |                                                              | <b>Note:</b> Primary function is not available in this package configuration; GPIO function must be used instead.                                                                                                                                                                                                          |

| A13<br>(GPIOA5) | 20      |                             |                                                              |                                                                                                                                                                                                                                                                                                                            |

| GPIOB0          | 27      | Schmitt<br>Input/<br>Output | Input,<br>pull-up<br>enabled                                 | Port B GPIO — These four GPIO pins can be individually programmed as an input or output pin.                                                                                                                                                                                                                               |

| (A16)           |         | Output                      |                                                              | Address Bus — A16 - A19 specify four of the address lines for                                                                                                                                                                                                                                                              |

| GPIOB1          | 28      |                             |                                                              | external program or data memory accesses. Depending upon the state of the DRV bit in the EMI bus control register (BCR), A16 -                                                                                                                                                                                             |

| (A17)           |         |                             |                                                              | A19 and EMI control signals are tri-stated when the external bus is inactive.                                                                                                                                                                                                                                              |

| GPIOB2          | 29      |                             |                                                              | After reset, the default state is GPIO.                                                                                                                                                                                                                                                                                    |

| (A18)           |         |                             |                                                              | To deactivate the internal pull-up resistor, clear bit 0 in the                                                                                                                                                                                                                                                            |

| GPIOB3          | 30      |                             |                                                              | GPIOB_PUR register.                                                                                                                                                                                                                                                                                                        |

| (A19)           |         |                             |                                                              | Example: GPIOB1, clear bit 1 in the GPIOB_PUR register.                                                                                                                                                                                                                                                                    |

Table 2-2 Signal and Package Information for the 128-Pin LQFP (Continued)

| Signal<br>Name        | Pin No. | Туре                        | State<br>During<br>Reset                                     | Signal Description                                                                                                                                                                                                                                              |

|-----------------------|---------|-----------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOB4                | 31      | Schmitt<br>Input/<br>Output | Input,<br>pull-up<br>enabled                                 | Port B GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                           |

| (A20)                 |         | Output                      |                                                              | Address Bus — A20 specifies one of the address lines for external program or data memory accesses. Depending upon the state of the DRV bit in the EMI bus control register (BCR), A20 and EMI control signals are tri-stated when the external bus is inactive. |

| (prescaler_<br>clock) |         | Output                      |                                                              | Clock Output — can be used to monitor the prescaler_clock on GPIOB4.                                                                                                                                                                                            |

|                       |         |                             |                                                              | After reset, the default state is GPIO.                                                                                                                                                                                                                         |

|                       |         |                             |                                                              | This pin can also be used to view the prescaler_clock. In these cases, the GPIOB_PER can be used to disable the GPIO. The CLKOSR register in the SIM can then be used to choose between address and clock functions; see  Part 6.5.7 for details                |

|                       |         |                             |                                                              | To deactivate the internal pull-up resistor, clear bit 4 in the GPIOB_PUR register.                                                                                                                                                                             |

| D7                    | 22      | Input/<br>Output            | In reset,<br>output is<br>disabled,<br>pull-up is<br>enabled | Data Bus — D7 - D10 specify part of the data for external program or data memory accesses. Depending upon the state of the DRV bit in the SEMI bus control register (BCR), D7 - D10 are tri-stated when the external bus is inactive                            |

| (GPIOF0)              |         | Input/                      |                                                              | Port F GPIO — These four GPIO pins can be individually                                                                                                                                                                                                          |

| D8<br>(GPIOF1)        | 23      | Output                      |                                                              | programmed as input or output pins.  After reset, these pins default to Data Bus functionality and should                                                                                                                                                       |

| D9<br>(GPIOF2)        | 24      |                             |                                                              | be programmed as GPIO.  To deactivate the internal pull-up resistor, clear the appropriate                                                                                                                                                                      |

| D10                   | 26      |                             |                                                              | GPIO bit in the GPIOF_PUR register.                                                                                                                                                                                                                             |

| (GPIOF3)              |         |                             |                                                              | Example: GPIOF0, clear bit 0 in the GPIOF_PUR register.                                                                                                                                                                                                         |

|                       |         |                             |                                                              | <b>Note:</b> Primary function is not available in this package configuration; GPIO function must be used instead.                                                                                                                                               |

Table 2-2 Signal and Package Information for the 128-Pin LQFP (Continued)

| Signal<br>Name     | Pin No. | Туре                        | State<br>During<br>Reset     | Signal Description                                                                                                                                                                                                                                                   |

|--------------------|---------|-----------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOD0             | 42      | Input/<br>Output            | Input,<br>pull-up            | Port D GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                |

| (CS2)              |         | Output                      | enabled                      | Chip Select — CS2 may be programmed within the EMI module to act as a chip select for specific areas of the external memory map. Depending upon the state of the DRV bit in the EMI Bus Control Register (BCR), CS2 is tri-stated when the external bus is inactive. |

| (CAN2_TX)          |         | Open<br>Drain<br>Output     |                              | FlexCAN2 Transmit Data — CAN output.                                                                                                                                                                                                                                 |

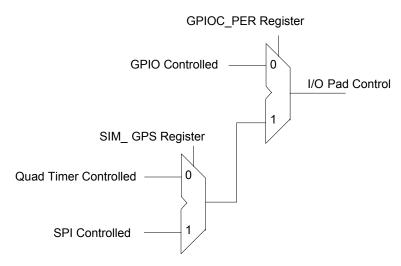

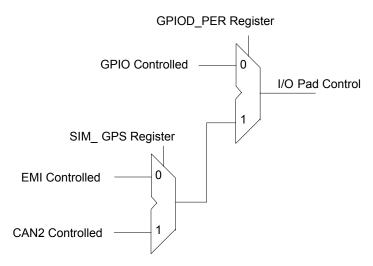

|                    |         |                             |                              | At reset, this pin is configured as GPIO. This configuration can be changed by setting bit 0 in the GPIO_D_PER register, then change bit 4 in the SIM_GPS register to select the desired peripheral function.                                                        |

|                    |         |                             |                              | To deactivate the internal pull-up resistor, clear bit 0 in the GPIOD_PUR register.                                                                                                                                                                                  |

| GPIOD1             | 43      | Schmitt<br>Input/<br>Output | Input,<br>pull-up<br>enabled | Port D GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                |

| ( <del>CS3</del> ) |         | Output                      |                              | Chip Select — CS3 may be programmed within the EMI module to act as a chip select for specific areas of the external memory map.                                                                                                                                     |

|                    |         |                             |                              | Depending upon the state of the DRV bit in the EMI Bus Control Register (BCR), CS3 is tri-stated when the external bus is inactive.                                                                                                                                  |

| (CAN2_RX)          |         | Schmitt<br>Input            |                              | FlexCAN2 Receive Data — This is the CAN input. This pin has an internal pull-up resistor.                                                                                                                                                                            |

|                    |         |                             |                              | At reset, this pin is configured as GPIO. This configuration can be changed by setting bit 1 in the GPIO_D_PER register, then change bit 5 in the SIM_GPS register to select the desired peripheral function.                                                        |

|                    |         |                             |                              | To deactivate the internal pull-up resistor, clear bit 1 in the GPIOD_PUR register.                                                                                                                                                                                  |

Table 2-2 Signal and Package Information for the 128-Pin LQFP (Continued)

| Signal<br>Name           | Pin No. | Туре             | State<br>During<br>Reset                                     | Signal Description                                                                                                                        |

|--------------------------|---------|------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOD2                   | 44      | Input/<br>Output | Input,<br>pull-up<br>enabled                                 | Port D GPIO — These four GPIO pins can be individually programmed as input or output pins.                                                |

| ( <del>CS4</del> )       |         | Output           | enabled                                                      | Chip Select — CS4 - CS7 may be programmed within the EMI                                                                                  |

| GPIOD3<br>(CS5)          | 45      |                  |                                                              | module to act as chip selects for specific areas of the external memory map.                                                              |

| G <u>PIOD</u> 4<br>(CS6) | 46      |                  |                                                              | Depending upon the state of the DRV bit in the EMI bus control register (BCR), CS4 - CS7 are tri-stated when the external bus is inactive |

| G <u>PIOD</u> 5<br>(CS7) | 47      |                  |                                                              | After reset, these pins are configured as GPIO.                                                                                           |

| (55.7)                   |         |                  |                                                              | To deactivate the internal pull-up resistor, clear the appropriate GPIO bit in the GPIOD_PUR register.                                    |

|                          |         |                  |                                                              | Example: GPIOD2, clear bit 2 in the GPIOD_PUR register.                                                                                   |

| TXD0                     | 7       | Output           | In reset,<br>output is<br>disabled,<br>pull-up is<br>enabled | Transmit Data — SCI0 transmit data output                                                                                                 |

| (GPIOE0)                 |         | Input/<br>Output |                                                              | Port E GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                     |

|                          |         |                  |                                                              | After reset, the default state is SCI output.                                                                                             |

|                          |         |                  |                                                              | To deactivate the internal pull-up resistor, clear bit 0 in the GPIOE_PUR register.                                                       |

| RXD0                     | 8       | Input            | Input,                                                       | Receive Data — SCI0 receive data input                                                                                                    |

| (GPIOE1)                 |         | Input/<br>Output | pull-up<br>enabled                                           | Port E GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                     |

|                          |         |                  |                                                              | After reset, the default state is SCI output.                                                                                             |

|                          |         |                  |                                                              | To deactivate the internal pull-up resistor, clear bit 1 in the GPIOE_PUR register.                                                       |

| TXD1                     | 40      | Output           | In reset,                                                    | Transmit Data — SCI1 transmit data output                                                                                                 |

| (GPIOD6)                 |         | Input/<br>Output | output is<br>disabled,<br>pull-up is<br>enabled              | Port D GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                     |

|                          |         |                  | 3.145104                                                     | After reset, the default state is SCI output.                                                                                             |

|                          |         |                  |                                                              | To deactivate the internal pull-up resistor, clear bit 6 in the GPIOD_PUR register.                                                       |

Table 2-2 Signal and Package Information for the 128-Pin LQFP (Continued)

| Signal<br>Name | Pin No. | Туре             | State<br>During<br>Reset                                     | Signal Description                                                                                                                                                                                                          |

|----------------|---------|------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD1           | 41      | Input            | Input,                                                       | Receive Data — SCI1 receive data input                                                                                                                                                                                      |

| (GPIOD7)       |         | Input/<br>Output | pull-up<br>enabled                                           | Port D GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                       |

|                |         |                  |                                                              | After reset, the default state is SCI input.                                                                                                                                                                                |

|                |         |                  |                                                              | To deactivate the internal pull-up resistor, clear bit 7 in the GPIOD_PUR register.                                                                                                                                         |

| тск            | 115     | Schmitt<br>Input | Input,<br>pulled low<br>internally                           | <b>Test Clock Input</b> — This input pin provides a gated clock to synchronize the test logic and shift serial data to the JTAG/EOnCE port. The pin is connected internally to a pull-down resistor.                        |

| TMS            | 116     | Schmitt<br>Input | Input,<br>pulled high<br>internally                          | <b>Test Mode Select Input</b> — This input pin is used to sequence the JTAG TAP controller's state machine. It is sampled on the rising edge of TCK and has an on-chip pull-up resistor.                                    |

|                |         |                  |                                                              | To deactivate the internal pull-up resistor, set the JTAG bit in the SIM_PUDR register.                                                                                                                                     |

|                |         |                  |                                                              | <b>Note:</b> Always tie the TMS pin to V <sub>DD</sub> through a 2.2K resistor.                                                                                                                                             |

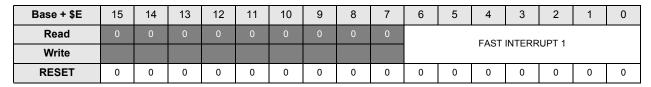

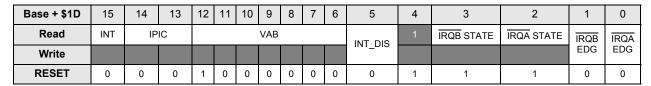

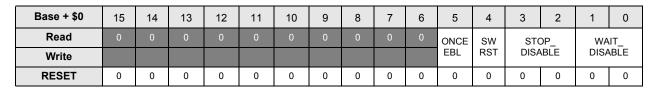

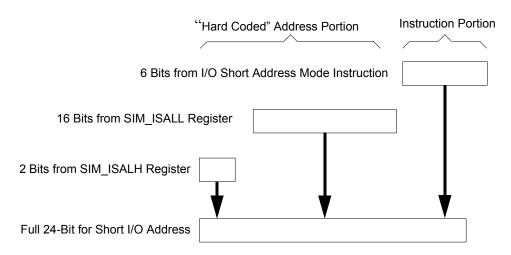

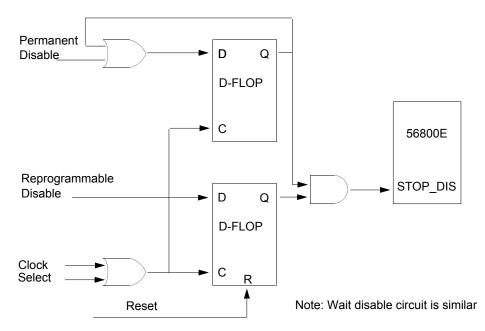

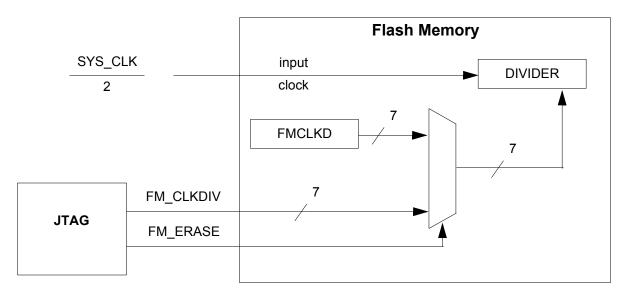

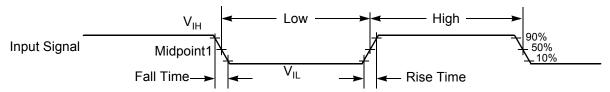

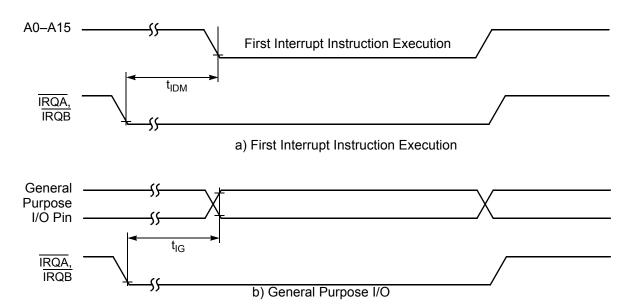

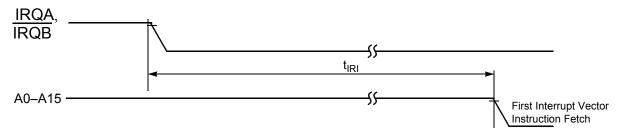

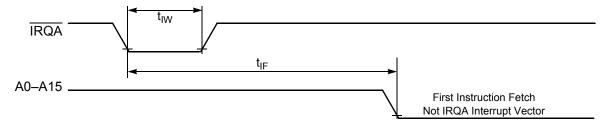

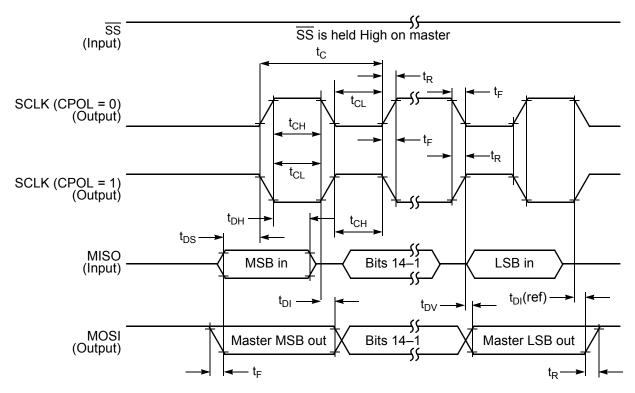

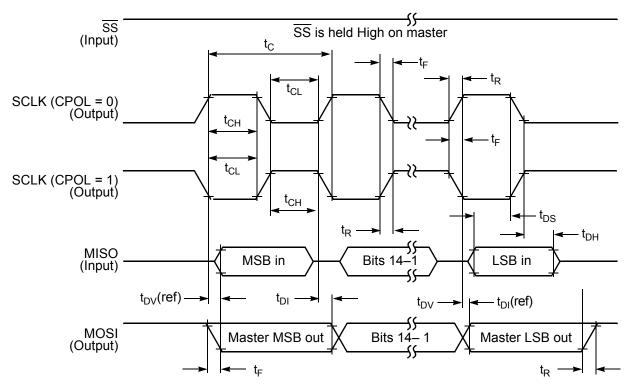

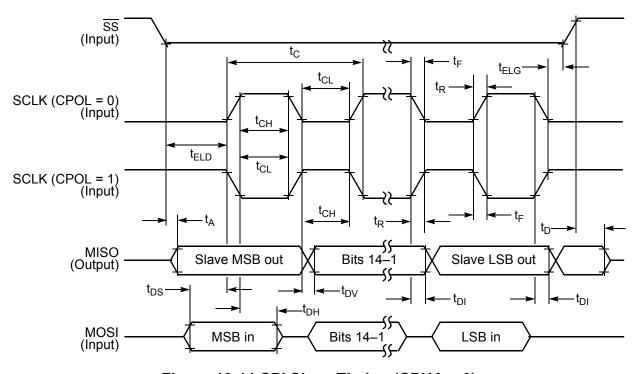

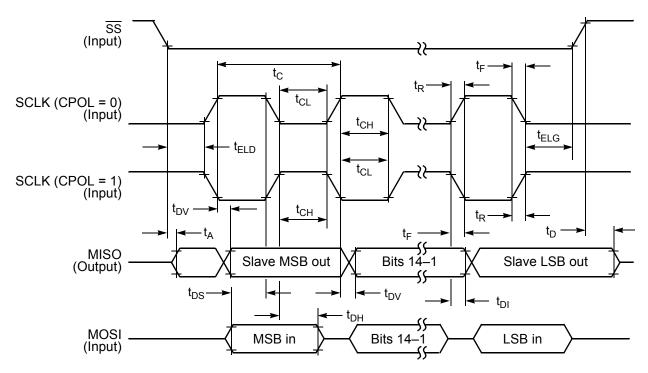

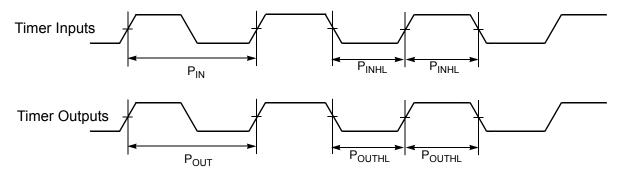

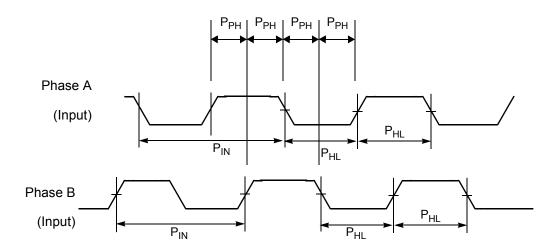

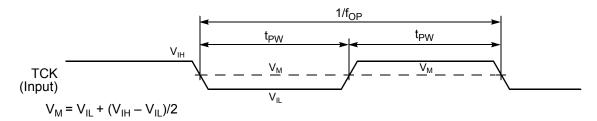

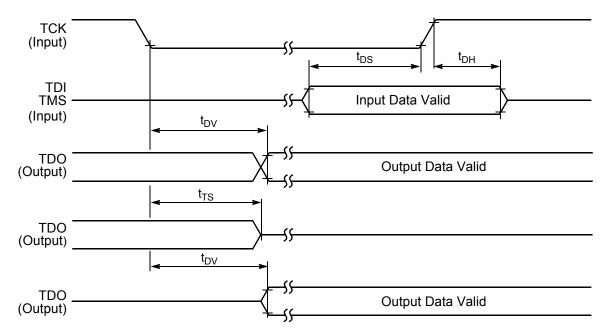

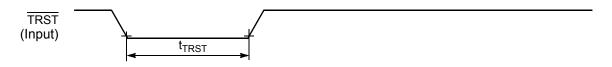

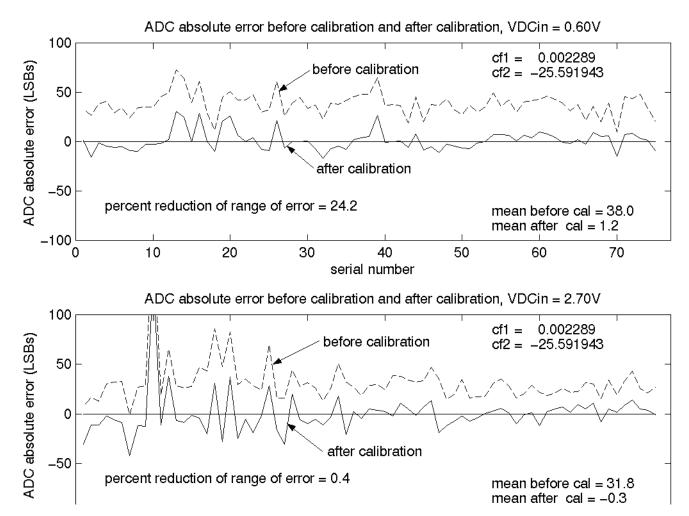

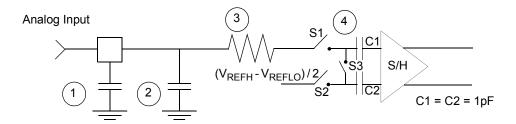

| TDI            | 117     | Schmitt<br>Input | Input,<br>pulled high<br>internally                          | <b>Test Data Input</b> — This input pin provides a serial input data stream to the JTAG/EOnCE port. It is sampled on the rising edge of TCK and has an on-chip pull-up resistor.                                            |