November 2006

1.2 GHz

500 MHz

3000 V/us

13.6 dB

120 mA

-53/-54 dBc

3.3V ±10%

# **General Description**

The LMH6555 is an ultra high speed differential line driver with 50 dB SFDR at 750 MHz. The LMH6555 features a fixed gain of 13.6 dB. An input to the device allows the output common mode voltage to be set independent of the input common mode voltage in order to simplify the interface to high speed differential input ADC's . A unique architecture allows the device to operate as a fully differential driver or as a singleended to differential converter.

The outstanding linearity and drive capability ( $100\Omega$  differential load) of this device is a perfect match for driving high speed analog-to-digital converters. When combined with the ADC081000/ADC08D1500, the LMH6555 forms an excellent 8-bit data acquisition system with analog bandwidths exceeding 1 GHz.

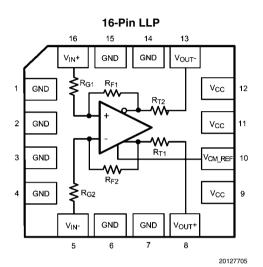

The LMH6555 is offered in a space saving 16-pin LLP package.

#### Features

Typical Unless Otherwise Specified:

- $-3 \text{ dB bandwidth } (V_{OUT} = 0.80_{PP})$

- ±0.5 dB gain flatness (V<sub>OUT</sub> = 0.80 V<sub>PP</sub>)

Slew rate

- Slew rate

- 2<sup>nd</sup>/3<sup>rd</sup> Harmonics (750 MHz)

- Fixed gain

- Supply current

Single supply of

- Single supply operation

- Adjustable common-mode output voltage

# Applications

- Differential ADC driver

- National Semiconductor ADC081000/ ADC08D1500 driver

- Single ended to differential converter

- Differential driver

- Intermediate frequency (IF) amplifier

- Communication receivers

- Oscilloscope front end

Single Ended to Differential Conversion

20127704

# Block Diagram

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance (Note 5)                    |            |

|-------------------------------------------|------------|

| Human Body Model                          | 2000V      |

| Machine Model                             | 200V       |

| V <sub>S</sub>                            | TBD        |

| Output Short Circuit Duration (one pin to |            |

| ground)                                   | Infinite   |

| Common Mode Input Voltage                 | -1V to TBD |

| Maximum Junction Temperature<br>Storage Temperature Range | +150°C<br>–65°C to +150°C |

|-----------------------------------------------------------|---------------------------|

| Soldering Information                                     |                           |

| Infrared or Convection (20 sec.)                          | 235°C                     |

| Wave Soldering (10 sec.)                                  | 260°C                     |

|                                                           |                           |

### Operating Ratings (Note 1)

| Temperature Range (Note 4)                      | –40°C to +85°C |

|-------------------------------------------------|----------------|

| Supply Voltage Range                            | +3.3V ±10%     |

| Package Thermal Resistance $(\theta_{JA})$ (Not | e 4)           |

| 16-Pin LLP                                      | 65°C/W         |

#### 3.3V Electrical Characteristics (Note 2)

Unless otherwise specified, all limits are guaranteed for  $T_A = 25^{\circ}$ C,  $V_{CM\_REF} = 1.2$ V, both inputs tied to 0.3V through  $50\Omega$  ( $R_{S1} \& R_{S2}$ ) each (Note 11),  $V_S = 3.3$ V,  $R_L = 100\Omega$  differential,  $V_{OUT} = 0.8 V_{PP}$ ; See Notes section for definition of terms used throughout the datasheet. **Boldface** limits apply at the temperature extremes.

| Symbol                                      | Parameter                                 | Conditions                                                                                    | Min<br>(Note 8)   | Typ<br>(Note 7) | Max<br>(Note 8)   | Units  |  |

|---------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------|-----------------|-------------------|--------|--|

| Differential AC                             | C Performance                             |                                                                                               | (                 |                 | (                 |        |  |

| SSBW                                        | -3 dB Bandwidth                           | $V_{OUT} = 0.25 V_{PP}$                                                                       |                   | 1200            |                   |        |  |

| LSBW                                        | _                                         | $V_{OUT} = 0.8 V_{PP}$                                                                        |                   | 1200            |                   | MHz    |  |

| GF_0.5                                      | ±0.5 dB Gain Flatness                     | $V_{OUT} = 0.8 V_{PP}$                                                                        |                   | 500             |                   | MHz    |  |

| Ph_Delta                                    | Phase Delta                               | Output Differential Phase Difference,<br>f = 400 MHz                                          |                   | TBD             |                   | deg    |  |

| TRS/TRL                                     | Rise/ Fall Time                           | $V_{OUT} = 0.4 V_{PP}$                                                                        |                   | 320             |                   | pS     |  |

| OS                                          | Overshoot                                 | $V_{OUT} = 0.4 V_{PP}$                                                                        |                   | 14              |                   | %      |  |

| SR                                          | Slew Rate                                 | 0.8V Step, 10% to 90%,(Note 6)                                                                |                   | 3000            |                   | V/µs   |  |

| t <sub>s</sub>                              | Settling Time                             | 0.8V Step, V <sub>OUT</sub> within ±0.1%                                                      |                   | TBD             |                   | ns     |  |

| A <sub>V_DIFF</sub>                         | Insertion Gain (IS <sub>21</sub> I)       | DC, $\frac{\Delta V_{OUT}}{\Delta V_{IN}}$<br>$\Delta V_{IN} = 50 \text{ mV}$                 | TBD<br><b>TBD</b> | 13.6            | TBD<br><b>TBD</b> | dB     |  |

| A <sub>V_VAR</sub> Insertion Gain Variation |                                           | $V_{CM_{REF}}$ Input Varied from 0.95V to<br>1.45V, $V_{OUT} = 0.8 V_{PP}$                    |                   | ±TBD            | ±TBD              | dB     |  |

| Distortion And                              | Noise Response                            |                                                                                               |                   |                 |                   |        |  |

| HD2_L                                       | 2 <sup>nd</sup> Harmonic Distortion       | 250 MHz (Note 12)                                                                             |                   | -60             |                   |        |  |

| HD2_M                                       |                                           | 500 MHz (Note 12)                                                                             |                   | -62             |                   | dBc    |  |

| HD2_H                                       |                                           | 750 MHz (Note 12)                                                                             |                   | -53             |                   |        |  |

| HD3_L                                       | 3 <sup>rd</sup> Harmonic Distortion       | 250 MHz (Note 12)                                                                             |                   | -67             |                   |        |  |

| HD3_M                                       |                                           | 500 MHz (Note 12)                                                                             |                   | -61             |                   | dBc    |  |

| HD3_H                                       |                                           | 750 MHz (Note 12)                                                                             |                   | -54             |                   |        |  |

| OIP3_L                                      | Output 3rd Order Intercept                | 70 MHz (Note 12)                                                                              |                   | TBD             |                   | dBm    |  |

| OIP3_H                                      |                                           | 250 MHz (Note 12)                                                                             |                   | TBD             |                   | dBiii  |  |

| OIM3                                        | Third Order Intermodulation<br>Distortion | f <sub>1</sub> = 70 MHz, f <sub>2</sub> = 70 MHz + 10 kHz,<br>P <sub>IN</sub> = TBD (Note 12) |                   | TBD             |                   | dBc    |  |

| e <sub>no</sub>                             | Output Referred Voltage Noise             | >1 MHz                                                                                        |                   | 24              |                   | nV/√Hz |  |

| NF                                          | Noise Figure                              | Relative to Differential Inputs                                                               |                   | TBD             |                   | dB     |  |

| Input Characte                              | eristics                                  |                                                                                               |                   |                 |                   |        |  |

| R <sub>IN</sub>                             | Input Resistance                          | Single Ended Input Drive                                                                      | TBD               | 50              | TBD               | Ω      |  |

| R <sub>IN_DIFF</sub>                        | Differential Input Resistance             | Differential Input Drive                                                                      | TBD               | 80              | TBD               | Ω      |  |

| C <sub>IN</sub>                             | Input Capacitance                         | Each Input to GND                                                                             |                   | 0.3             |                   | pF     |  |

| Symbol                     | Parameter                                    | Conditions                                                          | Min<br>(Note 8)    | Typ<br>(Note 7) | Max<br>(Note 8)    | Units |

|----------------------------|----------------------------------------------|---------------------------------------------------------------------|--------------------|-----------------|--------------------|-------|

| Output Charact             | eristics                                     |                                                                     | •                  | •               |                    |       |

| CMVR                       | Input Common Mode Voltage<br>Range           | $A_{V\_DIFF} - A_{V\_CM} \ge 30 \text{ dB}$                         | 0                  |                 | TBD                | V     |

| V <sub>OOS</sub>           | Output Offset Voltage                        | Differential Mode                                                   |                    | TBD             | ±100<br><b>TBD</b> | mV    |

| TCV <sub>OOS</sub>         | Output Offset Voltage<br>Average Drift       | (Note 9)                                                            |                    | ±200            | TBD                | µV/°C |

| R <sub>o</sub>             | Output Resistance                            | $R_{T1}$ and $R_{T2}$                                               | TBD                | 50              | TBD                | Ω     |

| V <sub>OUT</sub>           | Differential Output Voltage Swing            | $\Delta A_{V_{DIFF}} \leq 1 \text{ dB}$                             | TBD<br>TBD         | 800             |                    | mV    |

| V <sub>O_CM</sub>          | Output Common Mode Voltage<br>Range          | $V_{CM_{REF}}$ Input Varied,<br>$V_{OUT} = 0.80 V_{PP}$             | 0.95<br><b>TBD</b> |                 | 1.45<br><b>TBD</b> | V     |

| BAL_Error_DC               | Output Balance Error                         | DC, $\frac{\Delta V_{O_CM}}{\Delta V_{OUT}}$                        |                    | TBD             | TBD                |       |

| BAL_Error_AC               |                                              | f = 500 MHz,                                                        |                    | TBD             |                    | dB    |

| A <sub>V_CM</sub>          | Common Mode Gain                             | DC, $\Delta V_{O_{CM}} / \Delta V_{I_{CM}}$                         | TBD<br>TBD         | TBD             | TBD<br>TBD         | dB    |

| V <sub>CM_REF</sub> Charac | teristics                                    |                                                                     |                    |                 |                    |       |

| V <sub>OS_CM</sub>         | Output CM Offset Voltage                     | $V_{OS_{CM}} = V_{O_{CM}} - V_{CM_{REF}}$                           |                    | TBD             | ±50                | mV    |

| в_СМ                       | V <sub>CM_REF</sub> Bias Current             | 0.95V ≤ V <sub>CM REF</sub> ≤ 1.45V (Note 10)                       |                    | -100            | TBD                | μA    |

| R <sub>IN_CM</sub>         | V <sub>CM_REF</sub> Input Resistance         |                                                                     |                    | TBD             |                    | kΩ    |

| Gain_V <sub>CM_REF</sub>   | V <sub>CM_REF</sub> Input Gain to Output     | $\Delta V_{O_{CM}} / \Delta V_{CM_{REF}}$                           | TBD                | 0.99            | TBD                | V/V   |

| Power Supply               |                                              |                                                                     |                    |                 |                    |       |

| I <sub>S</sub>             | Supply Current                               | R <sub>S1</sub> & R <sub>S2</sub> Open (Note 3)                     | TBD<br>TBD         | 120             | TBD<br>TBD         | mA    |

| PSRR                       | Differential Power Supply<br>Rejection Ratio | DC, $\Delta V_{S} = \pm 0.3 V$ , $\Delta V_{OUT} / \Delta V_{S}$    | TBD<br>TBD         | 76              |                    | dB    |

| PSRR_CM                    | Common Mode PSRR                             | DC, $\Delta V_{S} = \pm 0.3 V$ , $\Delta V_{O_{CM}} / \Delta V_{S}$ | TBD<br>TBD         | TBD             |                    | dB    |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications, see the Electrical Characteristics tables.

Note 2: Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

Note 3: Total supply current is affected by the input voltages connected through R<sub>S1</sub> and R<sub>S2</sub>. Supply current tested with input removed.

Note 4: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$  and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_J_{MAX}) - T_A / \theta_{JA}$ . All numbers apply for package soldered directly into a 2 layer PC board with zero air flow.

Note 5: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC)

Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

Note 6: Slew Rate is the average of the rising and falling edges.

Note 7: Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 8: Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods.

Note 9: Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.

Note 10: Positive current is current flowing into the device.

Note 11: Quiescent device common mode input voltage is 0.3V.

Note 12: Distortion data taken under single ended input condition.

# Ordering Information

| Package    | Part Number | Package Marking | Transport Media          | NSC Drawing |

|------------|-------------|-----------------|--------------------------|-------------|

| 16-Pin LLP | LMH6555SQ   |                 | 1k Units Tape and Reel   | SQA16A      |

|            | LMH6555SQX  | L6555SQ         | 4.5k Units Tape and Reel | JUAIDA      |

# Definition of Terms and Specifications (Alphabetical order)

Unless otherwise specified,  $V_{CM\_REF} = 1.2V$

| 1.  | 1. A <sub>V_CM</sub> (dB)                     | Change in the output common mode voltage ( $\Delta V_{O_{CM}}$ ) with respect to the change in input common mode voltage ( $\Delta V_{I_{CM}}$ )                                                                                                                                                                                                                |  |  |

|-----|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2.  | A <sub>V_DIFF</sub> (dB)                      | Insertion gain from a single ended 50 $\Omega$ (or 100 $\Omega$ differential) source to the differential output ( $\Delta V_{OUT}$ )                                                                                                                                                                                                                            |  |  |

| 3.  | ΔA <sub>V_DIFF</sub> (dB)                     | Variation in insertion gain ( $A_{V DIFF}$ ) with input signal change ( $\Delta V_{IN}$ )                                                                                                                                                                                                                                                                       |  |  |

| 4.  | A <sub>V_VAR</sub> (dB)                       | Variation of insertion gain ( $A_{V_{DIFF}}$ ) with $V_{CM_{REF}}$ input change ( $\Delta V_{CM_{REF}}$ ). Calculated as the change in $A_{V_{DIFF}}$ (dB) at various $V_{CM_{REF}}$                                                                                                                                                                            |  |  |

| 5.  | CMVR (V)                                      | Range of input common mode voltage ( $V_{I_{CM}}$ ) where the insertion gain ( $A_{V_{DIFF}}$ ) is 30 dB large than common mode gain ( $A_{V_{CM}}$ ) and hence the amplifier's output is dominated by its differential output                                                                                                                                  |  |  |

| 6.  | Gain_VCM_REF (V/V)                            | Variation in output common mode voltage ( $\Delta V_{O_{CM}}$ ) with respect to change in $V_{CM_{REF}}$ input ( $\Delta V_{CM_{REF}}$ ) with maximum differential output                                                                                                                                                                                       |  |  |

| 7.  | Pin (dBm referenced to 50Ω)                   | Input power associated with each of the tones for OIM3 testing                                                                                                                                                                                                                                                                                                  |  |  |

| 8.  | PSRR (dB)                                     | Differential output change ( $\Delta V_{OUT}$ ) with respect to the power supply voltage change ( $\Delta V_S$ ) with nominal differential output                                                                                                                                                                                                               |  |  |

| 9.  | PSRR_CM (dB)                                  | Output common mode voltage change ( $\Delta V_{O_CM}$ ) with respect to the change in the power supply voltage ( $\Delta V_S$ )                                                                                                                                                                                                                                 |  |  |

| 10. | R <sub>IN</sub> (Ω)                           | Single ended input impedance to ground                                                                                                                                                                                                                                                                                                                          |  |  |

| 11. | $R_{IN\_DIFF}(\Omega)$                        | Differential input impedance                                                                                                                                                                                                                                                                                                                                    |  |  |

| 12. | $R_{L}(\Omega)$                               | Differential output load                                                                                                                                                                                                                                                                                                                                        |  |  |

| 13. | R <sub>O</sub> (Ω)                            | Equivalent to R <sub>T1</sub> & R <sub>T2</sub>                                                                                                                                                                                                                                                                                                                 |  |  |

| 14. | R <sub>S1</sub> , R <sub>S2</sub> (Ω)         | Source impedance to V <sub>IN+</sub> and V <sub>IN-</sub> respectively                                                                                                                                                                                                                                                                                          |  |  |

| 15. | $R_{T1}, R_{T2} (\Omega)$                     | Output impedance looking into each output                                                                                                                                                                                                                                                                                                                       |  |  |

| 16. | V <sub>CM_REF</sub> (V)                       | Device input pin voltage which controls output common mode                                                                                                                                                                                                                                                                                                      |  |  |

| 17. | $\Delta V_{CM_{REF}}(V)$                      | Change in the V <sub>CM REF</sub> input voltage                                                                                                                                                                                                                                                                                                                 |  |  |

| 18. | V <sub>I_CM</sub> (V)                         | DC average of the inputs $(V_{IN+}, V_{IN-})$                                                                                                                                                                                                                                                                                                                   |  |  |

| 19. | $\Delta V_{I_{CM}}(V)$                        | Variation in input common mode voltage (V <sub>I CM</sub> )                                                                                                                                                                                                                                                                                                     |  |  |

| 20. | V <sub>IN*</sub> , V <sub>IN-</sub> (V)       | Device input pin voltages                                                                                                                                                                                                                                                                                                                                       |  |  |

| 21. | ΔV <sub>IN</sub> (V)                          | Terminated (50 $\Omega$ for single ended and 100 $\Omega$ for differential) generator voltage                                                                                                                                                                                                                                                                   |  |  |

| 22. | V <sub>O_CM</sub> (V)                         | Output common mode voltage (DC average of V <sub>OUT+</sub> and V <sub>OUT-</sub> )                                                                                                                                                                                                                                                                             |  |  |

| 23. | $\Delta V_{O_{CM}}(V)$                        | Variation in output common mode voltage (V <sub>O CM</sub> )                                                                                                                                                                                                                                                                                                    |  |  |

| 24. | $\frac{\Delta V_{O_CM}}{\Delta V_{OUT}} (dB)$ | Balance Error. Measure of the output swing balance of $V_{OUT+}$ and $V_{OUT-}$ , as reflected on the output common mode voltage ( $V_{O_{-}CM}$ ), relative to the differential output swing ( $V_{OUT}$ ). Calculated as output common mode voltage change ( $\Delta V_{O_{-}CM}$ ) divided into the output differential voltage change ( $\Delta V_{OUT}$ ). |  |  |

| 25. | $rac{V_{O_{CM}}}{V_{OUT}}$ (dB)              | AC version of the DC balance error $\left(\frac{\Delta V_{O_CM}}{\Delta V_{OUT}}\right)$ test                                                                                                                                                                                                                                                                   |  |  |

| 26. | V <sub>OOS</sub> (V)                          | DC Offset Voltage. Differential output voltage measured with both inputs grounded through $50\Omega$                                                                                                                                                                                                                                                            |  |  |

| <    |

|------|

| Т    |

| ŋ    |

| ប្ចា |

| Ϋ́   |

| UI.  |

|     | <b>1</b>                      |                                                                                                                    |

|-----|-------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 27. | V <sub>OS_CM</sub> (V)        | Difference between the output common mode voltage ( $V_{O_{CM}}$ ) and the voltage on the                          |

|     |                               | $V_{\text{CM}\_\text{REF}}$ input, for the allowable $V_{\text{CM}\_\text{REF}}$ range                             |

| 28. | V <sub>OUT</sub> (V)          | Differential Output Voltage (V <sub>OUT*</sub> - V <sub>OUT-</sub> ) (Corrected for DC offset (V <sub>OOS</sub> )) |

| 29. | ΔV <sub>OUT</sub> (V)         | Change in the differential output voltage (Corrected for DC offset $(V_{OOS})$ )                                   |

| 30. | $V_{OUT^{+}}, V_{OUT^{-}}(V)$ | Device output pin voltages                                                                                         |

| 31. | V <sub>S</sub> (V)            | Supply Voltage (V+ - V-)                                                                                           |

| 32. | $\Delta V_{S}(V)$             | Change in V <sub>CC</sub> supply voltage                                                                           |

# **Connection Diagram**

### **Application Information**

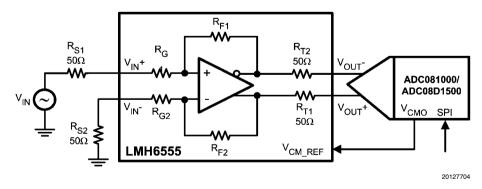

The LMH6555 consists of three individual amplifiers: The V<sub>OUT+</sub> driver, V<sub>OUT-</sub> driver, and the common mode amplifier. Being a differential amplifier, the LMH6555 will not respond to the input common mode input (as long as it is within its input common mode range) and instead the output common mode is forced by the built-in common mode amplifier with V<sub>CM REF</sub> as its input. As shown in *Figure 1* below, the VCMO

of most differential high speed ADC's will be tied to the V<sub>CM\_REF</sub> input of the LMH6555 for direct output common mode control. In some cases, the output drive capability of the ADC VCMO output may need an external buffer (not shown) to increase its current capability in order to drive the V<sub>CM\_REF</sub> pin. The LMH6555 Electrical Characteristics table shows the gain (A<sub>V\_CM</sub>) and the offset (V<sub>OS\_CM</sub>) from the V<sub>CM\_REF</sub> to the device output common mode.

FIGURE 1. Single Ended to Differential Conversion

The single ended AC input and output impedance of the LMH6555 I/O pins are close to  $50\Omega$  and are also specified in the Electrical Characteristics table (R<sub>IN</sub> and R<sub>O</sub>). With differential input drive, the differential input impedance (R<sub>IN\_DIFF</sub>) will be close to  $80\Omega$ .

The device nominal input common mode voltage is close to 0.3V at V<sub>IN+</sub> and V<sub>IN</sub> with a weak relationship to the V<sub>CM\_REF</sub> voltage. Thus, the input source will experience a DC current which is dependant on its DC voltage. Because of this, the differential output offset voltage is influenced by the matching between R<sub>S1</sub> and R<sub>S2</sub> under DC and AC conditions. So, for example, in a single ended input condition, if the signal source is AC coupled to one input, the undriven input needs to also be AC coupled.

In applications where very low output offset is required, adjusting the value of  $R_{S2}$  (the input which is not driven) can be an effective method of trimming the output offset voltage of

the LMH6555 in a single ended input configuration. The nominal value of  $R_{S1}$  and  $R_{S2}$  on the other hand will affect the insertion gain. The LMH6555 can also be used with the input signal AC coupled. In this case, the coupling capacitors need to be large enough to not block the frequency content below  $(1/2\pi R_{\rm IN}C) Hz.$

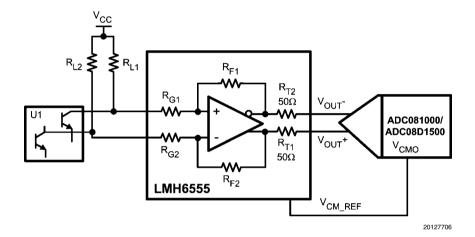

The single ended output impedance of the LMH6555 is 50 $\Omega$ . The LMH6555 Electrical Characteristics shows the device performance with 100 $\Omega$  differential output load, as would be the case if a device such as the ADC081000 were being driven. As shown in *Figure 2* below, some applications can benefit from using the LMH6555 to interface a Class A type differential output device (U1) to a high speed ADC. In this application, the LMH6555 performs the task of buffering and amplifying the signal to properly drive the 100 $\Omega$  differential input impedance of the ADC.

FIGURE 2. Differential Buffering and Amplification

In this application, U1's DC common mode output will be affected by the LMH6555 input common mode voltage through  $R_{G}$  and  $R_{L}$ . The equivalent load to the driver Collector within U1 would be the combination of  $R_{L}$  and  $R_{IN\_DIFF}$  (≅80 $\Omega$ ). Series isolation resistors (not shown) between U1 outputs and LMH6555 input pins would offer additional isolation at the expense of more signal loss. Alternatively, input AC coupling could have been used to alleviate the common mode concerns.

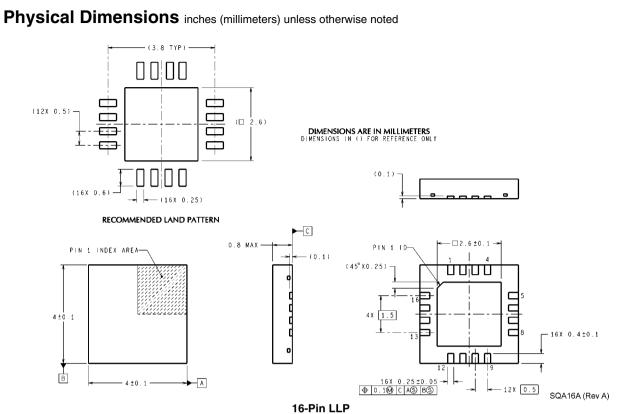

#### EXPOSED PAD LLP PACKAGE

The LMH6555 is packaged in a thermally enhanced package. The exposed pad (device bottom) is connected to the GND pins. It is recommended, but not necessary, that the exposed pad be connected to the supply ground plane. The thermal dissipation of the device is largely dependent on the connection of this pad. The exposed pad should be attached to as much copper on the circuit board as possible, preferably external copper. However, it is very important to maintain good high speed layout practices when designing a system board. Here is a link to more information on the National 16 pin LLP package:

http://www.national.com/packaging/folders/sqa16a.html

NS Package Number SQA16A

LMH6555

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2006 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tei: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tei: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560