# Am79C978A

## PCnet<sup>™</sup>- Home Single-Chip 1/10 Mbps PCI Home Networking Controller

## **DISTINCTIVE CHARACTERISTICS**

- Fully integrated 1 Mbps HomePNA Physical Layer (PHY) as defined by Home Phoneline Networking Alliance (HomePNA) specification 1.1

- Optimized for home networking applications over ordinary copper telephone wire

- In-band control features

- Adjustable power and speed levels

- 32 bits of reserved in-band messaging piggybacked on Ethernet packet

- Register programmable features

- Power control

- Performance registers

- Speed control

- Major frame timing parameters programmable: ISBI, AID ISBI, pulse width, inter-symbol time

- Fully integrated 10 Mbps PHY interface

- Comprehensive Auto-Negotiation implementation

- Full-duplex capability

- Optimized for 10BASE-T applications

- Integrated Fast Ethernet controller for the Peripheral Component Interconnect (PCI) bus

- 32-bit glueless PCI host interface

- Supports PCI clock frequency from DC to 33 MHz independent of network clock

- Supports network operation with PCI clock from 15 MHz to 33 MHz

- High performance bus mastering architecture with integrated Direct Memory Access (DMA) Buffer Management Unit for low CPU and bus utilization

- PCI draft specification revision 2.2 compliant

- Supports PCI Subsystem/Subvendor ID/ Vendor ID programming through the EEPROM interface

- Supports both PCI 5.0-V and 3.3-V signaling environments

- Plug and Play compatible

- Supports an unlimited PCI burst length

- Big endian and little endian byte alignments supported

- Implements optional PCI power management event (PME) pin

- Dual-speed CSMA/CD (10 Mbps and 100 Mbps) Media Access Controller (MAC) compliant with IEEE/ANSI 802.3 Ethernet standard

- Compliant with HomePNA specification 1.1

- Media Independent Interface (MII) for connecting external 10/100 Mbps transceivers

- IEEE 802.3u compliant MII

- Intelligent Auto-Poll<sup>™</sup> external PHY status monitor and interrupt

- Supports both auto-negotiable and nonauto-negotiable external PHYs

- Supports 10BASE-T, 100BASETX/FX, 100BASET4, and 100BASET2 IEEE 802.3 compliant MII PHYs at full-duplex or halfduplex

- Full-duplex operation supported on the MII port with independent Transmit (TX) and Receive (RX) channels

- Supports PC98/PC99 and Net PC specifications

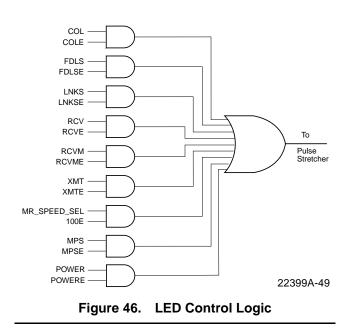

- Implements full OnNow features including pattern matching and link status wake-up events

- Implements Magic Packet<sup>™</sup> mode

- Magic Packet mode and the physical address loaded from EEPROM at power up without requiring PCI clock

- Supports PCI Bus Power Management Interface specification revision 1.1

- Supports Advanced Configuration and Power Interface (ACPI) specification version 1.0

- Supports Network Device Class Power Management specification version 1.0a

- Independent internal TX and RX FIFOs

- Programmable FIFO watermarks for both TX and RX operations

- RX frame queuing for high latency PCI bus host operation

- Programmable allocation of buffer space between RX and TX queues

- Extensive programmable internal/external loopback capabilities

- EEPROM interface supports jumperless design and provides through-chip programming

- Supports full programmability of half-/fullduplex operation through EEPROM mapping

- Programmable PHY reset output pin capable of resetting external PHY without the need for buffering

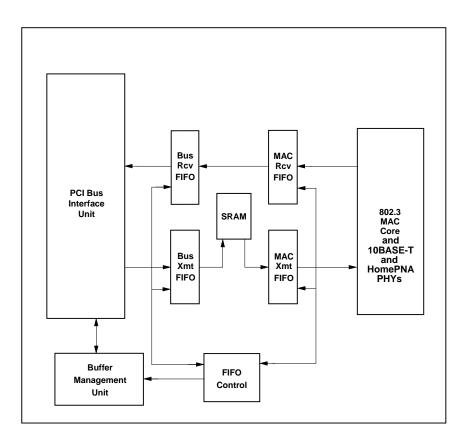

- Extensive programmable LED status support

- Look-Ahead Packet Processing (LAPP) data handling technique reduces system overhead

by allowing protocol analysis to begin before the end of a receive frame

- Includes Programmable Inter Packet Gap (IPG) to address less network aggressive MAC controllers

- Offers the Modified Back-Off algorithm to address the Ethernet Capture Effect

- IEEE 1149.1-compliant JTAG Boundary Scan test access port interface and NAND tree test mode for board-level production connectivity test

- Software compatible with AMD's PCnet<sup>™</sup> Family and LANCE/C-LANCE register and descriptor architecture

- Very low power consumption

- +3.3 V power supply along with 5 V tolerant I/Os enable broad system compatibility

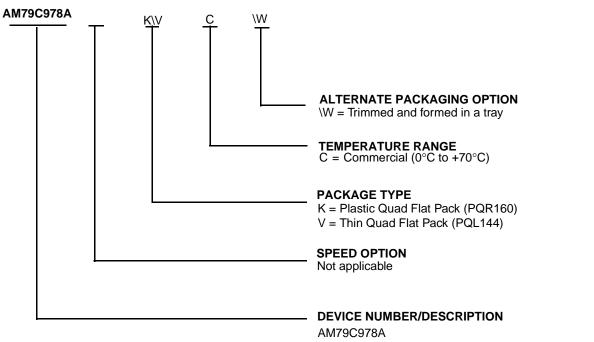

- Available in 144-pin TQFP and 160-pin PQFP packages

## **GENERAL DESCRIPTION**

The Am79C978A controller is the first in a series of home networking products from AMD. The Am79C978A controller is fabricated in an advanced low power 3.3 V CMOS process to provide low operating current for power sensitive applications.

The Am79C978A controller contains an Ethernet Controller based on the Am79C971 Fast Ethernet controller, a physical layer device for supporting the 802.3 standard for 10BASE-T, and a physical layer device for data networking at speeds up to 1 Mbps over ordinary residential telephone wiring.

The integrated PCI Ethernet controller is a highly integrated 32-bit full-duplex, 10/100 Mbps Ethernet controller solution designed to address high-performance system application requirements. It is a flexible busmastering device that can be used in any application, including network ready PCs. The bus master architecture provides high data throughput and low CPU and system bus utilization.

The integrated Ethernet transceiver is a physical layer device supporting the IEEE 802.3 standards for 10BASE-T. It provides all of the PHY layer functions required to support 10 Mbps data transfer speeds.

The integrated HomePNA transceiver is a physical layer device that enables data networking at speeds up to 1 Mbps over common residential phone wiring regardless of topology and without disrupting telephone (POTS) service.

The 32-bit multiplexed bus interface unit provides a direct interface to the PCI local bus, simplifying the design of an Ethernet or home network node in a PC system. The device has built-in support for both little and big endian byte alignment. The integrated home networking controller's advanced CMOS design allows the bus interface to be connected to either a +5.0 V or a +3.3 V signaling environment. A compliant IEEE 1149.1 JTAG test interface for board level testing is also provided, as well as a NAND tree test structure for those systems that do not support the JTAG interface.

The integrated Am79C978A home networking controller is also compliant with the PC98, PC99, and Net PC specifications. It includes the full implementation of the Microsoft OnNow and ACPI specifications, which are backward compatible with Magic Packet technology, and is compliant with the PCI Bus Power Management Interface specification by supporting the four power management states (D0, D1, D2, and D3), the optional PME pin, and the necessary configuration and data registers.

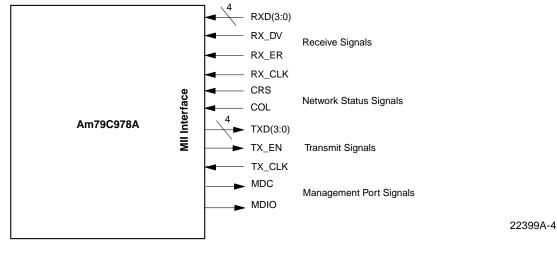

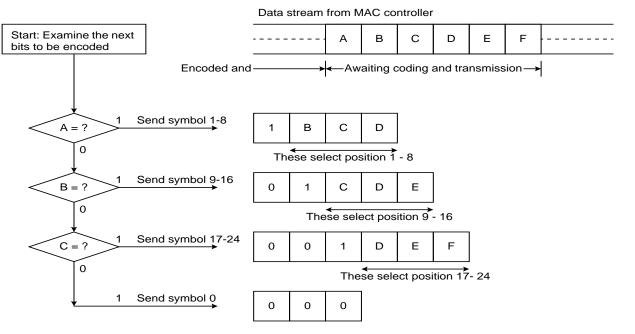

The integrated Am79C978A home networking controller is a complete Ethernet or home network node integrated into a single VLSI device. It contains a bus interface unit, a Direct Memory Access (DMA) Buffer Management Unit, an ISO/IEC 88023 (IEEE 802.3) compliant Media Access Controller (MAC), a Transmit FIFO and a large Receive FIFO, and an IEEE 802.3u compliant MII. Both IEEE 802.3 compliant full-duplex and half-duplex operations are supported on the MII interface. 10/100 Mbps operation is supported through the MII interface.

The integrated Am79C978A home networking controller is register compatible with the LANCE (Am7990) and C-LANCE (Am79C90) Ethernet controllers and all Ethernet controllers in the PCnet Family (*except* ILACC<sup>™</sup> (Am79C900)), including PCnet-ISA (Am79C960), PCnet-ISA+ (Am79C961), PCnet-ISA II (Am79C961A), PCnet-32 (Am79C965A), PCnet-PCI (Am79C970), PCnet-PCI II (Am79C970A), PCnet*FAST* (Am79C971), and PCnet-*FAST*+ (Am79C972). The Buffer Management Unit supports the LANCE and PCnet descriptor software models.

The integrated Am79C978A controller supports autoconfiguration in the PCI configuration space. Additional integrated controller configuration parameters, including the unique IEEE physical address, can be read from an external non-volatile memory (EEPROM) immediately following system reset.

In addition, the Am79C978A controller provides programmable on-chip LED drivers for transmit, receive, collision, link integrity, Magic Packet status, speed, activity, power output, address match, full-duplex, or 100 Mbps status.

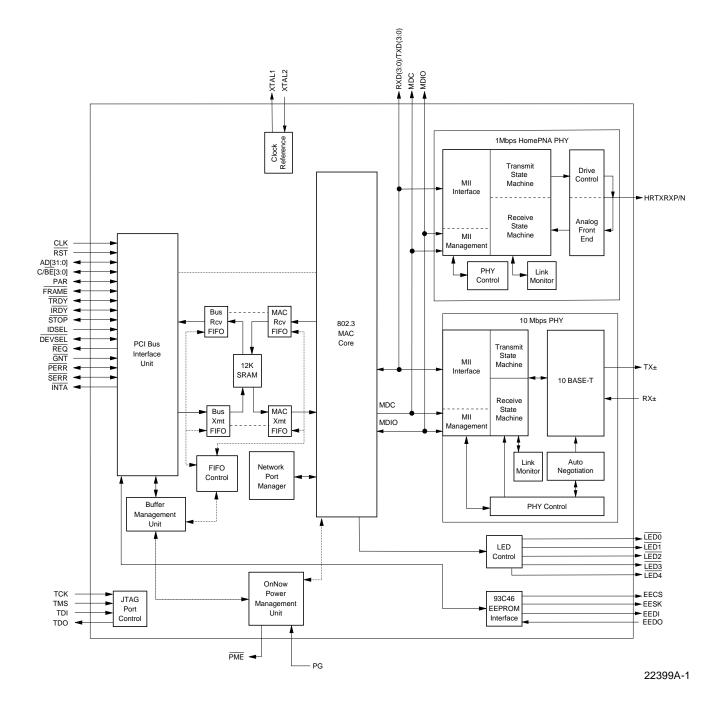

## **BLOCK DIAGRAM**

## TABLE OF CONTENTS

| AM79C978A1                                    |

|-----------------------------------------------|

| DISTINCTIVE CHARACTERISTICS1                  |

| GENERAL DESCRIPTION                           |

| BLOCK DIAGRAM                                 |

| TABLE OF CONTENTS                             |

| RELATED AMD PRODUCTS                          |

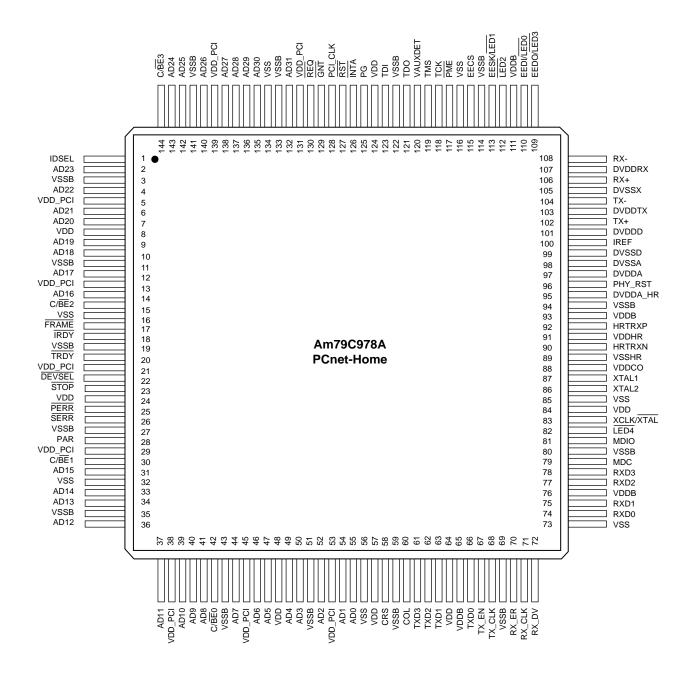

| CONNECTION DIAGRAM (144 TQFP)11               |

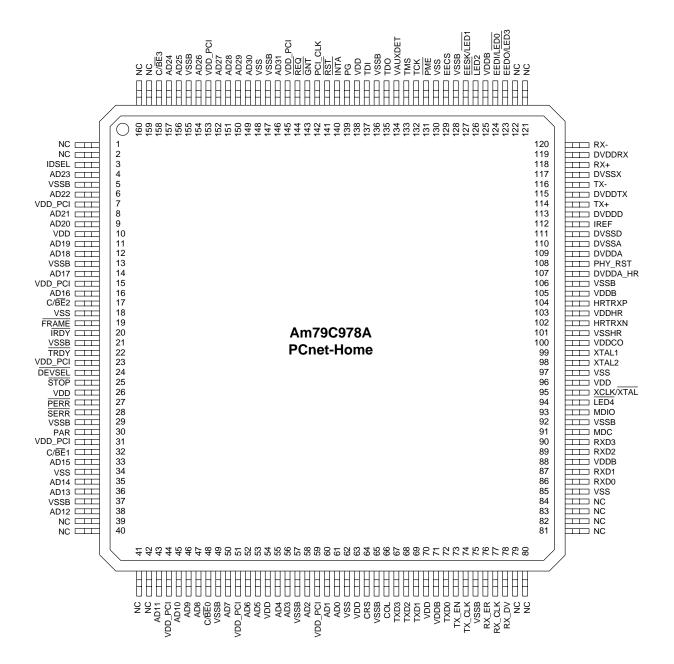

| CONNECTION DIAGRAM (160 PQFP)                 |

| PIN DESIGNATIONS (PQL144)                     |

| Listed By Pin Number                          |

| PIN DESIGNATIONS (PQR160)14                   |

| Listed By Pin Number                          |

| PIN DESIGNATIONS (PQL144)                     |

| Listed By Group                               |

| PIN DESIGNATIONS (PQR160)                     |

| Listed By Group                               |

| PIN DESIGNATIONS                              |

| Listed By Driver Type                         |

| ORDERING INFORMATION                          |

| Standard Products                             |

| PIN DESCRIPTIONS                              |

| PCI Interface                                 |

| Magic Packet Interface                        |

| Board Interface                               |

| EEPROM Interface                              |

| MII Interface                                 |

| IEEE 1149.1 (1990) Test Access Port Interface |

| Ethernet Network Interfaces                   |

| HomePNA PHY Network Interface                 |

| Clock Interface                               |

| External Crystal Characteristics              |

| Power Supply                                  |

| BASIC FUNCTIONS                               |

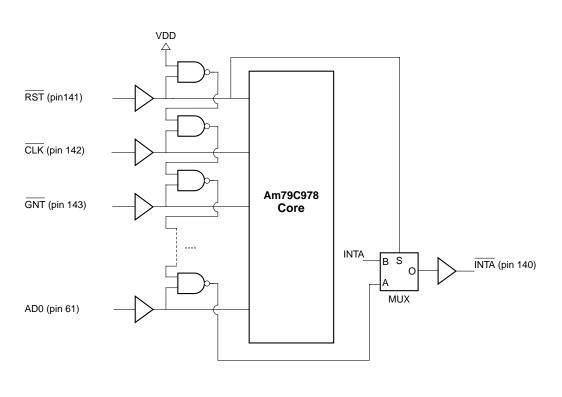

| System Bus Interface                          |

| Software Interface                            |

| Network Interfaces                            |

| Media Independent Interface                   |

| 10BASE-T PHY                                  |

| PCI and JTAG Configuration Information        |

| Slave Bus Interface Unit                      |

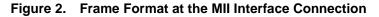

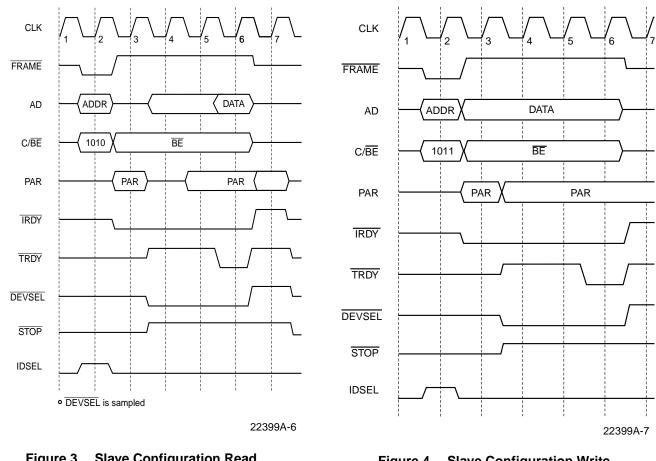

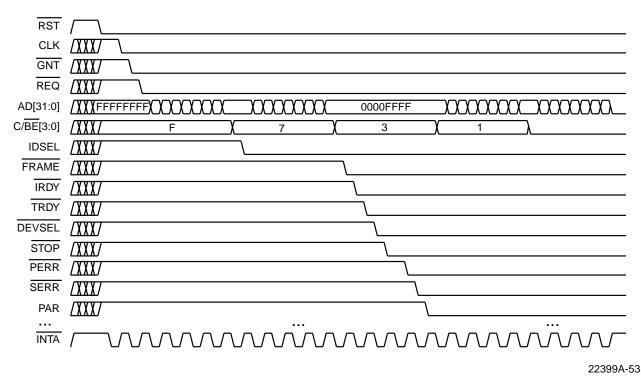

| Slave Configuration Transfers                 |

| Slave I/O Transfers                           |

| Expansion ROM Transfers                       |

| Slave Cycle Termination                       |

| Parity Error Response                         |

| Master Bus Interface Unit                     |

| Buffer Management Unit                        |

| Software Interrupt Timer                      |

| 10/100 Media Access Controller                |

| Transmit Operation                            |

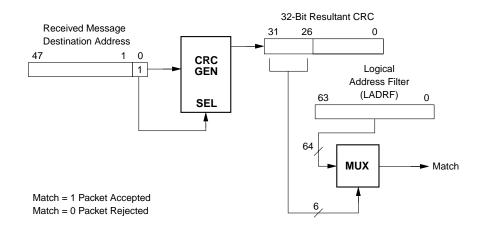

| Receive Operation                             |

| Loopback Operation                            |

| PHY/MAC Interface                             |

| 10BASE-T Physical Layer                       |

| Auto-Negotiation                              |

| DETAILED FUNCTIONS                            |

| 1 Mbps HomePNA PHY                                 |

|----------------------------------------------------|

| HomePNA PHY Medium Interface74                     |

| Management Interfaces                              |

| EEPROM Interface                                   |

| LED Support                                        |

| Power Savings Mode                                 |

| Magic Packet Mode                                  |

| IEEE 1149.1 (1990) Test Access Port Interface      |

| NAND Tree Testing                                  |

| Reset                                              |

| Software Access                                    |

| USER ACCESSIBLE REGISTERS                          |

| PCI Configuration Registers                        |

| RAP Register                                       |

| Control and Status Registers (CSRs)                |

| Bus Configuration Registers (BCRs)                 |

| 10BASE-T PHY Management Registers (TBRs)           |

| 1 Mbps HomePNA PHY Internal Registers              |

| Initialization Block                               |

| Receive Descriptors                                |

| Transmit Descriptors                               |

| REGISTER SUMMARY                                   |

| PCI Configuration Registers                        |

| Control and Status Registers                       |

| Bus Configuration Registers                        |

| 10BASE-T PHY Management Registers                  |

| 1 Mbps HomePNA PHY Management Registers            |

| REGISTER PROGRAMMING SUMMARY                       |

| Am79C978A Programmable Registers                   |

| AIM/9C976A Programmable Registers                  |

| OPERATING RANGES                                   |

| Commercial (C) Devices                             |

| DC CHARACTERISTICS OVER COMMERCIAL OPERATING       |

| RANGES UNLESS OTHERWISE SPECIFIED                  |

| SWITCHING CHARACTERISTICS: BUS INTERFACE           |

| 10BASE-T Mode                                      |

|                                                    |

| Power Supply Current                               |

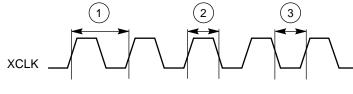

| External Clock                                     |

| PMD Interface                                      |

| 10BASE-T                                           |

|                                                    |

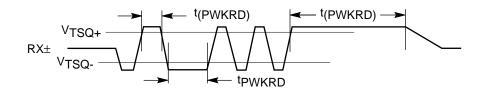

| SWITCHING WAVEFORMS                                |

| Key to Switching Waveforms                         |

| SWITCHING TEST CIRCUITS                            |

| SWITCHING WAVEFORMS: STSTEM BOS INTERFACE          |

| PHYSICAL DIMENSIONS*                               |

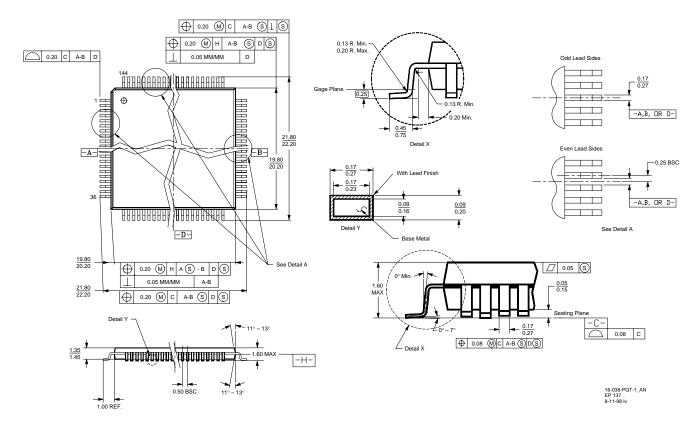

| PQL144                                             |

| Thin Quad Flat Pack (measured in millimeters)      |

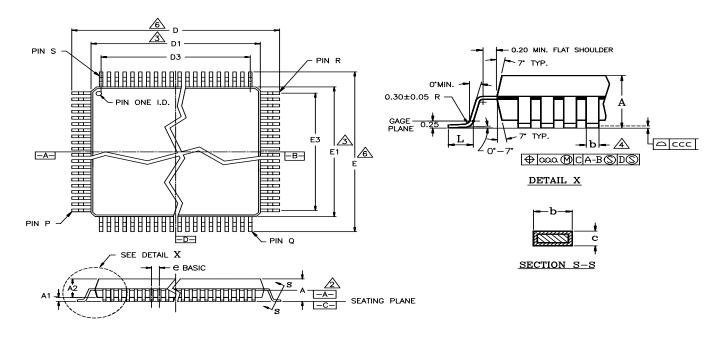

| PQR160                                             |

| PQR 160                                            |

| APPENDIX A — ALTERNATIVE METHOD FOR INITIALIZATION |

| APPENDIX A — ALTERNATIVE METHOD FOR INITIALIZATION |

| Introduction                                       |

| Outline of LAPP Flow                               |

| INDEX                                              |

|                                                    |

| LIST OF FIGURES                                                          |

|--------------------------------------------------------------------------|

| Figure 1. Media Independent Interface                                    |

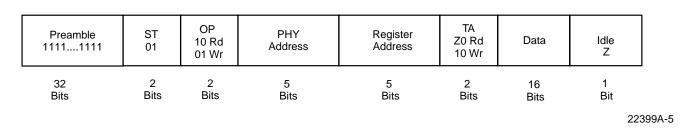

| Figure 2. Frame Format at the MII Interface Connection                   |

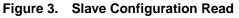

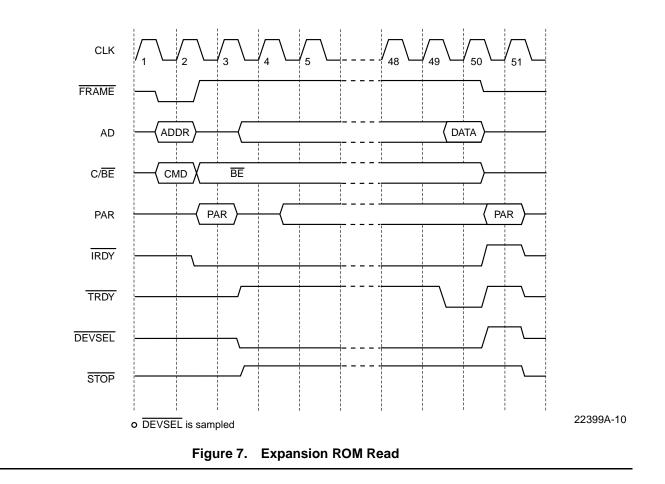

| Figure 3. Slave Configuration Read                                       |

| Figure 4. Slave Configuration Write                                      |

| Figure 5. Slave Read Using I/O Command                                   |

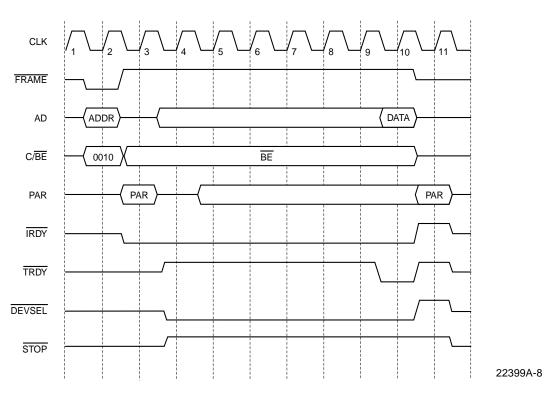

| Figure 6. Slave Write Using Memory Command                               |

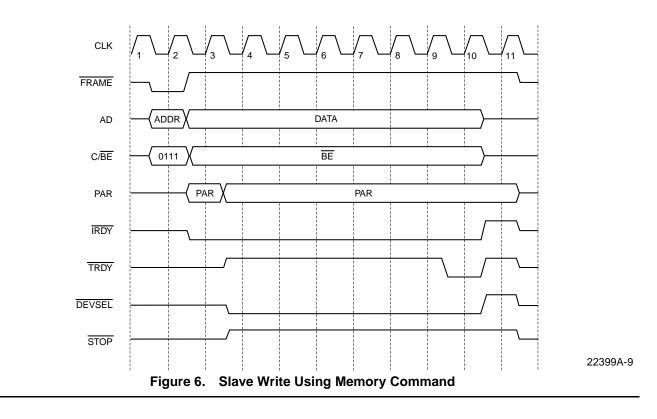

| Figure 7. Expansion ROM Read                                             |

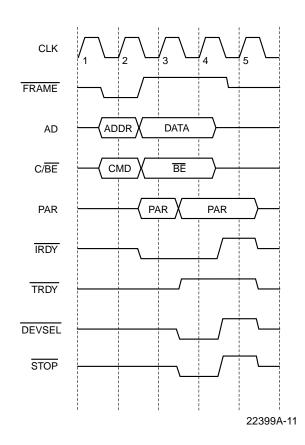

| Figure 8. Disconnect of Slave Cycle When Busy                            |

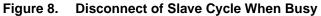

| Figure 9. Disconnect of Slave Burst Transfer - No Host Wait States       |

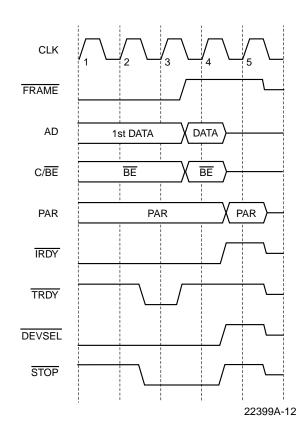

| Figure 10. Disconnect of Slave Burst Transfer - Host Inserts Wait States |

| Figure 11. Address Parity Error Response                                 |

| Figure 12. Slave Cycle Data Parity Error Response                        |

| Figure 13. Bus Acquisition                                               |

| Figure 14. Non-Burst Read Transfer    40                                 |

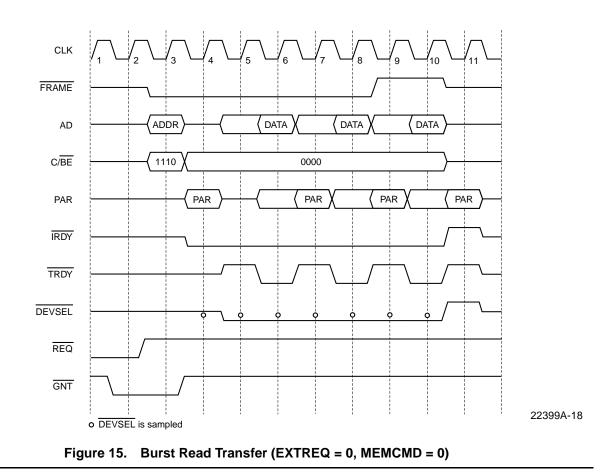

| Figure 15. Burst Read Transfer (EXTREQ = 0, MEMCMD = 0)                  |

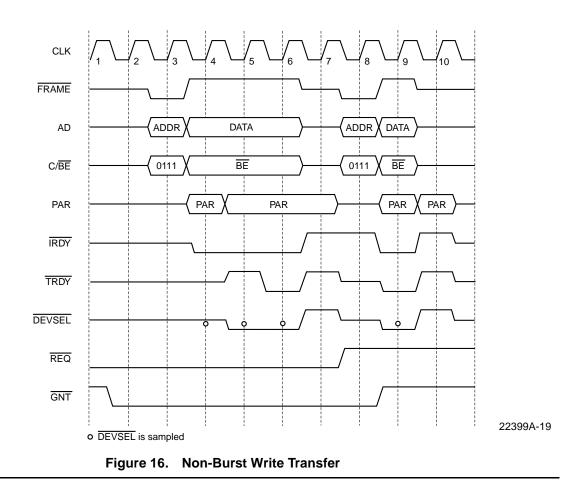

| Figure 16. Non-Burst Write Transfer                                      |

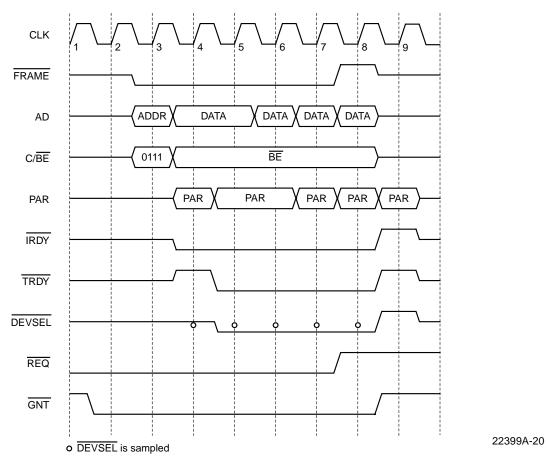

| Figure 17. Burst Write Transfer (EXTREQ = 1)                             |

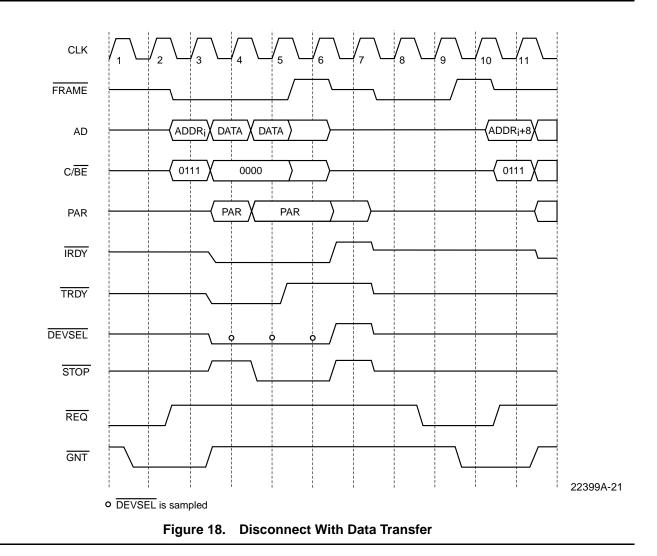

| Figure 18. Disconnect With Data Transfer                                 |

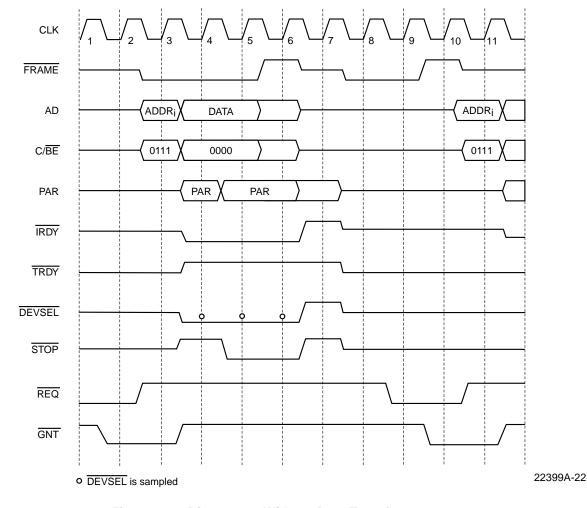

| Figure 19. Disconnect Without Data Transfer                              |

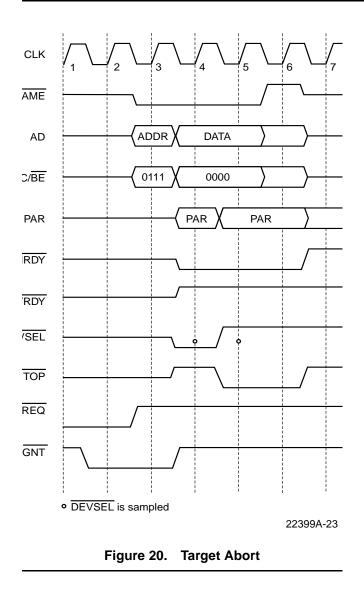

| Figure 20. Target Abort                                                  |

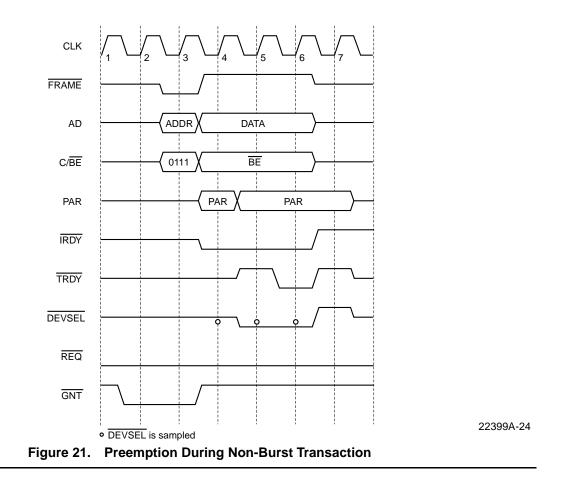

| Figure 21. Preemption During Non-Burst Transaction                       |

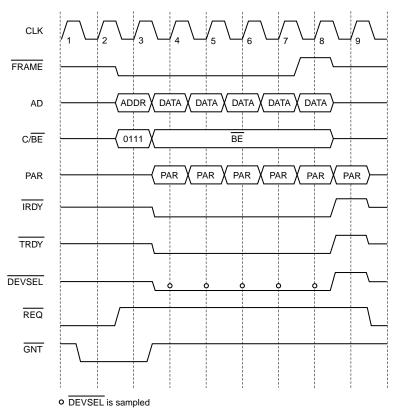

| Figure 22. Preemption During Burst Transaction                           |

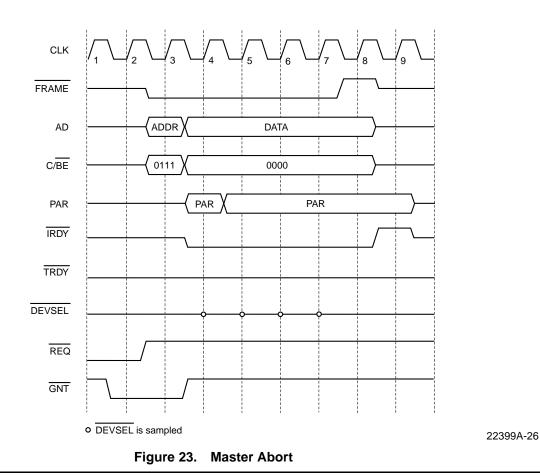

| Figure 23. Master Abort                                                  |

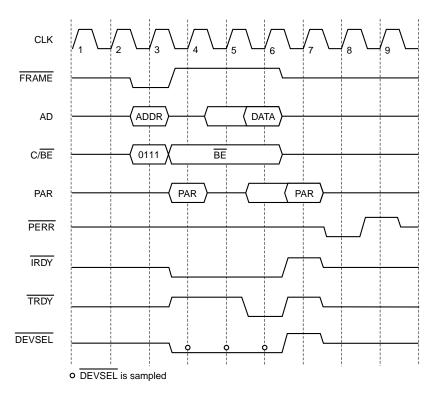

| Figure 24. Master Cycle Data Parity Error Response                       |

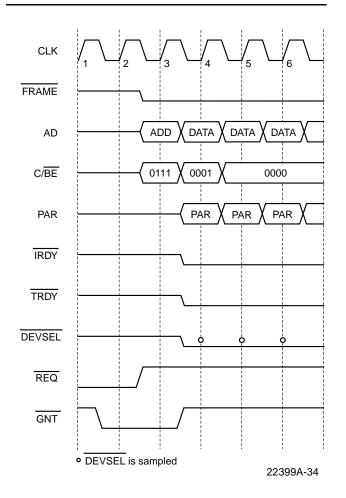

| Figure 25. Initialization Block Read In Non-Burst Mode                   |

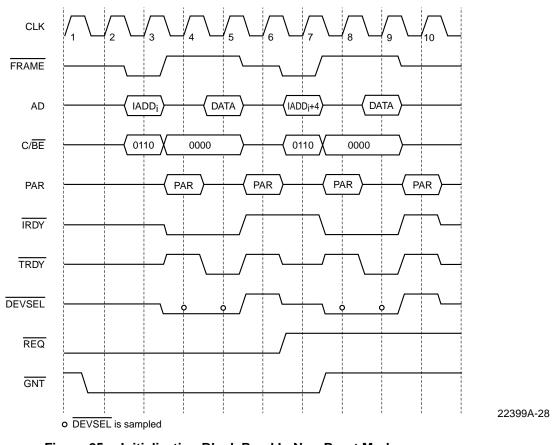

| Figure 26. Initialization Block Read In Burst Mode                       |

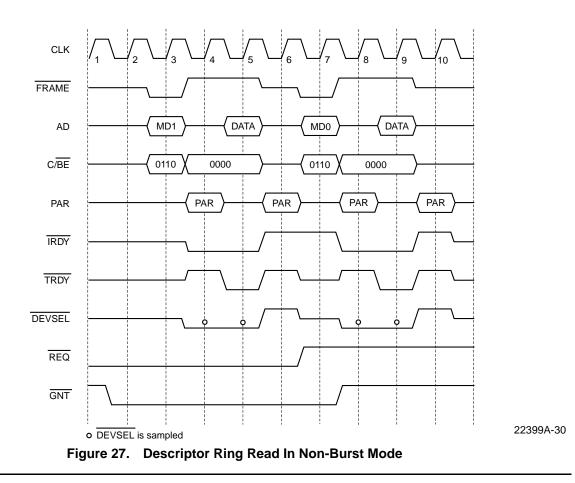

| Figure 27. Descriptor Ring Read In Non-Burst Mode                        |

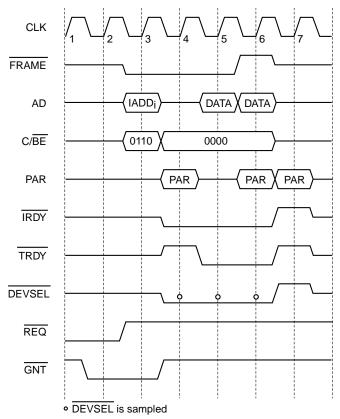

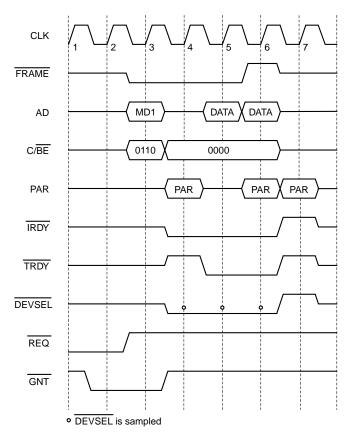

| Figure 28. Descriptor Ring Read In Burst Mode    52                      |

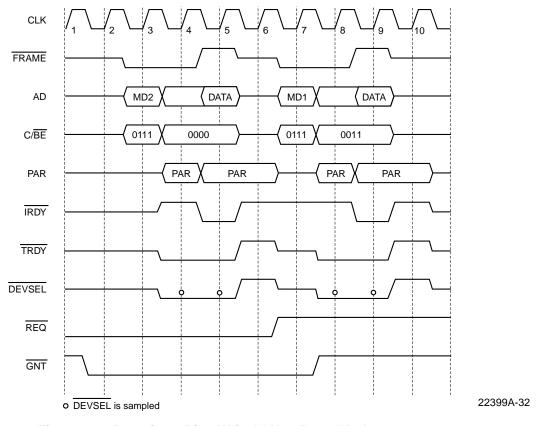

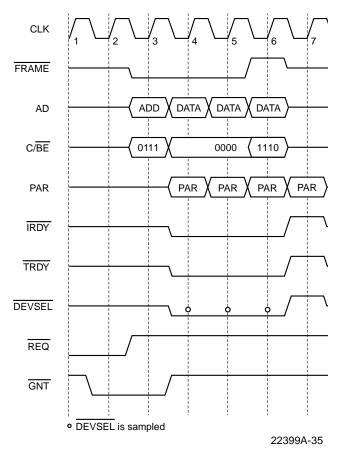

| Figure 29. Descriptor Ring Write In Non-Burst Mode    53                 |

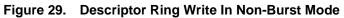

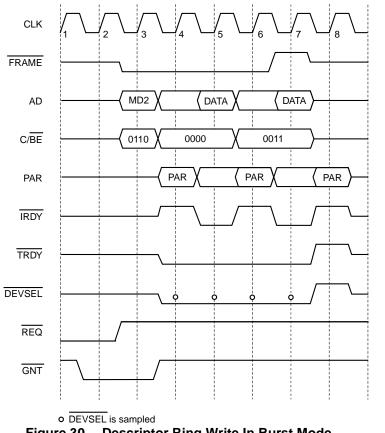

| Figure 30. Descriptor Ring Write In Burst Mode    53                     |

| Figure 31. FIFO Burst Write at Start of Unaligned Buffer                 |

| Figure 32. FIFO Burst Write at End of Unaligned Buffer                   |

| Figure 33. 16-Bit Software Model    58                                   |

| Figure 34. 32-Bit Software Model    59                                   |

| Figure 35. ISO 8802-3 (IEEE/ANSI 802.3) Data Frame                       |

| Figure 36. IEEE 802.3 Frame and Length Field Transmission Order          |

| Figure 37. 10BASE-T Transmit and Receive Data Paths                      |

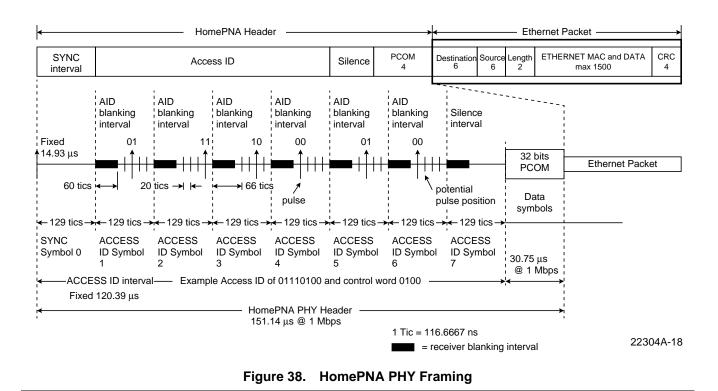

| Figure 38. HomePNA PHY Framing75                                         |

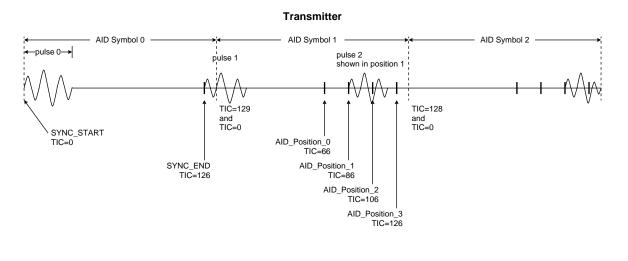

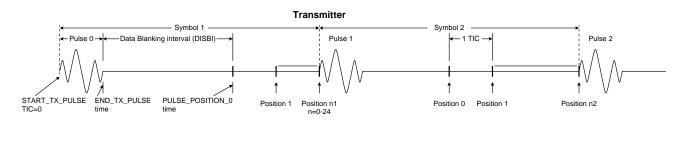

| Figure 39. AID Symbol Transmit Timing                                    |

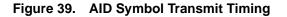

| Figure 40. AID Symbol Receive Timing76                                   |

| Figure 41. Transmit Data Symbol Timing                                   |

| Figure 42. Receive Symbol Timing    78                                   |

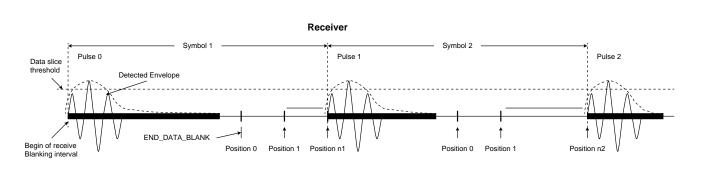

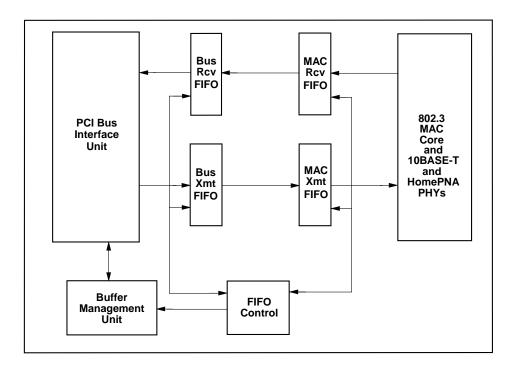

| Figure 43. RLL 25 Coding Tree                                            |

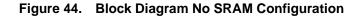

| Figure 44. Block Diagram No SRAM Configuration    82                     |

| Figure 45. Block Diagram Low Latency Receive Configuration               |

| Figure 46. LED Control Logic    86                                       |

| Figure 47. OnNow Functional Diagram    87                                |

| Figure 48. Pattern Match RAM    89                                       |

| Figure 49. NAND Tree Circuitry (160 PQFP)91                              |

| Figure 50. NAND Tree Waveform                                            |

| Figure 51. Address Match Logic    197                                    |

| Figure 52. Clock Timing    222                                           |

| Figure 53. PMD Interface Timing (PECL)    222                            |

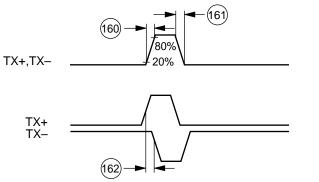

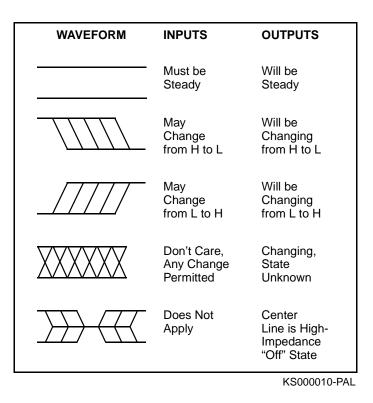

| Figure 54. 10 Mbps Transmit (TX±) Timing Diagram    223                  |

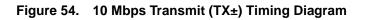

| Figure 55. 10 Mbps Receive (RX±) Timing Diagram    223                   |

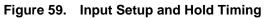

| Figure 56. Normal and Tri-State Outputs                                  |

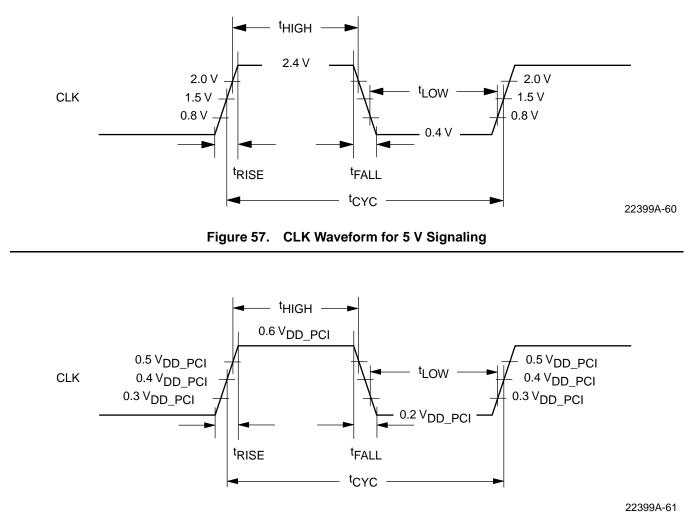

| Figure 57. CLK Waveform for 5 V Signaling                                |

| Figure 58. CLK Waveform for 3.3 V Signaling                    | 26  |

|----------------------------------------------------------------|-----|

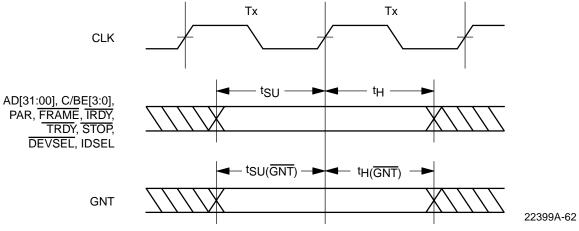

| Figure 59. Input Setup and Hold Timing                         | 26  |

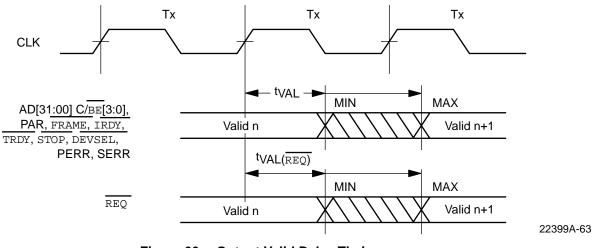

| Figure 60. Output Valid Delay Timing                           | 27  |

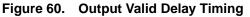

| Figure 61. Output Tri-State Delay Timing                       | 27  |

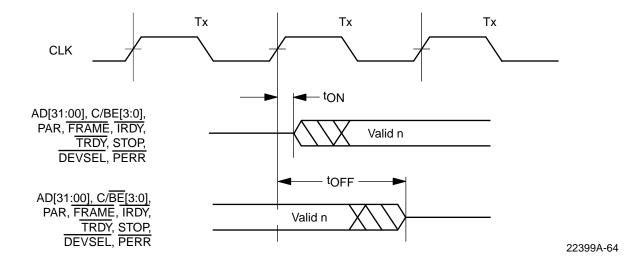

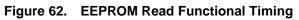

| Figure 62. EEPROM Read Functional Timing                       | 27  |

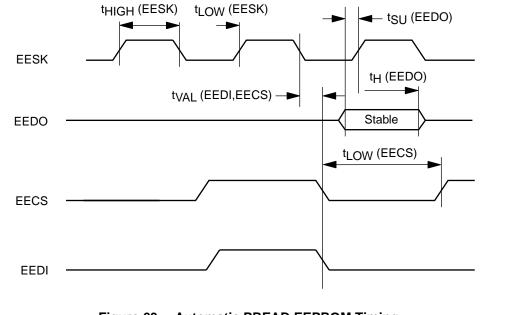

| Figure 63. Automatic PREAD EEPROM Timing                       | 28  |

| Figure 64. JTAG (IEEE 1149.1) TCK Waveform for 5 V Signaling   | 28  |

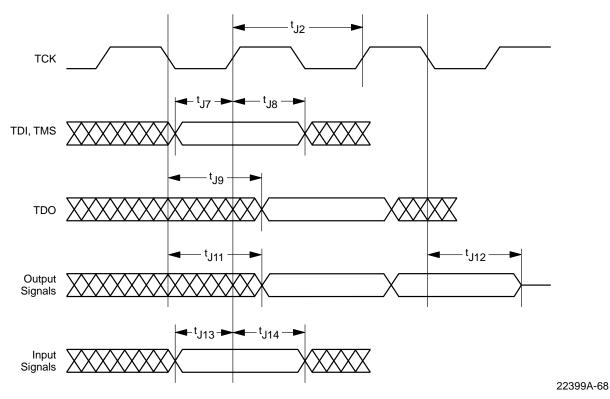

| Figure 65. JTAG (IEEE 1149.1) Test Signal Timing               | 29  |

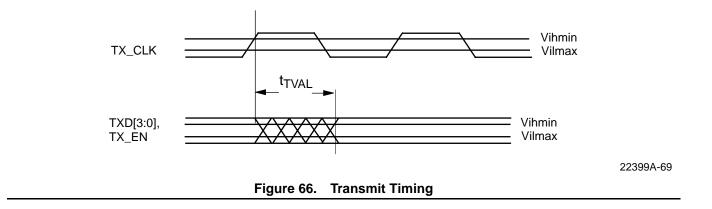

| Figure 66. Transmit Timing                                     | 30  |

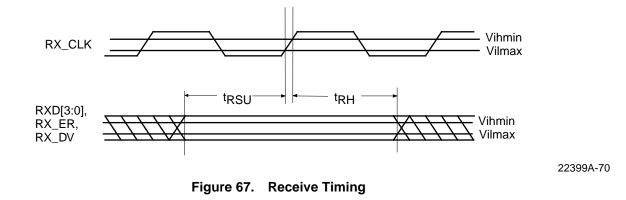

| Figure 67. Receive Timing                                      | 30  |

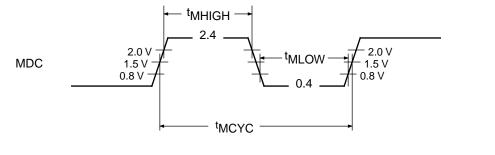

| Figure 68. MDC Waveform                                        | 30  |

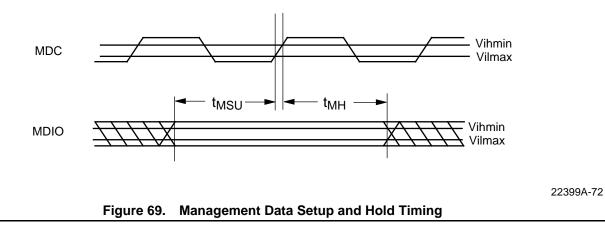

| Figure 69. Management Data Setup and Hold Timing               | 31  |

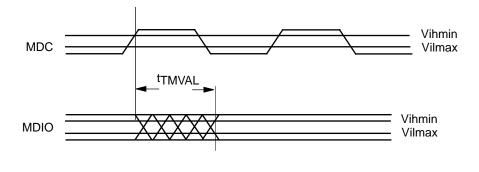

| Figure 70. Management Data Output Valid Delay Timing           | 31  |

| Figure B-1. LAPP TimelineB-                                    | 3-4 |

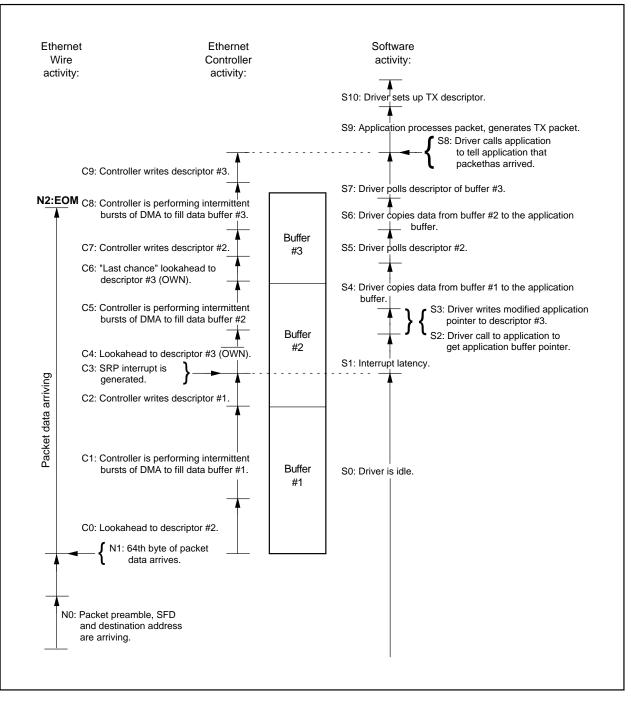

| Figure B-2. LAPP 3 Buffer GroupingB-                           | 3-5 |

| Figure B-3. LAPP Timeline for Two-Interrupt MethodB-           | 3-9 |

| Figure B-4. LAPP 3 Buffer Grouping for Two-interrupt MethodB-1 | 10  |

#### LIST OF TABLES

| Table 1. Interrupt Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2. External Clock/Crystal Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27   |

| Table 3. Crystal Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27   |

| Table 4. PCI Device ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32   |

| Table 5. PCI Software Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32   |

| Table 6. Slave Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32   |

| Table 7. Slave Configuration Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33   |

| Table 8. Master Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39   |

| Table 9. Descriptor Read Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| Table 10. Descriptor Write Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| Table 11. Receive Address Match                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Table 12. Auto-Negotiation Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73   |

| Table 13. HomePNA PHY Pulse Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75   |

| Table 14. Access ID Symbol Pulse Positions and Encoding         Image: Control of the symbol Pulse Position Pulse Positin Pulse Positin Pulse Positin Pulse Position Pulse Position Puls | 77   |

| Table 15. Blanking Interval Speed Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| Table 16. Master Station Control Word Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Table 17. Slave Station Control Word Status Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Table 18. MII Control Frame Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| Table 19. EEPROM Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 85   |

| Table 20. LED Default Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| Table 21. IEEE 1149.1 Supported Instruction Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| Table 22. BSR Mode Of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Table 23. Device ID Register    Image: Comparison of the second se   |      |

| Table 24. NAND Tree Pin Sequence (160 PQFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Table 25. NAND Tree Pin Sequence (144 TQFP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Table 26. PCI Configuration Space Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Table 27. I/O Map in Word I/O Mode (DWIO = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| Table 28. Legal I/O Accesses in Word I/O Mode (DWIO = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

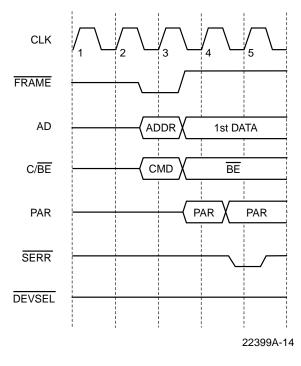

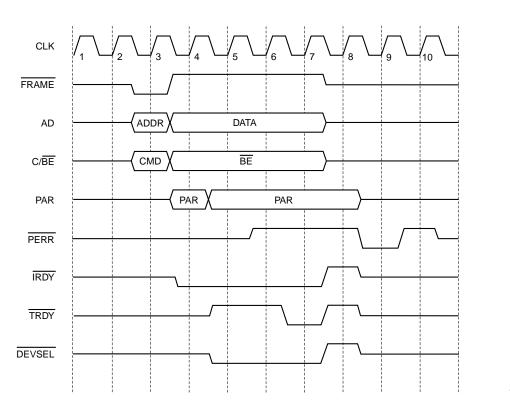

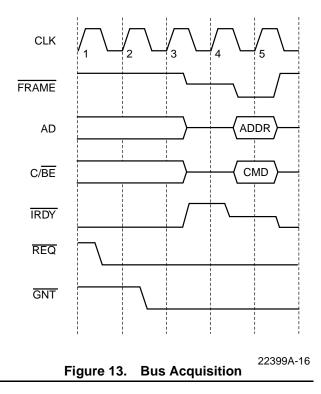

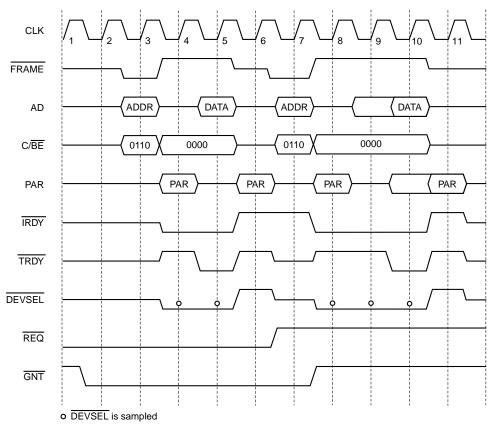

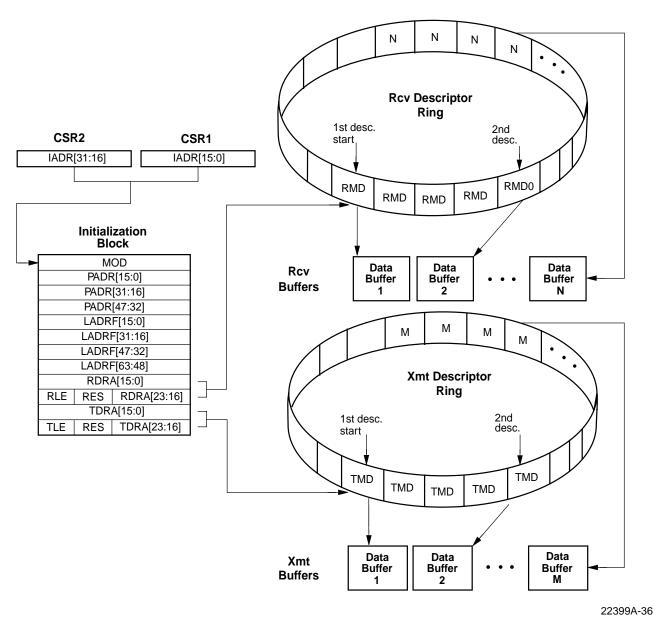

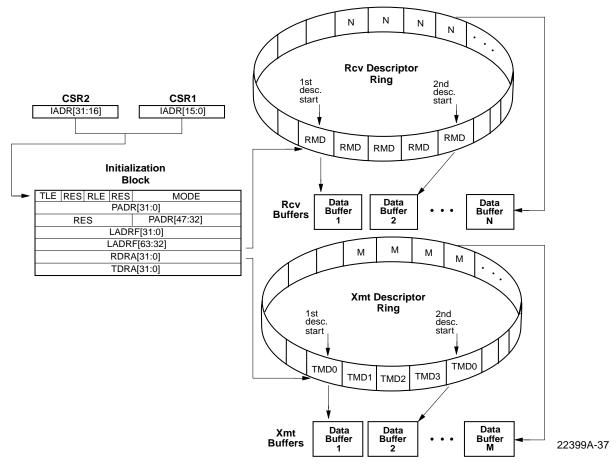

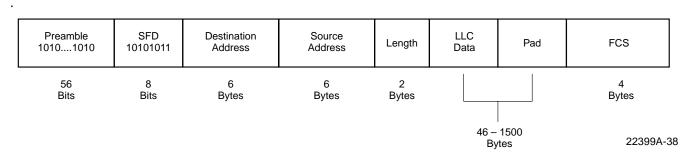

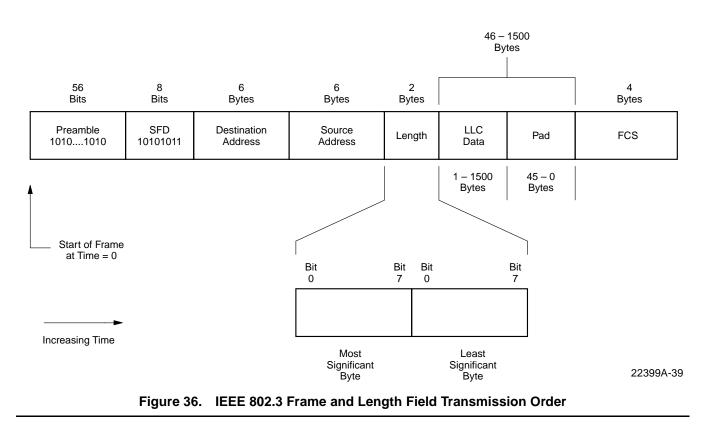

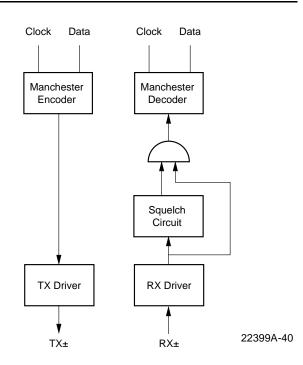

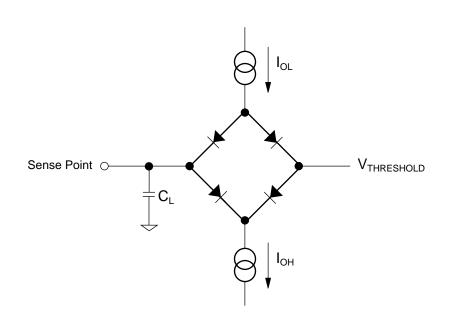

| Table 29. I/O Map in DWord I/O Mode (DWIO = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |