# 3.1 Megapixel CMOS Sensor

## **Features**

- HiSENS™ High Sensitivity in low-light conditions

- 1/2.8" optical format image sensor

- · Fast frame readout at full resolution

- · Progressive scan

- I<sup>2</sup>C serial control interface

- · Selectable 8 and 12 bit parallel data port

- Low-power 30 frames/s preview mode

- Programmable controls: frame size, frame rate, gain exposure, blanking, flip and mirroring, windowing, auto black level offset correction and panning

- · Horizontal and vertical binning for increased sensitivity

- · Available in 48-pin PLCC package

# **Applications**

- · Cellular phone camera modules

- Pocket PCs

- PDAs

- Toys

- · Battery operated devices

# Table 0-1. Key Performance Parameters

| Parameter                            | Typical Value                                               |

|--------------------------------------|-------------------------------------------------------------|

| Optical Format                       | 1/2.8-inch                                                  |

| Active Imager Size                   | 5.2 mm x 3.9 mm                                             |

| Active Pixels                        | 2048H x 1536V                                               |

| Pixel Size                           | 2.54 μm x 2.54 μm                                           |

| Color Filter Array                   | RGB Bayer Pattern                                           |

| Shutter Type                         | Electronic Rolling Shutter                                  |

| Maximum Data Rate/<br>Master Clock   | 48 MPS/48 MHz                                               |

| Frame Rate                           | 14 fps (2048 x 1536)<br>80 fps (640 x 480)                  |

| ADC Resolution                       | 12-bit (72 dB), on-chip                                     |

| Dynamic Range                        | 55 dB                                                       |

| Responsivity                         | >1.0V/lux-sec (550 nm)                                      |

| SNR <sub>MAX</sub> in dB             | QXGA: 35<br>VGA: 40                                         |

| Supply Voltage @ 25°C                | Analog: 2.5V–3.1V<br>Digital: 1.65V–2.0V<br>I/O: 1.8V–2.8V  |

| Analog and Digital Power Consumption | 60 mW @ 30 fps (640 x 480)<br>215 mW @ 15 fps (2048 x 1536) |

| Operating Temperature                | -30°C to +70°C                                              |

| Packaging                            | 48-pin PLCC                                                 |

|                                      |                                                             |

# **TABLE OF CONTENTS**

| FEATURES                                               |    |

|--------------------------------------------------------|----|

| APPLICATIONS                                           | 1  |

| 1.0 GENERAL DESCRIPTION                                | 4  |

| 2.0 PIN DESCRIPTION                                    | 5  |

| 3.0 FUNCTIONAL OVERVIEW                                |    |

| 4.0 SIGNAL DESCRIPTION                                 |    |

|                                                        |    |

| 5.0 PIXEL ARRAY STRUCTURE                              |    |

| 6.0 DATA FORMATS                                       | 9  |

| 6.1 Frame Timing                                       | 9  |

| 6.2 Frames per Second and Integration Time Calculation |    |

| 6.3 Output Data Timing                                 |    |

| 7.0 SERIAL BUS DESCRIPTION                             | 11 |

| 7.1 Serial Bus Protocol                                | 11 |

| 7.2 Detailed Timing                                    |    |

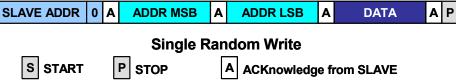

| 7.3 Single Random WRITE                                |    |

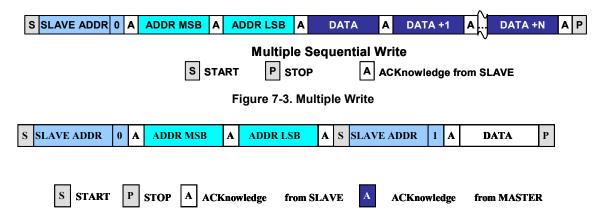

| 7.4 Multiple WRITE                                     |    |

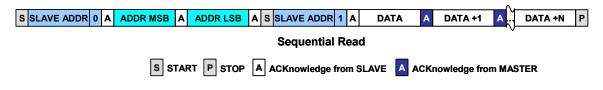

| 7.5 Single Random READ                                 |    |

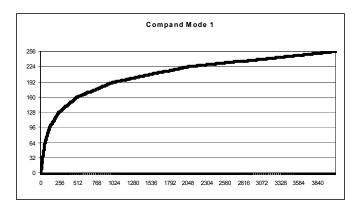

| 7.6 Multiple Sequential READ                           |    |

| 8.0 REGISTERS                                          |    |

| 8.1 Register Map                                       |    |

| 8.2 Control Registers                                  |    |

| 8.3 Status Registers                                   |    |

| 9.0 FEATURE DESCRIPTIONS                               |    |

| 9.1 HiSENS™                                            |    |

| 9.2 Power Saver Settings                               |    |

| 9.3 Selectable Frame Rate                              |    |

| 9.4 FPN Reduction                                      |    |

| 9.6 Digital Gain per Color                             |    |

| 9.7 Exposure Control                                   |    |

| 9.8 Resolution Control                                 |    |

| 9.9 Sub-window Control                                 |    |

| 9.10 Analog On-chip Binning                            |    |

| 9.11 Digital On-chip Binning                           |    |

| 9.12 50-/60-Hz Flicker Reduction                       |    |

| 9.14 Power-on Reset                                    |    |

| 9.15 On-chip Test Pattern Generation                   |    |

| 9.16 Exposure Control Region of Interest (ROI)         |    |

| 9.17 Register Setting Sync Control                     |    |

| 9.18 Preview and Video Mode                            |    |

| 9.19 Parallel Digital Interface                        |    |

| 10.0 ELECTRICAL SPECIFICATIONS                         | 35 |

| 10.1 Absolute Maximum Ratings                          | 35 |

| 10.2 Operating Conditions                              | 35 |

| 11.0 ELECTRICAL CHARACTERISTICS                        | 35 |

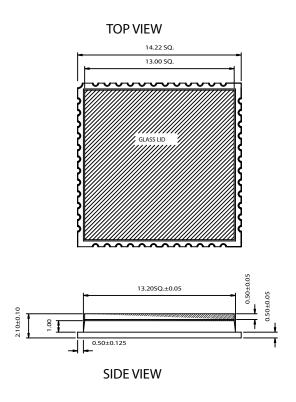

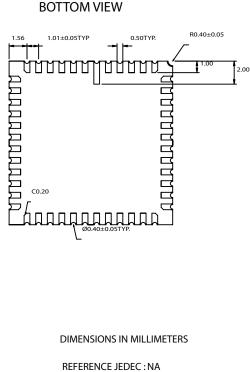

| 12.0 48-PIN PLCC PACKAGE DIAGRAM                       | 36 |

| 12.1 Ordering Information                              |    |

|                                                        |    |

# **LIST OF FIGURES**

| Figure 1-1. Block Diagram                                      | 4  |

|----------------------------------------------------------------|----|

| Figure 2-1. Bond Diagram for 48-PLCC Package                   | 5  |

| Figure 3-1. Typical Configuration                              |    |

| Figure 5-1. Pixel Array                                        |    |

| Figure 6-1. Frame Timing                                       | 9  |

| Figure 6-2. Row Timing                                         | 10 |

| Figure 6-3. Row Timing With Binning                            | 10 |

| Figure 6-4. Pixel Data Timing                                  | 11 |

| Figure 7-2. Single Random Write                                | 11 |

| Figure 7-1. Serial Bus Timing                                  |    |

| Figure 7-3. Multiple Write                                     |    |

| Figure 7-4. Single Random Read                                 |    |

| Figure 7-5. Multiple Sequential Read                           |    |

| Figure 9-1. SMPTE Color Bars                                   |    |

| Figure 12-1. 48-Pin PLCC Package Diagram                       | 36 |

|                                                                |    |

| LIST OF TABLES                                                 |    |

| Table 0-1. Key Performance Parameters                          |    |

| Table 4-1. Signal Description                                  |    |

| Table 6-1. Embedded Sync                                       |    |

| Table 8-1. Register Map                                        |    |

| Table 9-1. Power Modes                                         | 32 |

| Table 9-2. Typical Power Consumption in Common Operating Modes | 32 |

| Table 11-1. Énvironmental Specifications                       | 35 |

| Table 12-1 Ordering Information                                | 36 |

# 1.0 General Description

Cypress Semiconductor Corporation's (Cypress's) CMOS sensor is a 3.1-megapixel (QXGA) format, 1/2.8-inch active-pixel digital image sensor with an active imaging pixel array of 2048H x 1536V. The sensor incorporates camera functions such as frame size/rate, flip, mirroring and binning for increased sensitivity. The sensor functions are all programmable through a  $\rm I^2C$  serial interface.

The megapixel CMOS sensor features Cypress's HiSENS circuitry, which dramatically improves low light sensitivity without increasing the number of transistors used in the pixel and maintains the fill factor while reducing the cost and complexity of the sensor.

An on-chip analog-to-digital converter (ADC) provides 12 bits per pixel. The sensor can be programmed by the user to meet the application specific requirements such as windowing, gain, panning and other parameters. The sensor can output a QXGA image up to 14 frames per second (fps).

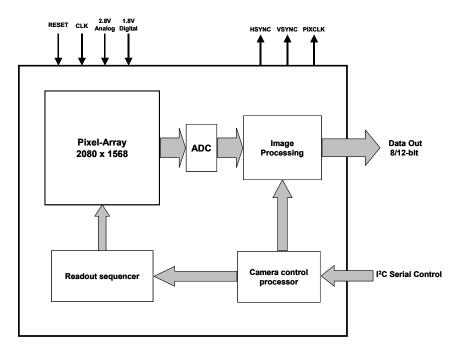

Figure 1-1. Block Diagram

# 2.0 Pin Description

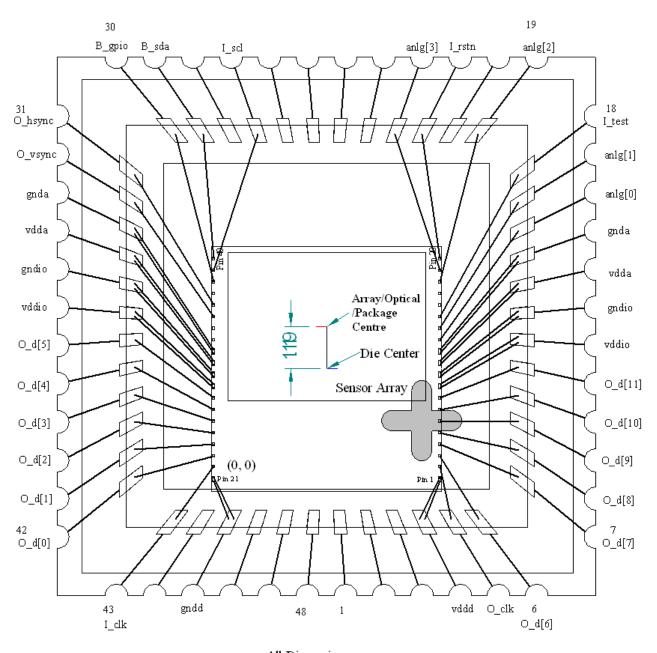

All Dimensions: mm

Figure 2-1. Bond Diagram for 48-PLCC Package

Note: The sensor die is placed in the package so that the array center (optical center) of the die is centered in the package. The die is offset in the "Y" direction by 1.119 mm to achieve this.

## 3.0 Functional Overview

The sensor is a progressive-scan sensor that generates a stream of pixel data qualified by HSYNC and VSYNC signals. In default mode, the data rate (pixel clock) is the same as the master clock frequency, one pixel is generated every master clock cycle.

The core of the sensor is an active-pixel array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row. In the time interval between resetting and reading a row, the pixels in that row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. After a row is read, the data from the columns is sequenced through an analog signal chain (providing offset correction), and then through an ADC. The output from the ADC is a 12-bit value for each pixel in the array. The pixel array contains optically active and light-shielded "black" pixels. The black pixels are used to provide data for on-chip offset correction algorithms (black level control).

The sensor contains a set of 8-bit control and status registers that can be used to control many aspects of the sensor operations. These registers can be accessed through a I<sup>2</sup>C serial interface. In this document, registers are specified either by name (e.g., column start) or by register address (e.g., Reg0x04). Fields within a register are specified by bit or by bit range (e.g., Reg0x20[0] or Reg0x0B[13:0]. The control and status registers are described in Registers, Section 8.0.

The output from the sensor is a Bayer pattern: alternate rows are a sequence of either green/red pixels or blue/green pixels. The offset and gain stages of the analog signal chain provide per-color control of the pixel data.

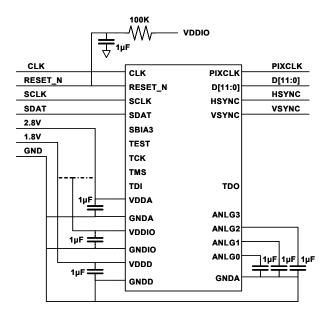

Figure 3-1. Typical Configuration

Figure 3-1 shows a typical module wiring diagram. VDDIO can be connected to either the 1.8V supply or the 2.8V supply (but not both) to match the voltage requirements of the back-end processing chip. It is recommended that the 1.8V supply be used to minimize power consumption. The capacitor for the VDDIO supply is optional but the capacitors for VDDD and VDDA are required and must provide sufficient decoupling on the module to insure clean supply voltages. Note that ANLG[2:0] must be connected to capacitors to minimize image noise. ANLG[3] is only for test purposes and should be unconnected. Note that RESET\_N is typically connected with an RC circuit to hold RESET\_N low until both power supplies have reached their proper level.

# 4.0 Signal Description

Table 4-1. Signal Description

| Pin | Function | Type          | Note                                         |  |  |  |  |

|-----|----------|---------------|----------------------------------------------|--|--|--|--|

| 1   | Vddd     | Power         | Digital Core Power (1.8V nominal)            |  |  |  |  |

| 2   | PIXCLK   | Output        | Pixel Clock (data strobe)                    |  |  |  |  |

| 3   | D6       | Output        | Digital Video Out                            |  |  |  |  |

| 4   | D7       | Output        | Digital Video Out                            |  |  |  |  |

| 5   | D8       | Output        | Digital Video Out                            |  |  |  |  |

| 6   | D9       | Output        | Digital Video Out                            |  |  |  |  |

| 7   | D10      | Output        | Digital Video Out                            |  |  |  |  |

| 8   | D11      | Output        | Digital Video Out (MSB)                      |  |  |  |  |

| 9   | Vddio    | Bidirectional | Digital IO Supply (1.8V nominal or 2.8V)     |  |  |  |  |

| 10  | GNDIO    | Power         | IO Ground                                    |  |  |  |  |

| 11  | Vdda     | Power         | Analog Supply to Pixel Array (2.8V nominal)  |  |  |  |  |

| 12  | GNDA     | Power         | Analog Ground                                |  |  |  |  |

| 13  | ANLG[0]  | Bidirectional | Analog Debug                                 |  |  |  |  |

| 14  | ANLG[1]  | Bidirectional | Analog Debug                                 |  |  |  |  |

| 15  | TEST     | Input         | Test Mode                                    |  |  |  |  |

| 16  | SBIA3    | Input         | Serial Bus Interface Address bit 3           |  |  |  |  |

| 17  | TDI      | Input         | JTAG Data In                                 |  |  |  |  |

| 18  | ANLG[2]  | Bidirectional | Analog Debug                                 |  |  |  |  |

| 19  | ANLG[3]  | Bidirectional | Analog Debug                                 |  |  |  |  |

| 20  | RESET_N  | Input         | Reset active low                             |  |  |  |  |

| 21  | GNDD     | Power         | Digital Ground                               |  |  |  |  |

| 22  | CLK      | Input         | Input Clock (up to 48 MHz)                   |  |  |  |  |

| 23  | D0       | Output        | Digital Video Out                            |  |  |  |  |

| 24  | D1       | Output        | Digital Video Out                            |  |  |  |  |

| 25  | D2       | Output        | Digital Video Out                            |  |  |  |  |

| 26  | D3       | Output        | Digital Video Out                            |  |  |  |  |

| 27  | D4       | Output        | Digital Video Out                            |  |  |  |  |

| 28  | D5       | Output        | Digital Video Out                            |  |  |  |  |

| 29  | VDDIO    | Bidirectional | Digital IO Supply (1.8V nominal or 2.8V)     |  |  |  |  |

| 30  | GNDIO    | Bidirectional | IO Ground                                    |  |  |  |  |

| 31  | VDDA     | Bidirectional | Analog Supply to Pixel Array (2.8V nominal)  |  |  |  |  |

| 32  | GNDA     | Power         | Analog Ground                                |  |  |  |  |

| 33  | TCK      | Input         | JTAG Clock                                   |  |  |  |  |

| 34  | TMS      | Input         | JTAG                                         |  |  |  |  |

| 35  | VSYNC    | Output        | Frame Sync                                   |  |  |  |  |

| 36  | HSYNC    | Output        | Line Sync                                    |  |  |  |  |

| 37  | TDO      | Output        | JTAG Data Out                                |  |  |  |  |

| 38  | GPIO     | Bidirectional | General Purpose Digital IO                   |  |  |  |  |

| 39  | SCLK     | Input         | I <sup>2</sup> C Serial Communications Clock |  |  |  |  |

| 40  | SDAT     | Bidirectional | I <sup>2</sup> C Serial Communications Data  |  |  |  |  |

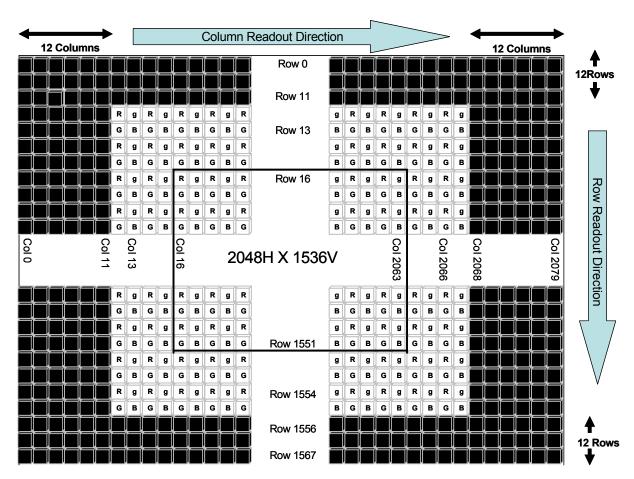

# 5.0 Pixel Array Structure

The sensor device is a camera on a chip CMOS imager with 3-megapixel resolution (QXGA) in a 1/2.8" optical format. This requires a 2.54-µm square pixel pitch for adequate sensitivity. Figure 5-1 below shows the layout of the Pixel Array. The 12 outermost rows and columns of the array are covered with metal and are thus optically black. The black rows can also be set via internal registers to be read out as valid frame data. There are 2048H x 1536V optically active pixels surrounded by an additional 2 Bayer patterns (4 pixels) around the image

to avoid boundary effects during color interpolation and correction.

The sensor is designed with a mosaic of color filters arranged in a standard Bayer pattern shown in *Figure 5-1*. The odd numbered columns contain green and blue pixels as do the odd numbered rows. Correspondingly, the even rows and even columns contain green and red pixels. The imager will output either all Bayer patterned pixels or all physical pixels based upon register settings. The Bayer primitive pattern at the periphery should be used for border interpolation.

2080H X 1568V Total Pixels (2056H X 1544V Active Pixels)

Figure 5-1. Pixel Array

#### 6.0 Data Formats

The imager is read out in a progressive scan fashion. This means that each successive row is read out in an increasing row number. The data is digitized via on chip A/D converters and the output resolution is selectable at 8 and 12 bits resolution. The pixel data is output in parallel with synchronization signals for frame (VSYNC), line (HSYNC), and pixel (PIXCLK). The frame and line sync signals may be embedded in the data as set by internal registers. When sync signals are embedded in the data, the numbers of available colors is reduced by one value. The embedded SYNC values are indicated by a pattern of 0xFF, 0x00, 0x00, SYNC\_VALUE where SYNC\_VALUE is listed in Table 6-1.

Table 6-1. Embedded Sync

| SYNC_VALUE | Description |

|------------|-------------|

| 00         | Row Start   |

| 01         | Row End     |

| 02         | Frame Start |

| 03         | Frame End   |

To prevent SYNC from being inadvertently indicated in the active portion of the image, the 0xFF value is remapped to 0xFE when operating in 8-bits/pixel mode. The embedded sync format follows several industry standards including ITU-R BT.656.

With discrete sync signals, the polarity of the HSYNC, VSYNC, and PIXCLK may be independently inverted with respect to the active pixel readout. HSYNC and VSYNC toggle even when embedded syncs are enabled.

The resolution is set by three factors. The resolution may be decreased by sub-windowing a smaller region of interest (ROI), as set in the internal registers. The imager can also be programmed to sub-sample the array to read out every n<sup>th</sup> Bayer rows and m<sup>th</sup> Bayer columns. Finally, the imager can be programmed to bin (combine) adjacent pixels of similar color in both row and column directions independently with strengths of 2, 3, or 4.

The output data can be shifted down by 4 bits to accommodate back-end processors that want to switch from processing 12-bit data to 8-bit data where the LSBs must remain at bit zero on the Pixel Bus.

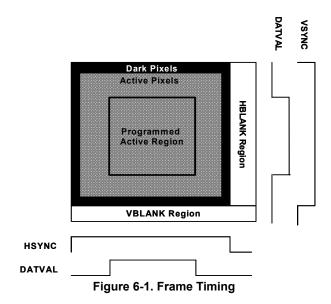

## 6.1 Frame Timing

A frame of data is comprised of valid image data which is output when the HSYNC and VSYNC signals are inactive (1). Frame rate is computed as a function of the CLK frequency, the row timing, the number of rows and the number of vertical blanking (VBLANK) rows programmed. The frame timing is programmable via a number of registers described later in this document.

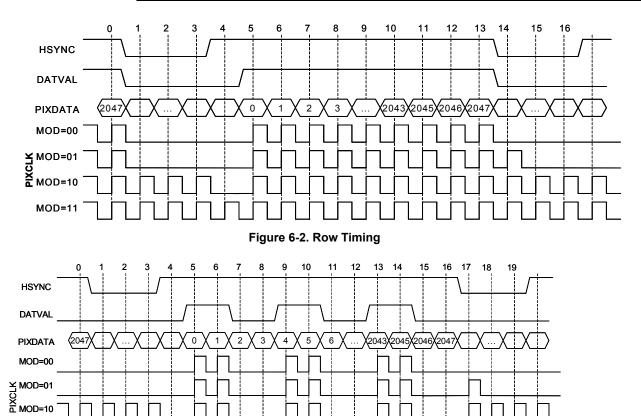

Interfacing to a back-end processor involves the control signals, HSYNC and VSYNC, and the appropriate PIXCLK timing. The Imager has several programmable modes to allow interfacing to a wide variety of back-end processors. *Figure 6-2* shows typical interface signals.

There are two basic modes of operation, HSYNC and DATVAL. In HSYNC mode, the HSYNC signal indicates the

start of a new row of the image. In this mode PIXCLK only clocks when there is valid data on the PIXDATA bus.

In DATVAL mode, PIXCLK runs throughout the HBLANKING period (or optionally free-runs) and the HSYNC signals becomes a Data Valid signal which tells the back-end processor when there is valid data on the PIXDATA bus.

Note that if Dark Pixels are enabled to be output or if digital horizontal binning is used, DATVAL will toggle many times during a single row. Enabling Embedded Syncs does not change the row or frame timing. The 4-byte SYNC fields are inserted into the data stream during the HBLANK time (HBLANK must be at least 8).

The timing diagram in *Figure 6-2* shows the detailed row timing of all of the modes that the imager can produce. The HSYNC signal can be programmed to be either HSYNC or DATVAL. PIXCLK can be programmed in four different operating modes. Depending on the back-end processor, some modes will work better than others. Generally DATVAL mode with PIXCLDK mode = 10 is the most common mode. In this mode the HSYNC signal is acting as a DATA VALID pulse. PIXCLK runs continuously except when invalid data is on the PIXDATA bus. In the diagram above, CLK 4 is when the dark pixels are being processed. If the dark pixels were enabled to be output then CLK 4 would be high. Note that the number of clocks is significantly reduced in this diagram for ease of viewing. HSYNC is typically low for 16 or more clocks and there are 24 dark pixels, not just the one shown here.

The row timing gets more complicated when horizontal binning or subsampling is enabled (see *Figure 6-3*). The timing diagram shows the case where HBIN by 2 is enabled. Note that since the output format is Bayer patterns, it outputs 2 pixels, then skip (or bin) 2 pixels. Note that when using DATVAL mode, the DATVAL signal will toggle many times each row. However, using PIXCLK mode = 01, the backend processor will not clock in the pixels when DATVAL is low and thus it looks to the processor like DATVAL is always high when there is valid data.

MOD=11

Figure 6-3. Row Timing With Binning

PIXCLK mode = 11 is typically only used in DATVAL mode. Otherwise, the processor has to clock in every pixel in a frame and then compute which ones are valid and which ones re not based on the bin/subsampling modes.

# 6.2 Frames per Second and Integration Time Calculation

The number of frames per second taken by the Osprey is programmable. It can vary from less then 1 fps to 14 fps in full resolution capture mode (and can be much higher in reduced resolution modes). The frame rate is dictated by input clk frequency, the total number of rows output per frame and the time required to read out a single row. The total number of rows output and the time required to output a row can be calculated using simple formula's based on I<sup>2</sup>c register reads.

RowNum register (0x4) stores the number of active rows output.COLCNT register (0xa8) stores the # of clks required to read out a single row (hence time required to read out a single row is COLCNT / CLK FREQ. COLCNT is modified based on active number of columns output (COLNUM register (0x6) and the HBLANK register (0x8,0x9), which adds additional clk cycles onto the end of the row readout). Note that COLCNT is a 12bit register.

Frames/Second = Clock Frequency / (Total number of Rows per frame \* COLCNT (register 0xa8 and 0xa9))

Where Total number of Rows per frame =RowNum(register 0x4 and 0x5 +1)+ VBLANK(0xC and 0xD) + Number of Dark rows.

The RowNum register will have a value 1 less than actual number of active rows and hence an addition of 1 in the formula.

The Dark rows are the optically black rows located towards the periphery to calculate the black level. At least 4 rows must be turned on to properly compute the dark current. By default, the middle 4 rows are turned on which typically are the best for computing Dark current. Please refer section 7.2.36.

Integration Time Calculation

TINT (in Seconds) = COLCNT (register 0xa8 and 0xa9) \* INTTIME (register 0xE and 0xF) / Clock Frequency

It is recommended that INTTIME should not be set larger than the Total Number of Rows per Frame.

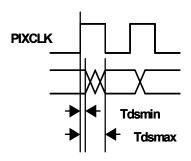

# 6.3 Output Data Timing

The Pixel Output bus has programmable polarities for the clock and the sync signals to simplify timing to the back-end processor. The timing of all of the signals is relative to PIXCLK. The delay time for HSYNC, VSYNC and the PIXDAT bus to be valid relative to the selected edge of PIXCLK is a minimum of 0 ns (Ddsmin) and a maximum of 4 ns (Tdsmax).

Figure 6-4. Pixel Data Timing

# 7.0 Serial Bus Description

The CYIWOSC3000AA includes a serial control interface that allows the application processor to control the imager using only two signals. The Serial Bus Interface (SBI) is a simple bidirectional communication interface based on the I<sup>2</sup>C protocol that is in wide use throughout the industry. The serial bus operates at speeds of up to 400,000 bits per second. The Interface is a multi-drop protocol which allows multiple devices to be connected to a single pair of wires and can be used between numerous standard image processing chips.

The two interface signals are called SCLK and SDAT. SCLK provides a clock for asserting and sampling the SDAT signal. SCLK is unidirectional from the bus master, typically an image processing chip, to the CYIWOSC3000AA image sensor. SDAT is the data bus and is bidirectional. Both signals are open-drain and require a pull-up resistor of 1.5K Ohms.

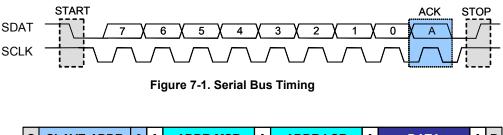

Data is always transmitted with the Most-Significant-Bit (MSB) first. Eight bits of data are always transferred and are followed by a single ACKnowledge bit.

## 7.1 Serial Bus Protocol

Data transfer on the Serial Bus Interface is initiated with a START condition. The START condition is indicated when the SDAT signal goes low while SCLK remains high. The START condition may be initiated at anytime during a transfer and the imager will restart the transfer to begin accepting the SLAVE ADDRESS which must immediately follow the START.

The SDAT line must only transition when SCLK is low when data is being transferred. If SDAT transitions while SCLK is high, then it will be interpreted as either a START or a STOP condition. Sufficient timing margins must be provided around the rising and falling edges of SCLK to insure that a START or STOP condition are not mistakenly recognized.

The SLAVE ADDRESS is a sequence of 7 bits, a READ/WRITE bit and an ACKnowledge bit. Data is always transmitted MSB first and LSB last as shown in Figure 7-1. The SLAVE ADDRESS is 7 bits long and must be 1110\_x10 (0xE4 or 0xEC) where x is the state of the SBIA3 pin. The SBIA3 pin allows two CYIWOSC3000AA Image Sensors to be connected to the same Serial Bus Interface. The LSB of the SLAVE ADDRESS is the READ/WRITE bit where a high (1) indicates that a READ cycle will follow and a low (0) indicates that a write cycle will follow. After the READ/WRITE bit, the CYIWOSC3000AA Image Sensor will assert SDAT low shortly after SCLK goes low to acknowledge that the SLAVE ADDRESS has been recognized and is ready to process the command that will follow.

If a read transaction has been requested (READ/WRITE is high), then the imager will begin driving SDAT with the register data at the current address. If a write transaction has been requested then the bus master should send the two REG ADDRESS bytes. The REG ADDRESS bytes specifies which register in the imager is to be accessed.

The next byte of data is the write data. Additional bytes of data can be written and the ADDRESS will be automatically incremented to the next register. Upon completion of all data being transferred, the master should issue a STOP command to place the SBI in an idle state. A STOP command is initiated by first driving SDAT low and SCLK high, then bringing SDAT high while SCLK remains high.

# 7.2 Detailed Timing

Figure 7-1 shows the detailed timing of each byte of data to be transferred on the SBI. A transfer begins with the START condition. This is always followed by 8-bits of data. The Acknowledge bit always follows the data which is from the receiver of the data to the transmitter. Additional bytes of data can then be transferred until either the STOP condition or another START condition is detected. Data is always transferred most-significant-bit first.

Figure 7-2. Single Random Write

Figure 7-4. Single Random Read

# 7.3 Single Random WRITE

A WRITE cycle to any register is accomplished by sending a START followed by a 7 bit SLAVE ADDRESS, one bit of zero (the read/write indicator) and an ACK bit (see *Figure 7-2*). Then the 16-bit register address must be sent in two bytes, each with an ACK bit from the slave. Finally the 8-bits of data are sent and the slave will respond with a final ACK bit. The master can then either issue a STOP command or write to the next sequential address by sending additional data bytes.

# 7.4 Multiple WRITE

Multiple registers can be written in a single stream of data which reduces the time required to update registers. In Figure 7-3, DATA would be written to the address given in ADDR. DATA+1 would be written to ADDR+1 and so on with each byte of data being written to the next higher register address.

# 7.5 Single Random READ

A single random read cycle requires that a dummy write cycle be done first so that the register address can be set. The first SLAVE ADDR is followed with a 0 bit which indicates that this is a write cycle. The register address follows but instead of sending the data to write, a new START condition is sent which restarts the SBI state machine but the REG ADDR remains initialized. The SLAVE ADDR must be sent again but this time is followed with a 1 bit indicating that this is a read cycle. The

slave responds with the ACK bit and then drives the 8 data bits of the register which has been read. After the eight data bits, the slave does NOT assert the ACK bit. Instead, it tri-states the SDAT signal so that the master can either ACK, or assert the STOP condition.

# 7.6 Multiple Sequential READ

Multiple sequential registers can be read without having to resend the SLAVE ADDR and register addresses. To read multiple registers, simply continue to issue more SCLKs and the imager will increment to the next higher register address. After each byte that is transferred, the master must issue an ACK by driving SDAT low if it wishes to continue to read more data. The last byte that is read should not ACK, which allows the master to drive SDAT low before releasing SCLK and then release SDAT to cause a STOP condition to be recognized. Alternatively, if the master does not drive SDAT low during the ACK bit, the imager will release the SDAT line and the state machine will return to its idle state waiting for the next START condition.

The register ADDR is always retained at the current address as long as power is applied to the chip. A register read at the current address can be initiated at any time without having to send the register ADDR first if the desired register is already being addressed. Note that the register address is incremented on the rising edge of SCLK at the start of the ACK bit.

Figure 7-5. Multiple Sequential Read

# 8.0 Registers

# 8.1 Register Map

Table 8-1. Register Map

| ADDR | Name                   | 7        | 6 | 5   | 4       | 3 2     | 2 1  | 0  | Description                     |

|------|------------------------|----------|---|-----|---------|---------|------|----|---------------------------------|

| 00   | ROWSH <sup>[1]</sup>   | F        |   |     |         | R       | ows  | Н  | Row Start Address High          |

| 01   | ROWSL <sup>[1]</sup>   |          |   |     | RO      | WSL     |      |    | Row Start Address Low           |

| 02   | COLSH <sup>[1]</sup>   | М        |   |     |         | С       | OLSI | 1  | Column Start Address High       |

| 03   | COLSL <sup>[1]</sup>   |          |   |     | СО      | LSL     |      |    | Column Start Address Low        |

| 04   | ROWNUMH <sup>[1]</sup> |          |   |     |         | RO      | WNU  | ИΗ | Number of Rows High             |

| 05   | ROWNUML <sup>[1]</sup> |          |   | F   | ROW     | NUML    |      |    | Number of Rows Low              |

| 06   | COLNUMH <sup>[1]</sup> |          |   |     |         | СО      | LNUI | ЛΗ | Number of Columns High          |

| 07   | COLNUML <sup>[1]</sup> |          |   | (   | COLI    | NUML    |      |    | Number of Columns Low           |

| 80   | HBLANKH                |          |   |     |         | HB      | LAN  | ίH | Horizontal Blanking High        |

| 09   | HBLANKL                |          |   |     | HBL     | ANKL    |      |    | Horizontal Blanking Low         |

| 0A   | DEVID                  |          |   | DE\ | /ID=    | 0x4F('0 | )')  |    | Device Identification           |

| 0B   | VERSION                |          |   | ,   | VER     | SION    |      |    | Silicon Version                 |

| 0C   | VBLANKH                |          |   | ,   | VBL     | ANKH    |      |    | Vertical Blanking High          |

| 0D   | VBLANKL                |          |   | ,   | VBL     | ANKL    |      |    | Vertical Blanking Low           |

| 0E   | INTTIMEH               | INTTIMEH |   |     |         |         |      |    | Integration Time High           |

| 0F   | INTTIMEL               | INTTIMEL |   |     |         |         |      |    | Integration Time Low            |

| 10   | RGAINH <sup>[1]</sup>  |          |   |     |         | R       | GAIN | Н  | Red Gain Integer                |

| 11   | RGAINL <sup>[1]</sup>  | RGAINL   |   |     |         |         |      |    | Red Gain Fraction               |

| 12   | GrGAINH <sup>[1]</sup> |          |   |     |         | Gr      | GAIN | Н  | Green-red Gain Integer          |

| 13   | GrGAINL <sup>[1]</sup> |          |   |     | GrG     | AINL    |      |    | Green-red Gain fraction         |

| 14   | GbGAINH <sup>[1]</sup> |          |   |     |         | Gb      | GAIN | IH | Green-blue Gain Integer         |

| 15   | GbGAINL <sup>[1]</sup> |          |   |     | GbGAINL |         |      |    | Green-blue Gain fraction        |

| 16   | BGAINH <sup>[1]</sup>  |          |   |     |         | В       | GAIN | Н  | Blue Gain Integer               |

| 17   | BGAINL <sup>[1]</sup>  |          |   |     | BG      | AINL    |      |    | Blue Gain fraction              |

| 18   | GAIN                   |          |   |     |         |         |      | Е  | Digital Gain Enable             |

| 1E   | TINTINCH               | Е        |   |     |         | TI      | NTIN | С  | TINT Increment High             |

| 1F   | TINTINVL               |          |   |     | TIN     | TINC    |      |    | TINT Increment Low              |

| 20   | ROIXSH <sup>[1]</sup>  |          |   |     |         | R       | OIXS | Н  | Region Of Interest X Start High |

| 21   | ROIXSL <sup>[1]</sup>  |          |   |     | RO      | IXSL    |      |    | Region Of Interest X Start Low  |

| 22   | ROIWXH <sup>[1]</sup>  |          |   |     |         | R       | NWIC | Н  | Region Of Interest X Width High |

| 23   | ROIWXL <sup>[1]</sup>  | ROIWXL   |   |     |         |         |      |    | Region Of Interest X Width Low  |

| 24   | ROIYSH <sup>[1]</sup>  |          |   |     |         | ROIYSH  |      |    | Region Of Interest Y Start High |

| 25   | ROIYSL <sup>[1]</sup>  |          |   |     | RO      | IYSL    |      |    | Region Of Interest Y Start Low  |

| 26   | ROIWYH <sup>[1]</sup>  |          |   |     |         | R       | OIWY | Н  | Region Of Interest Y Width High |

| 27   | ROIWYL <sup>[1]</sup>  |          |   |     | ROI     | WYL     |      |    | Region Of Interest Y Width Low  |

| 28   | AEMAXH                 |          |   |     | AEN     | 1AXH    |      |    | Auto Exposure Maximum High      |

| 29   | AEMAXL                 |          |   |     | ΑĒΝ     | //AXL   |      |    | Auto Exposure Maximum Low       |

Note:

<sup>1.</sup> Registers controlled by the SYNC bit.

Table 8-1. Register Map (continued)

| ADDR | Name                   | 7 | 6    | 5    | 4   | 3    | 2     | 1     | 0     | Description                                  |

|------|------------------------|---|------|------|-----|------|-------|-------|-------|----------------------------------------------|

| 2A   | AEMINH                 |   |      |      | AEN | ИINH |       |       |       | Auto Exposure Minimum High                   |

| 2B   | AEMINL                 |   |      |      | AEI | MINL |       |       |       | Auto Exposure Minimum Low                    |

| 2C   | AEAVGH                 |   |      |      | AEA | VGF  | GH .  |       |       | Auto Exposure desired average luminance High |

| 2D   | AEAVGL                 |   | AEA' | VGL  |     |      |       |       |       | Auto Exposure desired average luminance Low  |

| 2F   | EXPOSURE               | Е | I    |      |     |      |       | D     | F     | Exposure Controls                            |

|      |                        |   |      |      |     |      |       |       |       |                                              |

| 30   | BLKLVLH <sup>[1]</sup> |   |      |      | BL  | .KH  |       |       |       | Black Level High                             |

| 31   | BLKLVLL <sup>[1]</sup> |   | BL   | KL   |     |      |       |       | 0     | Black Level Low                              |

| 32   | DARKMODE               | Е |      |      |     |      |       | MOD   | )     | Dark Current Subtraction Mode                |

| 33   | FPNMODE                |   |      | Н    | М   |      |       | V     | М     | Fixed Pattern Noise Modes                    |

| 35   | ABIN                   |   | /    | ABIN | 1   |      | VE    | BIN   |       | Analog Binning                               |

| 36   | HBIN                   | S | В    | Н    | B1  | W    | В     | H     | 32    | Horizontal Binning                           |

| 37   | VBIN                   | S | В    | VE   | 30  | W    | В     | VE    | BIN   | Vertical Binning                             |

| 38   | PIXREPL                |   |      |      |     |      |       | Т     | Ε     | Pixel Replacement                            |

| 39   | DATAFMT                | Е |      |      | F   | С    | Р     | 8     | D     | Pixel Data Format (8/12 bits)                |

| 3A   | SYNCPOL                | V | Н    |      | D   | Р    |       | М     | DD    | VSYNC, HSYNC, PIXCLK polarity                |

| 3B   | TSTPTN                 |   |      |      |     |      |       | MOD   |       | Test Pattern Enable                          |

| 3C   | FLIP                   |   |      |      |     |      |       | М     | F     | Flip/Mirror                                  |

| 3E   | DARKTOPH               |   |      |      |     |      |       |       |       | Top Dark Row Enable High                     |

| 3F   | DARKTOPL               |   |      |      |     |      |       |       |       | Top Dark Row Enable Low                      |

|      |                        |   |      |      |     |      |       |       |       |                                              |

| 60   | GPIO                   |   |      |      |     |      |       |       |       |                                              |

| 61   | I <sup>2</sup> CIO     |   |      |      |     |      |       |       |       |                                              |

| 62   | PCLKIO                 |   |      |      |     |      |       |       |       |                                              |

| 63   | PIXIO                  |   |      |      |     |      |       |       |       |                                              |

|      |                        |   |      |      |     |      |       |       |       |                                              |

| 70   | PWRCTL                 |   |      |      |     |      | ı     | Н     | Т     | Power and IO Control                         |

| 7E   | RESET                  |   |      |      | RE  | SET  |       |       |       | Device Reset register                        |

| 7F   | SYNC                   | Е | N    | ٧    |     |      |       |       |       | Register Synchronization                     |

|      |                        |   |      |      |     |      |       |       |       |                                              |

|      |                        | • |      |      |     | Stat | tus 8 | k Sta | tisti | cs Registers                                 |

| 80   | GrAVGH                 |   |      |      | GrA | VGH  |       |       |       | Green-red Average High                       |

| 81   | GrAVGL                 |   |      |      | GrA | VGL  |       |       |       | Green-red Average Low                        |

| 82   | GbAVGH                 |   |      |      | GbA | VGF  | ł     |       |       | Green-blue Average High                      |

| 83   | GbAVGL                 |   |      |      | GbA | WGL  | -     |       |       | Green-blue Average Low                       |

| 84   | RAVGH                  |   |      |      | RA  | VGH  |       |       |       | Red Average High                             |

| 85   | RAVGL                  |   |      |      | RA  | VGL  |       |       |       | Red Average Low                              |

| 86   | BAVGH                  |   |      |      | BA  | √GH  |       |       |       | Blue Average High                            |

| 87   | BAVGL                  |   |      |      | BA  | VGL  |       |       |       | Blue Average Low                             |

| 88   | LUMAVGH                |   |      | I    | _UM | AVG  | Н     |       |       | Luminance Average High                       |

| 89   | LUMAVGL                |   |      |      | _UM | AVG  | L     |       |       | Luminance Average Low                        |

Table 8-1. Register Map (continued)

| EPLPIX URROW OISEVARH |                                                   |                                                           |                                                                  | REP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                             | (                                                                                                                    |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 1 1 1 1 1                                                                                                     |

|-----------------------|---------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| OISEVARH              |                                                   |                                                           | (                                                                | חום                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                             |                                                                                                                      |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Number of Pixels Replaced                                                                                       |

|                       |                                                   |                                                           |                                                                  | JUK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ROV                                                                         | V                                                                                                                    |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Current Row being output (8 MSBs only)                                                                          |

| OISEVARI              |                                                   |                                                           | N                                                                | OISE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VAF                                                                         | RH                                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Dark Noise Variance High                                                                                        |

| OIOL V/ II L          |                                                   |                                                           | N                                                                | OISE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EVAF                                                                        | RL                                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Dark Noise Variance Low                                                                                         |

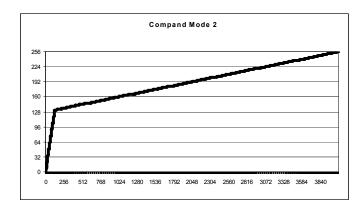

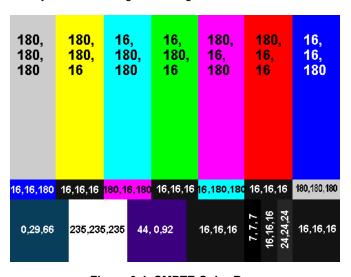

| CTROWSH               | ACTROWSH                                          |                                                           |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                                      |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Number of Active Rows High                                                                                      |