## MC68QH302

# Advance Information MC68QH302 Quad HDLC Integrated Multiprotocol Processor Technical Summary

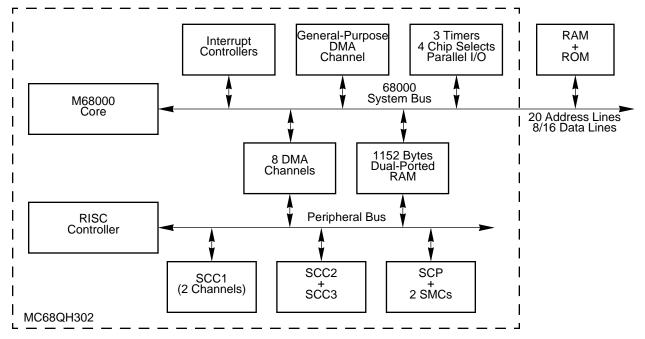

The MC68QH302, quad HDLC integrated multiprotocol processor, is based on the three-SCC MC68302 family of chips with the addition of the QH protocol and two extra serial DMA channels. The QH302 supports a total of four independent communications channels, handling two HDLC or transparent channels on SCC1; see Figure 1 for a block diagram.

In non-QH mode, the QH302 can be used in standard 302 applications as well.

To locate any published errata or updates for this document, refer to the website at http://www.mot.com/netcomm.

Figure 1. MC68QH302 Block Diagram

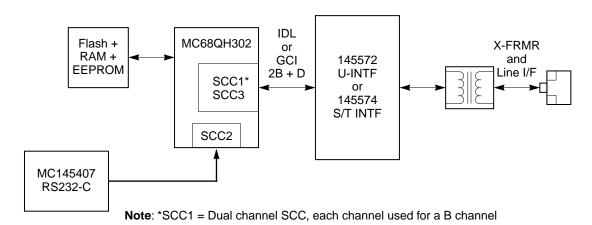

The MC68QH302 supports a full ISDN basic rate interface with one serial channel left over to communicate with the DTE as shown in Figure 2. The dual-channel SCC1 is used to support the two B channels.

Figure 2. MC68QH302 Supporting a Full ISDN Basic Rate Interface

#### 1.1 FEATURES

The main features of the MC68QH302 are as follows (**new features indicated in bold**):

- MC68000/MC68008 microprocessor core (may be disabled to use the IMP as a peripheral)

- Serial interface block including:

- Independent direct memory access (IDMA) controller

- Interrupt controller with two modes of operation

- Parallel I/O ports, some with interrupt capability

- On-chip 1152 bytes of dual-ported RAM

- Three timers, including a software watchdog timer

- Four programmable chip-select lines with wait-state logic

- Programmable address mapping of dual-ported RAM and IMP registers

- On-chip clock generator with an output clock signal

- System control

- System control register

- Bus arbitration logic with low-interrupt latency support

- Hardware watchdog for monitoring bus activity

- Low power (standby) modes

- Disable CPU logic (M68000)

- Freeze control for debugging selected on-chip peripherals

- DRAM refresh controller

- CP including:

- Main controller (RISC processor)

- Three physical full-duplex serial communication controllers (SCCs) with the following protocols:

- HDLC/SDLC

- UART

- Totally transparent

- V.110

- SCC1 can support two logical HDLC or transparent channels running QH protocol

- Eight serial DMA channels dedicated to the four serial channels

- Capability to send /receive up to eight buffers/frames without M68000 core intervention

- Flexible physical interface accessible by SCCs for interchip digital link (IDL), general circuit interface (GCI, also called IOM2), pulse code modulation (PCM), and nonmultiplexed serial interface (NMSI) operation

- Serial communication port (SCP) for synchronous communication

- Serial management controllers (SMCs) for IDL and GCI channels

- Application development system available with M68302FADS.

### 1.2 MC68QH302 Ordering Information

Table 1 identifies operating frequencies available for the MC68QH302.

Table 1. MC68QH302 Package/Frequency Availability

| Package Type                            | Operating<br>Voltage | Frequency<br>(MHz) | Temperature   | Order Number  |

|-----------------------------------------|----------------------|--------------------|---------------|---------------|

| 144-pin thin quad flat pack (PV suffix) | 5 V                  | 16.67              | 0° C to 70° C | MC68QH302PV16 |

|                                         |                      | 20                 |               | MC68QH302PV20 |

|                                         |                      | 25                 |               | MC68QH302PV25 |

The documents listed in Table 2 contain detailed information on the MC68QH302. These documents can be obtained from the Literature Distribution Centers at the addresses listed on the back page. Visit the website at http://www.mot.com/netcomm/ for more information.

**Table 2. Documentation**

| Document Title                                    | Order Number     | Contents                                                                                                      |

|---------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------|

| MC68302 User's Manual                             | MC68302UM/AD     | Detailed information for design                                                                               |

| M68000 Family Programmer's Reference<br>Manual    | M68000PM/AD      | M68000 family instruction set                                                                                 |

| The 68K Source                                    | BR729/D          | Independent vendor listing supporting software and development tools                                          |

| The MC68QH302 Supplement to MC68302 User's Manual | MC68QH302SUPL/AD | Highlights implementation-specific features of the MC68QH302, and discusses how they differ from the MC68302. |

Information in this document is provided solely to enable system and software implementers to use PowerPC microprocessors. There are no express or implied copyright licenses granted hereunder to design or fabricate PowerPC integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and (M) are registered trademarks of Motorola, Inc. Mfax is a trademark of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Motorola Literature Distribution Centers:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 5405; Denver, Colorado 80217; Tel.: 1-800-441-2447 or (303) 675-2140

JAPAN: Nippon Motorola Ltd SPD, Strategic Planning Office 4-32-1, Nishi- Gotanda Shinagawa-ku, Tokyo 141, Japan Tel.: 81-3-5487-8488

ASIA/PACIFC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong; Tel.: 852-26629298

Mfax™: RMFAX0@email.sps.mot.com; TOUCHTONE (602) 244-6609; US & Canada ONLY (800) 774-1848

INTERNET: http://motorola.com/sps

Technical Information: Motorola Inc. SPS Customer Support Center; (800) 521-6274; electronic mail address: crc@wmkmail.sps.mot.com.

**Document Comments**: FAX (512) 895-2638, Attn: RISC Applications Engineering.

World Wide Web Address: http://www.mot.com/netcomm/