# CY3LV512/010

# 512K / 1 Mbit CPLD Boot EEPROM

#### Features

- EE Reprogrammable 524,288 x 1- and 1,048,576 x 1-bit Serial Memories Designed to Store Configuration Data for Complex Programmable Logic Devices (CPLDs)

- In-System Programmable via two-wire Bus using Cypress's CYDH2200E Programming Kits

- · Simple Interface to SRAM-based CPLDs

- Compatible with Cypress Delta39K<sup>™</sup> & Quantum38K<sup>™</sup> CPLDs

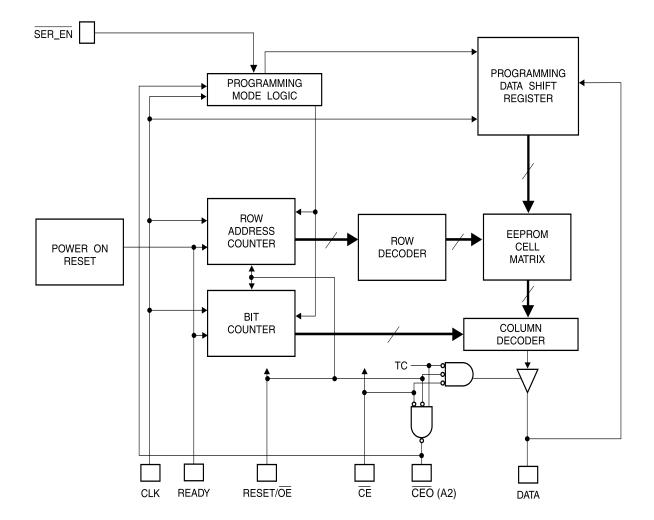

#### Block Diagram

- · Cascadable Read-Back to Support Higher-density CPLDs

- Low-power CMOS EEPROM Process

- Available in PLCC Package (Pin Compatible Across Product Family)

- Operate at 3.3V V<sub>CC</sub>

- System-friendly READY Pin

- Low-power Standby Mode

San Jose ٠

CA 95134 • 408-943-2600 Revised December 28, 2002

## **Functional Description**

The CY3LV512/010 (high-density CY3LV Series) CPLD boot EEPROMs provide an easy-to-use, cost-effective configuration memory for Complex Programmable Logic Devices. The CY3LV Series is packaged in the popular 20-pin PLCC. These devices support a system-friendly READY pin, which signifies a "good" power level to the CPLD and can be used to ensure reliable system power-up.

The CY3LV Series boot PROMs can be programmed with industry-standard programmers or Cypress's CYDH2200E CPLD boot PROM programming kit. Please refer to the data sheet "CYDH2200E CPLD Boot PROM Programming Kit" for details.

#### **CPLD Master Serial Mode Summary**

The I/O and logic functions of the CPLD and their associated interconnections are established by loading configuration data (bitstream) into the CPLD. This configuration data is loaded either automatically upon power-up, or upon issuing JTAG-command. The configuration data is stored in the internal Flash memory (Self-Boot packages only) or in the external CPLD boot PROM memory. This data is loaded from the appropriate memory depending on the state of the CPLD mode select pin (MSEL).

In Master Serial mode (when MSEL=1), the CPLD automatically loads the configuration program from an external memory i.e., CY3LV CPLD boot PROM. These PROMs have been designed for compatibility with the Master Serial Mode. This document discusses the interface between Cypress's SRAM based CPLDs (Quantum38K and Delta39K) and CY3LV PROMs.

For more details on the other modes of configuration of these CPLDs please refer to the application note titled "Configuring Delta39K/Quantum38K."

#### Controlling the CY3LV CPLD Boot PROMs During Configuration

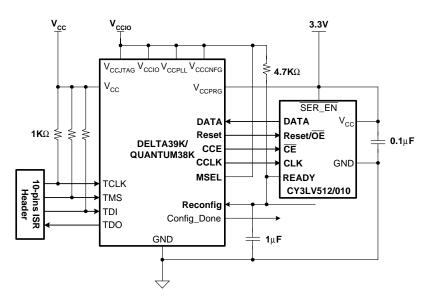

Most connections between the CPLD device and the CY3LV boot PROM are simple and self-explanatory. *Figure 1* shows the five signal interface required between the Delta39K/Quantum38K CPLD and the CY3LV boot PROM device.

- The DATA output of the boot PROM drives DATA input of the CPLD

- The master CPLD CCLK output drives the CLK input of the boot PROM

- The CPLD CCE pin drives the CE input of the boot PROM

- The RESET/ $\overline{\text{OE}}$  input of the boot PROM is driven by the CPLD RESET pin

- The READY pin of the boot PROM is connected to the RE-CONFIG pin of the CPLD

The READY pin is available as an open-collector indicator of the device's RESET status; it is driven LOW while the device is in its POWER-ON RESET cycle and released (three-stated) when the cycle is complete. The rising edge of the READY (hence RECONFIG) signal causes the CPLD to start configuring. The CONFIG\_DONE, CCE and RESET output of the CPLD are set LOW, CCLK is activated and CPLD starts receiving configuration data on the DATA pin. After all the configuration data is shifted in, the CPLD device deactivates the CCLK and sets CCE, RESET and CONFIG\_DONE HIGH.

A HIGH level on the RESET/ $\overline{\text{OE}}$  input — during CPLD reset — clears the boot PROM's internal address pointer and subsequent reconfiguration starts at the beginning.

The  $\overline{CEO}$  output of any CY3LV drives the  $\overline{CE}$  input of the next CY3LV in a cascade chain of EEPROMs.

SER\_EN must be connected to V<sub>CC</sub>, (except during In-System Programming).

Figure 1. Interface between Delta39K/Quantum38K CPLD and CY3LV boot PROM

#### Note:

Currently, 3 revisions of Delta39K100 and 2 revisions of Quantum38K100 devices are available marked as CY39100Vxxx, CY39100VxxA, and CY39100VxxB, CY38100Vxxx, and CY38100VxxB. *Figure 1* set-up represents the interface between CY39100VxxB/CY38100VxxB and CY3LV device. To get details on interface between other versions and CY3LV please refer to the application note titled "Configuring Delta39K/Quantum38K."

Setup in *Figure 1* also represents the interface between all other devices in Delta39K/Quantum38K families and CY3LV boot PROMs.

#### Cascading CY3LV CPLD boot PROMs

For future CPLDs requiring larger configuration memories, cascaded CPLD boot PROMs provide additional memory.

As the last bit from the first boot PROM is read, the clock signal to the boot PROM asserts its CEO output LOW and disables its DATA line driver. The second boot PROM recognizes the Low level on its CE input and enables its DATA output.

After configuration is complete, the address counters of all cascaded boot PROMs are reset if the RESET/OE on each boot PROM is driven to its active (HIGH) level.

#### **CY3LV Series RESET Polarity**

The CY3LV Series CPLD boot PROMs allow the user to program the reset polarity as either RESET/OE or RESET/OE.Cypress's SRAM based CPLDs (Delta39K and Quantum38K) require the RESET pin to be programmed active-High, i.e. as RESET/OE. CY3LV boot PROMs are shipped from the factory with the reset polarity programmed active-High. This polarity can be verified using industry standard programmers or Cypress's CYDH2200E boot PROM programming kit.

Note: Every time the boot PROM is reprogrammed, care should be taken to select the reset polarity to be "HIGH" programmer software.

#### **Programming Mode**

The programming mode is entered by bringing  $\overline{SER}_{EN}$  LOW. In this mode the chip can be programmed by the two-wire serial bus. The programming is done at V<sub>CC</sub> (3.3V nominal) supply only. The CY3LV parts are read/write at 3.3V nominal.

#### **Standby Mode**

The CY3LV enters a low-power standby mode whenever  $\overline{CE}$  is asserted High. In this mode, the boot PROM consumes less than 0.5 mA of current at 3.3V with CMOS level inputs. The output remains in a high-impedance state regardless of the state of the  $\overline{OE}$  input.

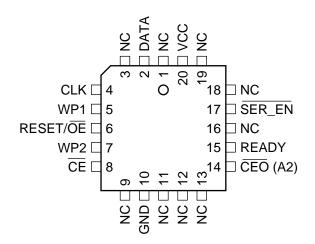

## Table 1. Pin Configurations

| 20-pin<br>PLCC | Name                   | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|----------------|------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2              | DATA                   | I/O | Three-state DATA output for configuration. Open-collector bidirectional pin for programming.                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 4              | CLK                    | Ι   | <b>lock input.</b> Used to increment the internal address and bit counter for reading and program-<br>ning.                                                                                                                                                                                                                                                                                                           |  |  |  |

| 5              | WP1                    | Ι   | <b>VRITE PROTECT (1).</b> Used to protect portions of memory during programming. Disabled<br>y default due to internal pull-down resistor. This input pin is not used during CPLD loading<br>perations.                                                                                                                                                                                                               |  |  |  |

| 6              | RE <u>SE</u> T /<br>OE | Ι   | <b>RESET/Output Enable input (when SER_EN is HIGH).</b> A LOW level on both the CE and RESET/OE inputs enables the data output driver. A HIGH level on RESET/OE resets both the address and bit counters. The logic polarity of this input is programmable as either RESET/OE or RESET/OE. Delta39K/Quantum38K CPLDs require this pin to be programmed as RESET/OE hence this document describes the pin as RESET/OE. |  |  |  |

| 7              | WP2                    | I   | <b>WRITE PROTECT (2).</b> Used to protect portions of memory during programming. Disabled by default due to internal pull-down resistor. This input pin is not used during CPLD loading operations.                                                                                                                                                                                                                   |  |  |  |

| 8              | CE                     | Ι   | <b>Chip Enable input.</b> Used for device <u>selection</u> . A LOW level on both $\overline{CE}$ and $\overline{OE}$ enables the data output driver. A HIGH level on $\overline{CE}$ disables both the address and bit counters and forces the device into a low-power standby mode. Note that this pin will not enable/disable the device in the two-wire Serial Programming Mode (i.e., when SER_EN is LOW).        |  |  |  |

| 10             | GND                    |     | Ground pin. A 0.1 $\mu$ F decoupling capacitor between V <sub>CC</sub> and GND is recommended                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 14             | CEO                    | 0   | <b>Chip Enable Output.</b> This signal is asserted LOW on the clock cycle following the last bit read from the memory. It will stay LOW as long as CE and OE are both LOW. It will then follow CE until OE goes HIGH. Thereafter, CEO will stay HIGH until the entire EEPROM is read again.                                                                                                                           |  |  |  |

|                | A2                     | I   | <b>Device selection input, A2.</b> This is used to enable (or select) the device during programming (i.e., when SER_EN is LOW).                                                                                                                                                                                                                                                                                       |  |  |  |

| 15             | READY                  | 0   | <b>Open collector reset state indicator.</b> Driven LOW during power-up reset, released when power-up is complete. (Recommend a 4.7 k $\Omega$ pull-up on this pin if used).                                                                                                                                                                                                                                          |  |  |  |

| 17             | SER_EN                 | Ι   | Serial enable must be held High during CPLD loading operations. Bringing SER_EN LOW enables the two-wire Serial Programming Mode.                                                                                                                                                                                                                                                                                     |  |  |  |

| 20             | VCC                    |     | +3.3V power supply pin.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

# **Pin Configurations**

## **Maximum Ratings**

| (Above which the useful life may be impaired. For user guide- |  |  |  |  |

|---------------------------------------------------------------|--|--|--|--|

| lines, not tested.)                                           |  |  |  |  |

| Operating Temperature55°C to +125°C                           |  |  |  |  |

Storage Temperature ......-65°C to +150°C

## Operating Range <sup>[1]</sup>

| Voltage on Any Pin<br>with Respect to Ground–0.1V to V <sub>CC</sub> + 0.5V |

|-----------------------------------------------------------------------------|

| Supply Voltage (V <sub>CC</sub> )0.5V to +7.0V                              |

| Maximum Soldering Temp. (10 sec. @ 1/16in.)                                 |

| ESD (R <sub>ZAP</sub> = 1.5K, C <sub>ZAP</sub> = 100 pF)2000V               |

| Range      | Ambient Temperature | Junction Temperature | CY3LV512/010 (V <sub>CC</sub> ) |  |  |

|------------|---------------------|----------------------|---------------------------------|--|--|

| Commercial | 0°C to + 70°C       | 0°C to + 90°C        | $3.3 \text{V} \pm 0.3 \text{V}$ |  |  |

| Industrial | -40°C to + 85°C     | –40°C to + 125°C     | $3.3V\pm0.3V$                   |  |  |

| Military   | –55°C to + 125°C    | –55°C to + 130°C     | $3.3V\pm0.3V$                   |  |  |

## 3.3V Device Electrical Characteristics Over the Operating Range

| Parameter        | Description                                                                |                     | Min, | Max,            | Unit |

|------------------|----------------------------------------------------------------------------|---------------------|------|-----------------|------|

| V <sub>IH</sub>  | High-level input voltage                                                   |                     |      | V <sub>CC</sub> | V    |

| V <sub>IL</sub>  | Low-level input voltage                                                    |                     | 0    | 0.8             | V    |

| V <sub>OH</sub>  | High-level output voltage ( $I_{OH} = -2.5 \text{ mA}$ )                   | Commercial          | 2.4  |                 | V    |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +3 mA)                         |                     |      | 0.4             | V    |

| V <sub>OH</sub>  | High-level output voltage ( $I_{OH} = -2 \text{ mA}$ )                     | Industrial          | 2.4  |                 | V    |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +3 mA)                         |                     |      | 0.4             | V    |

| V <sub>OH</sub>  | High-level output voltage ( $I_{OH} = -2 \text{ mA}$ )                     | Military            | 2.4  |                 | V    |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +2.5 mA)                       |                     |      | 0.4             | V    |

| I <sub>CCA</sub> | Supply current, active mode                                                |                     |      | 5               | mA   |

| IL               | Input or output leakage current (V <sub>IN</sub> = V <sub>CC</sub> or GND) |                     | -10  | 10              | μA   |

| I <sub>CCS</sub> | Supply current, standby mode                                               | Commercial          |      | 100             | μΑ   |

|                  |                                                                            | Industrial/Military |      | 100             | μΑ   |

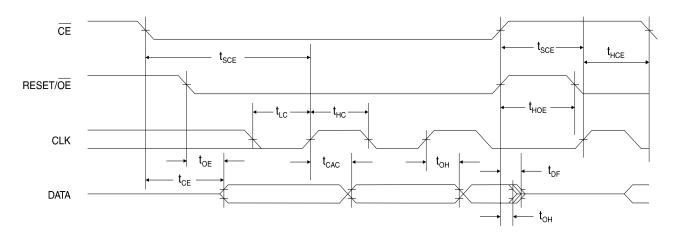

## Switching Characteristics for CY3LV512/010 (3.3V) Over the Operating Range

|                                                   | Commercial Ir                                             |      | Indu | strial |      |      |

|---------------------------------------------------|-----------------------------------------------------------|------|------|--------|------|------|

| Parameter                                         | Description                                               | Min. | Max. | Min.   | Max. | Unit |

| T <sub>OE</sub> <sup>[2]</sup>                    | OE to Data Delay                                          |      | 50   |        | 55   | ns   |

| T <sub>CE</sub> <sup>[2]</sup>                    | CE to Data Delay                                          |      | 55   |        | 60   | ns   |

| T <sub>CAC</sub> <sup>[2]</sup>                   | CLK to Data Delay                                         |      | 55   |        | 60   | ns   |

| Т <sub>ОН</sub>                                   | Data Hold From $\overline{CE}$ , $\overline{OE}$ , or CLK | 0    |      | 0      |      | ns   |

| T <sub>OH</sub><br>T <sub>DF</sub> <sup>[3]</sup> | CE or OE to Data Float Delay                              |      | 50   |        | 50   | ns   |

| T <sub>LC</sub>                                   | CLK Low Time                                              | 25   |      | 25     |      | ns   |

| Т <sub>НС</sub>                                   | CLK High Time                                             | 25   |      | 25     |      | ns   |

| T <sub>SCE</sub>                                  | CE Setup Time to CLK (to guarantee proper counting)       | 30   |      | 35     |      | ns   |

| T <sub>HCE</sub>                                  | CE Hold Time from CLK (to guarantee proper counting)      | 0    |      | 0      |      | ns   |

| T <sub>HOE</sub>                                  | OE High Time (guarantees counter is reset)                | 25   |      | 25     |      | ns   |

| F <sub>MAX</sub>                                  | MAX Input Clock Frequency                                 | 15   |      | 10     |      | MHz  |

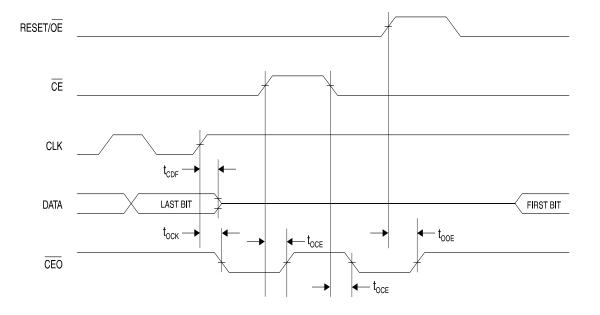

## Switching Characteristics for CY3LV512/010 (3.3V) when Cascading Over the Operating Range

|                                 |                           | Commercial |      | Industrial |      |      |

|---------------------------------|---------------------------|------------|------|------------|------|------|

| Parameter                       | Description               | Min.       | Max. | Min.       | Max. | Unit |

| t <sub>CDF</sub> <sup>[3]</sup> | CLK to Data Float Delay   |            | 50   |            | 50   | ns   |

| t <sub>OCK</sub> <sup>[2]</sup> | CLK to CEO Delay          |            | 50   |            | 55   | ns   |

| t <sub>OCE</sub> <sup>[2]</sup> | CE to CEO Delay           |            | 35   |            | 40   | ns   |

| t <sub>OOE</sub> <sup>[2]</sup> | RESET/OE to CEO Delay     |            | 35   |            | 35   | ns   |

| F <sub>MAX</sub>                | MAX Input Clock Frequency | 12.5       |      | 10         |      | MHz  |

## 3.3V Ordering Information

| Memory Size | Ordering Code | Package<br>Name | Package Type                        | Operating<br>Range |

|-------------|---------------|-----------------|-------------------------------------|--------------------|

| 1M          | CY3LV010-10JC | 20J             | 20-Lead Plastic Leaded Chip Carrier | Commercial         |

|             | CY3LV010-10JI | 20J             | 20-Lead Plastic Leaded Chip Carrier | Industrial         |

| 512K        | CY3LV512-10JC | 20J             | 20-Lead Plastic Leaded Chip Carrier | Commercial         |

|             | CY3LV512-10JI | 20J             | 20-Lead Plastic Leaded Chip Carrier | Industrial         |

Notes:

AC test load = 50 pF.

Float delays are measured with 5 pF AC loads. Transition is measured ±200 mV from steady state active levels.

<sup>1.</sup> The Voltage on any input or I/O pin cannot exceed the power pin during power-up.

## **AC Characteristics**

# AC Characteristics when Cascading

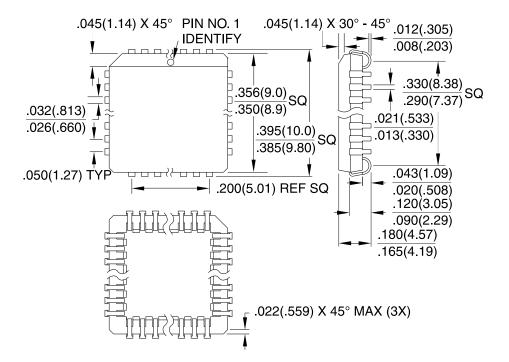

#### Package Diagrams: 20J, 20-lead, Plastic J-leaded Chip Carrier (PLCC)

Dimensions in Inches and (Millimeters)

© Cypress Semiconductor Corporation, 2001. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor against all charges.

| Document Title: CY3LV512/010 512K/1 Mbit CPLD BOOT EEPROM DATASHEET (Preliminary)<br>Document Number: 38-03002 |        |          |                       |                                                            |  |  |  |

|----------------------------------------------------------------------------------------------------------------|--------|----------|-----------------------|------------------------------------------------------------|--|--|--|

| REV. ECN NO. Issue Orig. of Change                                                                             |        |          | Description of Change |                                                            |  |  |  |

| **                                                                                                             | 106080 | 08/07/01 | RN                    | New Data Sheet                                             |  |  |  |

| *A                                                                                                             | 122216 | 12/28/02 | RBI                   | Power up requirements added to Operating Range Information |  |  |  |