# TMS320DM335 Digital Media System-on-Chip (DMSoC) Silicon Revision 1.1

# Silicon Errata

Literature Number: SPRZ287A July 2008-Revised October 2008

## **Contents**

| 1 | Introdu | uction      |                                                                                                  | 5    |

|---|---------|-------------|--------------------------------------------------------------------------------------------------|------|

|   | 1.1     |             | and Development Support Tool Nomenclature                                                        |      |

|   | 1.2     | Revision    | n Identification                                                                                 | 6    |

| 2 |         | n Revisions | n 1.1 Usage Notes and Known Design Exceptions to Functional                                      | 7    |

|   | 2.1     | Usage I     | Notes for Silicon Revision 1.1                                                                   |      |

|   |         | 2.1.1       | Possible Emulator Crash If TCK Frequency Is Greater than MXI Frequency                           | 7    |

|   |         | 2.1.2       | DM335 EVM V <sub>SS_USB_REF</sub> Pin Not Connected As Specified                                 | 7    |

|   |         | 2.1.3       | SD/SDIO card: How to Read M bytes (M=1, 2, 3) from SD or SDIO card                               | 7    |

|   |         | 2.1.4       | SD/SDIO card: How to Handle SDIO interrupt                                                       | 8    |

|   |         | 2.1.5       | Peripherals: Electrostatic Discharge (ESD) Sensitivity Classification                            | 8    |

|   |         | 2.1.6       | ASP: Transfers Should be Buffered in Internal Memory                                             | 9    |

|   |         | 2.1.7       | ASP: Initialization Procedure When External Device is Frame-Sync Master                          | 9    |

|   |         | 2.1.8       | NAND Layout Assumed by RBL for Big Block NAND Does Not Match NAND Manufacturers' Recommendations | 9    |

|   |         | 2.1.9       | GIO0 Low Setting During Device Boot May Cause Boot to Fail                                       | . 10 |

|   | 2.2     | Silicon I   | Revision 1.1 Known Design Exceptions to Functional Specifications                                | . 11 |

|   | Revisi  | on Histo    | ry                                                                                               | 25   |

## **List of Figures**

| 1 | Example, Device Revision Codes for TMS320DM335 (ZCE)                            | 6  |

|---|---------------------------------------------------------------------------------|----|

| 2 | Expected CSHOLD Behavior                                                        |    |

| 3 | Actual CSHOLD Behavior–32-Bit Writes to SPIDAT1                                 | 18 |

| 4 | Actual CSHOLD Behavior-Halfword Writes to SPIDAT1                               | 19 |

| 5 | Workaround Assuming 32-Bit Writes to SPIDAT1 Followed by a Write Only to CSHOLD | 19 |

| 6 | Workaround Assuming Halfword Writes to SPIDAT1                                  | 19 |

| 1 | List of Tables  Device Silicon Revisions                                        | 6  |

| 2 | Silicon Revision 1.1 Advisory List                                              |    |

| 3 | Bug Summary for the 0 Wait State Configuration                                  |    |

| 4 | Bug Summary for the 1 Wait State Configuration                                  |    |

| 5 | USB Electrical Characteristics in Violation                                     | 20 |

| 6 | Revision History                                                                | 25 |

# TMS320DM335 Digital Media System-on-Chip (DMSoC) Silicon Revision 1.1

#### 1 Introduction

This document describes the known exceptions to the functional specifications for the TMS320DM335 Digital Media System-on-Chip (DMSoC). [See *TMS320DM335 Digital Media System-on-Chip Data Manual* (literature number <u>SPRS528</u>).]

The advisory numbers in this document may not be sequential. Some advisory numbers may be moved to the next revision and others may have been removed and documented in the user's guide. When items are moved or deleted, the remaining numbers remain the same and are not resequenced.

This document also contains Usage Notes. Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### 1.1 Device and Development Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all DSP devices and support tools. Each DSP commercial family member has one of three prefixes: TMX, TMP, or TMS (e.g., **TMS320DM335**). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully qualified production devices/tools (TMS/TMDS).

Device development evolutionary flow:

**TMX** Experimental device that is not necessarily representative of the final device's electrical

specifications

**TMP** Final silicon die that conforms to the device's electrical specifications but has not completed

quality and reliability verification

**TMS** Fully-qualified production device

Support tool development evolutionary flow:

**TMDX** Development-support product that has not yet completed Texas Instruments internal

qualification testing

**TMDS** Fully-qualified development-support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

TMS devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. Tl's standard warranty applies.

Introduction www.ti.com

Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

#### 1.2 Revision Identification

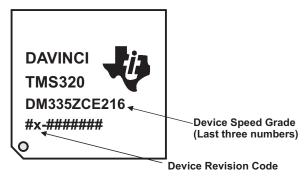

Figure 1 provide examples of the *TMS320DM335* and device markings. The device revision can be determined by the symbols marked on the top of the package. Some prototype devices may have markings different from those illustrated.

Figure 1. Example, Device Revision Codes for TMS320DM335 (ZCE)

#### NOTES:

- A. Qualified devices are marked with the letters "TMS" at the beginning of the device name, while nonqualified devices are marked with the letters "TMX" or "TMP" at the beginning of the device name.

- B. "#" denotes an alphanumeric character. "x" denotes an alpha character only.

Silicon revision is identified by a code on the chip as shown in Figure 1. If x is "blank", then the silicon is revision 1.1. Table 1 lists the silicon revisions associated with each device revision code for the DM335 device.

| Device Revision Code (x) | SILICON REVISION       | COMMENTS                              |

|--------------------------|------------------------|---------------------------------------|

| (blank)                  | Indicates Revision 1.1 | TMS320DM335ZCE135, TMS320DM335ZCE216, |

**Table 1. Device Silicon Revisions**

# 2 Silicon Revision 1.1 Usage Notes and Known Design Exceptions to Functional Specifications

#### 2.1 Usage Notes for Silicon Revision 1.1

Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### 2.1.1 Possible Emulator Crash If TCK Frequency Is Greater than MXI Frequency

If the frequency of TCK is greater than the frequency of MXI, there is a chance the emulator will crash when changing the PLL1 clock frequency. This can happen while stepping through code that configures the PLL1 controller or while using a GEL function that configures the PLL1 controller.

Additionally, the act of applying reset could cause the clock on the TCK pin to stop being generated, thereby crashing the emulator. This condition happens if the TCK frequency is 2x or greater than the MXI frequency during reset.

To avoid both of these issues, the MXI clock frequency must be greater than or equal to the TCK clock frequency.

#### 2.1.2 DM335 EVM V<sub>SS USB REF</sub> Pin Not Connected As Specified

On some versions of the DM335 EVM, the  $V_{SS\_USB\_REF}$  pin is not connected as specified in the data sheet. This *does not* create any USB functional issues; however, for USB compliance, DM335 designs *must* follow the pin connection specified in the USB Reference Resistor Routing figure in the *TMS320DM335 Digital Media System-on-Chip (DMSoC)* data sheet (literature number SPRS528).

#### 2.1.3 SD/SDIO card: How to Read M bytes (M=1, 2, 3) from SD or SDIO card

Direction: Read from SD or SDIO

Data size: 32\*N+M byte (where M=1, 2, 3 and N=0, 1, 2, 3,...) FIFO size is 32 bytes (ACCWD (FIFOCTL [4:3] = 0), FIFO trigger level is 256-bits (FIFOLEV (MMCFIFOCTL [2]) =1)

Reading from SD or SDIO when FIFO Trigger Level FIFOLEV is 256 bits causes the DRRDY(MMCST0[10]) bit not to be set for the last M bytes of the above data size equation and therefore the DMA read event and CPU interrupt for RRDY(MMCST0[10]) are not getting asserted, but the data in FIFO is correct.

There are two possible methods to work around this limitation.

- 1. Include SD status checking and/or SD interrupt enable for TRNDNE (MMCST0 [12]) or DATDNE (MMCST0 [0])

- 2. Use 128-bit FIFO trigger level (i.e. FIFOLEV (MMCFIFOCTL [2]) =0), since this is only a problem when FIFOLEV is 256 bits.

#### Note:

- 1. To ensure the start of the MMCSD transfer correctly, the DMATRIG bit (MMCCMD [16]) should always be set to '1' when writing the command to MMCCMD registers.

- 2. For SDIO read and write function, the MMCBLEN and MMCNBLK registers have to be set to equal the total byte count and total block count configured by the SDIO command (CMD52 or CMD53). For example, to read 3 bytes using CMD53, the software has to set MMCBLEN=3 and MMCNBLK=1.

- 3. The FIFOFUL and FIFOEMP status bits are set based on access size(ACCWD):

- If the number of bytes stored in the FIFO is smaller than access size, FIFOEMP is 1. Otherwise, FIFOEMP is 0.

- If the size of the remaining empty spaces in FIFO is smaller than access size, FIFOFUL is 1.

Otherwise, FIFOFUL is 0.

For example, when the access size (ACCWD) is 4 bytes and the FIFO level (FIFOLEV=1) is 256-bits or 32 bytes, and if the number of bytes in FIFO is

- 0 to 3: then, FIFOFUL=0, FIFOEMP=1

- 4 to 28: then, FIFOFUL=0, FIFOEMP=0

- 29 to 32: then, FIFOFUL=1, FIFOEMP=0

#### 2.1.4 SD/SDIO card: How to Handle SDIO interrupt

SDIO interrupt may be missed since SDIO interrupt processing is only done based on the IOINT (SDIOIST [0]) status.

SDIO Interrupt Detecting: SDIO interrupt is a level interrupt on SDIO protocol, but the interrupt generation logic detects the edge of DAT1 signal inside the host controller.

SDIO Interrupt Masking: The SDIO Interrupt may be enabled or disabled by the SDIO stack at any time.

SDIO Interrupt Status Clearing: SDIO interrupt status may not be cleared in an atomic sequence since a pending interrupt has to be cleared not only on the host controller but also on the SDIO module.

To guarantee that the SDIO interrupt is not missed, the host controller has to check the IOINT (SDIOIST[0]) status register as well as sample the DAT1 signal by checking the DAT1(SDIOST0[1-0]) status register at a certain condition.

The following is a suggested sequence for properly handling the SDIO interrupt:

- 1. SDIO stack informs the SDIO host controller to enable or unmask the SDIO interrupt.

- SDIO host controller enables or unmasks the SDIO interrupt. Before enabling the SDIO interrupt, the SDIO host controller software has to first sample the DAT1 signal (INTPRD==1 && DAT1==1) to make sure that the pending interrupt is reported to the SDIO stack and then to the SDIO client/function driver.

**Note:** SDIO interrupt is enabled at the request of the client/function driver of the SDIO stack. SDIO interrupt needs to be enabled both on the host controller and the SDIO card which may not happen in an atomic way. By the time the host controller enables the interrupt, the SDIO interrupt may be already pending. The SDIO controller can not detect interrupt pending before the interrupt is enabled on the controller.

- 3. When the SDIO interrupt is detected by the SDIO controller, the SDIO ISR has to process the SDIO interrupts in the following sequence:

- Check and clear SDIO interrupt status IOINT(SDIOIST[0]) immediately.

- Mask the SDIO interrupt on the SDIO host controller by setting IOINTEN (SDIOIEN[0]) =0.

- Notify the Interrupt event first to the SDIO stack and then to the SDIO client/function driver.

**Note:** The clearing of the SDIO interrupt on the SDIO card and SDIO controller does not happen in an atomic way. To mask the SDIO interrupt, it has to be ensured that the interrupt is not mistakenly detected by the host controller again. In addition, the client/function driver of the SDIO stack can therefore control the occurrence of interrupt and also the readiness to process the interrupt.

4. The SDIO stack client/function driver clears the SDIO interrupt status on the SDIO card.

#### 2.1.5 Peripherals: Electrostatic Discharge (ESD) Sensitivity Classification

JESD22-A114D, Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM), test results indicate that the TMS320DM335 device's electrostatic discharge (ESD) sensitivity classification is Class 0 due to 4 reserved pins (BGA ID: J1, K1, L1, M1). All other pins meet the Texas Instruments design goal ESD testing classification of Class 2. No workaround is required. Standard ESD-sensitivity device handling procedures provide sufficient protection.

JESD22-C101C, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components, testing was also conducted and results demonstrated that the TMS320DM335 device's charged-device model (CDM) sensitivity classification is Class III (500 to 1000 V). These results are consistent with the Texas Instruments CDM design goal.

#### 2.1.6 ASP: Transfers Should be Buffered in Internal Memory

In DM335 Silicon Revision 1.1, Audio Serial Port (ASP) transfers may need to originate and complete from on-chip buffers in ARM Internal RAM (TCM). This is due to the fact that there is no tolerance for audio data dropouts that may occur due to the delays in DDR2/mDDR accesses from other masters and from unavoidable DDR2/mDDR refresh cycles even if the Q0/TC0 is dedicated to transfers from off-chip memories. On-chip buffers might be needed to ensure immunity from DDR2/mDDR latencies. DDR2/mDDR latencies are system-dependent, varying between applications, and are impacted by the amount and type of data traffic to DDR2/mDDR memories. Once completed, the data can be shuttled between the internal buffer and the DDR2/mDDR memory by using EDMA Q1/TC1.

If using on-chip buffers for ASP transfers, also see the following advisories:

• 1.1.2 Concurrent Access to ARM Internal Memory May Result in Access Errors

#### 2.1.7 ASP: Initialization Procedure When External Device is Frame-Sync Master

On DM335 Silicon Revision 1.1, if the ASP transmitter expects a frame sync from an external device, care must be taken to ensure that the proper action is employed. After the transmitter comes out of reset (XRST = 1), it waits for a frame sync from the external device. If the first frame sync arrives very shortly after the transmitter is enabled, the CPU or EDMA controller may not have a chance to service the ASP data transmit register (DXR). In this case, the transmitter shifts out the default data in the transmit shift register (XSR) instead of the desired value, which has not yet arrived in the DXR. This causes problems in some applications such that the first data element in the frame is invalid. The data stream appears element-shifted (the first data word may appear in the second channel instead of the first).

To ensure proper operation when the external device is the frame master, you must make sure that the DXR is already serviced with the first word when a frame sync occurs. To do so, you can keep the transmitter in reset until the first frame sync is detected. The software is set up such that it will only take the transmitter out of reset (XRST = 1) promptly after detecting the first frame sync. This ensures that the transmitter does not begin data transfers at the data pin during the first frame-sync period. This also provides almost an entire frame period for the DM335 device to service the DXR with the first word before the second frame sync occurs. The transmitter only begins data transfers upon receiving the second frame sync. At this point, the DXR is already serviced with the first word.

The ASP transmitter and receiver on the DM335 device are capable of generating an interrupt upon the detection of frame synchronization. However, on the DM335 device, the receiver and/or transmitter must be out of reset to enable this feature. Therefore, instead of directly using the ASP interrupt to detect the first frame sync, on the DM335 device you can use the GPIO peripheral. This can be achieved by connecting the frame-sync signal to a GPIO pin. The software can either poll the GPIO pin to detect the first frame sync or program the GPIO peripheral to generate an interrupt to the CPU upon detecting the first frame-sync edge. For more information on the GPIO peripheral, see the *TMS320DM335 DMSoC General-Purpose Input/Output (GPIO) User's Guide* (SPRUFY8). For details on the initialization sequence when the external device is the frame-sync master, see the *TMS320DM335 DMSoC Audio Serial Port (ASP)* User's Guide (SPRUFZ3).

# 2.1.8 NAND Layout Assumed by RBL for Big Block NAND Does Not Match NAND Manufacturers' Recommendations

Typically NAND manufactures place Bad Block information in the spare bytes area. The RBL assumes a data layout as below:

512 bytes Data 16 bytes ECC Data 512 bytes Data 16 bytes ECC Data 512 bytes Data 16 bytes ECC Data 512 bytes Data 16 bytes ECC Data

This layout can cause real data to be placed in the spare area, which would erase meta-data that is placed there by the NAND manufacturer. Typically, NAND programmers assume consecutive data followed by the meta-data in the spare areas as below:

2048 bytes Data 64 bytes ECC Data

This does not affect small block NAND (512 bytes/page). Any device with page sizes larger than 512 bytes will be affected.

#### 2.1.9 GIO0 Low Setting During Device Boot May Cause Boot to Fail

If the GIO0 pin is low during device boot from a NAND device, the DM335 will not follow the normal boot process. The DM335 ROM Boot Loader (RBL) will attempt to read the User Boot Loader (UBL) header from a different NAND page range and will look for a different number in that header than that used in the normal boot process, which may cause the boot to fail.

To prevent this issue from occurring, ensure that the GIO0 pin is held high during NAND boot. Details about this issue will be incorporated into the next revision of the *TMS320DM335 Digital Media System-on-Chip (DMSoC)* Data Manual (literature number SPRS528).

## 2.2 Silicon Revision 1.1 Known Design Exceptions to Functional Specifications

## Table 2. Silicon Revision 1.1 Advisory List

| I | itle            |                                                                          | Page |

|---|-----------------|--------------------------------------------------------------------------|------|

|   | Advisory 1.1.1  | H3A data may get corrupted                                               | . 12 |

|   | Advisory 1.1.2  | Concurrent Access to ARM Internal Memory May Result in Access Errors     | . 15 |

|   | Advisory 1.1.3  | SPI: Receive Overrun Interrupt and Bit Error Can be Lost                 | . 16 |

|   | Advisory 1.1.4  | SPI: RXINTFLG Bit in SPIFLG Register May Not Get Cleared                 | . 16 |

|   | Advisory 1.1.5  | SPI: A Write to SPIFLG Receiver Overrun Bit Does Not Clear the Flag      | . 16 |

|   | Advisory 1.1.6  | SPI: SPIINTVECT and SPIFLG Registers are Cleared When Read in Debug Mode | . 17 |

|   | Advisory 1.1.7  | SPI: SPI Master Receives Extra Bit When SPICLK Polarity Changes          | . 17 |

|   | Advisory 1.1.8  | SPI Master Mode: Extra Step Required to Use CSHOLD                       | . 18 |

|   | Advisory 1.1.9  | USB: Some Electrical Parameters Violate USB Specification                | . 20 |

|   | Advisory 1.1.10 | VPBE: VENC Default Luma Interpolation Filter Does Not Clip to Zero       | . 21 |

|   | Advisory 1.1.11 | 1 RBL Code ECC Limitation                                                | . 22 |

|   | Advisory 1.1.12 | 2 USB (Device Mode): Calculated CRC Value Does Not Match Host CRC Value  | . 23 |

|   |                 |                                                                          |      |

#### Advisory 1.1.1 H3A data may get corrupted

#### Revision(s) Affected

#### 1.1

#### **Details**

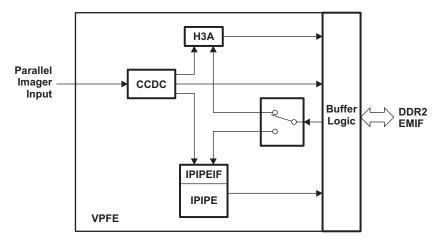

This problem affects H3A auto white balance, auto exposure, and auto focus when the image sensor data is large (i.e. greater than approximately 10 mega pixels) and the data path is from imager to CCDC to H3A .

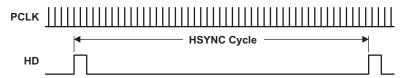

When the H3A module receives more than 4096 pixel clock cycles between consecutive HD rising edges, the H3A internal line buffer may become corrupt. The internal line buffer address is reset to zero at HD rising edge, is incremented every pixel clock cycle, and wraps back to address zero after 4096 pixel clocks. H3A calculations may not be correct when the line buffer is corrupt.

#### Workaround(s)

To workaround this problem, use any of the four workarounds described below.

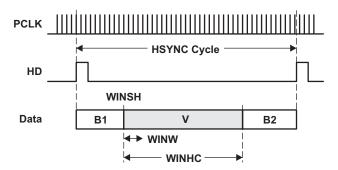

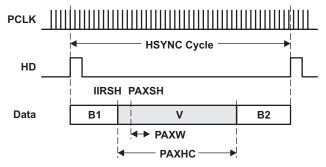

- 1. Constrain the valid AEW/AF data area. The valid data in the internal line buffer will not become corrupt under certain constraints. In particular, the problem will not occur when you adhere to the follow constraints (see figures):

- B1 + V < 4096 and

- B2 <= 4096 (B1+V) + B1

#### Where

- B1 = Data area from HD rising edge to start of valid AEW/AF data.

- V = Valid AEW/AF data area. This is the data area for AEW/AF calculations. This area is specified using registers in the H3A module. Note that the registers are different for AEW and for AF. For AEW, bits WINSH specify the horizontal start position of the AEW windows, bits WINW specify the horizontal width of the windows, and bits WINHC specify the total number of windows. The total number of pixels in the valid AEW data area is equal to V=WINW\*WINHC. For AF, bits IIRSH specify the horizontal start position of the IIR filter, bits PAXSH specify the horizontal start position of the AF paxels, bits PAXW specify the horizontal width of the paxels, and bits PAXHC specify the total number of paxels. The total number of pixels in the valid AF data area is equal to V=[ (PAXSH IIRSH) + PAXW\*PAXHC]. See the VPFE PRG for complete bit descriptions.

- B2 = Data area from end of valid AEW/AF data to next HD rising edge.

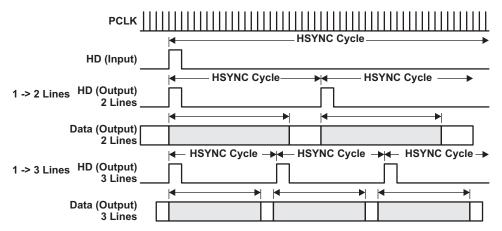

2. Use the imager's movie readout mode.

In the imager's movie readout mode the problem does not occur, because the number of horizontal pixels and blacking are is less than 4096 pixels and the H3A module receives less than 4096 pixel clock cycles between consecutive HD rising edges.

Note that the number of pixel clock cycles between consecutive HD rising edges that the H3A module receives is determined by the external or internal timing generator and also, if used, by the reformatter inside the CCDC. The reformatter is used when imagers have special readout patterns. For example, if the readout pattern contains two lines of actual image data per HSYNC, then the reformatter will convert the data from one to two lines, internally. The number of pixel clock cycles between consecutive HD rising edges that the H3A modules receives corresponds to the timing at the output of the reformatter.

- 3. Use the alternative data path for H3A. There are two possible data paths for H3A:

- a. Imager->CCDC->H3A

#### Advisory 1.1.2

#### Concurrent Access to ARM Internal Memory May Result in Access Errors

#### **Revisions Effected**

#### 1.1

#### **Details**

ARM internal memory consists of two physical memories: RAM0 and RAM1. The ARM processor can access these memories over two separate busses: ITCM bus and DTCM bus. The EDMA and USB module are DMA bus masters that can access these memories over the DMA bus, via special bus arbiters. See the *TMS320DM335 DMSoC ARM Subsystem Reference Guide* (literature number <a href="SPRUFX7">SPRUFX7</a>). Under certain conditions, access errors may occur when the ARM and these DMA bus masters attempt to access ARM internal memory at the same time. An access error means that data is not written or read properly. The conditions depend on whether ARM internal memory access is configured for 0 or 1 wait states and are further described below. Use bits AIM\_WAIST in the MISC register in the System Control Module to configure the wait states [see *TMS320DM335 DMSoC ARM Subsystem Reference Guide* (literature number <a href="SPRUFX7">SPRUFX7</a>)].

For both the 0 and 1 wait state configurations, access errors may occur under the following conditions (see Table 3 and Table 4):

- Access errors may occur in situations where an ARM DTCM access to RAM0 and a DMA bus access to RAM1 are attempted at the same time.

- Access errors may occur in situations where an ARM ITCM, an ARM DTCM, and a DMA bus access are attempted to the same physical memory (RAM0 or RAM1) at the same time.

For only the 1 wait state configuration, access errors may occur under the following conditions:

- Access errors may occur in situations where an ARM ITCM and a DMA bus access are attempted to the same physical memory (RAM0 or RAM1) at the same time.

- Access errors may occur in situations where an ARM DTCM and a DMA bus access are attempted to the same physical memory (RAM0 or RAM1) at the same time.

#### Workaround(s)

Avoid the conditions that cause accesses errors. Design your software so that accesses to ARM internal memory are according to the Bug Summary Table 3 and Table 4). In the tables, P means that no bug will occur under the corresponding conditions.

Table 3. Bug Summary for the 0 Wait State Configuration

|                 |    | 3  | ACT | IVE / | ACCI | ESSE | S  |    | 2 ACTIVE ACCESSES |    |    |    |    |    |    |    |    |    |    | 1 ACTIVE ACCESS |    |    |    |    |    |    |   |

|-----------------|----|----|-----|-------|------|------|----|----|-------------------|----|----|----|----|----|----|----|----|----|----|-----------------|----|----|----|----|----|----|---|

| ARM ITCM Access | R0 | R0 | R0  | R0    | R1   | R1   | R1 | R1 | R0                | R0 | R1 | R1 | R0 | R0 | R1 | R1 | n  | n  | n  | n               | R0 | n  | n  | R1 | n  | n  | n |

| ARM DTCM Access | R0 | R0 | R1  | R1    | R0   | R0   | R1 | R1 | R0                | R1 | R0 | R1 | n  | n  | n  | n  | R0 | R0 | R1 | R1              | n  | R0 | n  | n  | R1 | n  | n |

| DMA Access      | R0 | R1 | R0  | R1    | R0   | R1   | R0 | R1 | n                 | n  | n  | n  | R0 | R1 | R0 | R1 | R0 | R1 | R0 | R1              | n  | n  | R0 | n  | n  | R1 | n |

| Pass / Fail     | F  | F  | Р   | Р     | Р    | F    | Р  | F  | Р                 | Р  | Р  | Р  | Р  | Р  | Р  | Р  | Р  | F  | Р  | Р               | Р  | Р  | Р  | Р  | Р  | Р  | Р |

Table 4. Bug Summary for the 1 Wait State Configuration

|                 |    | 3  | ACT | IVE / | ACCI | ESSE | S  |    | 2 ACTIVE ACCESSES |    |    |    |    |    |    |    |    |    |    | 1 ACTIVE ACCESS |    |    |    |    |    |    |   |

|-----------------|----|----|-----|-------|------|------|----|----|-------------------|----|----|----|----|----|----|----|----|----|----|-----------------|----|----|----|----|----|----|---|

| ARM ITCM Access | R0 | R0 | R0  | R0    | R1   | R1   | R1 | R1 | R0                | R0 | R1 | R1 | R0 | R0 | R1 | R1 | n  | n  | n  | n               | R0 | n  | n  | R1 | n  | n  | n |

| ARM DTCM Access | R0 | R0 | R1  | R1    | R0   | R0   | R1 | R1 | R0                | R1 | R0 | R1 | n  | n  | n  | n  | R0 | R0 | R1 | R1              | n  | R0 | n  | n  | R1 | n  | n |

| DMA Access      | R0 | R1 | R0  | R1    | R0   | R1   | R0 | R1 | n                 | n  | n  | n  | R0 | R1 | R0 | R1 | R0 | R1 | R0 | R1              | n  | n  | R0 | n  | n  | R1 | n |

| Pass / Fail     | F  | F  | F   | F     | F    | F    | Р  | F  | Р                 | Р  | Р  | Р  | F  | Р  | Р  | F  | F  | F  | Р  | F               | Р  | Р  | Р  | Р  | Р  | Р  | Р |

Advisory 1.1.3 SPI: Receive Overrun Interrupt and Bit Error Can be Lost

Revision(s) Affected: 1.1

Details: Receive Overrun Interrupt (RXOVINT) and Bit Error interrupt (BITERRINT) can be lost if:

Reading of the SPIFLG register coincides with the setting of these interrupt flag bits. Reading of the upper 16 bits of SPIBUF register coincides with the setting of these

interrupt bits.

**Workaround:** Use the interrupt instead of the polling method to check the status of these interrupts.

Access only the lower 16 bits of the SPIBUF register to read received data.

If the polling method must be used, group the error interrupts into one Level (i.e., Level0) and the RX complete interrupt into the other Level (i.e., Level1). Use the SPIINTVECT0 and SPIINTVECT1 registers to find out the interrupt status first and then only read the

SPIFLG register to decode the source of the error interrupts.

Advisory 1.1.4 SPI: RXINTFLG Bit in SPIFLG Register May Not Get Cleared

Revision(s) Affected: 1.1

Details: The RXINTFLG bit in the SPIFLG register may not get cleared by reading the SPIBUF

register when the read coincides with the setting of the RXINTFLG bit due to new data

arrival.

Workaround: When the above condition occurs, the system is at the verge of receive overrun.

Therefore, either optimize the SPIBUF servicing routine to avoid receive overrun or use

the EDMA3 to avoid the race condition from occurring.

Advisory 1.1.5 SPI: A Write to SPIFLG Receiver Overrun Bit Does Not Clear the Flag

Revision(s) Affected: 1.1

Details: A write to the SPIFLG receiver overrun (SPIFLG.OVRNINTFLG) bit does not clear the

flag if the write coincides with the setting of the receive interrupt flag

(SPIFLG.RXINTFLG).

Workaround: Write to the SPIFLG.OVRNINTFLG bit, then read back the value of the flag. If the flag

did not clear, then write to clear the flag again.

www.ti.com Advisory 1.1.6 — SPI: SPIINTVECT and SPIFLG Registers are Cleared When Read in Debug Mode

Advisory 1.1.6 SPI: SPIINTVECT and SPIFLG Registers are Cleared When Read in Debug Mode

Revision(s) Affected 1.1

**Details** Both the INTVECT and SPIFLG registers are cleared when refreshing the memory

window in debug mode with CCS. These registers should be cleared only by regular

CPU reads, not during debug/suspend mode.

Workaround(s) None

Advisory 1.1.7 SPI: SPI Master Receives Extra Bit When SPICLK Polarity Changes

Revision(s) Affected 1.1

for the new buffer, then it will be considered as a real SPICLK edge and the receive shift

register shifts the data.

Workaround(s) Pre-select the SPIFMTx register by byte writing to just the DFSEL field in the SPIDAT1

register before actually writing to the SPIDAT1 field of the SPIDAT1 register. This additional step needs to be done only when there is going to be an SPICLK polarity

change for the new buffer.

#### Advisory 1.1.8 SPI Master Mode: Extra Step Required to Use CSHOLD

#### Revision(s) Affected

1.1

#### **Details**

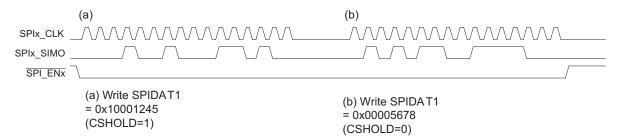

The SPI module chip-select hold (CSHOLD) feature allows the device to instruct the SPI to keep the chip-select pin asserted between transfers. This feature applies in master mode and is enabled by writing a '1' to SPIDAT1.CSHOLD (bit 28).

When data is written to the SPIDAT1 register with the CSHOLD bit set to '1', the master is supposed to keep the SPI\_ENx pin asserted after the transfer completes. When data is written to the SPIDAT1 register with CSHOLD set to '0', the master is supposed to de-assert the SPI\_ENx pin after the transfer completes.

For example, assume that the device needs to send two 16-bit words (0x1234 and 0x5678) to an SPI slave that requires its chip select to remain asserted between the transfers. This is a common requirement when communicating with SPI memory devices.

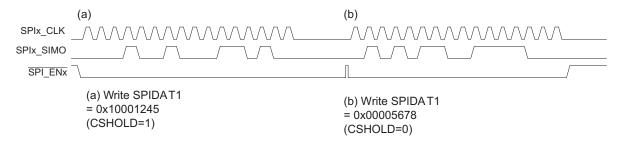

According to the SPI specification, the following sequence should produce the expected result as illustrated in Figure 2:

- Write 0x10001234 to SPIDAT1 for transmission of 0X1234 (CSHOLD = 1)

- Write 0x00005678 to SPIDAT1 for transmission of 0x5678 (CSHOLD = 0)

Figure 2. Expected CSHOLD Behavior

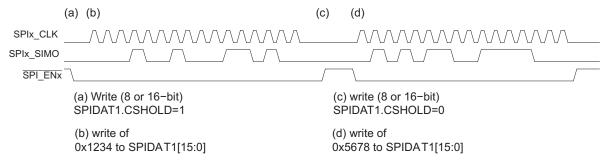

Instead, what actually occurs is that SPI\_ENx is momentarily de-asserted at the beginning of the second write, as illustrated in Figure 3.

Figure 3. Actual CSHOLD Behavior-32-Bit Writes to SPIDAT1

Both Figure 2 and Figure 3 assume that SPIDAT1 is written using a single 32-bit write instruction. If SPIDAT1 is instead written using an 8-bit or 16-bit instruction to write to the CSHOLD field, followed by a 16-bit write to the transmit shift register field of SPIDAT1, then what actually occurs is illustrated in Figure 4. This is the same case illustrated in Figure 3 except that the de-assertion of SPI\_ENx lasts for the duration between writing a '0' to the CSHOLD field and writing new data to the transmit shift register.

Figure 4. Actual CSHOLD Behavior-Halfword Writes to SPIDAT1

#### Workaround(s)

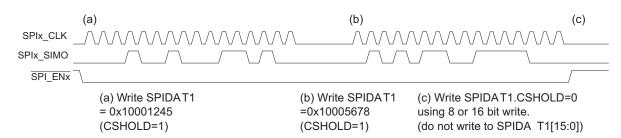

For each word in the sequence of words during which SPI\_ENx should be held low, write to the SPIDAT1 register with the CSHOLD bit set to '1'. Follow this by a write to only the CSHOLD field of SPIDAT1, setting CSHOLD = 0 to de-assert SPI\_ENx. See Figure 5 for an illustration.

Figure 5. Workaround Assuming 32-Bit Writes to SPIDAT1 Followed by a Write Only to CSHOLD

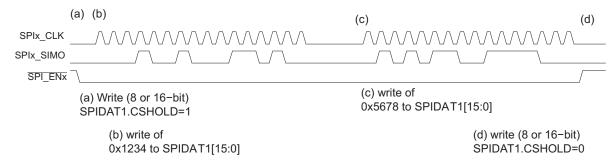

Alternative<u>ly, only write</u> to the SPIDAT1 CSHOLD field before and after the transfer to toggle the SPI\_ENx pin. During the transfer, write only to the data field of SPIDAT1[15:0] using 16-bit (halfword) write commands. For an illustration, see Figure 6.

Figure 6. Workaround Assuming Halfword Writes to SPIDAT1

### Advisory 1.1.9 USB: Some Electrical Parameters Violate USB Specification

Revision(s) Affected

1.1

Details

Some electrical characteristics violate the USB 2.0 specification; see Table 5.

**Table 5. USB Electrical Characteristics in Violation**

|                    |                                                                                        | USB SPEC | IFICATION |      | 335<br>CATION | UNIT |

|--------------------|----------------------------------------------------------------------------------------|----------|-----------|------|---------------|------|

|                    |                                                                                        | MIN      | MAX       | MIN  | MAX           |      |

| V <sub>HSDSC</sub> | USB high-speed<br>disconnect detection<br>threshold (differential<br>signal amplitude) | 525      | 625       | 525  | 675           | mV   |

| V <sub>BUS</sub>   | USB external charge pump input                                                         | 4.75     | 5.25      | 4.85 | 5.25          | V    |

Workaround(s)

Consider these violations and design your system accordingly.

| Advisory 1.1.10      | VPBE: VENC Default Luma Interpolation Filter Does Not Clip to Zero                                                                                                                                                 |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | 1.1                                                                                                                                                                                                                |

| Details              | The Video Encoder (VENC) in the VPBE subsystem includes an optional 2x interpolation function for the luma signal. The default filter used for this interpolation (VMISC.YUPF = 0) does not clip the Luma to zero. |

| Workaround(s)        | Do not use the default luma 2x interpolation filter (VMISC.YUPF = 0). Instead, use the alternate luma 2x interpolation filter (VMISC.YUPF = 1).                                                                    |

#### Advisory 1.1.11 RBL Code ECC Limitation

#### Revision(s) Affected

1.1

#### **Details**

During NAND boot, the ROM Bootloader (RBL) does not implement error correction and detection (ECC). In particular, during NAND boot, the RBL will neither detect nor correct bit errors while loading the user boot loader (UBL).

Once the UBL is loaded, the UBL can implement error correction and detection. For more information on the NAND boot process, see the "NAND Boot Mode" section in the *TMS320DM335 Digital Media System-on-Chip ARM Subsystem Reference Guide* (literature number SPRUFX7).

This is a limitation in the RBL. This is *not* a limitation in the ECC hardware that is a feature of the Asynchronous EMIF(AEMIF) peripheral. Therefore any software outside of the RBL, such as the UBL and NAND driver, can use the ECC hardware to implement NAND error correction and detection.

#### Workaround(s)

The impact of this problem is limited by the incidence of read errors of the NAND device. In very rare situations, a bit error could occur in the UBL transfer. The impact can be limited by choosing a NAND device with lower incidence of read errors. SLC NAND is recommended. SLC NAND typically has a lower incidence of read errors compared to MLC NAND. The impact can also be limited by minimizing the size of the UBL. **Note**: the maximum UBL size is 30Kbytes.

This limitation has no impact on any of the other boot modes: MMC/SD boot mode, AEMIF/OneNAND boot mode, UART boot mode. This limitation also has no impact on managed NAND devices.

#### Advisory 1.1.12

#### USB (Device Mode): Calculated CRC Value Does Not Match Host CRC Value

Revision(s) Affected:

1.1

**Details:**

The USB Controller can occasionally calculate a bad CRC for a received data packet. This error is rare and only occurs when **ALL** of the following conditions are met:

- · USB Controller is in Device Mode of Operation and is receiving data

- Received data packet has a good CRC value of 0x7FF2

- A timing violation caused by a synchronization error (race condition)

The timing synchronization error is caused by a race condition between two control signals in the PHY Clock and System Clock domains. When these two synchronized control signals are crossing a clock boundary and the received data packet has a good CRC value of 0x7FF2, a race condition may occur causing one of the control signals to be latched a few pico-seconds ahead of the other control signal.

The issue has been observed on both Bulk (Non-Isochronous) and Isochronous transfers and may potentially exist on Control and Interrupt transfers since the data paths for all these transfers are the same or are very similar.

When the problem occurs in Non-Isochronous transfer types, the data that was "in-flight" to the USB Controller's FIFO from the Host is discarded by the USB Controller. Due to the error condition, the USB Controller also refrains from sending an ACK packet to the Host, as mandated by the USB transfer protocol. This forces the Host to re-transmit the data packet, anticipating an error in data transmission. The problem is usually corrected when the Host re-transmits the data packet.

When this problem occurs in Isochronous transfer mode for either High- or Full-speed, the USB Controller flags the device application S/W that a CRC error existed but retains the received data within the FIFO as well as captures the received data packet size value minus one byte from the actual data size. Since the magnitude of the actual timing violated due to the synchronization problem is only in pico-seconds, the entire data sent from the Host is routed into the USB device receive FIFO (i.e., even though the received data counter is one byte less, the full data packet is available for the USB driver).

Workaround(s):

Case 1a: Non-Isochronous Transfers (High-Speed): For non-Isochronous transfers operating in High-Speed mode, the Host and Device H/W perform the necessary re-transmission; thererfore, the issue should be transparent to the Host driver. The issue will also be transparent to the USB device driver since the H/W flushes the received data and forces the Host driver to re-transmit by not sending an ACK packet. For this reason, no interrupt is generated by the H/W to signify an error condition to the device-side application S/W.

Although quite rare, when both the Host and Device are operating in High-Speed mode and all the three consecutive transmissions did not occur without an error, the Host will use a PING packet at a later time to check if the endpoint is ready for accepting data. Upon the Host receiving an ACK packet in response to the PING packet, the Host re-initiates the previously failed transmission again. This process continues until the transfer takes place without error. For this reason, the Non-Isochronous High-Speed transfer is immune to this issue except for a throughput reduction for the time it takes for the re-transmission.

Case 1b: Non-Isochronous Transfers (Full-Speed): For non-Isochronous transfers operating in Full-Speed mode, it is recommended that the Host driver be constructed in such a way that it invokes the transfer multiple times prior to forcing a reset to the USB device. When the transfer is repeated, it is expected for the transfer to complete "error-free".

If the Host driver is not "set up" to invoke multiple failed transfers then, the Host driver will reset the USB driver, re-enumerate, and continue from where it left off.

Case 2: Isochronous Transfers (High- and Full-Speed): For Isochronous Transfers operating in either High- or Full-Speed modes, upon receiving a CRC error, the USB controller flags the device application S/W that a CRC error existed but will retain the received data within the FIFO as well as capture the received data packet size value minus one byte from the actual data packet size. Since the magnitude of the actual timing violated due to the synchronization problem is only in pico-seconds, the entire data sent from the Host is routed into the USB device receive FIFO (i.e., even though the received data counter is one byte less, the full data packet is available for the USB driver) and the USB driver should ignore the received CRC error and read one more additional byte from the receive FIFO. This one-byte counter difference is transparent to the Host H/W and S/W.

Due to the rare occurrence of this issue and its very minimal impact on applications, there are no plans to correct this issue in future silicon revisions.

www.ti.com Revision History

## **Revision History**

This data sheet revision history highlights the technical changes made to the SPRZ287 errata to make it an SPRZ287A revision.

Scope: Added additional advisories.

#### Table 6. Revision History

#### ADDS/CHANGES/DELETES

Section 2.1, Silicon Revision 1.1 Usage Notes

- · Added the following Usage Notes:

- NAND Layout Assumed by RBL for Big Block NAND Does Not Match NAND Manufacturers' Recommendations

- GIO0 Low Setting During Device Boot May Cause Boot to Fail

Table 2, Silicon Revision 1.1 Advisory List

- Added the following Advisories:

- Advisory 1.1.11 RBL Code ECC Limitation

- Advisory 1.1.12 USB (Device Mode): Calculated CRC Value Does Not Match Host CRC Value

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated