# 256K x 16 Static RAM

#### **Features**

- Low Voltage range:

- -2.7V-3.3V

- · Ultra-low active power

- Typical active current: 1.5 mA @ f = 1MHz

Typical active current: 7 mA @ f = f<sub>max</sub>

- · Low standby power

- Easy memory expansion with  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  features

- · Automatic power-down when deselected

- CMOS for optimum speed/power

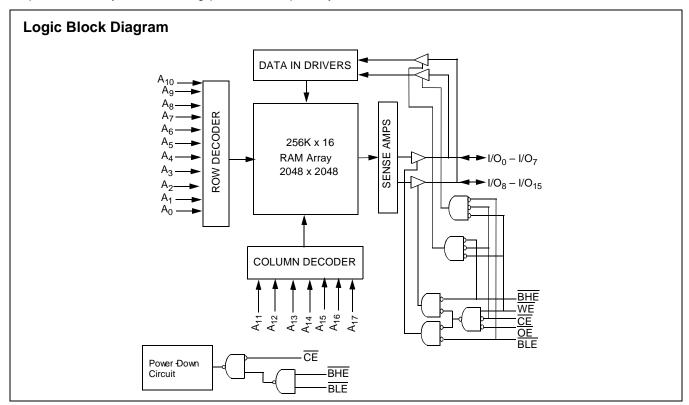

#### **Functional Description**

The WCMA4016U4X is a high-performance CMOS static RAMs organized as 256K words by 16 bits. These devices feature advanced circuit design to provide ultra-low active current. This device is ideal for portable applications such as cellular telephones. The devices also have an automatic power-down feature that significantly reduces power consumption by 80% when addresses are not toggling. The device can also be put into standby mode reducing power consumption by

more than 99% when deselected ( $\overline{\text{CE}}$  HIGH or both  $\overline{\text{BLE}}$  and  $\overline{\text{BHE}}$  are HIGH). The input/output pins (I/O<sub>0</sub> through I/O<sub>15</sub>) are placed in a high-impedance state when: deselected ( $\overline{\text{CE}}$  HIGH), outputs are disabled ( $\overline{\text{OE}}$  HIGH), both Byte High Enable and Byte Low Enable are disabled ( $\overline{\text{BHE}}$ ,  $\overline{\text{BLE}}$  HIGH), or during a write operation ( $\overline{\text{CE}}$  LOW and  $\overline{\text{WE}}$  LOW).

Writing to the device is accomplished by taking Chip Enable  $(\overline{CE})$  and Write Enable (WE) inputs LOW. If Byte Low Enable (BLE) is LOW, then data from I/O pins (I/O $_0$  through I/O $_7$ ), is written into the location specified on the address pins (A $_0$  through A $_{17}$ ). If Byte High Enable (BHE) is LOW, then data from I/O pins (I/O $_8$  through I/O $_{15}$ ) is written into the location specified on the address pins (A $_0$  through A $_{17}$ ).

Reading\_from the device is accomplished by taking Chip Enable ( $\overline{\text{CE}}$ ) and Output Enable ( $\overline{\text{OE}}$ ) LOW while forcing the Write Enable ( $\overline{\text{WE}}$ ) HIGH. If Byte Low Enable ( $\overline{\text{BLE}}$ ) is LOW, then data from the memory location specified by the address pins will appear on I/O $_0$  to I/O $_7$ . If Byte High Enable ( $\overline{\text{BHE}}$ ) is LOW, then data from memory will appear on I/O $_8$  to I/O $_{15}$ . See the truth table at the back of this data sheet for a complete description of read and write modes.

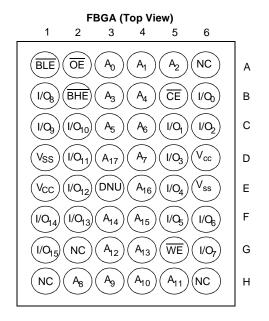

The WCMA4016U4X is available in a 48-ball FBGA package.

# Pin Configuration<sup>[1, 2]</sup>

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.) Storage Temperature ......-65°C to +150°C Ambient Temperature with Power Applied.....-55°C to +125°C

Supply Voltage to Ground Potential...-0.5V to V<sub>ccmax</sub> + 0.5V

DC Voltage Applied to Outputs in High Z State  $^{[3]}$  ......-0.5V to  $\rm V_{CC}$  + 0.3V

DC Input Voltage<sup>[3]</sup>.....-0.5V to V<sub>CC</sub> + 0.3V

| Output Current into Outputs (LOW)                      | 20 mA   |

|--------------------------------------------------------|---------|

| Static Discharge Voltage(per MIL-STD-883, Method 3015) | >2001V  |

| Latch-Up Current                                       | >200 mA |

## **Operating Range**

| Device      | Range      | Ambient<br>Temperature | v <sub>cc</sub> |

|-------------|------------|------------------------|-----------------|

| WCMA4016U4X | Industrial | -40°C to +85°C         | 2.7V to 3.3V    |

#### **Product Portfolio**

|             |                       |                                      |                       |       |                            | Po   | wer Dis             | sipation | (Industr                    | ial)         |

|-------------|-----------------------|--------------------------------------|-----------------------|-------|----------------------------|------|---------------------|----------|-----------------------------|--------------|

| Product     | V <sub>CC</sub> Range |                                      |                       | Speed | Operating, I <sub>CC</sub> |      |                     |          | Standby (I <sub>SB2</sub> ) |              |

| Froduct     | Product               |                                      | Эре                   | Speeu | f = 1                      | MHz  | f = 1               | max      | Sia                         | iluby (ISB2) |

|             | V <sub>CC(min.)</sub> | V <sub>CC(typ.)</sub> <sup>[4]</sup> | V <sub>CC(max.)</sub> |       | Typ. <sup>[4]</sup>        | Max. | Typ. <sup>[4]</sup> | Max.     | <b>Typ.</b> <sup>[4]</sup>  | Max.         |

| WCMA4016U4X | 2.7V                  | 3.0V                                 | 3.3V                  | 70 ns | 1.5 mA                     | 3 mA | 7 mA                | 15 mA    | 7 μΑ                        | 15 μΑ        |

#### Notes:

- NC pins are not connected to the die.

E3 (DNU) can be left as NC or Vss to ensure proper application.

V<sub>IL(min.)</sub> = -2.0V for pulse durations less than 20 ns.

Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at V<sub>CC</sub> = V<sub>CC(typ.)</sub>, T<sub>A</sub> = 25°C.

|                  |                                                      |                                                                                                                                                                                                              |                                             | V    | /CMA4016U           | 4X                     |      |

|------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------|---------------------|------------------------|------|

| Param-<br>eter   | Description                                          | Test Con                                                                                                                                                                                                     | ditions                                     | Min. | Typ. <sup>[4]</sup> | Max.                   | Unit |

| V <sub>OH</sub>  | Output HIGH Voltage                                  | $I_{OH} = -1.0 \text{ mA}$                                                                                                                                                                                   | $V_{CC} = 2.7V$                             | 2.4  |                     |                        | V    |

| V <sub>OL</sub>  | Output LOW Voltage                                   | I <sub>OL</sub> = 2.1mA                                                                                                                                                                                      | V <sub>CC</sub> = 2.7V                      |      |                     | 0.4                    | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                                   |                                                                                                                                                                                                              |                                             | 2.2  |                     | V <sub>CC</sub> + 0.3V | V    |

| V <sub>IL</sub>  | Input LOW Voltage                                    |                                                                                                                                                                                                              |                                             | -0.3 |                     | 0.8                    | V    |

| I <sub>IX</sub>  | Input Leakage Cur-<br>rent                           | $GND \leq V_I \leq V_{CC}$                                                                                                                                                                                   |                                             | -1   |                     | +1                     | μΑ   |

| I <sub>OZ</sub>  | Output Leakage Cur-<br>rent                          | GND ≤ V <sub>O</sub> ≤ V <sub>CC</sub> , Ou                                                                                                                                                                  | $GND \leq V_O \leq V_CC,  Output  Disabled$ |      |                     | +1                     | μΑ   |

|                  | V <sub>CC</sub> Operating Supply                     | $f = f_{MAX} = 1/t_{RC}$                                                                                                                                                                                     | $V_{CC} = 3.3V$                             |      | 7                   | 15                     |      |

| I <sub>CC</sub>  | Current                                              | f = 1 MHz                                                                                                                                                                                                    | I <sub>OUT</sub> = 0 mA<br>CMOS Levels      |      | 1.5                 | 3                      | mA   |

| I <sub>SB1</sub> | Automatic CE<br>Power-Down Cur-<br>rent— CMOS Inputs | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.2\text{V}$ $\text{V}_{\text{IN}} \ge \text{V}_{\text{CC}} - 0.2\text{V}$ or $\text{V}_{\text{f}} = \text{f}_{\text{max}}$ (Address and f=0 (OE,WE,BHE and |                                             | 7    | 15                  | μА                     |      |

| I <sub>SB2</sub> | Automatic CE<br>Power-Down Cur-<br>rent— CMOS Inputs | $\overline{CE} \ge V_{CC} - 0.2V$<br>$V_{IN} \ge V_{CC} - 0.2V$ or $V_{IN} \ge V_{CC} - 0.2V$                                                                                                                | V <sub>IN</sub> ≤ 0.2V,                     |      |                     |                        |      |

# Capacitance<sup>[5]</sup>

| Parameter Description |                    | Test Conditions                         | Max. | Unit |

|-----------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>       | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 6    | pF   |

| C <sub>OUT</sub>      | Output Capacitance | $V_{CC} = V_{CC(typ.)}$                 | 8    | pF   |

# **Thermal Resistance**

| Description                                             | Test Conditions                                                           | Symbol            | BGA | Units |

|---------------------------------------------------------|---------------------------------------------------------------------------|-------------------|-----|-------|

| Thermal Resistance (Junction to Ambient) <sup>[5]</sup> | Still Air, soldered on a 4.25 x 1.125 inch, 4-layer printed circuit board | $\Theta_{JA}$     | 55  | °C/W  |

| Thermal Resistance (Junction to Case) <sup>[5]</sup>    |                                                                           | $\Theta_{\sf JC}$ | 16  | °C/W  |

#### Note

5. Tested initially and after any design or process changes that may affect these parameters.

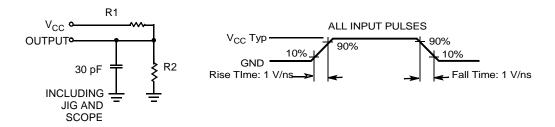

#### **AC Test Loads and Waveforms**

THÉVENIN EQUIVALENT Equivalent to:

| Parameters      | 3.0V  | Unit  |

|-----------------|-------|-------|

| R1              | 1.105 | KOhms |

| R2              | 1.550 | KOhms |

| R <sub>TH</sub> | 0.645 | KOhms |

| V <sub>TH</sub> | 1.75V | Volts |

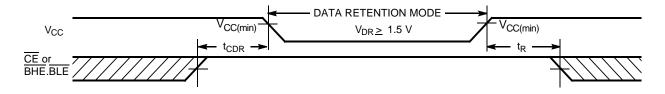

## Data Retention Characteristics (Over the Operating Range)

| Parameter                       | Description                             | Conditions                                                                                     | Min.            | Typ. <sup>[4]</sup> | Max.               | Unit |

|---------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------|-----------------|---------------------|--------------------|------|

| $V_{DR}$                        | V <sub>CC</sub> for Data Retention      |                                                                                                | 1.5             |                     | V <sub>ccmax</sub> | V    |

| I <sub>CCDR</sub>               | Data Retention Current                  | $V_{CC} = 1.5V$<br>$CE \ge V_{CC} - 0.2V$ ,<br>$V_{IN} \ge V_{CC} - 0.2V$ or $V_{IN} \le 0.2V$ |                 | 3                   | 10                 | μΑ   |

| t <sub>CDR</sub> <sup>[5]</sup> | Chip Deselect to Data<br>Retention Time |                                                                                                | 0               |                     |                    | ns   |

| t <sub>R</sub> <sup>[6]</sup>   | Operation Recovery Time                 |                                                                                                | t <sub>RC</sub> |                     |                    | ns   |

# Data Retention Waveform<sup>[7]</sup>

#### Note:

- 6. Full Device AC operation requires linear V<sub>CC</sub> ramp from V<sub>DR</sub> to V<sub>CC(min.)</sub> > 100μs or stable at V<sub>CC(min.)</sub> > 100 μs.

7. BHE.BLE is the AND of both BHE and BLE. Chip can be deselected by either disabling the chip enable signals or by disabling both BHE and BLE.

## Switching Characteristics Over the Operating Range<sup>[8]</sup>

|                                   |                                             | 70      | ns |      |  |

|-----------------------------------|---------------------------------------------|---------|----|------|--|

| Parameter                         | Description                                 | Min Max |    | Unit |  |

| READ CYCLE                        |                                             |         | 1  |      |  |

| t <sub>RC</sub>                   | Read Cycle Time                             | 70      |    | ns   |  |

| t <sub>AA</sub>                   | Address to Data Valid                       |         | 70 | ns   |  |

| t <sub>OHA</sub>                  | Data Hold from Address Change               | 10      |    | ns   |  |

| t <sub>ACE</sub>                  | CE LOW to Data Valid                        |         | 70 | ns   |  |

| t <sub>DOE</sub>                  | OE LOW to Data Valid                        |         | 35 | ns   |  |

| t <sub>LZOE</sub>                 | OE LOW to Low Z <sup>[9]</sup>              | 5       |    | ns   |  |

| t <sub>HZOE</sub>                 | OE HIGH to High Z <sup>[9, 11]</sup>        |         | 25 | ns   |  |

| t <sub>LZCE</sub>                 | CE LOW to Low Z <sup>[9]</sup>              | 10      |    | ns   |  |

| t <sub>HZCE</sub>                 | CE HIGH to High Z <sup>[9, 11]</sup>        |         | 25 | ns   |  |

| t <sub>PU</sub>                   |                                             | 0       |    | ns   |  |

| t <sub>PD</sub>                   |                                             |         | 70 | ns   |  |

| t <sub>DBE</sub>                  | BHE / BLE LOW to Data Valid                 |         | 70 | ns   |  |

| t <sub>LZBE</sub> <sup>[10]</sup> | BHE / BLE LOW to Low Z <sup>[9]</sup>       | 5       |    | ns   |  |

| t <sub>HZBE</sub>                 | BHE / BLE HIGH to High Z <sup>[9, 11]</sup> |         | 25 | ns   |  |

| WRITE CYCLE <sup>[12]</sup>       |                                             |         | •  |      |  |

| t <sub>WC</sub>                   | Write Cycle Time                            | 70      |    | ns   |  |

| t <sub>SCE</sub>                  | CE LOW to Write End                         | 60      |    | ns   |  |

| t <sub>AW</sub>                   | Address Set-Up to Write End                 | 60      |    | ns   |  |

| t <sub>HA</sub>                   | Address Hold from Write End                 | 0       |    | ns   |  |

| t <sub>SA</sub>                   | Address Set-Up to Write Start               | 0       |    | ns   |  |

| t <sub>PWE</sub>                  | WE Pulse Width                              | 50      |    | ns   |  |

| t <sub>BW</sub>                   | BHE / BLE Pulse Width                       | 60      |    | ns   |  |

| t <sub>SD</sub>                   | Data Set-Up to Write End                    | 30      |    | ns   |  |

| t <sub>HD</sub>                   | Data Hold from Write End                    | 0       |    | ns   |  |

| t <sub>HZWE</sub>                 | WE LOW to High Z <sup>[9, 11]</sup>         |         | 25 | ns   |  |

| t <sub>LZWE</sub>                 | WE HIGH to Low Z <sup>[9]</sup>             | 5       |    | ns   |  |

#### Notes:

- 8. Test conditions assume signal transition time of 5 ns or less, timing reference levels of  $V_{CC(typ.)}/2$ , input pulse levels of 0 to  $V_{CC(typ.)}$ , and output loading of the specified  $I_{OL}/I_{OH}$  and 30 pF load capacitance. At any given temperature and voltage condition,  $t_{HZCE}$  is less than  $t_{LZCE}$ ,  $t_{HZBE}$  is less than  $t_{LZDE}$ , and  $t_{HZOE}$ , and  $t_{HZWE}$  is less than  $t_{LZOE}$ .

- At any given temperature and voltage condition, t<sub>HZCE</sub> is less than t<sub>LZCE</sub>, t<sub>HZBE</sub> is less than t<sub>LZDE</sub>, t<sub>HZOE</sub> is less than t<sub>LZOE</sub>, and t<sub>HZWE</sub> is less than t<sub>LZDE</sub>, t<sub>HZOE</sub> is less than t<sub>LZDE</sub>, and t<sub>HZWE</sub> is less than t<sub>LZDE</sub>, that t<sub>LZDE</sub> is less than t<sub>LZDE</sub>, and t<sub>HZWE</sub> is less than t<sub>LZDE</sub>, t<sub>HZDE</sub> is less than t<sub>LZDE</sub>, and t<sub>HZWE</sub> is less than t<sub>LZDE</sub>, t<sub>HZDE</sub>, and t<sub>HZWE</sub> is less than t<sub>LZDE</sub>, that t<sub>HZDE</sub>, and t<sub>HZWE</sub> is less than t<sub>LZDE</sub>, that t<sub>HZDE</sub> is less than t<sub>LZDE</sub>, that t<sub>HZDE</sub> is less than t<sub>LZDE</sub>, and t<sub>HZWE</sub> is less than t<sub>LZDE</sub>, and t<sub>HZWE</sub> is less than t<sub>LZDE</sub>, that t<sub>HZDE</sub> is less than t<sub>LZDE</sub>, that t<sub>HZDE</sub> is less than t<sub>LZDE</sub>, that t<sub>LZDE</sub>, and t<sub>HZWE</sub> is less than t<sub>LZDE</sub>, that the t<sub>LZDE</sub>, that t<sub>LZDE</sub>, t

# **Switching Waveforms**

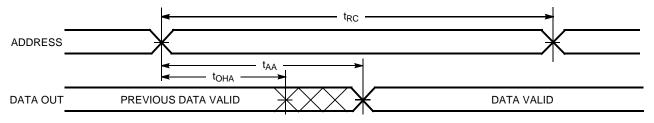

# Read Cycle No. 1 (Address Transition Controlled) [13, 14]

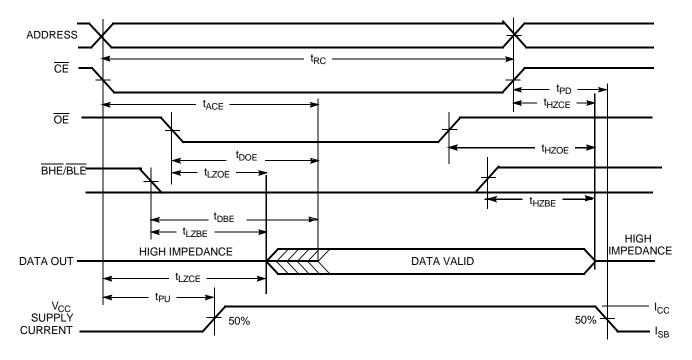

# Read Cycle No. 2 (OE Controlled) [14, 15]

#### Notes:

- Device is continuously selected. OE, CE = V<sub>IL</sub>, BHE and/or BLE = V<sub>IL</sub>.

WE is HIGH for read cycle.

Address valid prior to or coincident with CE, BHE, BLE transition LOW.

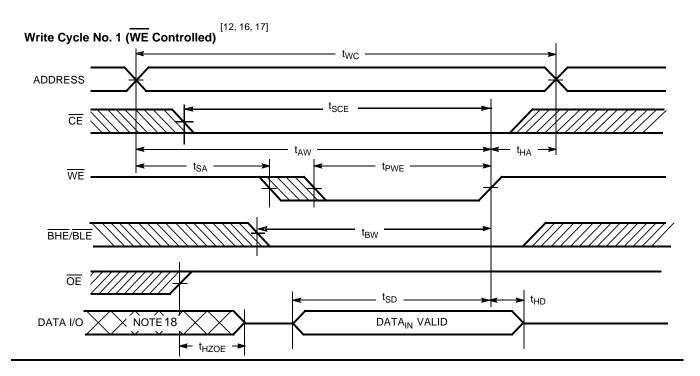

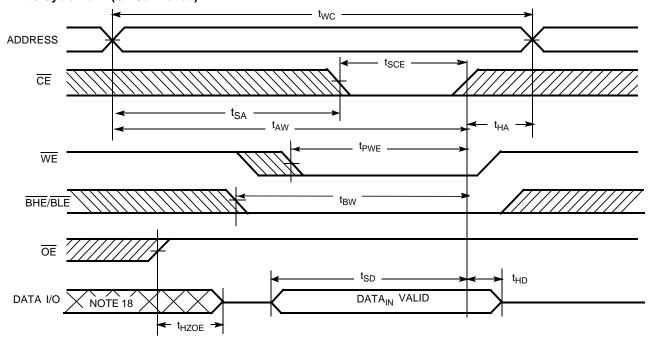

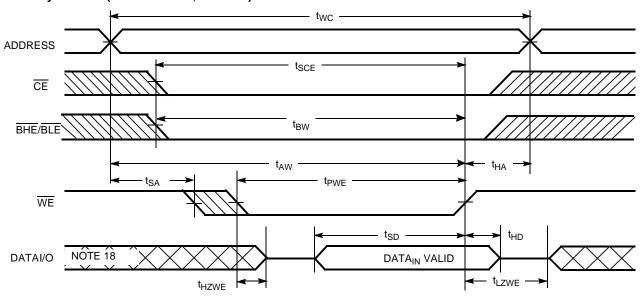

# Switching Waveforms (continued)

- 16. Data I/O is high-impedance if OE = V<sub>IH</sub>.

17. If CE goes HIGH simultaneously with WE HIGH, the output remains in a high-impedance state.

18. During this period, the I/Os are in output state and input signals should not be applied.

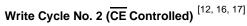

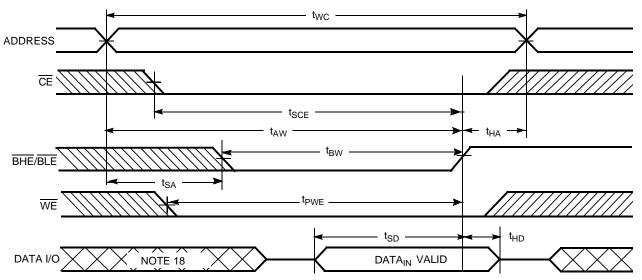

# Switching Waveforms (continued)

# Write Cycle No. 3 (WE Controlled, OE LOW) [17]

# Write Cycle No. 4 (BHE/BLE Controlled, OE LOW) [17]

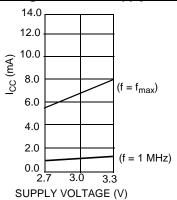

# **Typical DC and AC Parameters**

(Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at  $V_{CC} = V_{CC(typ.)}$ ,  $T_A = 25^{\circ}C.$ )

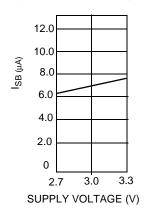

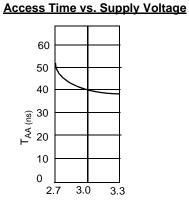

## Operating Current vs. Supply Voltage Standby Current vs. Supply Voltage

SUPPLY VOLTAGE (V)

## **Truth Table**

| CE | WE | OE | BHE | BLE | Inputs/Outputs                                                                                   | Mode                | Power                      |

|----|----|----|-----|-----|--------------------------------------------------------------------------------------------------|---------------------|----------------------------|

| Н  | Х  | Х  | Х   | Х   | High Z                                                                                           | Deselect/Power-Down | Standby (I <sub>SB</sub> ) |

| Х  | Х  | Х  | Н   | Н   | High Z                                                                                           | Deselect/Power-Down | Standby (I <sub>SB</sub> ) |

| L  | Н  | L  | L   | L   | Data Out (I/O <sub>O</sub> -I/O <sub>15</sub> )                                                  | Read                | Active (I <sub>CC</sub> )  |

| L  | Н  | L  | Н   | L   | Data Out (I/O <sub>O</sub> –I/O <sub>7</sub> );<br>I/O <sub>8</sub> –I/O <sub>15</sub> in High Z | Read                | Active (I <sub>CC</sub> )  |

| L  | Н  | L  | L   | Н   | Data Out (I/O <sub>8</sub> -I/O <sub>15</sub> );<br>I/O <sub>0</sub> -I/O <sub>7</sub> in High Z | Read                | Active (I <sub>CC</sub> )  |

| L  | Н  | Н  | L   | L   | High Z                                                                                           | Output Disabled     | Active (I <sub>CC</sub> )  |

| L  | Н  | Н  | Н   | L   | High Z                                                                                           | Output Disabled     | Active (I <sub>CC</sub> )  |

| L  | Н  | Н  | L   | Н   | High Z                                                                                           | Output Disabled     | Active (I <sub>CC</sub> )  |

| L  | L  | Х  | L   | L   | Data In (I/O <sub>O</sub> -I/O <sub>15</sub> )                                                   | Write               | Active (I <sub>CC</sub> )  |

| L  | L  | Х  | Н   | L   | Data In (I/O <sub>O</sub> –I/O <sub>7</sub> );<br>I/O <sub>8</sub> –I/O <sub>15</sub> in High Z  | Write               | Active (I <sub>CC</sub> )  |

| L  | L  | Х  | L   | Н   | Data In (I/O <sub>8</sub> -I/O <sub>15</sub> );<br>I/O <sub>0</sub> -I/O <sub>7</sub> in High Z  | Write               | Active (I <sub>CC</sub> )  |

# **Ordering Information**

| Speed<br>(ns) | Ordering Code    | Package<br>Name | Package Type           | Operating<br>Range |

|---------------|------------------|-----------------|------------------------|--------------------|

| 70            | WCMA4016U4X-FF70 | FB48A           | 48-Ball Fine Pitch BGA | Industrial         |

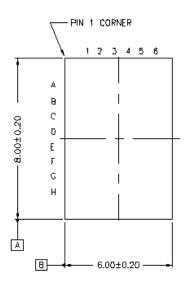

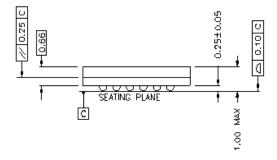

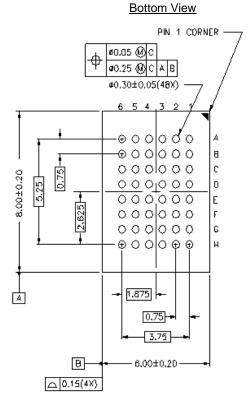

# **Package Diagrams**

# 48-Ball (6.0 mm x 8.0 mm x 1.0 mm) Fine Pitch BGA, FB48A

Top View

| Docur | Document Title: WCMA4016U4X 256K x 16 STATIC RAM |        |            |                 |                       |  |  |  |  |  |

|-------|--------------------------------------------------|--------|------------|-----------------|-----------------------|--|--|--|--|--|

| REV.  | Spec #                                           | ECN#   | Issue Date | Orig. of Change | Description of Change |  |  |  |  |  |

| **    | 38-14013                                         | 115230 | 4/24/2002  | MGN             | New Datasheet         |  |  |  |  |  |