### TrilithlC™

BTS 774 G

### Overview

### Features

- Quad switch driver

- Free configurable as bridge or quad-switch

- Optimized for DC motor management applications

- Ultra low R<sub>DS ON</sub> @ 25 °C: High-side switch: typ.165 mΩ, Low-side switch: typ. 45 mΩ

- Very high peak current capability

- · Very low quiescent current

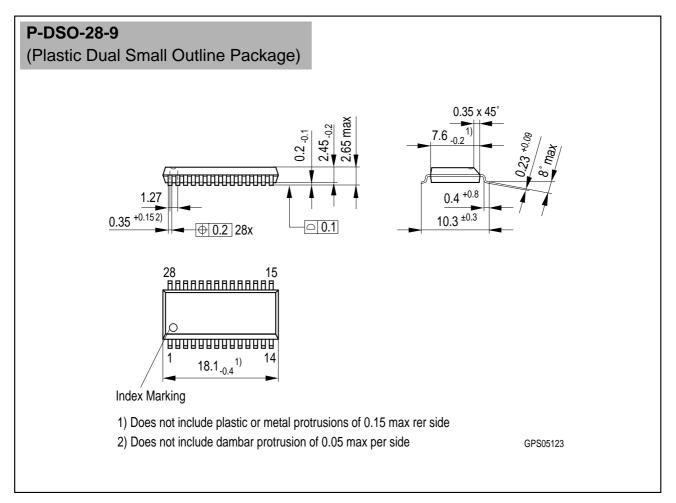

- · Space- and thermal optimized power P-DSO-Package

- Full short-circuit-protection

- Operates up to 40 V

- Status flag diagnosis

- · Overtemperature shut down with hysteresis

- Short-circuit detection and diagnosis

- Open-load detection and diagnosis

- C-MOS compatible inputs

- Internal clamp diodes

- Isolated sources for external current sensing

- · Over- and under-voltage detection with hysteresis

| Туре      | Ordering Code | Package    |

|-----------|---------------|------------|

| BTS 774 G | Q67007-A9336  | P-DSO-28-9 |

### Description

The **BTS 774 G** is a **TrilithIC** contains one double high-side switch and two low-side switches in **one P-DSO-28-9** -Package.

# "Silicon instead of heatsink" becomes true

The ultra low  $R_{\text{DS ON}}$  of this device avoids powerdissipation. It saves costs in mechanical construction and mounting and increases the efficiency.

The high-side switches are produced in the **SIEMENS SMART SIPMOS**<sup>®</sup> technology. It is fully protected and contains the signal conditioning circuitry for diagnosis. (The comparable standard high-side product is the **BTS 611L1**.)

For minimized  $R_{\text{DS ON}}$  the two low-side switches are N channel vertical power FETs in the **SIEMENS SMART SIPMOS**<sup>®</sup> technology. Fully protected by embedded protection functions. (The comparable standard product is the **BSP 78**).

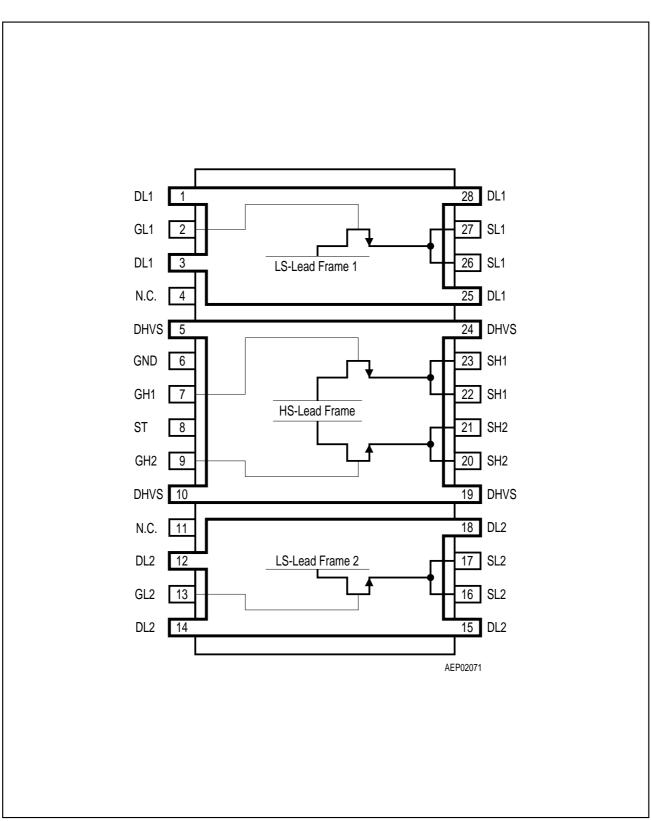

Each drain of these three chips is mounted on separated leadframes (see **P-DSO-28-9** pin configuration). The sources of all four power transistors are connected to separate pins.

So the **BTS 774 G** can be used in H-Bridge configuration as well as in any other switch configuration.

Moreover, it is possible to add current sense resistors.

All these features open a broad range of automotive and industrial applications.

Figure 1 Pin Configuration (top view)

### Pin Definitions and Functions

| Pin No.        | Symbol | Function                                                                       |  |  |  |  |  |  |

|----------------|--------|--------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1, 3, 25, 28   | DL1    | Drain of low-side switch1<br>Leadframe 1 <sup>1)</sup>                         |  |  |  |  |  |  |

| 2              | GL1    | Gate of low-side switch1                                                       |  |  |  |  |  |  |

| 4              | N.C.   | not connected                                                                  |  |  |  |  |  |  |

| 5, 10, 19, 24  | DHVS   | Drain of high-side switches and power supply voltage Leadframe 2 <sup>1)</sup> |  |  |  |  |  |  |

| 6              | GND    | Ground                                                                         |  |  |  |  |  |  |

| 7              | GH1    | Gate of high-side switch1                                                      |  |  |  |  |  |  |

| 8              | ST     | Status of high-side switches; open Drain output                                |  |  |  |  |  |  |

| 9              | GH2    | Gate of high-side switch2                                                      |  |  |  |  |  |  |

| 11             | N.C.   | not connected                                                                  |  |  |  |  |  |  |

| 12, 14, 15, 18 | DL2    | Drain of low-side switch2<br>Leadframe 3 <sup>1)</sup>                         |  |  |  |  |  |  |

| 13             | GL2    | Gate of low-side switch2                                                       |  |  |  |  |  |  |

| 16, 17         | SL2    | Source of low-side switch2                                                     |  |  |  |  |  |  |

| 20, 21         | SH2    | Source of high-side switch2                                                    |  |  |  |  |  |  |

| 22, 23         | SH1    | Source of high-side switch1                                                    |  |  |  |  |  |  |

| 26, 27         | SL1    | Source of low-side switch1                                                     |  |  |  |  |  |  |

<sup>1)</sup> To reduce the thermal resistance these pins are direct connected via metal bridges to the leadframe.

### Bold type: Pin needs power wiring

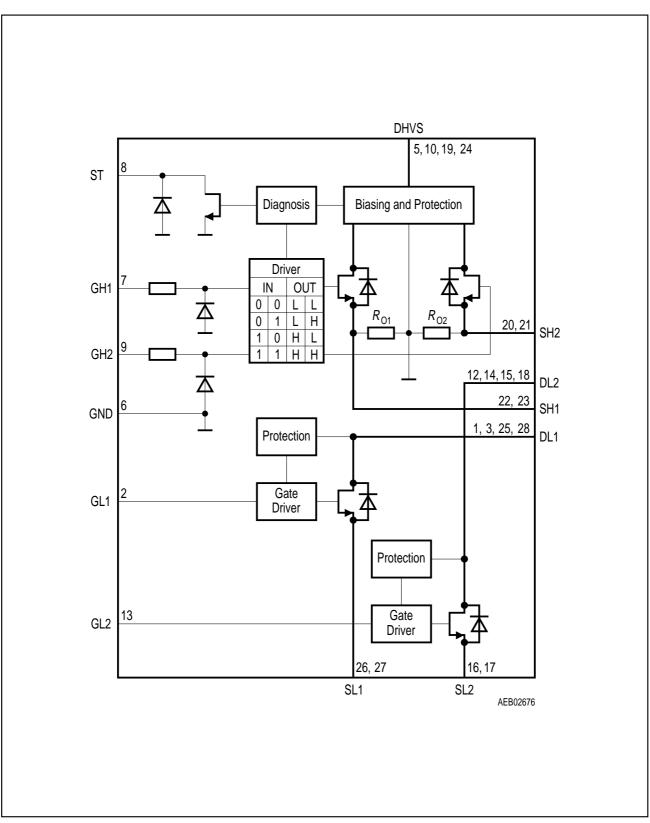

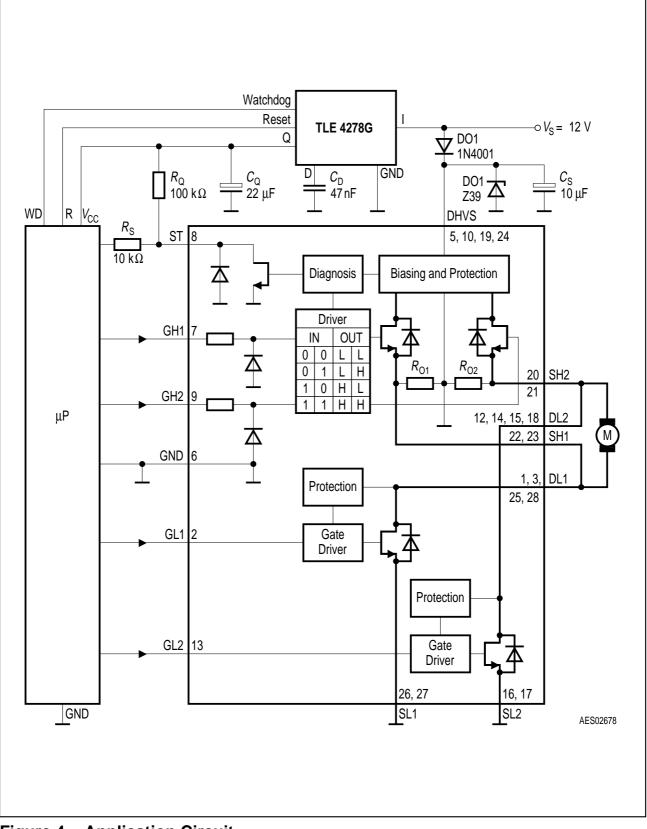

Figure 2 Block Diagram

### **Circuit Description**

### Input Circuit

The control inputs GH1,2 consist of TTL/CMOS compatible Schmitt-Triggers with hysteresis. Buffer amplifiers are driven by these stages and convert the logic signal into the necessary form for driving the power output stages.

The inputs GL1 and GL2 are connected to the internal gate-driving units of the fully protected N-channel vertical power-MOS-FETs.

### **Output Stages**

The output stages consist of an ultra low  $R_{\text{DS ON}}$  Power-MOS H-Bridge. Embedded protective circuits make the outputs short circuit proof to ground, to the supply voltage and load short circuit proof. Positive and negative voltage spikes, which occur when driving inductive loads, are limited by integrated power clamp diodes.

### **Short Circuit Protection**

The outputs are protected against

- output short circuit to ground

- output short circuit to the supply voltage, and

- overload (load short circuit).

An internal OP-Amp controls the Drain-Source-Voltage by comparing the DS-Voltage-Drop with an internal reference voltage. Above this trippoint the OP-Amp reduces the output current depending on the junction temperature and the drop voltage.

In the case of overloaded high-side switches the status output is set to low.

If the HS-Switches are in OFF-state-Condition internal resistors  $R_{O1,2}$  from SH1,2 to GND pull the voltage at SH1,2 to low values. On each output pin SH1 and SH2 an output examiner circuit compares the output voltages with the internal reference voltage VEO. This results in switching the status output to low. The fully protected low-side switches have no status output.

### **Overtemperature Protection**

The highside and the lowside switch also incorporates an overtemperature protection circuit with hysteresis which switches off the output transistors and sets the status output to low.

### Undervoltage-Lockout (UVLO)

When  $V_{\rm S}$  reaches the switch-on voltage  $V_{\rm UVON}$  the IC becomes active with a hysteresis. The High-Side output transistors are switched off if the supply voltage  $V_{\rm S}$  drops below the switch off value  $V_{\rm UVOFF}$ .

### Overvoltage-Lockout (OVLO)

When  $V_{\rm S}$  reaches the switch-off voltage  $V_{\rm OVOFF}$  the High-Side output transistors are switched off with a hysteresis. The IC becomes active if the supply voltage  $V_{\rm S}$  drops below the switch-on value  $V_{\rm OVON}$ .

### **Open Load Detection**

Open load is detected by current measurement. If the output current drops below an internal fixed level the error flag is set with a delay.

### **Status Flag**

Various errors as listed in the table "Diagnosis" are detected by switching the open drain output ST to low.

### Truthtable and Diagnosis (valid only for the High-Side-Switches)

| Flag                                       | GH1    | GH2 | SH1     | SH2 | ST | Remarks              |

|--------------------------------------------|--------|-----|---------|-----|----|----------------------|

|                                            | Inputs |     | Outputs |     |    |                      |

|                                            | 0      | 0   | L       | L   | 1  | stand-by mode        |

| Normal operation;                          | 0      | 1   | L       | Н   | 1  | switch2 active       |

| identical with functional truth table      | 1      | 0   | Н       | L   | 1  | switch1 active       |

|                                            | 1      | 1   | Н       | Н   | 1  | both switches active |

| Open load at high-side switch1             | 0      | 0   | Z       | L   | 1  |                      |

|                                            | 0      | 1   | Z       | Н   | 1  |                      |

|                                            | 1      | X   | Н       | X   | 0  | detected             |

| Open load at high-side switch2             | 0      | 0   | L       | Z   | 1  |                      |

|                                            | 1      | 0   | Н       | Z   | 1  |                      |

|                                            | X      | 1   | X       | H   | 0  | detected             |

| Short circuit to DHVS at high-side switch1 | 0      | 0   | Н       | L   | 0  | detected             |

|                                            | 0      | 1   | Н       | H   | 1  |                      |

|                                            | 1      | X   | Н       | X   | 1  |                      |

| Short circuit to DHVS at high-side switch2 | 0      | 0   | L       | H   | 0  | detected             |

|                                            | 1      | 0   | Н       | H   | 1  |                      |

|                                            | X      | 1   | X       | H   | 1  |                      |

| Overtemperature high-side switch1          | 0      | Х   | L       | X   | 1  |                      |

|                                            | 1      | X   | L       | X   | 0  | detected             |

| Overtemperature high-side switch2          | Х      | 0   | Х       | L   | 1  |                      |

|                                            | X      | 1   | X       | L   | 0  | detected             |

| Overtemperature both high-side switch      | 0      | 0   | L       | L   | 1  |                      |

|                                            | X      | 1   | L       | L   | 0  | detected             |

|                                            | 1      | X   | L       | L   | 0  | detected             |

| Over- and Under-Voltage                    | Х      | X   | L       | L   | 1  | not detected         |

Inputs:

- 0 = Logic LOW

- 1 = Logic HIGH

- X = don't care

- Outputs:

- Z = Output in tristate condition

- L = Output in sink condition

- H = Output in source condition

- X = Voltage level undefined

- Status:

- 1 = No error

- 0 = Error

### **Electrical Characteristics**

#### **Absolute Maximum Ratings**

$-40 \ ^{\circ}\text{C} < T_{i} < 150 \ ^{\circ}\text{C}$

| Parameter | Symbol | Limit Values |      | Unit | Remarks |

|-----------|--------|--------------|------|------|---------|

|           |        | min.         | max. |      |         |

#### High-Side-Switches (Pins DHVS, GH1,2 and SH1,2)

| Supply voltage   | Vs               | - 0.3 | 43 | V  | -                    |

|------------------|------------------|-------|----|----|----------------------|

| HS-drain current | I <sub>DHS</sub> | - 8   | *  | A  | * internally limited |

| HS-input current | I <sub>GH</sub>  | -2    | 2  | mA | Pin GH1 and GH2      |

| HS-input voltage | $V_{GH}$         | - 10  | 16 | V  | Pin GH1 and GH2      |

#### Status Output ST

| Status Output current I <sub>ST</sub> - | - 5 | 5 | mA | Pin ST |

|-----------------------------------------|-----|---|----|--------|

|-----------------------------------------|-----|---|----|--------|

### Low-Side-Switches (Pins DL1,2, GL1,2 and SL1,2)

| Break-down voltage | $V_{(BR)DSS}$    | 40    |    | V | $V_{\rm GS} = 0 \text{ V}; I_{\rm D} <= 1 \text{ mA}$ |

|--------------------|------------------|-------|----|---|-------------------------------------------------------|

| LS-drain current   | I <sub>DLS</sub> | 16    | *  | А | * internally limited                                  |

| LS-input voltage   | $V_{GL}$         | - 0.3 | 10 | V | Pin GL1 and GL2                                       |

#### Temperatures

| Junction temperature | Tj           | - 40 | 150 | °C | - |

|----------------------|--------------|------|-----|----|---|

| Storage temperature  | $T_{ m stg}$ | - 50 | 150 | °C | - |

### Thermal Resistances (one HS-LS-Path active)

| LS-junction case | R <sub>thjCLS</sub> | _ | 20 | K/W | measured to pin3 or 12 |

|------------------|---------------------|---|----|-----|------------------------|

| HS-junction case | $R_{ m thjCHS}$     | _ | 20 | K/W | measured to pin19      |

| Junction ambient | $R_{ m thja}$       | _ | 60 | K/W | -                      |

Note: Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit.

### **Operating Range**

| Parameter               | Symbol           | Limit           | Values | Unit | Remarks                                       |

|-------------------------|------------------|-----------------|--------|------|-----------------------------------------------|

|                         |                  | min.            | max.   |      |                                               |

| Supply voltage          | V <sub>S</sub>   | $V_{\rm UVOFF}$ | 36     | V    | After $V_{\rm S}$ rising above $V_{\rm UVON}$ |

| Input voltages          | $V_{\rm GH}$     | - 0.3           | 15     | V    | -                                             |

| Input voltages          | $V_{\rm GL}$     | - 0.3           | 10     | V    | -                                             |

| Output current          | I <sub>ST</sub>  | 0               | 2      | mA   | -                                             |

| HS-junction temperature | T <sub>jHS</sub> | - 40            | 150    | °C   | -                                             |

| LS-junction temperature | T <sub>jLS</sub> | - 40            | 150    | °C   | -                                             |

Note: In the operating range the functions given in the circuit description are fulfilled.

### **Electrical Characteristics**

$I_{SH1} = I_{SH2} = I_{SL1} = I_{SL2} = 0 \text{ A}; -40 \text{ }^{\circ}\text{C} < T_{j} < 150 \text{ }^{\circ}\text{C}; 8 \text{ V} > V_{S} > 18 \text{ V}$  unless otherwise specified

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

### **Current Consumption**

| Quiescent current | Is | - | 16 | 30  | μA | GH1 = GH2 = L<br>$V_{\rm S}$ = 13.2 V<br>$T_{\rm j}$ = 25 °C |

|-------------------|----|---|----|-----|----|--------------------------------------------------------------|

| Quiescent current | Is | - | -  | 35  | μA | $GH1 = GH2 = L$ $V_{\rm S} = 13.2 \text{ V}$                 |

| Supply current    | Is | _ | 2  | 3.5 | mA | GH1 or GH2 = H                                               |

| Supply current    | Is | _ | 4  | 7   | mA | GH1 and GH2 = H                                              |

### Under Voltage Lockout (UVLO)

| Switch-ON voltage        | $V_{\rm UVON}$  | -   | 5.4 | 7 | V | $V_{\rm S}$ increasing         |

|--------------------------|-----------------|-----|-----|---|---|--------------------------------|

| Switch-OFF voltage       | $V_{\rm UVOFF}$ | 3.5 | 4.2 | - | V | $V_{\rm S}$ decreasing         |

| Switch ON/OFF hysteresis | $V_{\rm UVHY}$  | _   | 1.2 | _ | V | $V_{\rm UVON} - V_{\rm UVOFF}$ |

### Over Voltage Lockout (OVLO)

| Switch-OFF voltage       | $V_{OVOFF}$ | 36 | 37.8 | 43 | V | Vsincreasing                   |

|--------------------------|-------------|----|------|----|---|--------------------------------|

| Switch-ON voltage        | $V_{OVON}$  | 35 | 37.3 | -  | V | $V_{\rm S}$ decreasing         |

| Switch OFF/ON hysteresis | $V_{OVHY}$  | _  | 0.7  | -  | V | $V_{\rm OVOFF} - V_{\rm OVON}$ |

### Short Circuit of Highside Switch to GND

| Initial peak SC current | I <sub>SCP</sub> | 8   | 10  | 13 | А | $T_{\rm j} = -40 ^{\circ}{\rm C}$ |

|-------------------------|------------------|-----|-----|----|---|-----------------------------------|

| Initial peak SC current | I <sub>SCP</sub> | 6.5 | 8.5 | 11 | А | <i>T</i> <sub>j</sub> = 25 °C     |

| Initial peak SC current | I <sub>SCP</sub> | 3.9 | 5   | 7  | A | <i>T</i> <sub>j</sub> = 150 °C    |

### Electrical Characteristics (cont'd)

$I_{SH1} = I_{SH2} = I_{SL1} = I_{SL2} = 0 \text{ A}; -40 \text{ }^{\circ}\text{C} < T_{j} < 150 \text{ }^{\circ}\text{C}; 8 \text{ V} > V_{S} > 18 \text{ V}$  unless otherwise specified

| Parameter | Symbol | Lir  | Limit Values |      | Unit | Test Condition |

|-----------|--------|------|--------------|------|------|----------------|

|           |        | min. | typ.         | max. |      |                |

### Short Circuit of Highside Switch to $V_s$

| OFF-state<br>examiner-voltage | V <sub>EO</sub> | 2 | 3  | 4  | V  | $V_{\rm GH}$ = 0 V |

|-------------------------------|-----------------|---|----|----|----|--------------------|

| Output pull-down-resistor     | R <sub>o</sub>  | 4 | 10 | 30 | kΩ | -                  |

#### **Open Circuit Detection of Highside Switch**

|  | Detection current | I <sub>OCD</sub> | 10 | 90 | 200 | mA | _ |

|--|-------------------|------------------|----|----|-----|----|---|

|--|-------------------|------------------|----|----|-----|----|---|

### **Switching Times of Highside Switch**

| Switch-ON-time; to 90% $V_{\rm SH}$ | t <sub>ON</sub>  | _ | 0.2  | 0.4 | ms | resistive load $I_{SH} = 1 \text{ A}; V_S = 12 \text{ V}$ |

|-------------------------------------|------------------|---|------|-----|----|-----------------------------------------------------------|

| Switch-OFF-time; to 10% $V_{SH}$    | t <sub>OFF</sub> | _ | 0.15 | 0.4 | ms | resistive load $I_{\rm SH}$ = 1 A; $V_{\rm S}$ = 12 V     |

Note: switching times are guaranteed by design

### **Control Inputs of Highside Switches GH 1, 2**

| H-input voltage         | V <sub>GHH</sub> | -   | 2.8 | 3.5 | V  | -                        |

|-------------------------|------------------|-----|-----|-----|----|--------------------------|

| L-input voltage         | $V_{\rm GHL}$    | 1.5 | 2.3 | -   | V  | -                        |

| Input voltage hysterese | $V_{\rm GHHY}$   | -   | 0.5 | -   | V  | -                        |

| H-input current         | I <sub>GHH</sub> | 20  | 60  | 90  | μA | $V_{\rm GH}$ = 5 V       |

| L-input current         | $I_{\rm GHL}$    | 1   | 25  | 50  | μA | $V_{\rm GH}$ = 0.4 V     |

| Input series resistance | $R_{I}$          | 2.5 | 3.5 | 6   | kΩ | -                        |

| Zener limit voltage     | $V_{\rm GHZ}$    | 5.4 | -   | _   | V  | I <sub>GH</sub> = 1.6 mA |

### Electrical Characteristics (cont'd)

$I_{SH1} = I_{SH2} = I_{SL1} = I_{SL2} = 0 \text{ A}; -40 \text{ }^{\circ}\text{C} < T_{j} < 150 \text{ }^{\circ}\text{C}; 8 \text{ V} > V_{S} > 18 \text{ V}$  unless otherwise specified

| Parameter | Symbol | Lir  | nit Valı | les  | Unit | Test Condition |

|-----------|--------|------|----------|------|------|----------------|

|           |        | min. | typ.     | max. |      |                |

### Control Inputs GL1, 2

| Gate-threshold-voltage | $V_{\rm GL(th)}$ | 0.9 | 1.7 | 2.2 | V  | $I_{\rm DL} = 2 \text{ mA}$ |

|------------------------|------------------|-----|-----|-----|----|-----------------------------|

| Input current          | $I_{\rm GLN}$    | -   | 10  | 30  | μA | $V_{\rm GL}$ = 5 V;         |

|                        |                  |     |     |     |    | normal operation            |

| Input current          | $I_{GLF}$        | -   | 150 | 300 | μA | $V_{\rm GL}$ = 5 V;         |

|                        |                  |     |     |     |    | failure mode                |

### Short Circuit of Lowside Switch to $V_s$

| Initial peak SC current | ISCP | 18 | 26 | 34 | А | $T_{\rm j} = -40 ^{\circ}{\rm C}$ |

|-------------------------|------|----|----|----|---|-----------------------------------|

|                         |      | 15 | 21 | 27 | А | <i>T</i> <sub>j</sub> = 25 °C     |

|                         |      | 10 | 14 | 18 | A | <i>T</i> <sub>j</sub> = 150 °C    |

### Switching Times of Lowside Switch

| Switch-ON-time;<br>to 90% V <sub>SL</sub> | t <sub>ON</sub>  | _ | 100 | 200 | μs | resistive load $I_{\rm SH}$ = 1 A; $V_{\rm S}$ = 12 V |

|-------------------------------------------|------------------|---|-----|-----|----|-------------------------------------------------------|

| Switch-OFF-time; to 10% $V_{SL}$          | t <sub>OFF</sub> | _ | 50  | 200 | μs | resistive load $I_{\rm SH}$ = 1 A; $V_{\rm S}$ = 12 V |

Note: Switching times are guaranteed by design.

### Status Flag Output ST of Highside Switch

| Low output voltage  | $V_{\rm STL}$      | _   | 0.2 | 0.6 | V  | <i>I</i> <sub>ST</sub> = 1.6 mA |

|---------------------|--------------------|-----|-----|-----|----|---------------------------------|

| Leakage current     | $I_{\rm STLK}$     | _   | _   | 10  | μA | $V_{\rm ST}$ = 5 V              |

| Zener-limit-voltage | $V_{\mathrm{STZ}}$ | 5.4 | _   | _   | V  | <i>I</i> <sub>ST</sub> = 1.6 mA |

### Electrical Characteristics (cont'd)

$I_{SH1} = I_{SH2} = I_{SL1} = I_{SL2} = 0 \text{ A}; -40 \text{ }^{\circ}\text{C} < T_{j} < 150 \text{ }^{\circ}\text{C}; 8 \text{ V} > V_{S} > 18 \text{ V}$  unless otherwise specified

| Parameter | Symbol | Limit Values |      |      | Unit | <b>Test Condition</b> |

|-----------|--------|--------------|------|------|------|-----------------------|

|           |        | min.         | typ. | max. |      |                       |

#### Thermal Shutdown

| Thermal shutdown junction temperature  | $T_{\rm jSD}$    | 155 | _  | 190 | °C | -                                      |

|----------------------------------------|------------------|-----|----|-----|----|----------------------------------------|

| Thermal switch-on junction temperature | T <sub>jSO</sub> | 150 | _  | 180 | °C | _                                      |

| Temperature hysteresis                 | $\Delta T$       | _   | 10 | _   | °C | $\Delta T = T_{\rm jSD} - T_{\rm jSO}$ |

### Output Stages

| Leakage current<br>of highside switch                      | I <sub>HLK</sub>     | - | -   | 12  | μA | $V_{\rm GH} = V_{\rm SH} = 0 \ { m V}$                                     |

|------------------------------------------------------------|----------------------|---|-----|-----|----|----------------------------------------------------------------------------|

| Leakage current of lowside switch                          | I <sub>lkl</sub>     | - | 1.3 | 10  | μA | $V_{\rm GL}$ = 0 V<br>$V_{\rm DS}$ = 13 V                                  |

| Clamp-diode of highside switch; forward-Voltage            | V <sub>FH</sub>      | - | 0.8 | 1.5 | V  | <i>I</i> <sub>FH</sub> = 3 A                                               |

| Clamp-diode leakage-<br>current of highside switch         | I <sub>lkcl</sub>    | - | -   | 10  | mA | <i>I</i> <sub>FH</sub> = 3 A                                               |

| Clamp-diode of lowside switch; forward-voltage             | V <sub>FL</sub>      | - | 0.8 | 1.2 | V  | <i>I</i> <sub>FL</sub> = 3 A                                               |

| Static drain-source<br>on-resistance<br>of highside switch | R <sub>ds on h</sub> | - | 165 | 220 | mΩ | $I_{\rm SH}$ = 1 A<br>$T_{\rm j}$ = 25 °C                                  |

| Static drain-source<br>on-resistance of lowside<br>switch  | R <sub>ds on L</sub> | - | 45  | 60  | mΩ | $I_{SL} = 1 \text{ A};$<br>$V_{GL} = 5 \text{ V}$<br>$T_j = 25 \text{ °C}$ |

| Static path on-resistance                                  | $R_{\rm DS  ON}$     | - | -   | 500 | mΩ | $R_{\text{DS ON H}} + R_{\text{DS ON L}}$ $I_{\text{SH}} = 1 \text{ A};$   |

Note: The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25^{\circ}C$  and the given supply voltage.

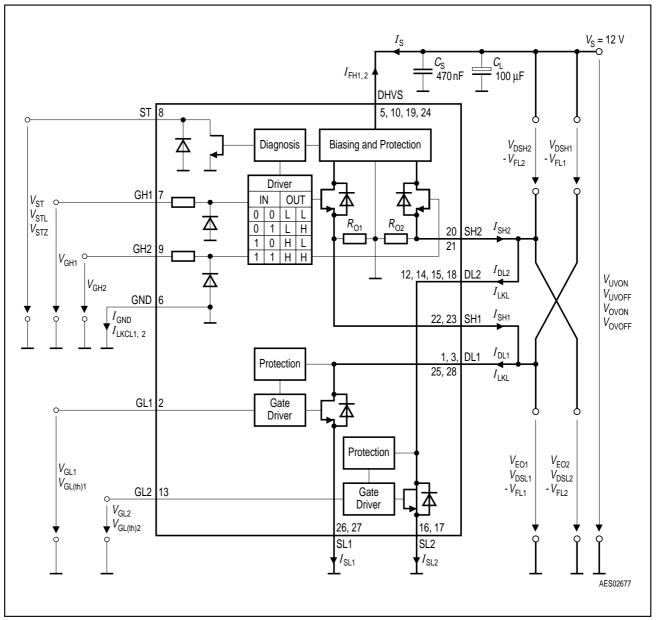

### Figure 3 Test Circuit

| HS-Source-Current         | Named during     | Named during     | Named during      |

|---------------------------|------------------|------------------|-------------------|

|                           | Short Circuit    | Open Circuit     | Leakage-Cond.     |

| <i>I</i> <sub>SH1,2</sub> | I <sub>SCP</sub> | I <sub>OCD</sub> | I <sub>HSLK</sub> |

Figure 4 Application Circuit

### **Package Outlines**

Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book "Package Information". SMD = Surface Mounted Device

Dimensions in mm