# Design Idea DI-101 DPA-Switch<sup>®</sup> Under-Voltage with Wide Hysteresis

| Application | Device  | Power Output | Input Voltage | Output Voltage | Topology |

|-------------|---------|--------------|---------------|----------------|----------|

| PoE/VoIP    | DPA423G | -            | 34-57 VDC     | -              | -        |

## **Design Highlights**

- High hysteresis under-voltage lockout for Power over Ethernet (PoE) Powered Devices (PDs)

- Turn-on threshold of 42 VDC and turn-off threshold of 34 VDC

- Compliance to PoE standard (IEEE 802.3af) over complete voltage window ensures compatibility with PSE equipment. Tested by University of New Hampshire Interoperability Consortium (UNH-IOC)\*

# Wide Hysteresis Under-Voltage

The default under-voltage lockout and overvoltage shutdown thresholds of the *DPA-Switch* are programmed with a single resistor ( $R_{LS}$ ) connected from the positive input voltage to the L-pin. The default overvoltage and under-voltage thresholds have a fixed ratio (ratio approximately 2.7:1).

In a PoE system, the Power Sourcing Equipment (PSE) provides a minimum operating voltage of 44 VDC. However, the PoE specification allows CAT-5 (Ethernet) cable lengths up to 100 meters/ 300 ft (with up to 20  $\Omega$  of cable impedance). At peak operating current (350 mA), the voltage at the PD can drop to approximately

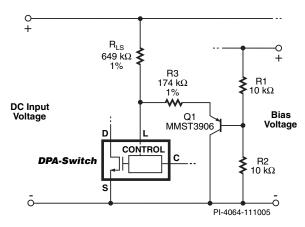

Figure 1. DPA-Switch with Wide Hysteresis UVLO.

37 VDC (350 mA  $\times$  20  $\Omega$ ). A minimum of 7 VDC undervoltage hysteresis is required to accommodate the cable drop voltage and prevent nuisance lockouts from occurring.

# Operation

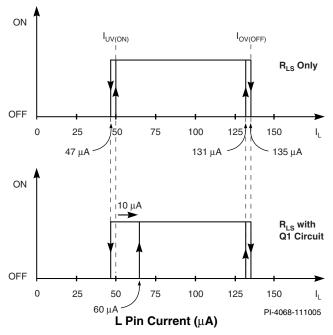

This circuit takes advantage of accurate *DPA-Switch* L-pin current sensing as the basis for a new composite threshold, programmed for 42 VDC turn-on and 34 VDC turn-off. The *DPA-Switch* detects the input voltage via current in the L-pin resistor  $R_{LS}$ . Above an UV-on threshold (50  $\mu$ A), the *DPA-Switch* begins switching and below an UV-off threshold (47  $\mu$ A), the *DPA-Switch* is disabled. Transistor Q1 is turned on via bias resistor R2, causing a voltage drop across R3 and subtracting a fixed current of approximately 10  $\mu$ A (moving the effective threshold to 60  $\mu$ A) from the L-pin. When the power supply becomes operational, the bias voltage pulls up via R1, turning off Q1, cutting off the R3 current and returning to the default UV-off threshold (47  $\mu$ A).

Figure 2. L-Pin Current without/with Wide UVLO Circuit.

\*UNH-IOC test reports are available on the PI website www.powerint.com/poe

## **Design Formulae**

Component values can be calculated according to the following formulae and parameters:

Design parameters were selected as follows:

| $V_{UV_ON} = 42 \text{ VDC}$<br>$V_{UV_OFF} = 34 \text{ VDC}$ | Input under-voltage on-threshold Default under-voltage off- |

|---------------------------------------------------------------|-------------------------------------------------------------|

| 0.1-011                                                       | threshold                                                   |

| $V_{DIN} = 1.4 \text{ VDC}$                                   | Diode drop for PoE reverse                                  |

| Dirt                                                          | protection input diodes                                     |

| $R1 = 10 \text{ k}\Omega$                                     | This value is assumed                                       |

From the DPA-Switch data sheet we have the following:

| $I_{UV_{ON}} = 50 \ \mu A$                             | L-pin current for UV turn on       |

|--------------------------------------------------------|------------------------------------|

| $I_{UV,OFF} = 47 \ \mu A$                              | L-pin current for UV turn off      |

| $I_{UV_OFF} = 47 \ \mu A$<br>V <sub>L</sub> = 2.35 VDC | L-pin voltage at $I_L = I_{UV ON}$ |

| $V_{c}^{2} = 5.8 \text{ VDC}$                          | Control-pin voltage                |

We can assume:

| $V_{Q1(BE)} = 0.6 \text{ VDC}$         | Transistor base-emitter voltage |

|----------------------------------------|---------------------------------|

| $V_{Q1(BE)REV}^{(AL)} < 4 \text{ VDC}$ | 80% of the max reverse base-    |

|                                        | emitter voltage                 |

| $\beta = 100$                          | Transistor minimum current gain |

Bias Voltage ( $V_{BIAS}$ ) = 8 VDC

Resistor values R<sub>1,s</sub>, R2 and R3 are calculated as follows:

$$R_{LS} = \frac{V_{UV\_OFF} - V_L - V_{DIN}}{I_{UV\_OFF}}$$

$$R_3 = \frac{(V_L - V_{Q1(BE)}) \cdot R_{LS}}{V_{UV\_ON} - I_{UV\_ON} \cdot R_{LS} - V_L - V_{DIN}}$$

$$R_2 < \frac{R_1 \cdot \left(V_{Q1(BE)REV} + V_L\right)}{V_{BIAS} - V_L - V_{Q1(BE)REV}}$$

#### For the latest updates, visit www.powerint.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS. The products and applications illustrated herein (transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations' patents may be found at **www.powerint.com**. Power Integrations grants its customers a license under certain patent rights as set forth at http://www.powerint.com/ip.htm.

The PI logo, **TOPSwitch**, **TinySwitch**, **LinkSwitch**, **DPA-Switch**, **EcoSmart**, **Clampless**, **E-Shield**, **Filterfuse**, **PI Expert** and **PI FACTS** are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©Copyright 2005, Power Integrations, Inc.

| Power Integ       | rations 5245         | Hellyer Avenue   | San Jose, California 95138                                                              |

|-------------------|----------------------|------------------|-----------------------------------------------------------------------------------------|

| MAIN PHONE NUMBER | APPLICATIONS HOTLINE | APPLICATIONS FAX | For a complete listing of worldwide sales offices, please visit <b>www.powerint.com</b> |

| +1 408-414-9200   | +1 408-414-9660      | +1 408-414-9760  |                                                                                         |

For design verification:

$$V_{UV\_ON} = \left(I_{UV\_ON} + \frac{V_L - V_{Q1(BE)}}{R_3}\right) \cdot R_{LS} + V_L + V_{DIN}$$

$$V_{UV\_OFF} = I_{UV\_OFF} \cdot R_{LS} + V_L + V_{DIN}$$

$$V_{OV\_OFF} = I_{OV\_OFF} \cdot R_{LS} + V_L + V_{DIN}$$

$$V_{Q1(BE)REV} = \frac{V_{BIAS} \cdot R_2}{R_1 + R_2} - V_L$$

## **Key Design Points**

- Use a 1% resistor for  $R_{LS}$  to maintain the highest accuracy for the turn-on/turn-off thresholds.

- The over-voltage threshold is fixed at  $I_{OV\_OFF} = 135 \ \mu A$ , and can be calculated according to the formula above  $(V_{OV\_OFF})$ .

- The bias voltage ( $V_{BIAS}$ ) is divided by R2 and R1. The reverse base emitter voltage  $V_{QI(BE)REV}$  is the divided bias voltage minus  $V_L$ . Make sure  $V_{QI(BE)REV}$  stays below 5 V (the transistor rating).

- For PoE applications, make sure to include voltage drops of input diodes ( $V_{DIN}$ ) and pass-FET drop when calculating  $R_{LS}$ . For non-PoE applications, assume  $V_{DIN} = 0$ .

- Note: Due to the L-pin synchronization function (with a 1 V threshold), resistor R2 should be sufficiently large to prevent Q1 turn-on below L-pin voltage 1 V.