# CMOS SERIAL E<sup>2</sup>PROM

S-93C86B

The S-93C86B is a high speed, low current consumption, 16 K-bit serial  $E^2PROM$  with a wide operating voltage range. It is organized as 1024-word  $\times$  16-bit, respectively. This product is capable of sequential read, at which time addresses are automatically incremented in 16-bit blocks. The instruction code is compatible with the NM93CS86.

#### ■ Features

• Low current consumption Standby:  $1.5 \mu A$  Max.  $(V_{CC} = 5.5 \text{ V}, \text{ at } -40 \text{ to } +85^{\circ}\text{C})$

Operating: 0.8 mA Max.  $(V_{CC} = 5.5 \text{ V})$

$0.4 \text{ mA Max.} (V_{CC} = 2.5 \text{ V})$

• Wide operating voltage range Read: 1.8 to 5.5 V (at -40 to +85°C)

Write:  $2.7 \text{ to } 5.5 \text{ V (at } -40 \text{ to } +85^{\circ}\text{C)}$

• Sequential read capable

• Write disable function when power supply voltage is low

• Function to protect against write due to erroneous instruction recognition

• Endurance: 10<sup>7</sup> cycles/word<sup>\*1</sup> (at +25°C) write capable,

$10^6$  cycles/word<sup>\*1</sup> (at +85°C)  $3 \times 10^5$  cycles/word<sup>\*1</sup> (at +105°C)

\*1. For each address (Word: 16 bits)

Data retention:

S-93C86B:

10 years (after rewriting 10<sup>6</sup> cycles/word at +85°C)

K-bit NM93CS86 instruction code compatible

• High-temperature operation: +105°C Max. supported

(Only S-93C86BD4H-J8T2G and S-93C86BD4H-T8T2G)

• Write time: 4.0 ms Max.

· Lead-free products

#### ■ Packages

| Package name     |         | Drawing code |         |

|------------------|---------|--------------|---------|

|                  | Package | Tape         | Reel    |

| 8-Pin SOP(JEDEC) | FJ008-A | FJ008-D      | FJ008-D |

| 8-Pin TSSOP      | FT008-A | FT008-E      | FT008-E |

Caution This product is intended to use in general electronic devices such as consumer electronics, office equipment, and communications devices. Before using the product in medical equipment or automobile equipment including car audio, keyless entry and engine control unit, contact to SII is indispensable.

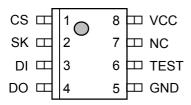

# **■** Pin Configurations

8-Pin SOP(JEDEC) Top view

Figure 1

S-93C86BD4I-J8T1G S-93C86BD4H-J8T2G

Table 1

| Pin No. | Symbol | Description        |

|---------|--------|--------------------|

| 1       | CS     | Chip select input  |

| 2       | SK     | Serial clock input |

| 3       | DI     | Serial data input  |

| 4       | DO     | Serial data output |

| 5       | GND    | Ground             |

| 6       | TEST*1 | Test               |

| 7       | NC     | No connection      |

| 8       | VCC    | Power supply       |

\*1. Connect to GND or  $V_{\text{CC}}$ .

Even if this pin is not connected, performance is not affected so long as the absolute maximum rating is not exceeded.

**Remark** See Dimensions for details of the package drawings.

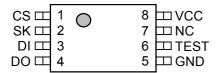

8-Pin TSSOP Top view

Figure 2

S-93C86BD4I-T8T1G S-93C86BD4H-T8T2G

Table 2

| Pin No. | Symbol | Description        |

|---------|--------|--------------------|

| 1       | CS     | Chip select input  |

| 2       | SK     | Serial clock input |

| 3       | DI     | Serial data input  |

| 4       | DO     | Serial data output |

| 5       | GND    | Ground             |

| 6       | TEST*1 | Test               |

| 7       | NC     | No connection      |

| 8       | VCC    | Power supply       |

<sup>\*1.</sup> Connect to GND or  $V_{CC}$ .

Even if this pin is not connected, performance is not affected so long as the absolute maximum rating is not exceeded.

**Remark** See Dimensions for details of the package drawings.

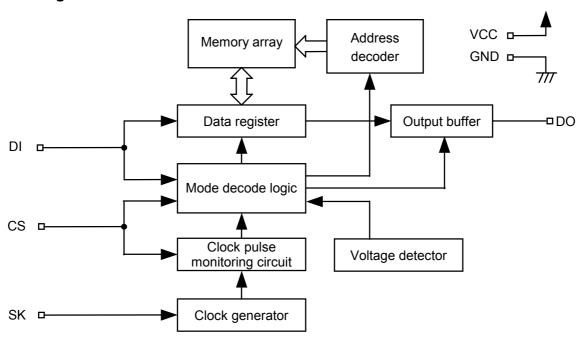

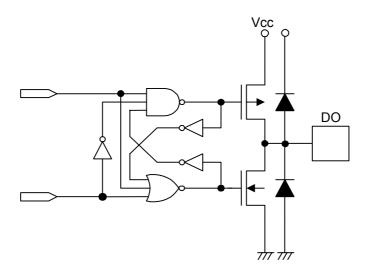

# **■** Block Diagram

Figure 3

# **■ Instruction Sets**

Table 3

| Instruction          | Start Bit | Operation | on Code |    |    |    |    | Add | ress |    |    |    |    | Data               |

|----------------------|-----------|-----------|---------|----|----|----|----|-----|------|----|----|----|----|--------------------|

| SK input clock       | 1         | 2         | 3       | 4  | 5  | 6  | 7  | 8   | 9    | 10 | 11 | 12 | 13 | 14 to 29           |

| READ (Read data)     | 1         | 1         | 0       | A9 | A8 | A7 | A6 | A5  | A4   | А3 | A2 | A1 | A0 | D15 to D0 Output*1 |

| WRITE (Write data)   | 1         | 0         | 1       | A9 | A8 | A7 | A6 | A5  | A4   | А3 | A2 | A1 | Α0 | D15 to D0 Input    |

| ERASE (Erase data)   | 1         | 1         | 1       | Α9 | A8 | A7 | A6 | A5  | A4   | А3 | A2 | A1 | Α0 | _                  |

| WRAL (Write all)     | 1         | 0         | 0       | 0  | 1  | Х  | Х  | Х   | Х    | Х  | Х  | Х  | Χ  | D15 to D0 Input    |

| ERAL (Erase all)     | 1         | 0         | 0       | 1  | 0  | Х  | Х  | Χ   | Х    | Χ  | Х  | Х  | Χ  | _                  |

| EWEN (Write enable)  | 1         | 0         | 0       | 1  | 1  | Х  | Х  | Х   | Х    | Х  | Х  | Х  | Χ  | _                  |

| EWDS (Write disable) | 1         | 0         | 0       | 0  | 0  | Х  | Х  | Х   | Х    | Х  | Х  | Х  | Χ  | _                  |

**<sup>\*1.</sup>** When the 16-bit data in the specified address has been output, the data in the next address is output.

Remark x: Don't care

# ■ Absolute Maximum Ratings

Table 4

| Item                          | Symbol           | Ratings                        | Unit |

|-------------------------------|------------------|--------------------------------|------|

| Power supply voltage          | V <sub>CC</sub>  | −0.3 to +7.0                   | V    |

| Input voltage                 | V <sub>IN</sub>  | -0.3 to V <sub>CC</sub> $+0.3$ | V    |

| Output voltage                | V <sub>OUT</sub> | −0.3 to V <sub>CC</sub>        | V    |

| Operating ambient temperature | T <sub>opr</sub> | -40 to +105                    | °C   |

| Storage temperature           | T <sub>stg</sub> | −65 to +150                    | °C   |

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

# **■** Recommended Operating Conditions

Table 5

| Item                     | Symbol          | Conditions                               | -40                 | ) to +8 | 5°C                  | +85  | to +10 | 5°C      | Unit  |

|--------------------------|-----------------|------------------------------------------|---------------------|---------|----------------------|------|--------|----------|-------|

| item                     | Symbol          | Conditions                               | Min.                | Тур.    | Max.                 | Min. | Тур.   | Max.     | Offic |

|                          |                 | READ/EWDS                                | 1.8                 |         | 5.5                  | 4.5  |        | 5.5      | V     |

| Power supply voltage     | $V_{CC}$        | WRITE/ERASE/<br>WRAL/ERAL/EWEN           | 2.7                 | _       | 5.5                  | 4.5  | _      | 5.5      | ٧     |

|                          |                 | $V_{CC} = 4.5 \text{ to } 5.5 \text{ V}$ | 2.0                 |         | V <sub>CC</sub>      | 2.0  |        | $V_{CC}$ | V     |

| High level input voltage | $V_{\text{IH}}$ | $V_{CC} = 2.7 \text{ to } 4.5 \text{ V}$ | $0.8 \times V_{CC}$ |         | $V_{CC}$             |      |        |          | V     |

|                          |                 | $V_{CC} = 1.8 \text{ to } 2.7 \text{ V}$ | $0.8 \times V_{CC}$ |         | $V_{CC}$             |      |        |          | V     |

|                          |                 | $V_{CC} = 4.5 \text{ to } 5.5 \text{ V}$ | 0.0                 | _       | 0.8                  | 0.0  |        | 0.8      | V     |

| Low level input voltage  | $V_{IL}$        | $V_{CC} = 2.7 \text{ to } 4.5 \text{ V}$ | 0.0                 |         | $0.2 \times V_{CC}$  |      |        |          | V     |

|                          |                 | $V_{CC} = 1.8 \text{ to } 2.7 \text{ V}$ | 0.0                 |         | $0.15 \times V_{CC}$ |      |        |          | V     |

# ■ Pin Capacitance

Table 6

$(Ta = 25^{\circ}C, f = 1.0 \text{ MHz}, V_{CC} = 5.0 \text{ V})$

| Item               | Symbol           | Conditions      | Min. | Тур. | Max. | Unit |

|--------------------|------------------|-----------------|------|------|------|------|

| Input Capacitance  | C <sub>IN</sub>  | $V_{IN} = 0 V$  | _    |      | 8    | pF   |

| Output Capacitance | C <sub>OUT</sub> | $V_{OUT} = 0 V$ | _    | _    | 10   | pF   |

#### **■** Endurance

Table 7

| Item       | Symbol         | Operating<br>Temperature | Min.            | Тур. | Max. | Unit          |

|------------|----------------|--------------------------|-----------------|------|------|---------------|

| Endurance  | N <sub>w</sub> | –40 to +85°C             | 10 <sup>6</sup> |      |      | cycles/word*1 |

| Lituarance | INW            | +85 to +105°C            | $3 \times 10^5$ | _    | _    | Cycles/Word   |

<sup>\*1.</sup> For each address (Word: 16 bits)

# **■ DC Electrical Characteristics**

# Table 8

|                            |                  |            |                   |                                |      | -40  | to +85°                                                            | °C   |      |       |                                            | +85  | to +10 | 5°C  |    |

|----------------------------|------------------|------------|-------------------|--------------------------------|------|------|--------------------------------------------------------------------|------|------|-------|--------------------------------------------|------|--------|------|----|

| Item                       | Symbol           | Conditions | V <sub>CC</sub> = | V <sub>CC</sub> = 4.5 to 5.5 V |      |      | $V_{CC} = 2.5 \text{ to } 4.5 \text{ V}$ $V_{CC} = 1.8 \text{ to}$ |      |      | 2.5 V | $V V_{CC} = 4.5 \text{ to } 5.5 \text{ V}$ |      |        | Unit |    |

|                            |                  |            | Min.              | Тур.                           | Max. | Min. | Тур.                                                               | Max. | Min. | Тур.  | Max.                                       | Min. | Тур.   | Max. |    |

| Current consumption (READ) | I <sub>CC1</sub> | DO no load | _                 |                                | 0.8  |      |                                                                    | 0.5  | _    | _     | 0.4                                        | _    |        | 0.8  | mA |

# Table 9

|                             |                  |                   |      |                                          | –40 to | +85°C |                                          |      | +85  | 5 to +10                                 | 5°C  |    |  |

|-----------------------------|------------------|-------------------|------|------------------------------------------|--------|-------|------------------------------------------|------|------|------------------------------------------|------|----|--|

| Item                        | Symbol           | Symbol Conditions |      | $V_{CC} = 4.5 \text{ to } 5.5 \text{ V}$ |        |       | $V_{CC} = 2.7 \text{ to } 4.5 \text{ V}$ |      |      | $V_{CC} = 4.5 \text{ to } 5.5 \text{ V}$ |      |    |  |

|                             |                  |                   | Min. | Тур.                                     | Max.   | Min.  | Тур.                                     | Max. | Min. | Тур.                                     | Max. |    |  |

| Current consumption (WRITE) | I <sub>CC2</sub> | DO no load        |      |                                          | 2.0    | _     | _                                        | 1.5  |      | _                                        | 2.0  | mA |  |

# Table 10

|                                      |                 |                                                                                                             |                      |         |       | –40 to               | +85°   | C    |                      |         |      | +85 to               | +105    | 5°C   |      |

|--------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------|----------------------|---------|-------|----------------------|--------|------|----------------------|---------|------|----------------------|---------|-------|------|

| Item                                 | Symbol          | Conditions                                                                                                  | $V_{CC} = 4$         | .5 to 5 | 5.5 V | $V_{CC} = 2$ .       | 5 to 4 | .5 V | $V_{CC} = 1$         | .8 to 2 | .5 V | $V_{CC} = 4$         | .5 to 5 | 5.5 V | Unit |

|                                      |                 |                                                                                                             | Min.                 | Тур.    | Max.  | Min.                 | Тур.   | Max. | Min.                 | Тур.    | Max. | Min.                 | Тур.    | Max.  |      |

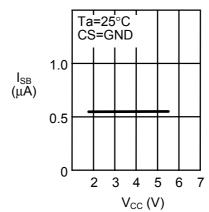

| Standby<br>current<br>consumption    | I <sub>SB</sub> | $\label{eq:cs} \begin{split} &CS = GND, \\ &DO = Open, \\ &Other inputs to V_{CC} \ or \\ &GND \end{split}$ |                      | ı       | 1.5   |                      |        | 1.5  | l                    | _       | 1.5  | l                    |         | 2.0   | μΑ   |

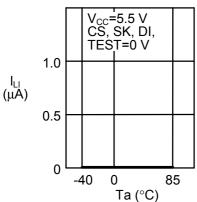

| Input leakage current                | I <sub>LI</sub> | $V_{IN} = GND \text{ to } V_{CC}$                                                                           | I                    | 0.1     | 1.0   | _                    | 0.1    | 1.0  | -                    | 0.1     | 1.0  | -                    | 0.1     | 1.0   | μΑ   |

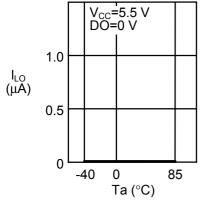

| Output<br>leakage<br>current         | I <sub>LO</sub> | $V_{OUT} = GND \text{ to } V_{CC}$                                                                          | _                    | 0.1     | 1.0   | _                    | 0.1    | 1.0  | _                    | 0.1     | 1.0  | _                    | 0.1     | 1.0   | μΑ   |

| Low level                            | /               | $I_{OL} = 2.1 \text{ mA}$                                                                                   |                      | l       | 0.4   | _                    |        | 1    | _                    | _       |      |                      |         | 0.4   | V    |

| output voltage                       | V <sub>OL</sub> | $I_{OL} = 100 \mu A$                                                                                        | _                    | _       | 0.1   | _                    | _      | 0.1  | _                    | _       | 0.1  | _                    | _       | 0.1   | V    |

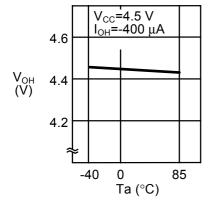

|                                      |                 | $I_{OH} = -400 \mu A$                                                                                       | 2.4                  |         |       |                      |        |      |                      | _       |      | 2.4                  |         | _     | V    |

| High level output voltage            | V <sub>OH</sub> | $I_{OH} = -100 \mu A$                                                                                       | V <sub>CC</sub> -0.3 |         |       | V <sub>CC</sub> -0.3 |        |      |                      | _       |      | V <sub>CC</sub> -0.3 |         | _     | V    |

|                                      |                 | $I_{OH} = -10 \mu A$                                                                                        | V <sub>CC</sub> -0.2 | _       | _     | V <sub>CC</sub> -0.2 | _      |      | V <sub>CC</sub> -0.2 | _       |      | V <sub>CC</sub> -0.2 | _       | _     | V    |

| Write enable latch data hold voltage | $V_{DH}$        | Only when write disable mode                                                                                | 1.5                  | _       |       | 1.5                  |        |      | 1.5                  | _       |      | 1.5                  |         | _     | V    |

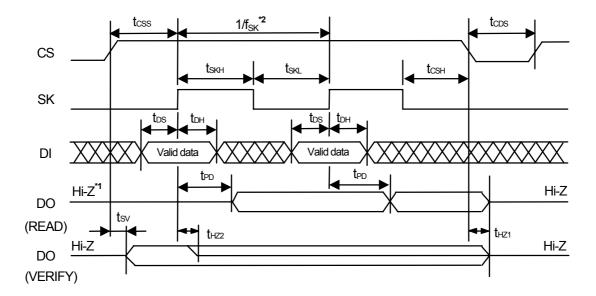

# ■ AC Electrical Characteristics

**Table 11 Measurement Conditions**

| Input pulse voltage      | $0.1 \times V_{CC}$ to $0.9 \times V_{CC}$ |

|--------------------------|--------------------------------------------|

| Output reference voltage | $0.5 \times V_{CC}$                        |

| Output load              | 100 pF                                     |

Table 12

|                      |                    |                   |        |       | -40               | ) to +8 | 5°C   |                   |        |       | +85               | to +10 | )5°C  |      |

|----------------------|--------------------|-------------------|--------|-------|-------------------|---------|-------|-------------------|--------|-------|-------------------|--------|-------|------|

| Item                 | Symbol             | V <sub>CC</sub> = | 4.5 to | 5.5 V | V <sub>CC</sub> = | 2.5 to  | 4.5 V | V <sub>CC</sub> = | 1.8 to | 2.5 V | V <sub>CC</sub> = | 4.5 to | 5.5 V | Unit |

|                      |                    | Min.              | Тур.   | Max.  | Min.              | Тур.    | Max.  | Min.              | Тур.   | Max.  | Min.              | Тур.   | Max.  |      |

| CS setup time        | t <sub>CSS</sub>   | 0.2               | _      | _     | 0.4               | _       | _     | 1.0               |        | _     | 0.2               |        |       | μs   |

| CS hold time         | t <sub>CSH</sub>   | 0                 | _      | _     | 0                 | _       | _     | 0                 | _      | _     | 0                 |        | _     | μs   |

| CS deselect time     | t <sub>CDS</sub>   | 0.2               | _      | _     | 0.2               | _       | _     | 0.4               | _      | _     | 0.2               |        | _     | μs   |

| Data setup time      | $t_{DS}$           | 0.1               | _      | _     | 0.2               | _       | _     | 0.4               | _      | _     | 0.1               |        |       | μs   |

| Data hold time       | $t_{DH}$           | 0.1               | _      | _     | 0.2               | _       | _     | 0.4               | _      | _     | 0.1               |        |       | μs   |

| Output delay time    | $t_{PD}$           | _                 | _      | 0.4   | _                 | _       | 0.8   | _                 | _      | 2.0   |                   |        | 0.6   | μs   |

| Clock frequency*1    | $f_{SK}$           | 0                 | _      | 2.0   | 0                 | _       | 0.5   | 0                 | _      | 0.25  | 0                 |        | 1.0   | MHz  |

| SK clock time "L" *1 | t <sub>SKL</sub>   | 0.1               | _      | _     | 0.5               | _       | _     | 1.0               | _      | _     | 0.25              |        |       | μs   |

| SK clock time "H" *1 | t <sub>SKH</sub>   | 0.1               | _      | _     | 0.5               | _       | _     | 1.0               | _      | _     | 0.25              |        | _     | μs   |

| Output disable time  | $t_{HZ1}, t_{HZ2}$ | 0                 |        | 0.15  | 0                 | _       | 0.5   | 0                 | _      | 1.0   | 0                 |        | 0.15  | μs   |

| Output enable time   | t <sub>SV</sub>    | 0                 |        | 0.15  | 0                 | _       | 0.5   | 0                 | _      | 1.0   | 0                 |        | 0.15  | μs   |

<sup>\*1.</sup> The clock cycle of the SK clock (frequency:  $f_{SK}$ ) is  $1/f_{SK}$   $\mu s$ . This clock cycle is determined by a combination of several AC characteristics, so be aware that even if the SK clock cycle time is minimized, the clock cycle  $(1/f_{SK})$  cannot be made to equal  $t_{SKL}(Min.) + t_{SKH}(Min.)$ .

Table 13

|            |                 | _               | -40 to +85°     | С    | +85 to +105°C                            |      |      | Unit |

|------------|-----------------|-----------------|-----------------|------|------------------------------------------|------|------|------|

| Item       | Symbol          | V <sub>CC</sub> | c = 2.7  to  5. | 5 V  | $V_{CC} = 4.5 \text{ to } 5.5 \text{ V}$ |      |      |      |

|            |                 | Min.            | Тур.            | Max. | Min.                                     | Тур. | Max. |      |

| Write time | t <sub>PR</sub> |                 | 2.0             | 4.0  | _                                        | 2.0  | 4.0  | ms   |

- \*1. Indicates high impedance.

- \*2.  $1/f_{SK}$  is the SK clock cycle. This clock cycle is determined by a combination of several AC characteristics, so be aware that even if the SK clock cycle time is minimized, the clock cycle  $(1/f_{SK})$  cannot be made to equal  $t_{SKL}(Min.) + t_{SKH}(Min.)$ .

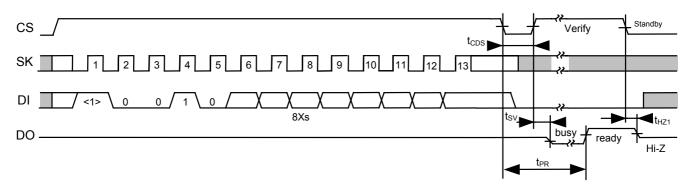

Figure 4 Timing Chart

#### ■ Operation

All instructions are executed by inputting DI in synchronization with the rising edge of SK after CS goes high. An instruction set is input in the order of start bit, instruction, address, and data.

Instruction input finishes when CS goes low. A low level must be input to CS between commands during  $t_{\text{CDS}}$ . While a low level is being input to CS, the S-93C86B is in standby mode, so the SK and DI inputs are invalid and no instructions are allowed.

#### ■ Start Bit

A start bit is recognized when the DI pin goes high at the rise of SK after CS goes high. After CS goes high, a start bit is not recognized even if the SK pulse is input as long as the DI pin is low.

#### 1. Dummy clock

SK clocks input while the DI pin is low before a start bit is input are called dummy clocks. Dummy clocks are effective when aligning the number of instruction sets (clocks) sent by the CPU with those required for serial memory operation. For example, when a CPU instruction set is 16 bits, the number of instruction set clocks can be adjusted by inserting a 3-bit dummy clock for the S-93C86B.

#### 2. Start bit input failure

- When the output status of the DO pin is high during the verify period after a write operation, if a high level is input to the DI pin at the rising edge of SK, the S-93C86B recognizes that a start bit has been input. To prevent this failure, input a low level to the DI pin during the verify operation period (refer to "4.1 Verify operation").

- When a 3-wire interface is configured by connecting the DI input pin and DO output pin, a period in which the data output from the CPU and the serial memory collide may be generated, preventing successful input of the start bit. Take the measures described in "■ 3-Wire Interface (Direct Connection between DI and DO)".

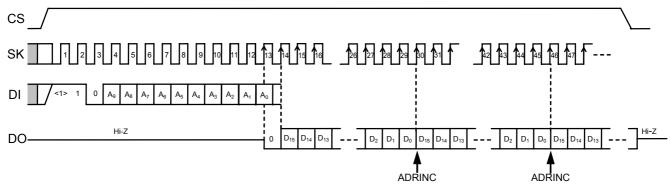

#### 3. Reading (READ)

The READ instruction reads data from a specified address.

After CS has gone high, input an instruction in the order of the start bit, read instruction, and address. Since the last input address  $(A_0)$  has been latched, the output status of the DO pin changes from high impedance (Hi-Z) to low, which is held until the next rise of SK. 16-bit data starts to be output in synchronization with the next rise of SK.

#### 3.1 Sequential read

After the 16-bit data at the specified address has been output, inputting SK while CS is high automatically increments the address, and causes the 16-bit data at the next address to be output sequentially. The above method makes it possible to read the data in the whole memory space. The last address ( $A_9 \cdot \cdot \cdot A_1 A_0 = 1 \cdot \cdot \cdot 1$ ) rolls over to the top address ( $A_9 \cdot \cdot \cdot A_1 A_0 = 0 \cdot \cdot \cdot 0$ ).

Figure 5 Read Timing

#### 4. Writing (WRITE, ERASE, WRAL, ERAL)

A write operation includes four write instructions: data write (WRITE), data erase (ERASE), chip write (WRAL), and chip erase (ERAL).

A write instruction (WRITE, ERASE, WRAL, ERAL) starts a write operation to the memory cell when a low level is input to CS after a specified number of clocks have been input. The SK and DI inputs are invalid during the write period, so do not input an instruction.

Input an instruction while the output status of the DO pin is high or high impedance (Hi-Z).

A write operation is valid only in program enable mode (refer to "5. Write enable (EWEN) and write disable (EWDS)").

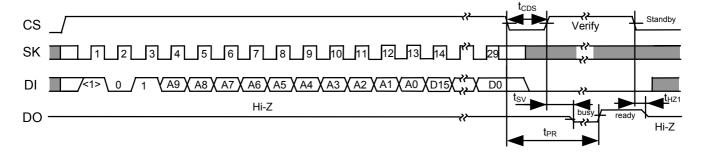

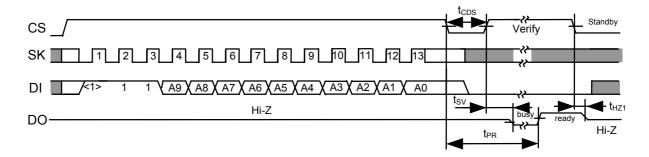

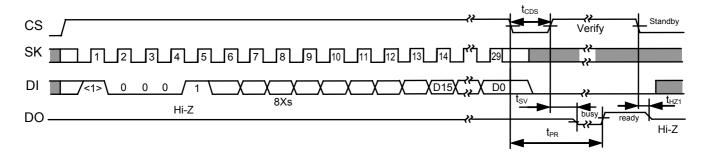

#### 4.1 Verify operation

A write operation executed by any instruction is completed within 4 ms (write time  $t_{PR}$ : typically 2 ms), so if the completion of the write operation is recognized, the write cycle can be minimized. A sequential operation to confirm the status of a write operation is called a verify operation.

#### (1) Operation

After the write operation has started (CS = low), the status of the write operation can be verified by confirming the output status of the DO pin by inputting a high level to CS again. This sequence is called a verify operation, and the period that a high level is input to the CS pin after the write operation has started is called the verify operation period.

The relationship between the output status of the DO pin and the write operation during the verify operation period is as follows.

• DO pin = low: Writing in progress (busy)

• DO pin = high: Writing completed (ready)

#### (2) Operation example

There are two methods to perform a verify operation: Waiting for a change in the output status of the DO pin while keeping CS high, or suspending the verify operation (CS = low) once and then performing it again to verify the output status of the DO pin. The latter method allows the CPU to perform other processing during the wait period, allowing an efficient system to be designed.

#### Caution 1. Input a low level to the DI pin during a verify operation.

If a high level is input to the DI pin at the rise of SK when the output status of the DO pin is high, the S-93C86B latches the instruction assuming that a start bit has been input. In this case, note that the DO pin immediately enters a high-impedance (Hi-Z) state.

#### 4.2 Writing data (WRITE)

To write 16-bit data to a specified address, change CS to high and then input the WRITE instruction, address, and 16-bit data following the start bit. The write operation starts when CS goes low. There is no need to set the data to 1 before writing. When the clocks more than the specified number have been input, the clock pulse monitoring circuit cancels the WRITE instruction. For details of the clock pulse monitoring circuit, refer to "■ Function to Protect Against Write due to Erroneous Instruction Recognition".

Figure 6 Data Write Timing

#### 4.3 Erasing data (ERASE)

To erase 16-bit data at a specified address, set all 16 bits of the data to 1, change CS to high, and then input the ERASE instruction and address following the start bit. There is no need to input data. The data erase operation starts when CS goes low. When the clocks more than the specified number have been input, the clock pulse monitoring circuit cancels the ERASE instruction. For details of the clock pulse monitoring circuit, refer to "

Function to Protect Against Write due to Erroneous Instruction Recognition".

Figure 7 Data Erase Timing

#### 4.4 Writing to chip (WRAL)

To write the same 16-bit data to the entire memory address space, change CS to high, and then input the WRAL instruction, an address, and 16-bit data following the start bit. Any address can be input. The write operation starts when CS goes low. There is no need to set the data to 1 before writing. When the clocks more than the specified number been input, the clock pulse monitoring circuit cancels the WRAL instruction. For details of the clock pulse monitoring circuit, refer to "■ Function to Protect Against Write due to Erroneous Instruction Recognition".

Figure 8 Chip Write Timing

### 4.5 Erasing chip (ERAL)

To erase the data of the entire memory address space, set all the data to 1, change CS to high, and then input the ERAL instruction and an address following the start bit. Any address can be input. There is no need to input data. The chips erase operation starts when CS goes low. When the clocks more than the specified number have been input, the clock pulse monitoring circuit cancels the ERAL instruction. For details of the clock pulse monitoring circuit, refer to "■ Function to Protect Against Write due to Erroneous Instruction Recognition".

Figure 9 Chip Erase Timing

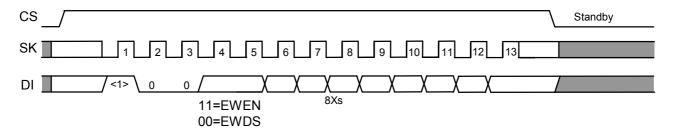

#### 5. Write enable (EWEN) and write disable (EWDS)

The EWEN instruction is an instruction that enables a write operation. The status in which a write operation is enabled is called the program enable mode.

The EWDS instruction is an instruction that disables a write operation. The status in which a write operation is disabled is called the program disable mode.

After CS goes high, input an instruction in the order of the start bit, EWEN or EWDS instruction, and address (optional). Each mode becomes valid by inputting a low level to CS after the last address (optional) has been input.

Figure 10 Write Enable/Disable Timing

#### (1) Recommendation for write operation disable instruction

It is recommended to implement a design that prevents an incorrect write operation when a write instruction is erroneously recognized by executing the write operation disable instruction when executing instructions other than write instruction, and immediately after power-on and before power off.

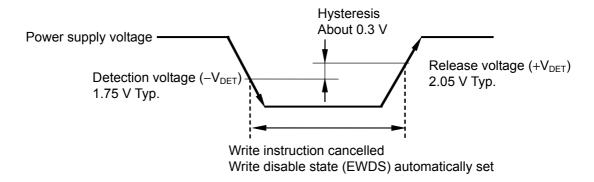

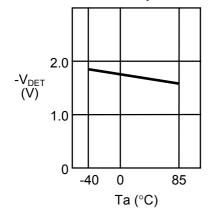

# ■ Write Disable Function when Power Supply Voltage is Low

The S-93C86B provides a built-in detector to detect a low power supply voltage and disable writing. When the power supply voltage is low or at power application, the write instructions (WRITE, ERASE, WRAL, and ERAL) are cancelled, and the write disable state (EWDS) is automatically set. The detection voltage is 1.75 V typ., the release voltage is 2.05 V typ., and there is a hysteresis of about 0.3 V (refer to **Figure 11**). Therefore, when a write operation is performed after the power supply voltage has dropped and then risen again up to the level at which writing is possible, a write enable instruction (EWEN) must be sent before a write instruction (WRITE, ERASE, WRAL, or ERAL) is executed.

When the power supply voltage drops during a write operation, the data being written to an address at that time is not guaranteed.

Figure 11 Operation when Power Supply Voltage is Low

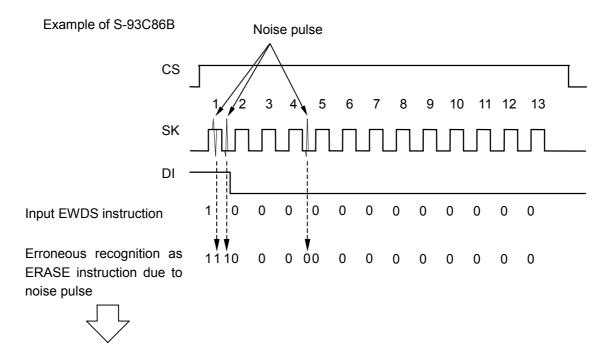

# ■ Function to Protect Against Write due to Erroneous Instruction Recognition

The S-93C86B provides a built-in clock pulse monitoring circuit which is used to prevent an erroneous write operation by canceling write instructions (WRITE, ERASE, WRAL, and ERAL) recognized erroneously due to an erroneous clock count caused by the application of noise pulses or double counting of clocks. Instructions are cancelled if a clock pulse whose count other than the one specified for each write instruction (WRITE, ERASE, WRAL, or ERAL) is detected.

<Example> Erroneous recognition of program disable instruction (EWDS) as erase instruction (ERASE)

In products that do not incorporate a clock pulse monitoring circuit, FFFF is mistakenly written to address 00h. However the S-93C86B detects the over count and cancels the instruction without performing a write operation.

Figure 12 Example of Clock Pulse Monitoring Circuit Operation

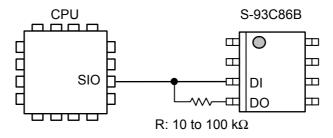

#### ■ 3-Wire Interface (Direct Connection between DI and DO)

There are two types of serial interface configurations: a 4-wire interface configured using the CS, SK, DI, and DO pins, and a 3-wire interface that connects the DI input pin and DO output pin.

When the 3-wire interface is employed, a period in which the data output from the CPU and the data output from the serial memory collide may occur, causing a malfunction. To prevent such a malfunction, connect the DI and DO pins of the S-93C86B via a resistor (10 to 100 k $\Omega$ ) so that the data output from the CPU takes precedence in being input to the DI pin (refer to "Figure 13 Connection of 3-Wire Interface").

Figure 13 Connection of 3-Wire Interface

#### ■ I/O Pins

#### 1. Connection of input pins

All the input pins of the S-93C86B employ a C-MOS structure, so design the equipment so that high impedance will not be input while the S-93C86B is operating. Especially, deselect the CS input (a low level) when turning on/off power and during standby. When the CS pin is deselected (a low level), incorrect data writing will not occur. Connect the CS pin to GND via a resistor (10 to 100 k $\Omega$  pull-down resistor). To prevent malfunction, it is recommended to use equivalent pull-down resistors for pins other than the CS pin.

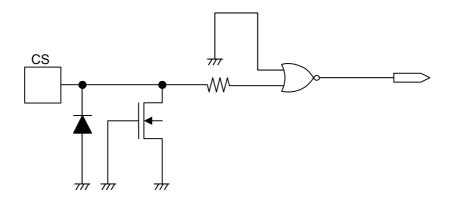

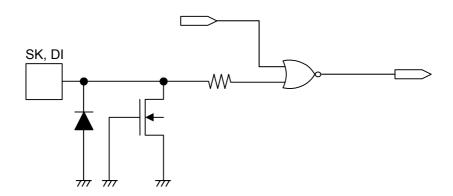

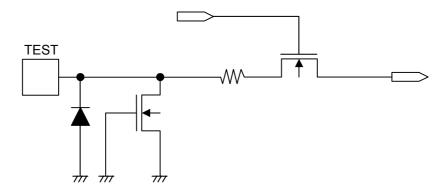

#### 2. Input and output pin equivalent circuits

The following shows the equivalent circuits of input pins of the S-93C86B. None of the input pins incorporate pull-up and pull-down elements, so special care must be taken when designing to prevent a floating status.

Output pins are high-level/low-level/high-impedance tri-state outputs. The TEST pin is disconnected from the internal circuit by a switching transistor during normal operation. As long as the absolute maximum rating is satisfied, the TEST pin and internal circuit will never be connected.

# 2.1 Input pin

Figure 14 CS Pin

Figure 15 SK, DI Pin

Figure 16 TEST Pin

#### 2.2 Output pin

Figure 17 DO Pin

#### 3. Input pin noise elimination time

The S-93C86B includes a built-in low-pass filter to eliminate noise at the SK, DI, and CS pins. This means that if the supply voltage is 5.0 V (at room temperature), noise with a pulse width of 20 ns or less can be eliminated.

Note, therefore, that noise with a pulse width of more than 20 ns will be recognized as a pulse if the voltage exceeds  $V_{IH}/V_{IL}$ .

#### **■** Precaution

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- SII claims no responsibility for any and all disputes arising out of or in connection with any infringement of the products including this IC upon patents owned by a third party.

# ■ Characteristics (Typical Data)

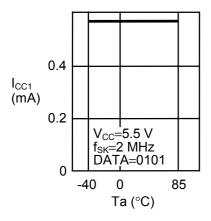

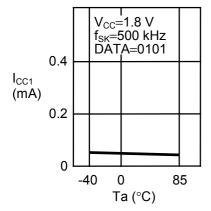

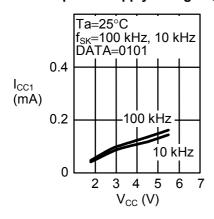

- 1. DC Characteristics

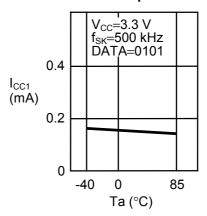

- 1. 1 Current consumption (READ) I<sub>CC1</sub> vs. ambient temperature Ta

1. 3 Current consumption (READ) I<sub>CC1</sub> vs. ambient temperature Ta

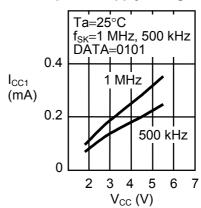

1. 5 Current consumption (READ) I<sub>CC1</sub> vs. power supply voltage V<sub>CC</sub>

1. 2 Current consumption (READ) I<sub>CC1</sub> vs. ambient temperature Ta

1. 4 Current consumption (READ) I<sub>CC1</sub> vs. power supply voltage V<sub>CC</sub>

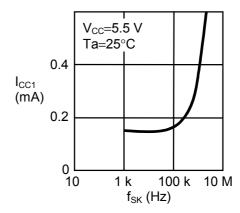

1. 6 Current consumption (READ) I<sub>CC1</sub> vs. Clock frequency f<sub>SK</sub>

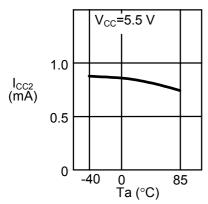

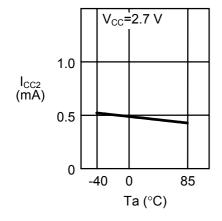

1. 7 Current consumption (WRITE)  $I_{\text{CC2}}$  vs. ambient temperature Ta

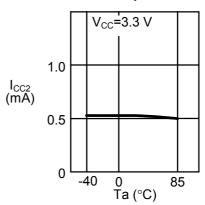

1. 9 Current consumption (WRITE) I<sub>CC2</sub> vs. ambient temperature Ta

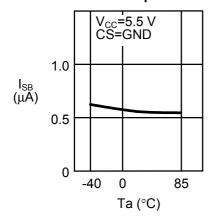

1. 11 Current consumption in standby mode I<sub>SB</sub> vs. ambient temperature Ta

1. 8 Current consumption (WRITE)  $I_{\text{CC2}}$  vs. ambient temperature Ta

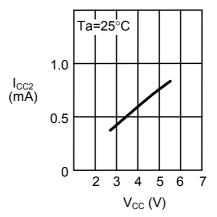

1. 10 Current consumption (WRITE)  $I_{CC2}$  vs. power supply voltage  $V_{CC}$

1. 12 Current consumption in standby mode  $I_{\text{SB}}$  vs. power supply voltage  $V_{\text{CC}}$

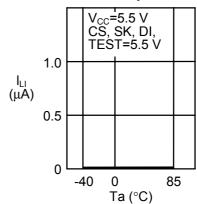

1. 13 Input leakage current I<sub>LI</sub> vs. ambient temperature Ta

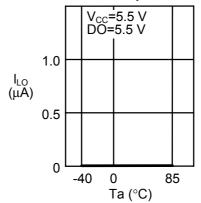

1. 15 Output leakage current I<sub>LO</sub> vs. ambient temperature Ta

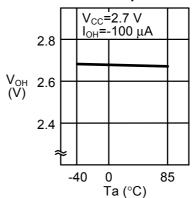

1. 17 High-level output voltage V<sub>OH</sub> vs. ambient temperature Ta

1. 14 Input leakage current I<sub>LI</sub> vs. ambient temperature Ta

1. 16 Output leakage current I<sub>LO</sub> vs. ambient temperature Ta

1. 18 High-level output voltage V<sub>OH</sub> vs. ambient temperature Ta

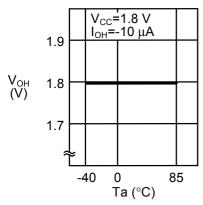

1. 19 High-level output voltage V<sub>OH</sub> vs. ambient temperature Ta

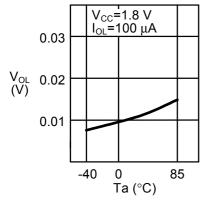

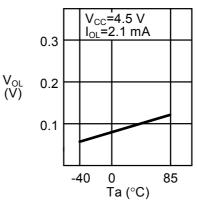

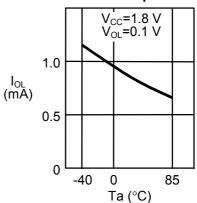

1. 21 Low-level output voltage  $V_{\text{OL}}$  vs. ambient temperature Ta

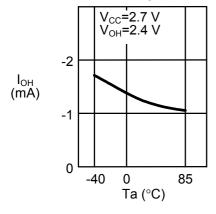

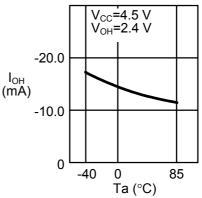

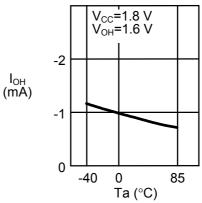

1. 23 High-level output current I<sub>OH</sub> vs. ambient temperature Ta

1. 20 Low-level output voltage V<sub>OL</sub> vs. ambient temperature Ta

1. 22 High-level output current I<sub>OH</sub> vs. ambient temperature Ta

1. 24 High-level output current I<sub>OH</sub> vs. ambient temperature Ta

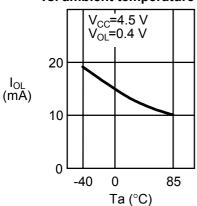

1. 25 Low-level output current  $I_{\text{OL}}$  vs. ambient temperature Ta

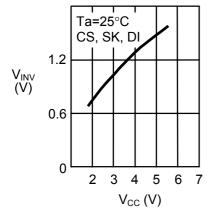

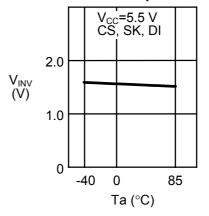

1. 27 Input inverted voltage  $V_{\text{INV}}$  vs. power supply voltage  $V_{\text{CC}}$

1. 29 Low supply voltage detection voltage –V<sub>DET</sub> vs. ambient temperature Ta

1. 26 Low-level output current I<sub>OL</sub> vs. ambient temperature Ta

1. 28 Input inverted voltage V<sub>INV</sub> vs. ambient temperature Ta

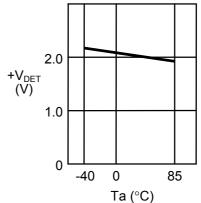

1. 30 Low supply voltage release voltage +V<sub>DET</sub> vs. ambient temperature Ta

#### 2. AC Characteristics

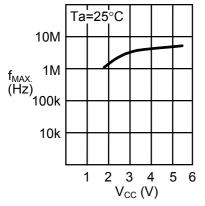

# 2. 1 Maximum operating frequency $f_{MAX.}$ vs. power supply voltage $V_{CC}$

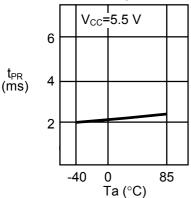

#### 2. 3 Write time t<sub>PR</sub>

vs. ambient temperature Ta

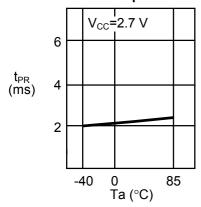

#### 2. 5 Write time tpr

vs. ambient temperature Ta

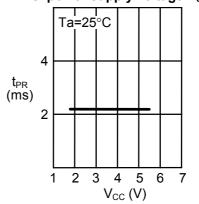

#### 2. 2 Write time t<sub>PR</sub>

vs. power supply voltage V<sub>cc</sub>

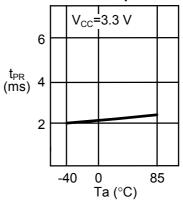

# 2. 4 Write time t<sub>PR</sub>

vs. ambient temperature Ta

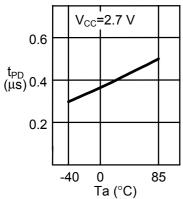

# 2. 6 Data output delay time t<sub>PD</sub> vs. ambient temperature Ta

2. 7 Data output delay time  $t_{\text{PD}}$  vs. ambient temperature Ta

2. 8 Data output delay time  $t_{\text{PD}}$  vs. ambient temperature Ta

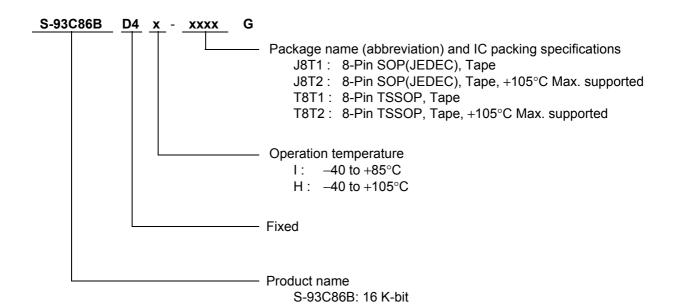

# **■ Product Name Structure**

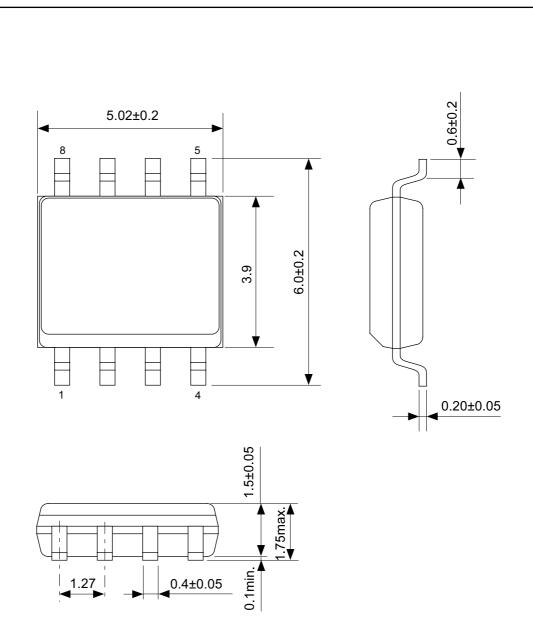

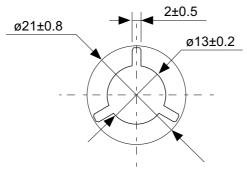

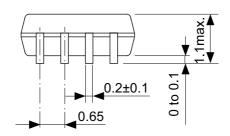

# No. FJ008-A-P-SD-2.1

| TITLE                  | SOP8J-D-PKG Dimensions |  |  |  |  |

|------------------------|------------------------|--|--|--|--|

| No.                    | FJ008-A-P-SD-2.1       |  |  |  |  |

| SCALE                  |                        |  |  |  |  |

| UNIT                   | mm                     |  |  |  |  |

|                        |                        |  |  |  |  |

|                        |                        |  |  |  |  |

|                        |                        |  |  |  |  |

|                        |                        |  |  |  |  |

| Seiko Instruments Inc. |                        |  |  |  |  |

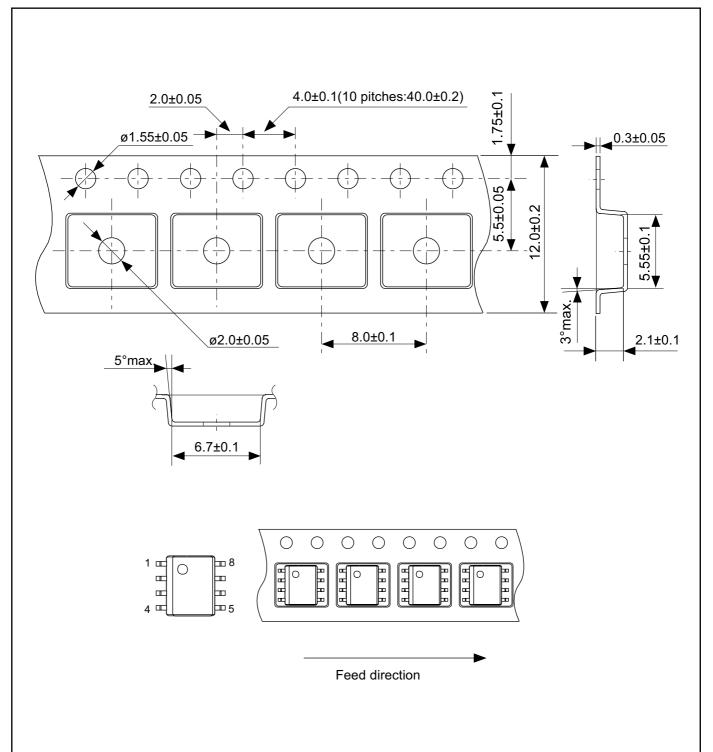

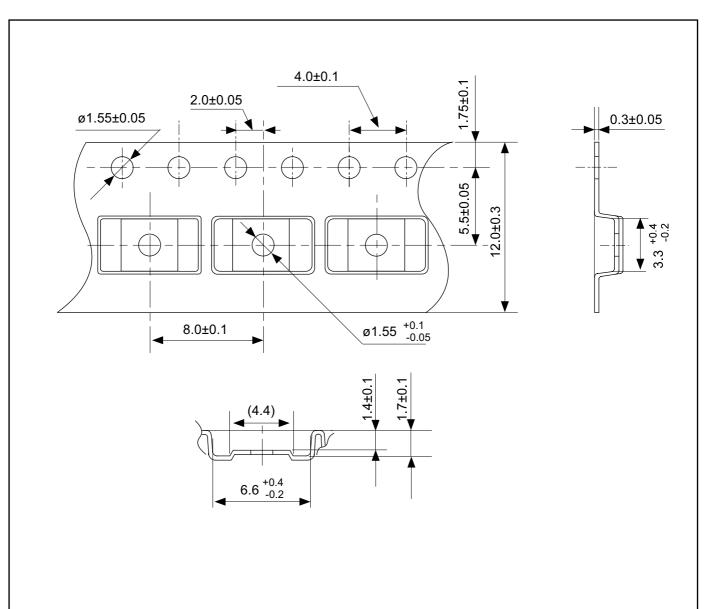

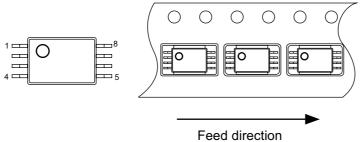

# No. FJ008-D-C-SD-1.1

| TITLE                  | SOP8J-D-Carrier Tape |  |  |  |  |  |

|------------------------|----------------------|--|--|--|--|--|

| No.                    | FJ008-D-C-SD-1.1     |  |  |  |  |  |

| SCALE                  |                      |  |  |  |  |  |

| UNIT                   | mm                   |  |  |  |  |  |

|                        |                      |  |  |  |  |  |

|                        |                      |  |  |  |  |  |

|                        |                      |  |  |  |  |  |

| Seiko Instruments Inc. |                      |  |  |  |  |  |

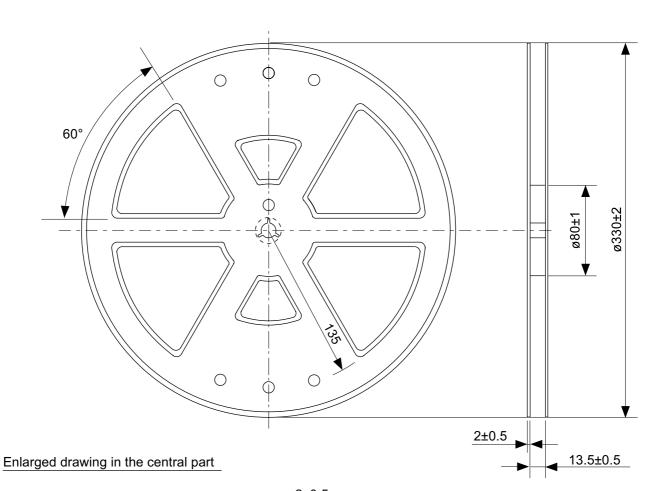

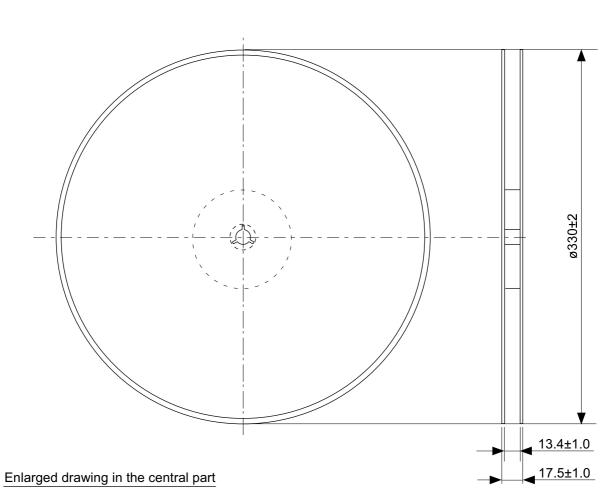

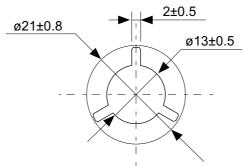

# No. FJ008-D-R-SD-1.1

| TITLE                  | SOP8J-D-Reel     |  |  |  |  |  |

|------------------------|------------------|--|--|--|--|--|

| No.                    | FJ008-D-R-SD-1.1 |  |  |  |  |  |

| SCALE                  | QTY. 2,000       |  |  |  |  |  |

| UNIT                   | mm               |  |  |  |  |  |

|                        |                  |  |  |  |  |  |

|                        |                  |  |  |  |  |  |

|                        |                  |  |  |  |  |  |

| Seiko Instruments Inc. |                  |  |  |  |  |  |

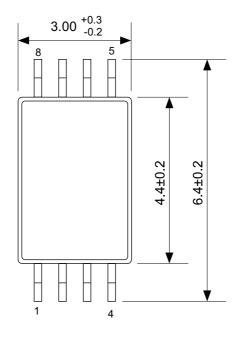

# No. FT008-A-P-SD-1.1

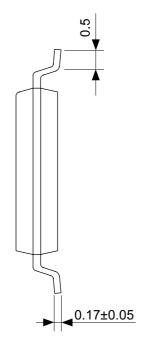

# No. FT008-E-C-SD-1.0

| TITLE                  | TSSOP8-E-Carrier Tape |  |  |  |  |

|------------------------|-----------------------|--|--|--|--|

| No.                    | FT008-E-C-SD-1.0      |  |  |  |  |

| SCALE                  |                       |  |  |  |  |

| UNIT                   | mm                    |  |  |  |  |

|                        |                       |  |  |  |  |

|                        |                       |  |  |  |  |

|                        |                       |  |  |  |  |

|                        |                       |  |  |  |  |

| Seiko Instruments Inc. |                       |  |  |  |  |

# No. FT008-E-R-SD-1.0

| TITLE                       | TSSOP8-E-Reel    |      |       |  |  |  |

|-----------------------------|------------------|------|-------|--|--|--|

| No.                         | FT008-E-R-SD-1.0 |      |       |  |  |  |

| SCALE                       |                  | QTY. | 3,000 |  |  |  |

| UNIT                        | mm               | -    | -     |  |  |  |

|                             |                  |      |       |  |  |  |

|                             |                  |      |       |  |  |  |

|                             |                  |      |       |  |  |  |

| Seiko Instruments Inc.      |                  |      |       |  |  |  |

| Seiko ilistiulliellis IIIC. |                  |      |       |  |  |  |

- The information described herein is subject to change without notice.

- Seiko Instruments Inc. is not responsible for any problems caused by circuits or diagrams described herein whose related industrial properties, patents, or other rights belong to third parties. The application circuit examples explain typical applications of the products, and do not guarantee the success of any specific mass-production design.

- When the products described herein are regulated products subject to the Wassenaar Arrangement or other agreements, they may not be exported without authorization from the appropriate governmental authority.

- Use of the information described herein for other purposes and/or reproduction or copying without the express permission of Seiko Instruments Inc. is strictly prohibited.

- The products described herein cannot be used as part of any device or equipment affecting the human body, such as exercise equipment, medical equipment, security systems, gas equipment, or any apparatus installed in airplanes and other vehicles, without prior written permission of Seiko Instruments Inc.

- Although Seiko Instruments Inc. exerts the greatest possible effort to ensure high quality and reliability, the failure or malfunction of semiconductor products may occur. The user of these products should therefore give thorough consideration to safety design, including redundancy, fire-prevention measures, and malfunction prevention, to prevent any accidents, fires, or community damage that may ensue.