#### LM193JAN

# Low Power Low Offset Voltage Dual Comparators

#### **General Description**

The LM193 series consists of two independent precision voltage comparators with an offset voltage specification as low as 2.0 mV max for two comparators which were designed specifically to operate from a single power supply over a wide range of voltages. Operation from split power supplies is also possible and the low power supply current drain is independent of the magnitude of the power supply voltage. These comparators also have a unique characteristic in that the input common-mode voltage range includes ground, even though operated from a single power supply voltage.

Application areas include limit comparators, simple analog to digital converters; pulse, squarewave and time delay generators; wide range VCO; MOS clock timers; multivibrators and high voltage digital logic gates. The LM193 series was designed to directly interface with TTL and CMOS. When operated from both plus and minus power supplies, the LM193 series will directly interface with MOS logic where their low power drain is a distinct advantage over standard comparators.

#### **Advantages**

- High precision comparators

- Reduced V<sub>OS</sub> drift over temperature

- Eliminates need for dual supplies

- Allows sensing near ground

- Compatible with all forms of logic

- Power drain suitable for battery operation

#### **Features**

- Wide supply

- Very low supply current drain (0.4 mA) independent of supply voltage

- Low input biasing current: 25 nA typ

- Low input offset current: ±3 nA typ

- Maximum offset voltage +5mV Max @ 25°C

- Input common-mode voltage range includes ground

- Differential input voltage range equal to the power supply voltage

- Low output saturation voltage,: 250 mV at 4 mA typ

- Output voltage compatible with TTL, DTL, ECL, MOS and CMOS logic systems

#### **Ordering Information**

| NS Part Number | JAN Part Number  | NS Package Number | Package Description |

|----------------|------------------|-------------------|---------------------|

| JL193BGA       | JM38510/11202BGA | H08C              | 8LD T0-99 Metal Can |

| JL193BPA       | JM38510/11202BPA | J08A              | 8LD CERDIP          |

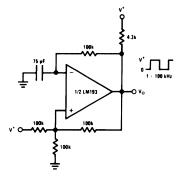

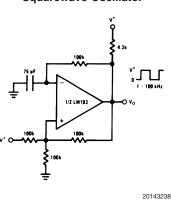

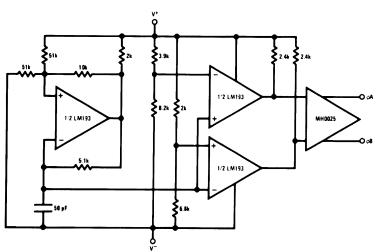

#### Squarewave Oscillator

20143238

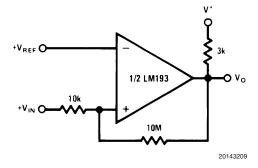

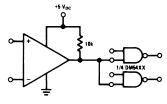

#### Non-Inverting Comparator with Hysteresis

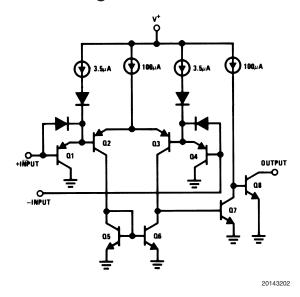

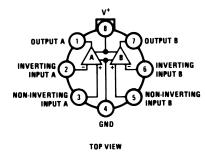

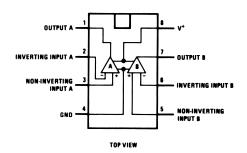

# **Schematic and Connection Diagrams**

Metal Can Package

20143203

#### **Dual-In-Line Package**

20143201

#### **Absolute Maximum Ratings** (Note 1)

Supply Voltage, V+  $36V_{DC}$  or  $\pm 18V_{DC}$  Differential Input Voltage (Note 5) 36V Output Voltage 36V Input Voltage  $-0.3V_{DC}$  to  $+36V_{DC}$  Input Current ( $V_{IN} < -0.3V_{DC}$ ) (Note 4) 50 mA Power Dissipation (Note 2),

CERDIP 400 mW @  $T_A = 125$  °C Metal Can 330 mW @  $T_A = 125$  °C

Thermal Resistance

θ<sub>JA</sub>

Metal Can (Still Air)

Metal Can (500LF/Min Air flow)

CERDIP (Still Air)

CERDIP (500LF/Min Air flow)

85°C/W

a)C

Metal Can 44°C/W

CERDIP 33°C/W

Lead Temperature (Soldering, 10 seconds) 260°C

ESD Tolerance (Note 6) 500V

#### **Quality Conformance Inspection**

Mil-Std-883, Method 5005 - Group A

| Subgroup | Description         | Temp°C |

|----------|---------------------|--------|

| 1        | Static tests at     | 25     |

| 2        | Static tests at     | 125    |

| 3        | Static tests at     | -55    |

| 4        | Dynamic tests at    | 25     |

| 5        | Dynamic tests at    | 125    |

| 6        | Dynamic tests at    | -55    |

| 7        | Functional tests at | 25     |

| 8A       | Functional tests at | 125    |

| 8B       | Functional tests at | -55    |

| 9        | Switching tests at  | 25     |

| 10       | Switching tests at  | 125    |

| 11       | Switching tests at  | -55    |

| 12       | Settling time at    | 25     |

| 13       | Settling time at    | 125    |

| 14       | Settling time at    | -55    |

# **LM193 JAN Electrical Characteristics DC Parameters**

| Symbol                    | Parameter                  | Conditions                                                    | Notes    | Min  | Max  | Unit  | Sub-        |

|---------------------------|----------------------------|---------------------------------------------------------------|----------|------|------|-------|-------------|

| V <sub>IO</sub>           | Input Offset Voltage       | +V <sub>CC</sub> = 30V, -V <sub>CC</sub> = 0V,                | Notes    | -5.0 | 5.0  | mV    | groups<br>1 |

| •10                       | Input Onset Voltage        | $V_{O} = 15V$                                                 |          | -7.0 | 7.0  | mV    | 2, 3        |

|                           |                            | $+V_{CC} = 2V, -V_{CC} = -28V,$                               |          | -5.0 | 5.0  | mV    | 1           |

|                           |                            | $V_O = -13V$                                                  |          | -7.0 | 7.0  | mV    | 2, 3        |

|                           |                            | $+V_{CC} = 5V, -V_{CC} = 0V,$                                 |          | -5.0 | 5.0  | mV    | 1           |

|                           |                            | $V_O = 1.4V$                                                  |          | -7.0 | 7.0  | mV    | 2, 3        |

|                           |                            | +V <sub>CC</sub> = 2V, -V <sub>CC</sub> = -3V,                |          | -5.0 | 5.0  | mV    | 1           |

|                           |                            | V <sub>O</sub> = -1.6V                                        |          | -7.0 | 7.0  | mV    | 2, 3        |

| I <sub>IO</sub>           | Input offset Current       | +V <sub>CC</sub> = 30V, -V <sub>CC</sub> = 0V,                | (Note 7) | -25  | 25   | nA    | 1, 2        |

|                           |                            | $V_O = 15V$ , $R_S = 20K\Omega$                               | (Note 7) | -75  | 75   | nA    | 3           |

|                           |                            | $+V_{CC} = 2V, -V_{CC} = -28V,$                               | (Note 7) | -25  | 25   | nA    | 1, 2        |

|                           |                            | $V_O = -13V$ , $R_S = 20K\Omega$                              | (Note 7) | -75  | 75   | nA    | 3           |

|                           |                            | $+V_{CC} = 5V, -V_{CC} = 0V,$                                 | (Note 7) | -25  | 25   | nA    | 1, 2        |

|                           |                            | $V_{O} = 1.4V, R_{S} = 20K\Omega$                             | (Note 7) | -75  | 75   | nA    | 3           |

|                           |                            | $+V_{CC} = 2V, -V_{CC} = -3V,$                                | (Note 7) | -25  | 25   | nA    | 1, 2        |

|                           |                            | $V_{O} = -1.6V, R_{S} = 20K\Omega$                            | (Note 7) | -75  | 75   | nA    | 3           |

| ±I <sub>IB</sub>          | Input Bias Current         | $+V_{CC} = 30V, -V_{CC} = 0V,$                                | (Note 7) | -100 | +0.1 | nA    | 1, 2        |

|                           |                            | $V_O = 15V$ , $R_S = 20K\Omega$                               | (Note 7) | -200 | +0.1 | nA    | 3           |

|                           |                            | $+V_{CC} = 2V, -V_{CC} = -28V,$                               | (Note 7) | -100 | +0.1 | nA    | 1, 2        |

|                           |                            | $V_{O} = -13V, R_{S} = 20K\Omega$                             | (Note 7) | -200 | +0.1 | nA    | 3           |

|                           |                            | $+V_{CC} = 5V, -V_{CC} = 0V,$                                 | (Note 7) | -100 | +0.1 | nA    | 1, 2        |

|                           |                            | $V_O = 1.4V$ , $R_S = 20K\Omega$                              | (Note 7) | -200 | +0.1 | nA    | 3           |

|                           |                            | $+V_{CC} = 2V, -V_{CC} = -3V,$                                | (Note 7) | -100 | +0.1 | nA    | 1, 2        |

|                           |                            | $V_{O} = -1.6V, R_{S} = 20K\Omega$                            | (Note 7) | -200 | +0.1 | nA    | 3           |

| CMRR                      | Input Voltage Common Mode  | $2V \le +V_{CC} \le 30V$ ,                                    |          |      |      |       |             |

|                           | Rejection                  | $-28V \le -V_{CC} \le 0V$ ,                                   |          |      |      |       |             |

|                           |                            | -13V ≤ V <sub>O</sub> ≤ 15V                                   |          | 76   |      | dB    | 1, 2, 3     |

|                           |                            | $2V \le +V_{CC} \le 5V$                                       |          |      |      |       |             |

|                           |                            | $-3V \le -V_{CC} \le 0V$ ,                                    |          | 70   |      | aD    | 1 0 0       |

| 1                         | Output Lookaga Current     | $-1.6V \le V_O \le 1.4V$<br>$+V_{CC} = 30V, -V_{CC} = 0V,$    |          | 70   |      | dB    | 1, 2, 3     |

| I <sub>CEX</sub>          | Output Leakage Current     | $V_{\rm CC} = 30V, -V_{\rm CC} = 0V,$<br>$V_{\rm O} = +30V$   |          |      | 1.0  | μA    | 1, 2, 3     |

| <u>.</u>                  | Input Leakage Current      | $+V_{CC} = 36V, -V_{CC} = 0V,$                                |          |      | 1.0  | μΛ    | 1, 2, 0     |

| +I <sub>IL</sub>          | Input Leakage Guirent      | $+V_{CC} = 36V, -V_{CC} = 6V,$<br>$+V_{I} = 34V, -V_{I} = 0V$ |          | -500 | 500  | nA    | 1, 2, 3     |

| -I <sub>IL</sub>          | Input Leakage Current      | $+V_{CC} = 36V, -V_{CC} = 0V,$                                |          | 000  | 000  | 10.0  | 1, 2, 0     |

| 'IL                       | mpat Loanago Garront       | $+V_1 = 0V, -V_1 = 34V$                                       |          | -500 | 500  | nA    | 1, 2, 3     |

| V <sub>OL</sub>           | Logical "0" Output Voltage | $+V_{CC} = 4.5V, -V_{CC} = 0V,$                               |          |      | 0.4  | V     | 1           |

| VOL                       |                            | $I_{O} = 4mA$                                                 |          |      | 0.7  | V     | 2, 3        |

|                           |                            | $+V_{CC} = 4.5V, -V_{CC} = 0V,$                               |          |      | 1.5  | V     | 1           |

|                           |                            | $I_O = 8mA$                                                   |          |      | 2.0  | V     | 2, 3        |

| I <sub>cc</sub>           | Power Supply Current       | $+V_{CC} = 5V, -V_{CC} = 0V,$                                 |          |      | 2.0  | mA    | 1, 2        |

|                           |                            | $V_{ID} = 15 \text{mV}$                                       |          |      | 3.0  | mA    | 3           |

|                           |                            | $+V_{CC} = 30V, -V_{CC} = 0V,$                                |          |      | 3.0  | mA    | 1, 2        |

|                           |                            | $V_{ID} = 15 \text{mV}$                                       |          |      | 4.0  | mA    | 3           |

| $\Delta_{IO}$ / $\DeltaT$ | Temperature Coefficient of | 25°C ≤ T <sub>A</sub> ≤ +125°C                                | (Note 9) | -25  | 25   | μV/°C | 2           |

| ΔΙΟ / ΔΙ                  | 1                          |                                                               |          |      |      |       |             |

#### LM193 JAN Electrical Characteristics (Continued)

#### DC Parameters (Continued)

|                            |                            |                                                                       |          |      |     |       | Sub-   |

|----------------------------|----------------------------|-----------------------------------------------------------------------|----------|------|-----|-------|--------|

| Symbol                     | Parameter                  | Conditions                                                            | Notes    | Min  | Max | Unit  | groups |

| $\Delta I_{IO} / \Delta T$ | Temperature Coefficient of | $25^{\circ}\text{C} \le \text{T}_{\text{A}} \le +125^{\circ}\text{C}$ | (Note 9) | -300 | 300 | pA/°C | 2      |

| Input Offset (             | Input Offset Current       | -55°C ≤ T <sub>A</sub> ≤ 25°C                                         | (Note 9) | -400 | 400 | pA/°C | 3      |

| A <sub>VS</sub>            | Open Loop Voltage Gain     | $+V_{CC} = 15V, -V_{CC} = 0V,$ $R_{L} = 15KΩ,$                        | (Note 8) | 50   |     | V/mV  | 4      |

|                            |                            | $1V \le V_O \le 11V$                                                  | (Note 8) | 25   |     | V/mV  | 5, 6   |

| V <sub>Lat</sub>           | Voltage Latch (Logical "1" | $+V_{CC} = 5V, -V_{CC} = 0V,$                                         |          |      |     |       |        |

|                            | Input)                     | $V_I = 10V$ , $I_O = 4mA$                                             |          |      | 0.4 | V     | 9      |

#### **AC Parameters**

The following conditions apply, unless otherwise specified.  $+V_{CC} = 5V$ ,  $-V_{CC} = 0V$

|                  |                    |                                                            |       |     |     |      | Sub-   |

|------------------|--------------------|------------------------------------------------------------|-------|-----|-----|------|--------|

| Symbol           | Parameter          | Conditions                                                 | Notes | Min | Max | Unit | groups |

| t <sub>RLH</sub> | Response Time      | $V_{I} = 100 \text{mV}, R_{L} = 5.1 \text{K}\Omega,$       |       |     | 5.0 | μS   | 7, 8B  |

|                  |                    | $V_{OD} = 5mV$                                             |       |     | 7.0 | μS   | 8A     |

|                  |                    | $V_I = 100 \text{mV}, R_L = 5.1 \text{K}\Omega,$           |       |     | 0.8 | μS   | 7, 8B  |

|                  |                    | $V_{OD} = 50 \text{mV}$                                    |       |     | 1.2 | μS   | 8A     |

| t <sub>RHL</sub> | Response Time      | $V_I = 100 \text{mV}, R_L = 5.1 \text{K}\Omega,$           |       |     | 2.5 | μS   | 7, 8B  |

|                  |                    | $V_{OD} = 5mV$                                             |       |     | 3.0 | μS   | 8A     |

|                  |                    | $V_I = 100 \text{mV}, R_L = 5.1 \text{K}\Omega,$           |       |     | 0.8 | μS   | 7, 8B  |

|                  |                    | $V_{OD} = 50 \text{mV}$                                    |       |     | 1.0 | μS   | 8A     |

| CS               | Channel Separation | $+V_{CC} = 20V, -V_{CC} = -10V,$<br>A to B                 |       | 80  |     | dB   | 7      |

|                  |                    | +V <sub>CC</sub> = 20V, -V <sub>CC</sub> = -10V,<br>B to A |       | 80  |     | dB   | 7      |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$  (maximum junction temperature),  $\theta_{JA}$  (package junction to ambient thermal resistance), and  $T_A$  (ambient temperature). The maximum allowable power dissipation at any temperature is  $P_{Dmax} = (T_{Jmax} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower.

**Note 3:** Short circuits from the output to V<sup>+</sup> can cause excessive heating and eventual destruction. When considering short circuits to ground, the maximum output current is approximately 20 mA independent of the magnitude of V<sup>+</sup>.

**Note 4:** This input current will only exist when the voltage at any of the input leads is driven negative. It is due to the collector-base junction of the input PNP transistors becoming forward biased and thereby acting as input diode clamps. In addition to this diode action, there is also lateral NPN parasitic transistor action on the IC chip. This transistor action can cause the output voltages of the comparators to go to the V<sup>+</sup> voltage level (or to ground for a large overdrive) for the time duration that an input is driven negative. This is not destructive and normal output states will re-establish when the input voltage, which was negative, again returns to a value greater than -0.3V<sub>DC</sub>.

Note 5: Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than -0.3V (or 0.3V below the magnitude of the negative power supply, if used).

**Note 6:** Human body model,  $1.5K\Omega$  in series with 100pF.

Note 7: S/S R\_S = 20K $\Omega$ , tested with R\_S = 100K $\Omega$  for better resolution

Note 8: K in datalog is equivalent to V/mV.

Note 9: Calculated parameter for  $\Delta V_{IO}$  /  $\Delta T$  and  $\Delta I_{IO}$  /  $\Delta T.$

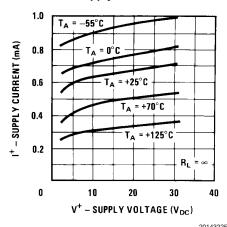

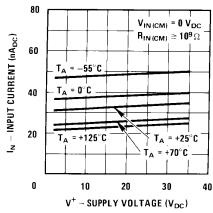

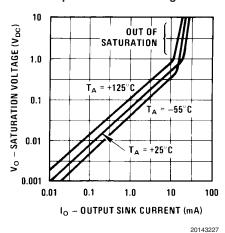

#### **Typical Performance Characteristics**

#### **Supply Current**

#### Input Current

2014222

#### **Output Saturation Voltage**

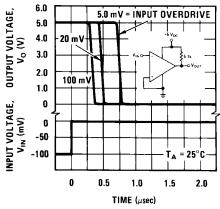

Response Time for Various Input Overdrives — Negative Transition

20143228

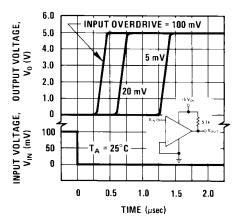

# Response Time for Various Input Overdrives — Positive Transition

20143229

#### **Application Hints**

The LM193 series are high gain, wide bandwidth devices which, like most comparators, can easily oscillate if the output lead is inadvertently allowed to capacitively couple to the inputs via stray capacitance. This shows up only during the output voltage transition intervals as the comparator change states. Power supply bypassing is not required to solve this problem. Standard PC board layout is helpful as it reduces stray input-output coupling. Reducing the input resistors to < 10 k $\Omega$  reduces the feedback signal levels and finally, adding even a small amount (1.0 to 10 mV) of positive feedback (hysteresis) causes such a rapid transition that oscillations due to stray feedback are not possible. Simply socketing the IC and attaching resistors to the pins will cause input-output oscillations during the small transition intervals unless hysteresis is used. If the input signal is a pulse waveform, with relatively fast rise and fall times, hysteresis is not required.

All input pins of any unused comparators should be tied to the negative supply.

The bias network of the LM193 series establishes a drain current which is independent of the magnitude of the power supply voltage over the range of from 2.0  $V_{\rm DC}$  to 30  $V_{\rm DC}$ .

It is usually unnecessary to use a bypass capacitor across the power supply line.

The differential input voltage may be larger than V $^+$  without damaging the device (Note 5). Protection should be provided to prevent the input voltages from going negative more than  $-0.3~V_{DC}$  (at  $25^{\circ}C$ ). An input clamp diode can be used as shown in the applications section.

The output of the LM193 series is the uncommitted collector of a grounded-emitter NPN output transistor. Many collectors can be tied together to provide an output OR'ing function. An output pull-up resistor can be connected to any available power supply voltage within the permitted supply voltage range and there is no restriction on this voltage due to the magnitude of the voltage which is applied to the V<sup>+</sup> terminal of the LM193 package. The output can also be used as a simple SPST switch to ground (when a pull-up resistor is not used). The amount of current which the output device can sink is limited by the drive available (which is independent of  $V^+$ ) and the  $\beta$  of this device. When the maximum current limit is reached (approximately 16mA), the output transistor will come out of saturation and the output voltage will rise very rapidly. The output saturation voltage is limited by the approximately  $60\Omega \; r_{SAT}$  of the output transistor. The low offset voltage of the output transistor (1.0mV) allows the output to clamp essentially to ground level for small load currents.

#### Typical Applications (V+=5.0 V<sub>DC</sub>)

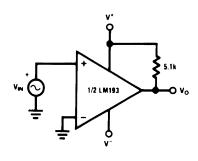

#### **Basic Comparator**

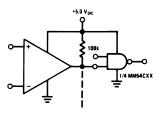

#### **Driving CMOS**

#### **Driving TTL**

20143237

#### **Squarewave Oscillator**

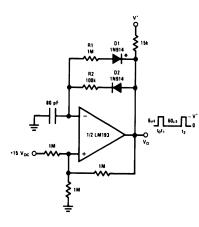

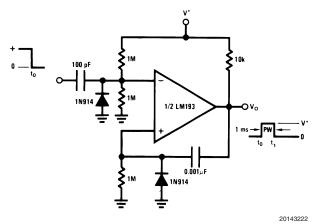

#### **Pulse Generator**

\* For large ratios of R1/R2, D1 can be omitted.

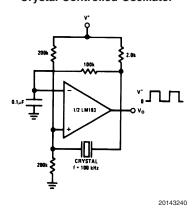

#### **Crystal Controlled Oscillator**

20143239

20143236

## **Typical Applications** (V<sup>+</sup>=5.0 V<sub>DC</sub>) (Continued)

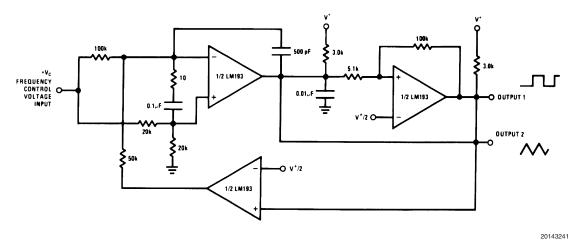

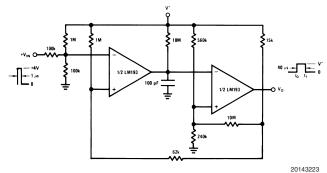

#### Two-Decade High Frequency VCO

$V^{\star} = +30 \ V_{DC}$   $+250 \ mV_{DC} \leq V_{C} \leq +50 \ V_{DC}$   $700Hz \leq f_{o} \leq 100kHz$

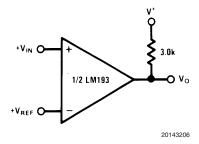

#### **Basic Comparator**

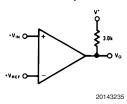

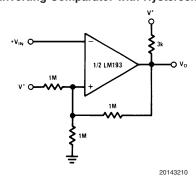

#### **Inverting Comparator with Hysteresis**

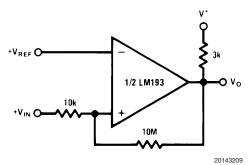

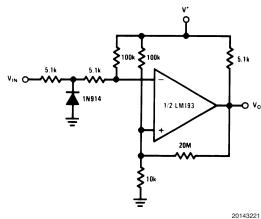

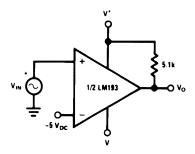

#### Non-Inverting Comparator with Hysteresis

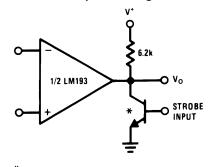

#### **Output Strobing**

\* OR LOGIC GATE

WITHOUT PULL-UP RESISTOR

20143211

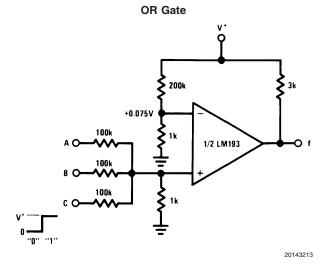

## Typical Applications (V $^+$ =5.0 V $_{DC}$ ) (Continued)

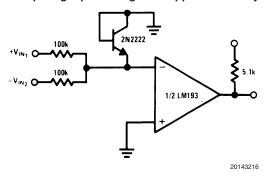

# AND Gate V 100k 100k

Large Fan-in AND Gate

20143212

100k 1/2 LM193 V<sub>OUT</sub>

100k 1/2 LM193 V<sub>OUT</sub>

100k 1/2 LM193 V<sub>OUT</sub>

100k 1/2 LM193 V<sub>OUT</sub>

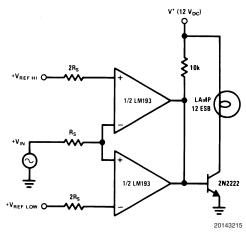

**Limit Comparator**

**Comparing Input Voltages of Opposite Polarity**

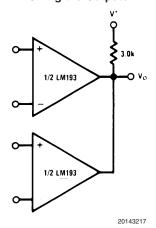

**ORing the Outputs**

# Typical Applications (V+=5.0 $V_{DC}$ ) (Continued)

#### **Zero Crossing Detector (Single Power Supply)**

**Zero Crossing Detector**

20143243

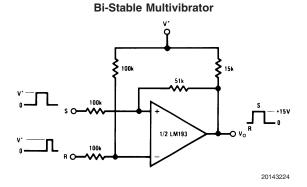

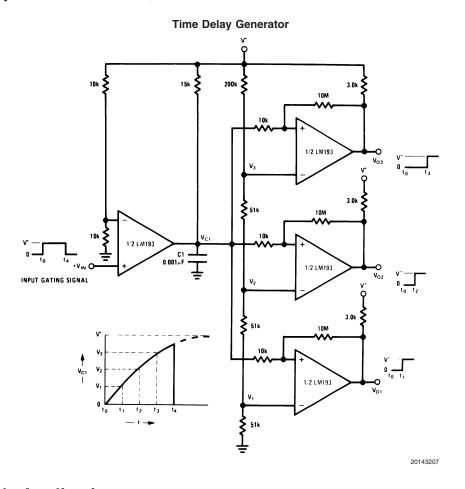

#### **One-Shot Multivibrator**

One-Shot Multivibrator with Input Lock Out

#### **Comparator With a Negative Reference**

# Typical Applications (V+=5.0 $V_{DC}$ ) (Continued)

# Split-Supply Applications $(V^+=+15\ V_{DC}\ and\ V^-=-15\ V_{DC})$

#### **MOS Clock Driver**

20143242

# Revision History Section Date Released Revision Section Originator Changes 05/09/05 A New Release. Corporate format L. Lytle 1 MDS datasheets converted into one Corp. datasheet format. DC Drift table was deleted due to no JANS product offerings. MJLM193-X Rev 1A1 MDS will be archived.

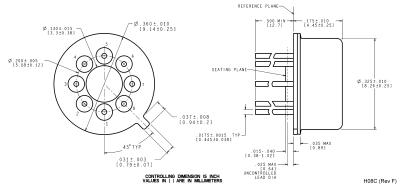

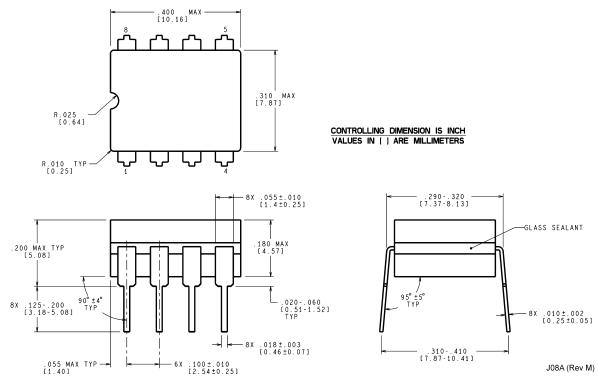

#### Physical Dimensions inches (millimeters) unless otherwise noted

Metal Can Package (H) NS Package Number H08C

Ceramic Dual-In-Line Package NS Package Number J08A

#### **Notes**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560