# PULSE DIALER WITH REDIAL

The KK5851 is a monolithic CMOS integrated circuit which uses an inexpensive RC oscillator for its frequency reference and provides all the features required for implementing a pulse dialer with 32 digit redial.

- Wide operating voltage range (2.0~6.0V)

- Low power dissipation

- Use either a standard 2 of 7 matrix keyboard with negative true common or the inexpensive form A-type keyboard

- Make/Break ratio can be selected

- Redial with <u>\* or #</u>

- Continuous MUTE

- Power up clear circuitry on chip

- 10 pps/20 pps can be selected

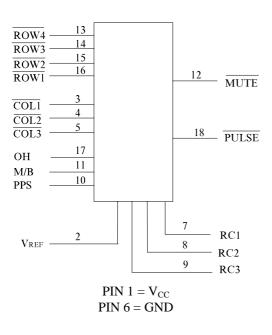

#### LOGIC DIAGRAM

#### PIN ASSIGNMENT

| V <sub>CC</sub> [1•               | 18 PULSE                            |

|-----------------------------------|-------------------------------------|

| $V_{REF}$ 2                       | 17 🗌 OH                             |

| $\overline{\text{COL1}}$ $\Box$ 3 | 16 $\Box \overline{ROW}1$           |

| $\overline{\text{COL2}}$ 4        | 15 $\Box$ ROW2                      |

| $\overline{\text{COL3}}$ [ 5      | 14 $\Box \overline{\text{ROW}}3$    |

| GND 🛛 6                           | 13 $\Box \overline{\text{ROW4}}$    |

| RC1 🛛 7                           | $12 \square \overline{\text{MUTE}}$ |

| RC2 [ 8                           | 11 🗌 M/B                            |

| RC3 [ 9                           | 10 🗌 PPS                            |

|                                   |                                     |

# KK5851

## **PIN DESCRIPTION**

| NAME                                      | PIN                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>CC</sub>                           | 1                     | Positive supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                           |                       | The voltage on this pin is measured relative to Pin 6 and is supplied from a $150\mu A$ current source. This voltage should be regulated to less than 6.0 volts using on external form or regulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| V <sub>REF</sub>                          | 2                     | The V <sub>REF</sub> output provides reference .<br>voltage that tracks internal<br>parameters of the KK5851N. V <sub>REF</sub><br>provides a negative voltage reference<br>to the V <sub>CC</sub> supply. Its magnitude will<br>be approximately 0.6 volt higher than<br>the minimum operating voltage of<br>each particular KK5851N.<br>The typical application would be to<br>connect the V <sub>REF</sub> pin to the GND pin<br>(Pin 1) should then be regulated to<br>150 $\mu$ A (I <sub>OP</sub> max). with this amount of<br>supply current, operation of the<br>KK851N is guaranteed.<br>The internal circuit of the V <sub>REF</sub><br>function is shown in Figure 1 with its<br>associated I-V characteristic |  |  |

|                                           | 2 4 5 1 2             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| R <u>ow1</u> - <u>Row</u> 4,<br>Col1-Col4 | 3,4,5,13,<br>14,15,16 | Keyboard inputs.<br>The KK5851N incorporates an innovative keyboard scheme that allows either the standard 2-of-7 keyboard with negative common or the inexpensive single contact (form A) keyboard to be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                           |                       | A valid key entry is defined by either a single row being connected to a single column or GND being simultaneously presented to both a single row and column. When in the on-hook mode, the row and column inputs are held high and no keyboard inputs are accepted.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                           |                       | When off-hook, the keyboard is completely static until the initial valid key input<br>is sensed. The oscillator is then enabled and the rows and columns are scanned<br>alternately (pulled high, then low) to verify the varied input. The input must<br>remain valid for 10msec of debounce time to be accepted.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                           |                       | Form A type keyboard 2 of 7 keyboard (negative common)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                           |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                           |                       | 2 of 7 keyboard Electronic input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                                           |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                           |                       | COL Vcc COL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                                           |                       | Vcc<br>GND ROW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                           |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|         |       | pin is connected                                                                                                                                                                                                                                                                                                                                                                               | l to the common                                                               | part in general                | applications.                                         |                 |

|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------|-----------------|

| RC1-RC3 | 7,8,9 | Oscillator                                                                                                                                                                                                                                                                                                                                                                                     |                                                                               |                                |                                                       |                 |

|         | , ,   | The KK5851N contains on-chip inverters to provide oscillator which will operate with a minimum external components.                                                                                                                                                                                                                                                                            |                                                                               |                                |                                                       | ch will operate |

|         |       | Following figure shows the on-chip configuration with the necessary external components. Optimum stability occurs with the ration $K=R_s/R$ equal to 10                                                                                                                                                                                                                                        |                                                                               |                                |                                                       |                 |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                | eriod is given by                                                             |                                | ration K=Kg/K equa                                    |                 |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                | 3.5KC <sub>s</sub> )/C-(2K/(                                                  |                                | 5K + 0.5)                                             |                 |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                | stray capacitance                                                             |                                | SIX + 0.5))                                           |                 |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               |                                | is capacitance minii                                  | mized.          |

|         |       | 5                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                                             | $\langle$                      |                                                       | 4               |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               | 7<br>= Cs<br><del>-</del><br>8 | IN5851N                                               |                 |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                | R                                                                             | 9                              |                                                       |                 |

| PPS     | 10    | 10/20pps Select                                                                                                                                                                                                                                                                                                                                                                                | ţ                                                                             |                                |                                                       |                 |

|         |       | Connecting this                                                                                                                                                                                                                                                                                                                                                                                | Connecting this pin to GND (pin 6) will select an output pulse rate of 10pps. |                                |                                                       |                 |

|         |       | Connecting the                                                                                                                                                                                                                                                                                                                                                                                 | pin V <sub>CC</sub> (pin 1)                                                   | will select an ou              | tput pulse rate of 20                                 | Opps.           |

| M/B     | 11    | Make/break Sel                                                                                                                                                                                                                                                                                                                                                                                 | ect                                                                           |                                |                                                       |                 |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                | io is controlled b                                                            |                                | k ratio of the puls<br><sub>CC</sub> or GND to this p |                 |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                | Input                                                                         | Make                           | Break                                                 |                 |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CC</sub> (Pin1)                                                        | 33.4%                          | 66.6%                                                 |                 |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                | GND(PIn 6)                                                                    | 40%                            | 60%                                                   |                 |

|         | 12    | Mute Output                                                                                                                                                                                                                                                                                                                                                                                    |                                                                               | •                              |                                                       |                 |

| Mute    |       | The mute output bipolar transister                                                                                                                                                                                                                                                                                                                                                             |                                                                               | n N-Channel tr                 | ansistor designed to                                  | drive external  |

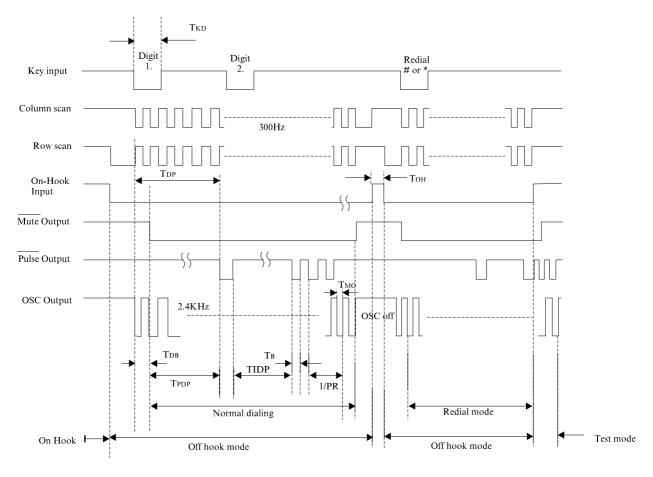

|         |       | This circuitry is usually <u>used</u> to mute the receiver during outpulsing. As shown in Fig. 2 the KK5851N mute output turns on (pulls to the $V_{GND}$ -supply) at the beginning of the predigital pause and turns off (goes to an open circuit) following the last break.                                                                                                                  |                                                                               |                                |                                                       |                 |

|         |       | The delay from the end of the last break until the mute output turns off is mute overlap and is specified as $t_{MO}$ .                                                                                                                                                                                                                                                                        |                                                                               |                                |                                                       |                 |

| ОН      | 17    | ON-HOOK/TE                                                                                                                                                                                                                                                                                                                                                                                     | ON-HOOK/TEST                                                                  |                                |                                                       |                 |

|         |       | This pin detects the state of the hook switch contact "OFF HOOK" corresponds to $V_{SS}$ condition. ÖN HOOK" corresponds to $V_{DD}$ condition. When outpulsing in this mode, which can be up to 300msec, is completed, the circuit is deactivated and will require current only necessary to sustain the memory and power-up-clear detect circuitry (refer to the electrical specifications). |                                                                               |                                |                                                       |                 |

|         |       |                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                             |                                | on the mute output<br>irst key entry is eith          |                 |

|       |    | number sequence stored on-chip will be outpulsed. Any other valid key entries will clear the memory and outpulse the new number sequence.                                                                                                                                                                                |

|-------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 18 | Pulse Output                                                                                                                                                                                                                                                                                                             |

| PULSE |    | The Pulse output is an open drain N-channel transistor designed to drive external bipolar transistor. These transistor would normally be used to pulse the telephone line by disconnecting and connecting the network. The KK5851N pulse output is an open circuit during make and pulls to the GND supply during break. |

### MAXIMUM RATINGS\*

| Symbol                   | Parameter                                                   | Value       | Unit |

|--------------------------|-------------------------------------------------------------|-------------|------|

| V <sub>CC</sub>          | V <sub>CC</sub> DC Supply Voltage (Referenced to GND)       |             | V    |

| V <sub>IN</sub>          | V <sub>IN</sub> DC Input Voltage (Referenced to GND)        |             | V    |

| P <sub>D</sub>           | P <sub>D</sub> Power Dissipation in Still Air <sup>**</sup> |             | mW   |

| Tstg Storage Temperature |                                                             | -40 to +125 | °C   |

\* Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the Recommended Operating Conditions.

\* Derating:  $-10^{\text{ mW}}/_{\circ \text{C}}$  from 65°C to 70°C.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter                             |  | Max             | Unit |

|-----------------|---------------------------------------|--|-----------------|------|

| V <sub>CC</sub> | DC Supply Voltage (Referenced to GND) |  | 6.0             | V    |

| $V_{\rm IN}$    | DC Input Voltage (Referenced to GND)  |  | V <sub>CC</sub> | V    |

| T <sub>A</sub>  | T <sub>A</sub> Operating Temperature  |  | +70             | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation,  $V_{IN}$  and  $V_{OUT}$  should be constrained to the range  $GND \leq (V_{IN} \text{ or } V_{OUT}) \leq V_{CC}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or  $V_{CC}$ ). Unused outputs must be left open.

## **DC ELECTRICAL CHARACTERISTICS**(Voltages Referenced to GND, $V_{CC} = 2.0$ V to 6.0V,

$T_A = -20$  to  $+70^{\circ}C$ ,  $F_{OSC}=2.4$ KHz)

|                  |                                     |                                                        | Gua         | ranteed L | limits          |      |

|------------------|-------------------------------------|--------------------------------------------------------|-------------|-----------|-----------------|------|

| Symbol           | Parameter                           | Test Conditions                                        | Min         | Тур       | Max             | Unit |

| V <sub>IH</sub>  | Input High Voltage                  |                                                        | $0.8V_{CC}$ |           | V <sub>CC</sub> | V    |

| V <sub>IL</sub>  | Input Low Voltage                   |                                                        | 0           |           | $0.2V_{CC}$     | V    |

| V <sub>DR</sub>  | Minimum Memory<br>Retention Voltage |                                                        | 1.0         |           |                 | V    |

| I <sub>OL</sub>  | Output Leakage Current              | <u>V<sub>CC</sub>=</u> 6. <u>0V</u><br>MUTE,PULSE=6.0V |             |           | 1               | μΑ   |

| I <sub>OL1</sub> | Minimum Output current              | V <sub>0</sub> =0.8V,V <sub>CC</sub> =2.5V             | 0.5         |           |                 | mA   |

|                  | (MUTE,PULSE)                        |                                                        |             |           |                 |      |

| I <sub>OL2</sub> | Minimum Output current              | $V_0 = 0.8V, V_{CC} = 3.5V$                            | 1.7         |           |                 | mA   |

|                  | (MUTE,PULSE)                        |                                                        |             |           |                 |      |

| I <sub>OD</sub>  | Operating Current                   | All output under no load, $V_{CC}=2.0V$                |             |           | 150             | μΑ   |

| I <sub>SD</sub>  | Maximum Standby<br>Current          | V <sub>CC</sub> =2.5V<br>V <sub>IH</sub> =2.5V         |             |           | 1               | μΑ   |

| I <sub>REF</sub> | Minimum Reference<br>Current        | V <sub>CC</sub> =6.0V                                  | 1           |           |                 | μΑ   |

### AC ELECTRICAL CHARACTERISTICS (Fosc= 2.4 KHz, V\_{CC}=2.0 to 6.0 V, T\_A=-20 to +70 ^{\circ}C)

| Symbol           | Parameter        | Test Conditions | Guaranteed Limit |      | Unit |                     |

|------------------|------------------|-----------------|------------------|------|------|---------------------|

| -                |                  |                 | Min.             | Тур. | Max  | ]                   |

| T <sub>KD</sub>  | Minimum Valid    |                 | 20               |      |      | mS                  |

|                  | Key Entry Time   |                 |                  |      |      |                     |

| T <sub>OH</sub>  | On Hook Time     |                 | 300              |      |      | mS                  |

|                  | Required to      |                 |                  |      |      |                     |

|                  | Clear Memory     |                 |                  |      |      |                     |

|                  | (Figure 2)       |                 |                  |      |      |                     |

| T <sub>IDR</sub> | Inter Digital    |                 |                  | 800  |      | mS                  |

|                  | Pause (Figure 2) |                 |                  |      |      |                     |

| $\Delta f$       | Frequency        |                 |                  | ±10  |      | %                   |

|                  | Sability         |                 |                  |      |      |                     |

| $T_{MO}$         | Recovery Time,   |                 |                  | 800  |      | mS                  |

|                  | MUTE to          |                 |                  |      |      |                     |

|                  | PULSE            |                 |                  |      |      |                     |

|                  | (Figure 2)       |                 |                  |      |      |                     |

| $T_{PDP}$        | Maximum Pre-     |                 |                  |      | 30   | mS                  |

|                  | digital Pause    |                 |                  |      |      |                     |

|                  | (Figure 2)       |                 |                  |      |      |                     |

| T <sub>DP</sub>  | Maximum Delay    |                 |                  |      | 50   | mS                  |

|                  | Time, Key Input  |                 |                  |      |      |                     |

|                  | to PULSE         |                 |                  |      |      |                     |

|                  | (Figure 2)       |                 |                  |      |      |                     |

| M/B              | Make/Break       |                 |                  | 1/2  |      | M/B=V <sub>CC</sub> |

|                  | Ratio            |                 |                  | 2/3  |      | M/B=GND             |

#### TIMING DIAGRAMM

Figure 2

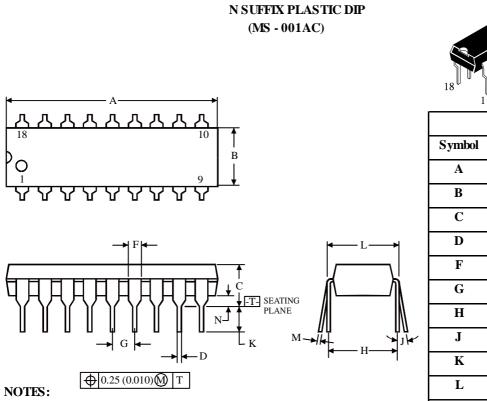

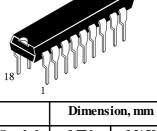

1. Dimensions "A", "B" do not include mold flash or protrusions.

Maximum mold flash or protrusions 0.25 mm (0.010) per side.

|        | Dimension, min |       |  |

|--------|----------------|-------|--|

| Symbol | MIN            | MAX   |  |

| Α      | 22.35          | 23.37 |  |

| В      | 6.1            | 7.11  |  |

| С      |                | 5.33  |  |

| D      | 0.36           | 0.56  |  |

| F      | 1.14           | 1.78  |  |

| G      | 2.54           |       |  |

| Н      | 7.             | 62    |  |

| J      | 0°             | 10°   |  |

| K      | 2.92           | 3.81  |  |

| L      | 7.62           | 8.26  |  |

| Μ      | 0.2 0.36       |       |  |

| Ν      | 0.38           |       |  |