# Oki, Network Solutions for a Global Society

## **OKI Semiconductor**

FEDL2500BFULL-02

Issue Date: Aug.9, 2004

# ML2500BTA

Analog-Storage Single-chip Record/Playback LSI with 1M Bit-Cell Flash Memory

#### **GENERAL DESCRIPTION**

Thanks to newly developed Analog Multi-Level Storage technology, ML2500B stores non-compressed analog source signal directly into on-chip 1M Bit-Cell Flash memory. The result is superb sound quality without noise and distortions introduced through coding/decoding, and impressive long-time record/playback capability up to 256 sec. ML2500B is fully controllable by an external MCU via the industry's standard Serial Peripheral Interface.

In addition, no backup requirement and low operating voltage (2.7 to 3.3 V) make the LSI an ideal choice for compact, handy and portable terminals. ML2500B is a true single-chip solution to record/playback subsystem for use with today's size-critical electronic products.

#### DIFFERENCES BETWEEN THE ML2500BTA AND THE ML2500TA

|                       | ML2500BTA                             | ML2500TA                              |

|-----------------------|---------------------------------------|---------------------------------------|

| Operating Temperature | Ta = -40 to +70°C                     | Ta = -10 to +70°C                     |

| Pin Symbol            | Pin 10: TEST2                         | Pin 10: NC                            |

| AC Characteristic     | DI hold time t <sub>DIH</sub> = 30 ns | DI hold time t <sub>DIH</sub> = 20 ns |

#### **FEATURES**

•On-chip non-volatile 1M bit-cell Flash memory

Program/Erase Cycles: 10,000 cycles

Data Retention: 10 years

•MCU Interface

Serial Peripheral Interface (SPI; Mode 0)

•Record/Playback Time Length (With the int. Osc. or ext. clock at 8.192 MHz)

Approx. 160 sec (At fsam = 6.4 kHz) Approx. 190 sec (At fsam = 5.3 kHz) Approx. 256 sec (At fsam = 4.0 kHz)

•Selectable Sampling Frequencies

4.0 kHz, 5.3 kHz, 6.4 kHz

- •Maximum number of recording phrases: 320 phrases

- •Phrase Control

Fully controllable with user-definable Start, Stop addresses

- •Built-in LPF/Smoothing Filter (LPF attenuation –40 dB/oct)

- •Built-in Oscillation Circuit (8.192 MHz), No oscillator required

Optional external clock input (Clock Frequency 4.0 to 8.192 MHz)

•Power Supply : 2.7 to 3.3 V

•Operating Temperature:

-40 to +70°C (guaranteed for both function and voice quality)

-40 to +85°C (guaranteed for function only) \*Notice

\*Notice

The voice quality can deteriorate at temperatures beyond the range of -40 to +70°C.

DC and AC characteristics in this data sheet are specified for -40 to +70°C operating temperature range.

•Package:

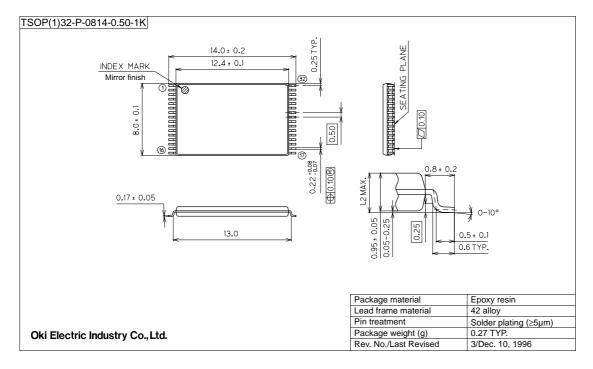

32-pin Plastic TSOP (TSOP(1)32-P-814-0.50-1K) (Product name: ML2500BTA)

Note: Please contact the Oki Sales office/Distributors for bare chips.

## CONTENTS

| GENERAL DESCRIPTION                                               | 1  |  |  |  |  |

|-------------------------------------------------------------------|----|--|--|--|--|

| FEATURES                                                          | 1  |  |  |  |  |

| BLOCK DIAGRAM                                                     | 3  |  |  |  |  |

| YIN CONFIGURATION                                                 |    |  |  |  |  |

| PIN DESCRIPTIONS                                                  | 4  |  |  |  |  |

| ABSOLUTE MAXIMUM RATINGS                                          | 5  |  |  |  |  |

| RECOMMENDED OPERATING CONDITIONS                                  | 5  |  |  |  |  |

| ELECTRICAL CHARACTERISTICS                                        | 5  |  |  |  |  |

| DC Characteristics                                                | 5  |  |  |  |  |

| Analog Characteristics                                            | 6  |  |  |  |  |

| AC Characteristics 1                                              | 7  |  |  |  |  |

| AC Characteristics 2                                              | 8  |  |  |  |  |

| TIMING DIAGRAM                                                    |    |  |  |  |  |

| Serial Peripheral Interface (SPI) AC Characteristics Timing Chart |    |  |  |  |  |

| Operational Timing at Power-On                                    |    |  |  |  |  |

| Timing for Power Up and Power Down Operations                     |    |  |  |  |  |

| Timing for Record/Playback Operation                              |    |  |  |  |  |

| Timing for Recording Operation                                    |    |  |  |  |  |

| 2. Timing for Playback Operation                                  |    |  |  |  |  |

| 3. Timing for Pausing Operation by the PAUSE Command              |    |  |  |  |  |

| FUNCTIONAL DESCRIPTION                                            |    |  |  |  |  |

| Serial Peripheral Interface (SPI)                                 |    |  |  |  |  |

| 1. Timing for Writing Command Data                                |    |  |  |  |  |

| 2. Timings for Reading out Status Data                            |    |  |  |  |  |

| Control Commands                                                  |    |  |  |  |  |

| Control Commands-Recording                                        |    |  |  |  |  |

| Control Commands-Playback                                         |    |  |  |  |  |

| 3. The List of Control Commands                                   |    |  |  |  |  |

| Addressable Memory Space for Recording                            |    |  |  |  |  |

| Address Control                                                   |    |  |  |  |  |

| 1. Address Control for Recording                                  |    |  |  |  |  |

| 2. Address Control for Playback                                   |    |  |  |  |  |

| LPF Cheracteristics                                               |    |  |  |  |  |

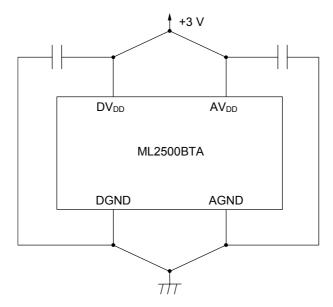

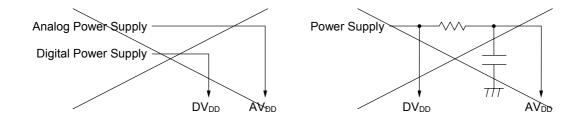

| Power Supply Circuit Design                                       |    |  |  |  |  |

| LOUT Output Voltage Range Allowance                               |    |  |  |  |  |

| States of Output Pins during Power Down                           |    |  |  |  |  |

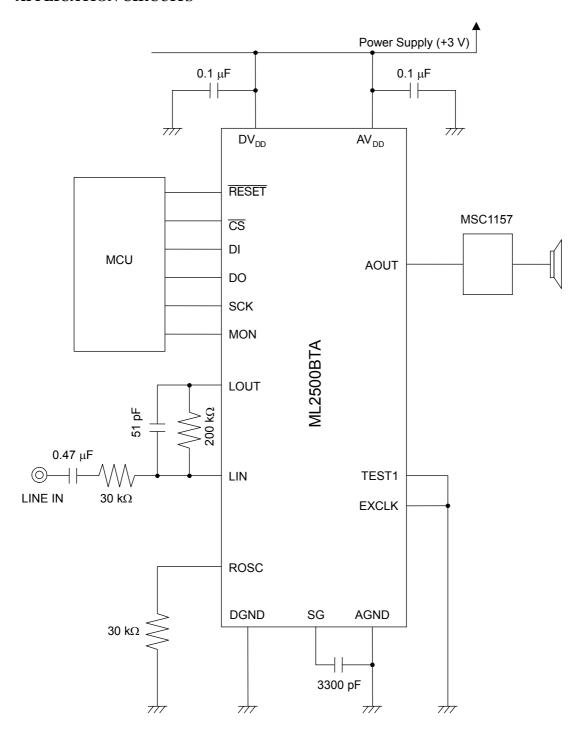

| APPLICATION CIRCUITS                                              |    |  |  |  |  |

| DACKAGE DIMENSIONS                                                | 25 |  |  |  |  |

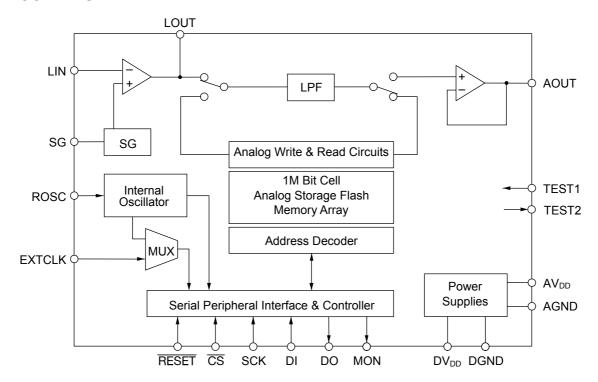

#### **BLOCK DIAGRAM**

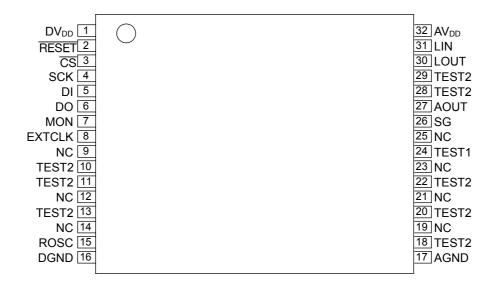

## PIN CONFIGURATION (TOP VIEW)

NC: No connection. Keep NC pins open.

32-Pin Plastic TSOP (Type 1)

## PIN DESCRIPTIONS

| Pin                                  | Symbol        | Туре | Description                                                                                                                                                                                                                                            |

|--------------------------------------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5                                    | DI            | I    | Serial input pin for command data.                                                                                                                                                                                                                     |

| 6                                    | DO            | 0    | Serial output pin for status data.                                                                                                                                                                                                                     |

| 4                                    | SCK           | I    | Shift clock input pin for the DI and the DO pins.                                                                                                                                                                                                      |

| 3                                    | <del>CS</del> | I    | Chip select pin. "L" level input enables data input/output through the serial interface.                                                                                                                                                               |

| 2                                    | RESET         | I    | RESET input pin, resetting the serial interface circuit only. "L" level input to this pin initializes the serial interface. Must input "L" pulse after each power-on.                                                                                  |

| 15                                   | ROSC          | I    | Insert a 30 k $\Omega$ resistor (Precision within ±1%) between this pin and the DGND pin. The same resistor should also be inserted if an external clock is used. The resistor value determines the frequency of the clock for control in this device. |

| 8                                    | EXTCLK        | I    | External clock input pin. Allowable clock frequency range is 4.0 to 8.192 MHz. When external clock is unused and internal oscillation clock is used, connect this pin to the DGND.                                                                     |

| 7                                    | MON           | 0    | Output "H" level during recording/playback operation.                                                                                                                                                                                                  |

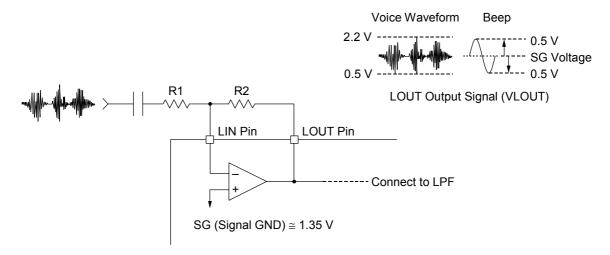

| 26                                   | SG            | 0    | Analog reference voltage (Signal Ground Voltage) output pin. It is recommendable to insert a capacitor of 3300 pF or less between this pin and the AGND pin. Loads except for capacitors should not be connected to this pin.                          |

| 31                                   | LIN           | I    | Inverting input pin for the internal OP amplifier. Non-inverting input pin is internally connected to SG voltage.                                                                                                                                      |

| 30                                   | LOUT          | 0    | Output pin from the internal OP amplifier.                                                                                                                                                                                                             |

| 27                                   | AOUT          | 0    | Analog waveform output. Connect to an amplifier to drive a SP.                                                                                                                                                                                         |

| 10, 11, 13,<br>18, 20, 22,<br>28, 29 | TEST2         | 0    | Pins for testing the LSI. Must be held "OPEN".                                                                                                                                                                                                         |

| 24                                   | TEST1         | I    | LSI's testing pin. Must be connected to DGND.                                                                                                                                                                                                          |

| 1                                    | $DV_{DD}$     | _    | Digital power supply pin. Insert a 0.1 $\mu F$ or larger by-pass capacitor between this pin and the DGND pin.                                                                                                                                          |

| 16                                   | DGND          | _    | Digital Ground pin                                                                                                                                                                                                                                     |

| 32                                   | $AV_DD$       |      | Analog power supply pin. Insert a 0.1 $\mu F$ or larger by-pass capacitor between this pin and the AGND pin.                                                                                                                                           |

| 17                                   | AGND          | _    | Analog Ground pin                                                                                                                                                                                                                                      |

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol           | Condition | Rating                       | Unit |

|----------------------|------------------|-----------|------------------------------|------|

| Power Supply Voltage | $V_{DD}$         | Ta = 25°C | -0.3 to +5.0                 | V    |

| Input Voltage        | V <sub>IN</sub>  | 1a = 25 C | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Storage Temperature  | T <sub>STG</sub> | _         | -55 to +150                  | °C   |

## RECOMMENDED OPERATING CONDITIONS

| Parameter                     | Symbol               | Condition         | Range           |       | Unit |     |

|-------------------------------|----------------------|-------------------|-----------------|-------|------|-----|

| Power Supply Voltage          | $V_{DD}$             | DGND = AGND = 0 V | 2.7 to 3.3      |       | V    |     |

| Operating Temperature         | T <sub>op</sub>      | _                 | -40 to +70      |       | °C   |     |

|                               |                      |                   | Min.            | Тур.  | Max. |     |

| External Clock Frequency 1 *1 | f <sub>EXTCLK1</sub> | _                 | 3.85            | 4.096 | 4.34 | MHz |

| External Clock Frequency 2 *1 | f <sub>EXTCLK2</sub> | _                 | 7.70 8.192 8.68 |       | MHz  |     |

<sup>\*1:</sup> Applicable only with external clock

## **ELECTRICAL CHARACTERISTICS**

### **DC** Characteristics

$DV_{DD} = AV_{DD} = 2.7 \text{ to } 3.3 \text{ V}, DGND = AGND = 0 \text{ V}, Ta = -40 \text{ to } +70^{\circ}\text{C}$

| Donous etc.                     |                                 | 0                | ·                      |                      | ı    | NA                         | 11:4 |

|---------------------------------|---------------------------------|------------------|------------------------|----------------------|------|----------------------------|------|

| Parameter                       |                                 | Symbol           | Condition              | Min.                 | Тур. | Max.                       | Unit |

| "H" Input Voltage               | *1                              | V <sub>IH</sub>  | DGND = AGND = 0 V      | $0.8 \times V_{DD}$  | _    | _                          | V    |

| "L" Input Voltage               | *1                              | $V_{IL}$         | _                      |                      | _    | $0.2 \times V_{\text{DD}}$ | V    |

| "H" Output Voltage              | *2                              | $V_{OH}$         | $I_{OH} = -40 \mu A$   | V <sub>DD</sub> -0.3 | _    | _                          | V    |

| "L" Output Voltage              | *2                              | V <sub>OL</sub>  | I <sub>OL</sub> = 2 mA |                      | _    | 0.45                       | V    |

| "H" Input Current               | *1                              | I <sub>IH</sub>  | $V_{IH} = V_{DD}$      |                      | _    | 10                         | μΑ   |

| "L" Input Current               | *1                              | I <sub>IL</sub>  | V <sub>IL</sub> = 0 V  | -10                  | _    | _                          | μΑ   |

| Operating Current Consump       | Operating Current Consumption 1 |                  | In Recording Operation |                      | 30   | 45                         | mA   |

| Operating Current Consumption 2 |                                 | I <sub>DD2</sub> | In Playback Operation  | 1                    | 20   | 30                         | mA   |

| Operating Current Consumption 3 |                                 | I <sub>DD3</sub> | In Command-Wait State  |                      | 5    | 10                         | mA   |

| Powerdown Current Consun        | nption                          | I <sub>DDS</sub> | <u> </u>               |                      | _    | 10                         | μА   |

<sup>\*1:</sup> Applied to logic input pins (DI, SCK,  $\overline{\text{CS}}$ ,  $\overline{\text{RESET}}$  and EXTCLK) except ROSC and TEST1 pins. \*2: Applied to logic output pins (DO and MON) except TEST2 pin.

## **Analog Characteristics**

$DV_{DD}$  =  $AV_{DD}$  = 2.7 to 3.3 V, DGND = AGND = 0 V, Ta = -40 to  $+70^{\circ}C$

| Parameter                | r             | Symbol            | Condition                  | Min. | Тур. | Max. | Unit |

|--------------------------|---------------|-------------------|----------------------------|------|------|------|------|

| LIN Input Impedance      | *1            | $R_{LIN}$         | _                          | 1    | _    | _    | МΩ   |

| Input OP. Amplifier Oper | n Loop Gain*2 | $G_OP$            | $f_{IN} = 0$ to 4 kHz      | 40   |      | _    | dB   |

| LOUT Load Resistance     | *3            | R <sub>LOUT</sub> | _                          | 200  |      | _    | kΩ   |

| AOUT Load Resistance     | *4            | R <sub>AOUT</sub> | _                          | 50   | _    | _    | kΩ   |

| LOUT Output Voltage      | Voice voltage | \/                | _                          | 0.5  | _    | 2.2  | V    |

| Allowance *5             | Beep voltage  | $V_{LOUT}$        | With respect to SG voltage | -0.5 | _    | +0.5 | V    |

<sup>\*1:</sup> Applied to LIN pin.

\*2: Applied to LIN and LOUT pins.

\*3: Applied to LOUT pin.

\*4: Applied to AOUT pin.

<sup>\*5:</sup> Refer to "LOUT Output Voltage Range Allowance" section.

## **AC Characteristics 1**

$DV_{DD} = AV_{DD} = 2.7 \text{ to } 3.3 \text{ V}, DGND = AGND = 0 \text{ V}, Ta = -40 \text{ to } +70^{\circ}\text{C}$

| Parame                                                            | ator                                                           | Symbol             | = $AV_{DD}$ = 2.7 to 3.3 V, Definition                  | Min. | Typ.                                        | a = -40<br>Max. | Unit |  |

|-------------------------------------------------------------------|----------------------------------------------------------------|--------------------|---------------------------------------------------------|------|---------------------------------------------|-----------------|------|--|

| -                                                                 |                                                                |                    | Condition                                               | 40   | 50                                          | 60              | %    |  |

| External Clock Duty C<br>RESET Pulse Width                        | - Jycie                                                        | f <sub>duty</sub>  | _                                                       | 1    | 50                                          | 00              |      |  |

|                                                                   |                                                                | t <sub>RST</sub>   | _                                                       | I    | _                                           | 1               | μS   |  |

| Powering up time Power-down Shift Tim                             | o offer DDWN                                                   | t <sub>PWUP</sub>  | _                                                       | _    | _                                           | 1               | ms   |  |

| Command Input                                                     | ie aiter PDVVN                                                 | t <sub>PDWN</sub>  | _                                                       | _    | _                                           | 100             | μS   |  |

| Power-down Shift Time to RESET pin                                | ne after "L" Input                                             | t <sub>PDWNR</sub> | _                                                       | _    | _                                           | 100             | μS   |  |

| CS "L" Level Pulse W Power-down Reset                             | idth for                                                       | t <sub>CSWL</sub>  | _                                                       | 1    | _                                           | _               | μS   |  |

| MON Rising Time after Command Input                               | er REC<br>*1                                                   | t <sub>RECM</sub>  | At fsam = 6.4 kHz                                       | _    | _                                           | 165             | μS   |  |

| RPM Rising Time afte<br>Input                                     | r REC Command                                                  | t <sub>RECR</sub>  | _                                                       | _    | _                                           | 220             | ms   |  |

| MON Rising Time after Command Input                               | er PLAY                                                        | t <sub>PLYM</sub>  | _                                                       | _    | _                                           | 11              | ms   |  |

| RPM Rising Time after Command Input                               | er PLAY                                                        | t <sub>PLYR</sub>  | _                                                       | _    | _                                           | 11              | ms   |  |

|                                                                   |                                                                |                    | At fsam = 4.0 kHz                                       | _    | _                                           | 305             |      |  |

| MON Falling Time<br>after STOP                                    | At REC                                                         | t <sub>SPCM</sub>  | At fsam = 5.3 kHz                                       | _    | _                                           | 280             | ms   |  |

| Command Input                                                     |                                                                |                    | At fsam = 6.4 kHz                                       | _    | _                                           | 266             |      |  |

| Command Impac                                                     | At PLAY *1                                                     | t <sub>SPCM</sub>  | At fsam = 6.4 kHz                                       | _    | _                                           | 165             | μS   |  |

|                                                                   |                                                                |                    | At fsam = 4.0 kHz                                       | _    | _                                           | 305             |      |  |

| RPM Falling Time<br>after STOP                                    | At REC                                                         | tspcr              | At fsam = 5.3 kHz                                       | _    | _                                           | 280             | ms   |  |

| Command Input                                                     |                                                                |                    | At fsam = 6.4 kHz                                       | _    | _                                           | 266             |      |  |

| Command input                                                     | At PLAY *1                                                     | tspcr              | At fsam = 6.4 kHz                                       | _    | _                                           | 165             | μS   |  |

| VPM Bit Rising Time Command Input                                 | after PAUSE<br>*1                                              | t <sub>PSCP</sub>  | At fsam = 6.4 kHz                                       | _    | _                                           | 165             | μS   |  |

|                                                                   | VPM Bit Reset Time after PAUSE Command Input, while Pausing *1 |                    | At fsam = 6.4 kHz                                       | _    | _                                           | 165             | μS   |  |

| VPM Bit Reset Time after STOP Command Input, while Pausing *1     |                                                                | t <sub>SPCP2</sub> | At fsam = 6.4 kHz                                       | _    | _                                           | 165             | μS   |  |

| Complian Francisco                                                | Absolute Error                                                 | $\Delta f_{sam1}$  | $Ta = 25^{\circ}C,$ $DV_{DD} = AV_{DD} = 3.0 \text{ V}$ | -3.0 | Defined<br>Frequency                        | +3.0            |      |  |

| Sampling Frequency<br>Error When internal<br>oscillation clock is | V <sub>DD</sub> Variation<br>Error                             | $\Delta f_{sam2}$  | Ta = 25°C, DV <sub>DD</sub> = $AV_{DD}$ = 2.7 to 3.0 V  | -6.0 | Defined<br>Frequency                        | +6.0            | %    |  |

| used *2                                                           | Temperature<br>Variation Error                                 | $\Delta f_{sam3}$  | Ta = -40 to +70°C                                       | -3.0 | Defined<br>Frequency<br>+∆f <sub>sam2</sub> | +3.0            |      |  |

<sup>\*1:</sup> The value changes in proportion to the sampling frequency selected. \*2: When a 30 k $\Omega$  resistor is used between ROSC and DGND pins.

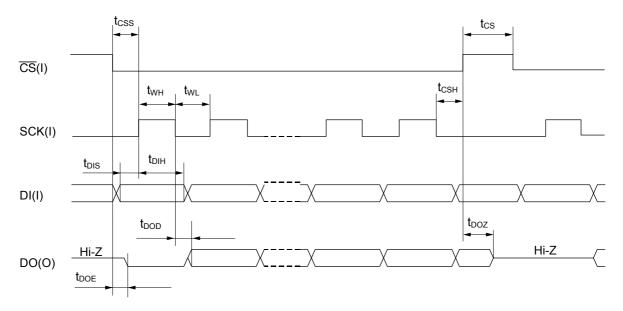

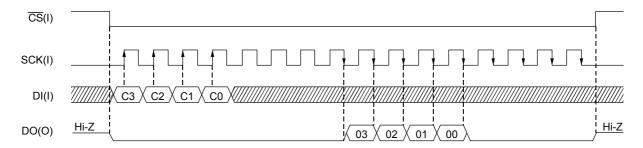

## **AC Characteristics 2**

| $DV_{DD} = AV_{DD} = 2.$ | 7 to 3 3 V  | DGND =                                  | AGND =     | 0 V | Ta = -  | 40 to +70°0 | 3 |

|--------------------------|-------------|-----------------------------------------|------------|-----|---------|-------------|---|

|                          | 1 LO O.O V. | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | / (OI 1D - | U V | , I u – | 70 10 170 1 | _ |

| Parameter                         | Symbol           | Condition | Min. | Тур. | Max. | Unit |

|-----------------------------------|------------------|-----------|------|------|------|------|

| <del>CS</del> ↓ – SCK↑ Setup Time | t <sub>CSS</sub> | _         | 100  | _    | _    | ns   |

| SCK↓ – <del>CS</del> ↑ Hold Time  | t <sub>CSH</sub> | _         | 100  | _    | _    | ns   |

| SCK "H" Level Pulse Width         | t <sub>WH</sub>  | _         | 100  | _    | _    | ns   |

| SCK "L" Level Pulse Width         | t <sub>WL</sub>  | _         | 100  | _    | _    | ns   |

| DI Setup Time                     | t <sub>DIS</sub> | _         | 20   | _    | _    | ns   |

| DI Hold Time                      | t <sub>DIH</sub> | _         | 30   | _    | _    | ns   |

| DO Output Delay Time              | t <sub>DOD</sub> | _         | _    | _    | 200  | ns   |

| DO Output Enable Shift Time       | t <sub>DOE</sub> | _         | _    | _    | 150  | ns   |

| DO Output Hi-Z Shift Time         | t <sub>DOZ</sub> | _         | _    | _    | 150  | ns   |

| Command Interval Time             | t <sub>CS</sub>  | _         | 5    | _    | _    | μS   |

## TIMING DIAGRAM

## Serial Peripheral Interface (SPI) AC Characteristics Timing Chart

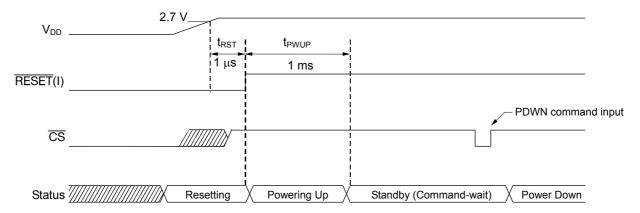

## **Operational Timing at Power-On**

To initialize the internal serial interface circuit of ML2500B after power-on, you must input "L" pulse to the  $\overline{RESET}$  pin at the timing shown below. After this "L" pulse input, the ML2500B enters into standby state (Command-wait state).

Timing for inputting RESET pulse at Power-on

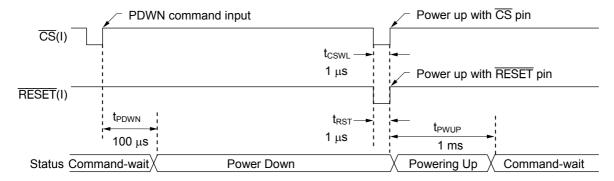

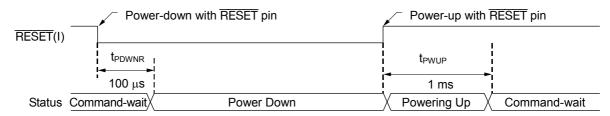

## **Timing for Power Up and Power Down Operations**

ML2500B stops its oscillation circuit to shift to power-down state either by using the PDWN command or by inputting Low level to the  $\overline{RESET}$  pin. In power-down state, the ML2500B turns into low power consumption mode.

Two options are available to power up the LSI again after power down by the PDWN command:

- 1. Input "L" pulse to the  $\overline{RESET}$  pin, or

- 2. Input Low level to the  $\overline{CS}$  pin.

The following charts show timings for power up and power down operations.

Timing for power-down operation by using the PDWN command

Timing for Power-down operation with  $\overline{RESET}$  pin

#### **Timing for Record/Playback Operation**

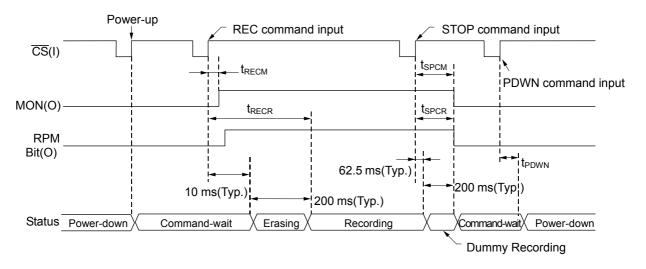

## 1. Timing for Recording Operation

The following chart shows timing for recording operation at 6.4 kHz sampling frequency. It is assumed that the Start and Stop Addresses are set by the STADR and SPADR commands prior to the REC command input.

(Note 1) It takes about 210 ms (Typ.) for the LSI to start actual recording after the REC command input, as the LSI first erase 1 sector before it can start recording.

(Note 2) When recording is stopped by the STOP command, the LSI continues to record until the last address of the current page is reached. This "lag" recording time is the STOP command of about 62.5 ms (Typ.). Afterwards, dummy recording is taken place up to the end of the following sector (max. 2 sectors). This dummy recording takes about 200 ms (Typ.). The dummy recording is given in the device specification and the recording contents are undefined.

(Note 3) It is recommended to use the power-down mode in order to reduce power consumption when record or playback are not performed.

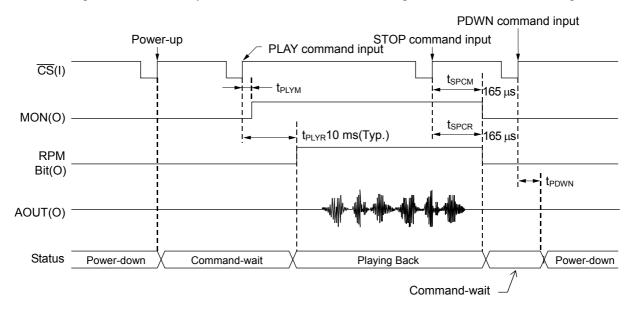

## 2. Timing for Playback Operation

The following chart shows timing for playback operation at 6.4 kHz sampling frequency. It is assumed that the Start and Stop Addresses are set by the STADR and SPADR commands prior to the PLAY command input.

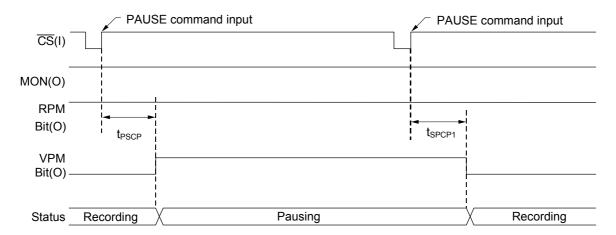

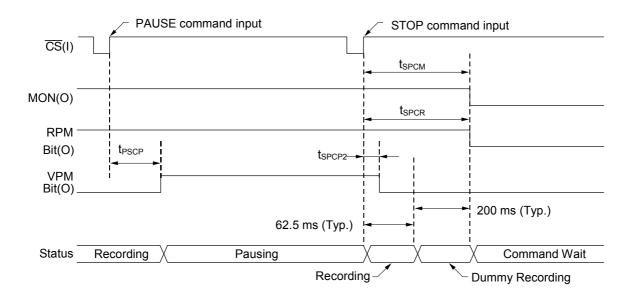

#### 3. Timing for Pausing Operation by the PAUSE Command

The following charts show timings for pausing recording operation by using the PAUSE command at 6.4 kHz sampling frequency.

(NOTE) If the STOP command is input while recording is suspended by the PAUSE command, the LSI resumes recording and keeps on recording until the last address of the current page is reached. This "lag" recording time is about 62.5 ms (Typ.).

Afterwards, dummy recording is taken place up to the end of the following sector (max. 2 sectors). This dummy recording takes about 200 ms (Typ.).

The dummy recording is given in the device specification and the recording contents are undefined.

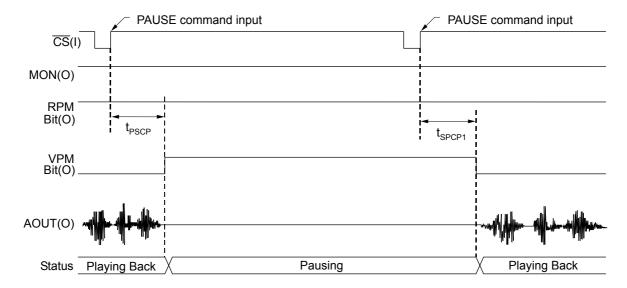

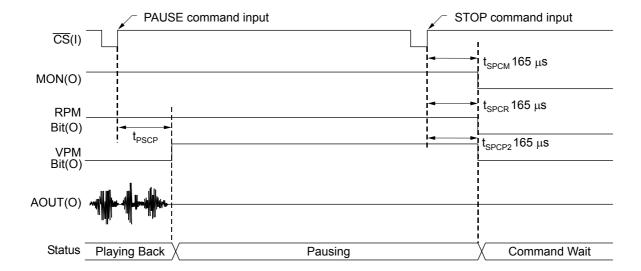

The following charts show timings for pausing playback by using the PAUSE command at 6.4 kHz sampling frequency.

#### **FUNCTIONAL DESCRIPTION**

## Serial Peripheral Interface (SPI)

$ML2500B\ communicates\ with\ the\ external\ Micro-Controller\ Unit\ through\ the\ industry's\ standard\ Serial\ Peripheral\ Interface\ (SPI).$

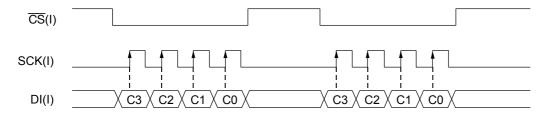

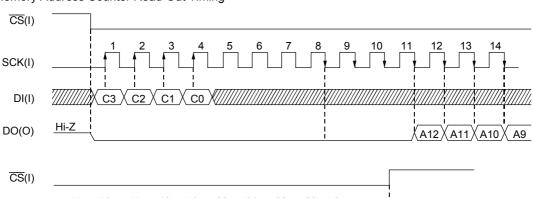

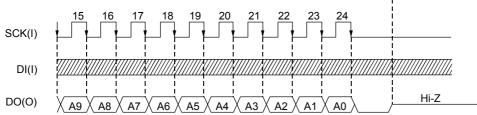

#### 1. Timing for Writing Command Data

The following charts show timings for writing command data. After "L" input to  $\overline{CS}$  pin, input command data, starting with the MSB in serial order, to the DI pin in sync with the SCK signal.

The command input to the DI pin is fetched to the LSI's internal shift resister at the rising edge of the SCK signal, and then the command is executed at the rising edge of the  $\overline{CS}$  pin. The DI input is either of 4, 8, or 24th bit.

When the  $\overline{\text{CS}}$  pin is brought to "H" level except at 4/8/24th bit for the command, the command input then is disregarded. It is a recommendable practice to input command data at the falling edge of the  $\overline{\text{CS}}$  pin while having the SCK pin at "L".

#### 4-bit Command Format

#### 8-bit Command Format

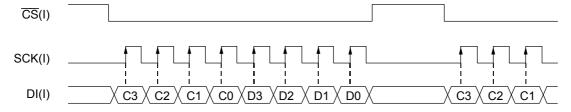

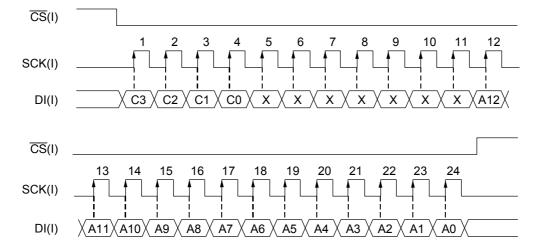

## 24-bit Command Format

#### 2. Timings for Reading out Status Data

Status data that can be read includes two types, the status register (refer to the section 1.7, RDSTAT Command) and the memory address counter (refer to the section 1.6, RDADR Command).

Timings for reading status data are shown in the charts below. After "L" input to the  $\overline{CS}$  pin, input the RDSTAT command to read status data. While the  $\overline{CS}$  pin being held "L", status data is output to the DO pin in serial sequence starting with the MSB, in synchronization with the 4th pulse SCK's falling edge following the command input. After reading status data, the DO pin returns to "Hi-Z" status regardless the number of SCK pulse, when the  $\overline{CS}$  pin is brought to "H" level.

#### Status Data Read-Out Timing

#### Memory Address Counter Read-Out Timing

#### **Control Commands**

You can control Record/Playback operations by using 4-bit commands through the serial interface.

#### 1. Control Commands-Recording

The following section describes commands used to control recording:

#### 1.1. REC Command (1XH)

By using the first 4 bits of this command, you can initiate recording, starting at the specified Start Address and recording lasts up to the specified Stop Address. When the specified Stop Address is reached, recording automatically ends up.

4-bit data preceded is to define a sampling frequency, as shown in the table below. When the sampling frequency is not defined with this command, recording is made at the last defined sampling frequency.

When reset and powered up, recording is made at 6.4 kHz (default) sampling frequency.

#### (With the internal oscillator or the external clock at 8.192 MHz)

| Data | Sampling Frequency |

|------|--------------------|

| 0H   | 4.0 kHz            |

| 1H   | 5.3 kHz            |

| 2H   | 6.4 kHz (Default)  |

You can specify the Start and Stop Addresses for a recording session by using the STADR and SPADR commands. See 1.4 and 1.5 of this Data Sheet for further details on the STADR and SPADR commands.

#### 1.2. STOP Command (3H)

You can stop recording by using this command. The data following to this command is disregarded.

#### 1.3. PAUSE Command (4H)

You can suspend recording temporarily by using this command. The data following to this command is disregarded.

To re-input the command resumes the suspended operation. If the STOP command is input while recording is suspended by the PAUSE command, the LSI shifts to Record Ending operation and then terminates recording.

#### 1.4. STADR Command (5H)

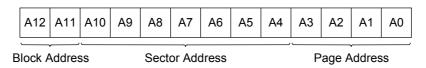

You can specify the Start Address for recording with 13-bit data preceded by this command.

You need to run the STADR command before you can use the REC command.

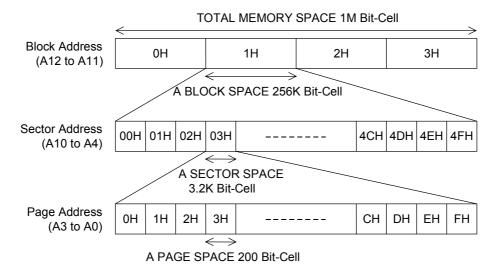

Due to the design of memory array configuration, lower 4-bit of 13-bit Start Address defined is automatically set to "0H". For further details, refer to "Addressable Memory Space for Recording" section. When this command is not executed prior to the REC command input, recording starts at the last defined Start Address. After resetting or power-on, the Start Address is set to the memory's starting address as default.

#### 1.5. SPADR command (6H)

You can specify the Stop Address for recording with 13-bit data preceded by this command.

You need to run the SPADR command before you can use the REC command.

When this command is not executed prior to the REC command input, recording ends at the last defined Stop Address. After resetting or power-on, the Stop Address is set to the memory's last address as default.

## 1.6. RDADR Command (7H)

By using this command you can read the address pointed by the current Memory Address Counter via serial interface. In sync with SCK signal following to the RDADR command, 13-bit Memory Address Counter's value, starting with the MSB, is output to the DO pin. The DO pin's output falls down to "L" level after 13th bit. Right after recording stops, use this command to read the Stop Address of the phrase that has just been recorded. This allows the external MCU to control addresses for recorded phrases. This command can be input during recording and record pausing. However, running the RDADR command after the STADR (SPADR) command input, lets the LSI output the address defined by the STADR (SPADR) command.

#### 1.7. RDSTAT Command (8H)

By using this command you can read out the values of the internal Status Register via serial interface. Reading the Status Register's values lets you know ML2500B's internal status as shown in the table below. In sync with SCK signal following to the RDSTAT command bits, 4-bit Status Register's data is output to the DO pin, starting with the MSB. The DO pin's output after 4th bit falls down to the GND level.

| Read Bit | Name | Status Description                                                                                                                                                     |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03       | MON  | Output "H" level while in record/playback operation, physical recording/playback time plus memory control time. This output is identical value to that of the MON pin. |

| 02       | VPM  | Output "H" level while recording/playback being suspended by the PAUSE command.                                                                                        |

| 01       | RPM  | Output "H" level while in record/playback operation, physical recording/playback time only without memory control time.                                                |

| 00       | FULL | Output "H" level simultaneously when the MON pin turns "L" level as recording/playback ends by reaching the last address of memory.                                    |

#### 2. Control Commands-Playback

The following section describes commands used to control playback:

#### 2.1. PLAY Command (2XH)

By using the first 4 bits of this command, you can initiate playback, starting at the specified Start Address and playback lasts up to the specified Stop Address. When the specified Stop Address is reached, playback automatically stops.

4-bit data preceded is to define a sampling frequency, same as with the REC command. When the sampling frequency is not defined with this command, playback is made last defined sampling frequency.

When reset and powered up, playback is made at 6.4 kHz (default) sampling frequency.

You can specify the Start and Stop Addresses for a playback session by using the STADR and SPADR commands. See 2.4 and 2.5 for further details on the STADR and SPADR commands. When the Start Address and the Stop Address are not defined by STADR and SPADR commands, playback is taken place by using the Start and Stop Addresses defined for the last playback session.

#### 2.2. STOP Command (3H)

You can stop playback by using this command. The data following to this command is disregarded.

#### 2.3. PAUSE Command (4H)

You can temporarily suspend playback by using this command. The data following to this command is disregarded.

Re-inputting this command resumes the suspended operation. If the STOP command is input while playback is suspended by the PAUSE command, the LSI stops playback.

#### 2.4. STADR Command (5H)

You can specify the Start Address for playback with 13-bit data preceded by this command.

You need to run STADR command before you can use the PLAY command.

When this command is not executed prior to the PLAY command input, playback starts at the last defined Start Address. After resetting or power-on, the Start Address is set to the memory's starting address as default.

#### 2.5. SPADR Command (6H)

You can specify the Stop Address for playback with 13-bit data preceded by this command.

You need to run the SPADR command before you can use the PLAY command.

When this command is not executed prior to the PLAY command input, playback ends at the last defined Stop Address. After resetting or power-on, the Stop Address is set to the memory's last address as default.

#### 2.6. RDADR Command (7H)

By using this command you can read the address pointed by the current Memory Address Counter via serial interface. In synchronization with SCK signal following to the RDADR command, 13-bit Memory Address Counter's value, starting with the MSB, is output to the DO pin. The DO pin's output falls down to "L" level after 13th bit. This command can be input during playback and playback pausing.

| , | v.           |

|---|--------------|

|   | Spuemme      |

|   | n            |

|   | ī            |

| , |              |

| į | _            |

|   | _            |

| , | ç            |

| , | ntro         |

| , | ontro        |

| , |              |

| , | ر<br>خ       |

|   | ر<br>خ       |

|   | 151 0        |

|   | O to tail of |

| 3.                              | . The list of Control Commands |     |                        |                                                                                                    |                                                                         |                                                                         |                                                                         |                                                                                   |                                                                                   |                                                                                   |                                                                                                   |                                                                        |                                                                        |                                                                        |                                                                                     |                                                                                     |                                                                                     |                      |                                       |                                          |                                         |                                       |                               |                                            |

|---------------------------------|--------------------------------|-----|------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------|---------------------------------------|------------------------------------------|-----------------------------------------|---------------------------------------|-------------------------------|--------------------------------------------|

|                                 | Command Function Name          |     | No Particular Function | Start recording either at default or last-defined sampling frequency. (Initial frequency: 6.4 kHz) | Record at fsam 4.0 kHz with int. oscillator or ext. clock at 8.192 MHz. | Record at fsam 5.3 kHz with int. oscillator or ext. clock at 8.192 MHz. | Record at fsam 6.4 kHz with int. oscillator or ext. clock at 8.192 MHz. | Record at fsam 5.3 kHz with ext. clock at 4.096 MHz. *Not supported for int. osc. | Record at fsam 6.4 kHz with ext. clock at 4.096 MHz. *Not supported for int. osc. | Record at fsam 4.0 kHz with ext. clock at 4.096 MHz. *Not supported for int. osc. | Start playback either at default or last-defined sampling frequency. (Initial frequency: 6.4 kHz) | Playback at fsam 4.0 kHz with int. oscillator or ext. clock 8.192 MHz. | Playback at fsam 5.3 kHz with int. oscillator or ext. clock 8.192 MHz. | Playback at fsam 6.4 kHz with int. oscillator or ext. clock 8.192 MHz. | Playback at fsam 5.3 kHz with ext. clock at 4.096 MHz. *Not supported for int. osc. | Playback at fsam 6.4 kHz with ext. clock at 4.096 MHz. *Not supported for int. osc. | Playback at fsam 4.0 kHz with ext. clock at 4.096 MHz. *Not supported for int. osc. | Stop Record/Playback | Pause Record/Playback, or reset PAUSE | Define Start Address for Record/Playback | Define Stop Address for Record/Playback | Read out Memory Address Counter value | Read out Status Register data | Power-down to enter into power saving mode |

|                                 |                                |     | NOOP                   | REC                                                                                                |                                                                         |                                                                         |                                                                         |                                                                                   |                                                                                   | PLAY                                                                              |                                                                                                   |                                                                        |                                                                        |                                                                        |                                                                                     |                                                                                     | STOP                                                                                | PAUSE                | STADR                                 | SPADR                                    | RDADR                                   | RDSTAT                                | PDWN                          |                                            |

|                                 |                                | 24  |                        |                                                                                                    |                                                                         |                                                                         | -                                                                       |                                                                                   | -                                                                                 | -                                                                                 |                                                                                                   | -                                                                      |                                                                        |                                                                        |                                                                                     |                                                                                     | -                                                                                   |                      |                                       | A0                                       | A0                                      | A0                                    |                               |                                            |

|                                 |                                | 23  |                        |                                                                                                    |                                                                         |                                                                         | -                                                                       |                                                                                   | -                                                                                 | -                                                                                 | -                                                                                                 | -                                                                      |                                                                        |                                                                        |                                                                                     |                                                                                     | -                                                                                   |                      | -                                     | A1                                       | A1                                      | A1                                    | _                             |                                            |

|                                 |                                | 22  |                        |                                                                                                    |                                                                         |                                                                         | 1                                                                       |                                                                                   | 1                                                                                 | -                                                                                 | -                                                                                                 | -                                                                      |                                                                        |                                                                        |                                                                                     |                                                                                     |                                                                                     |                      | -                                     | A2                                       | A2                                      | A2                                    | _                             |                                            |

|                                 |                                | 21  |                        |                                                                                                    |                                                                         |                                                                         | 1                                                                       |                                                                                   | 1                                                                                 | -                                                                                 | -                                                                                                 | -                                                                      |                                                                        |                                                                        |                                                                                     |                                                                                     |                                                                                     |                      | -                                     | A3                                       | А3                                      | А3                                    | _                             |                                            |

|                                 |                                | 20  |                        |                                                                                                    |                                                                         |                                                                         | 1                                                                       |                                                                                   | 1                                                                                 | -                                                                                 |                                                                                                   | -                                                                      |                                                                        |                                                                        |                                                                                     |                                                                                     |                                                                                     |                      | -                                     | A4                                       | A4                                      | A4                                    | _                             |                                            |

|                                 |                                | 19  |                        |                                                                                                    |                                                                         | -                                                                       | 1                                                                       | -                                                                                 | 1                                                                                 | 1                                                                                 | -                                                                                                 | 1                                                                      | -                                                                      | -                                                                      | -                                                                                   | -                                                                                   | 1                                                                                   | -                    | -                                     | A5                                       | A5                                      | A5                                    |                               |                                            |

|                                 |                                | 18  |                        |                                                                                                    |                                                                         |                                                                         | -                                                                       |                                                                                   | -                                                                                 | 1                                                                                 |                                                                                                   | -                                                                      |                                                                        |                                                                        |                                                                                     |                                                                                     | -                                                                                   |                      | -                                     | A6                                       | A6                                      | A6                                    |                               |                                            |

|                                 |                                | 17  |                        |                                                                                                    |                                                                         | -                                                                       | 1                                                                       | -                                                                                 | 1                                                                                 | 1                                                                                 | -                                                                                                 | 1                                                                      | -                                                                      | -                                                                      | -                                                                                   | -                                                                                   | 1                                                                                   | -                    | -                                     | A7                                       | A7                                      | A7                                    |                               | -                                          |

|                                 | _                              | 16  |                        |                                                                                                    |                                                                         | -                                                                       | 1                                                                       | -                                                                                 | 1                                                                                 | 1                                                                                 | -                                                                                                 | 1                                                                      | -                                                                      | -                                                                      | -                                                                                   | -                                                                                   | 1                                                                                   | -                    | -                                     | A8                                       | A8                                      | A8                                    | 0                             | -                                          |

|                                 | Data                           | 15  |                        |                                                                                                    |                                                                         | -                                                                       |                                                                         |                                                                                   |                                                                                   | -                                                                                 | -                                                                                                 | -                                                                      |                                                                        |                                                                        |                                                                                     |                                                                                     | 1                                                                                   | -                    | -                                     | A9                                       | A9                                      | A9                                    | 0                             | -                                          |

|                                 |                                | 14  |                        |                                                                                                    |                                                                         | -                                                                       |                                                                         |                                                                                   |                                                                                   | -                                                                                 | -                                                                                                 | -                                                                      |                                                                        |                                                                        |                                                                                     |                                                                                     | 1                                                                                   | -                    | -                                     | A12A11A10                                | A12A11A10                               | A12A11A10                             | 0                             | -                                          |

|                                 |                                | 13  |                        |                                                                                                    |                                                                         | -                                                                       | 1                                                                       | -                                                                                 | 1                                                                                 | 1                                                                                 | -                                                                                                 | 1                                                                      | -                                                                      | -                                                                      | -                                                                                   | -                                                                                   | 1                                                                                   | -                    | -                                     | A11                                      | A11                                     | A11                                   | 0                             | -                                          |

| ds                              |                                | 12  |                        |                                                                                                    |                                                                         | -                                                                       | 1                                                                       | -                                                                                 | 1                                                                                 | 1                                                                                 | -                                                                                                 | 1                                                                      | -                                                                      | -                                                                      | -                                                                                   | -                                                                                   | 1                                                                                   | -                    | -                                     | A12                                      | A12                                     | A12                                   | 00                            | 1                                          |

| nan                             |                                | 11  |                        |                                                                                                    |                                                                         |                                                                         | 1                                                                       |                                                                                   | 1                                                                                 | 1                                                                                 |                                                                                                   | 1                                                                      |                                                                        |                                                                        |                                                                                     |                                                                                     | 1                                                                                   |                      |                                       | ×                                        | ×                                       | ×                                     | 01                            |                                            |

| omr                             |                                | 10  |                        |                                                                                                    |                                                                         |                                                                         |                                                                         |                                                                                   |                                                                                   |                                                                                   |                                                                                                   |                                                                        |                                                                        |                                                                        |                                                                                     |                                                                                     |                                                                                     |                      |                                       | ×                                        | ×                                       | ×                                     | 3 02                          |                                            |

| l C                             |                                | 6   |                        |                                                                                                    |                                                                         |                                                                         |                                                                         |                                                                                   | l                                                                                 |                                                                                   |                                                                                                   |                                                                        |                                                                        |                                                                        |                                                                                     |                                                                                     | l                                                                                   |                      |                                       | ×                                        | ×                                       | ×                                     | ( 03                          | 1                                          |

| ntrc                            |                                | 2 8 |                        |                                                                                                    | 0                                                                       | 1                                                                       | 0                                                                       | 0                                                                                 | 0                                                                                 | 1                                                                                 |                                                                                                   | 0 0                                                                    | 0                                                                      | 0                                                                      | 0                                                                                   | 0                                                                                   | -                                                                                   |                      |                                       | ×                                        | ×                                       | ×                                     | ×                             | 1                                          |

| Co                              |                                | 9   | <u> </u>               |                                                                                                    | 0                                                                       | 0                                                                       | 0                                                                       | -                                                                                 | -                                                                                 | _                                                                                 | <u> </u>                                                                                          | 0                                                                      | 0                                                                      | 0                                                                      | -                                                                                   | -                                                                                   | _                                                                                   | 1                    | <u> </u>                              | ×                                        | ×                                       | ×                                     | ×                             | <u> </u>                                   |

| 3. The List of Control Commands |                                | 2   | i                      | i                                                                                                  | 0                                                                       | 0                                                                       | 0                                                                       | 0                                                                                 | 0                                                                                 | 0                                                                                 | Ī                                                                                                 | 0                                                                      | 0                                                                      | 0                                                                      | 0                                                                                   | 0                                                                                   | 0                                                                                   | i                    | İ                                     | ×                                        | ×                                       | ×                                     | ×                             |                                            |

| Lis                             | pu                             | 4   | 0                      | -                                                                                                  |                                                                         |                                                                         | -                                                                       | -                                                                                 | -                                                                                 |                                                                                   | 0                                                                                                 |                                                                        |                                                                        | -                                                                      | -                                                                                   | -                                                                                   | -                                                                                   | _                    | 0                                     | ~                                        | 0                                       | -                                     | 0                             | ~                                          |