### Asynchronous SRAM, 3.3V, 256Kx24

#### **FEATURES**

- 256Kx24 bit CMOS Static

- Random Access Memory Array

- Fast Access Times: 10, 12, and 15ns

- · Master Output Enable and Write Control

- TTL Compatible Inputs and Outputs

- · Fully Static, No Clocks

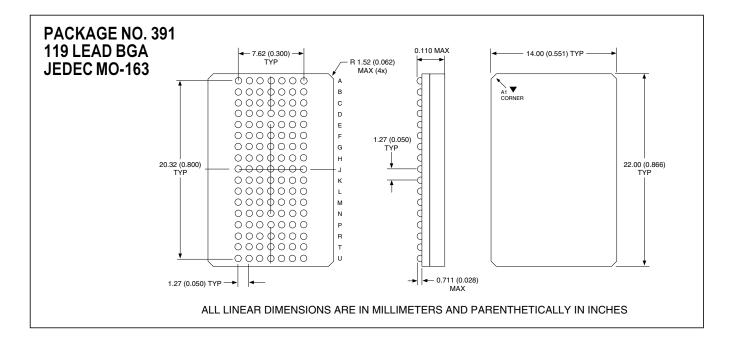

- Surface Mount Package

- 119 Lead BGA (JEDEC MO-163), No. 391

- Small Footprint, 14mmx22mm

- · Multiple Ground Pins for Maximum Noise Immunity

- Single +3.3V (±5%) Supply Operation

- DSP Memory Solution

- Motorola DSP5630x

- Analog Devices SHARC™

#### **DESCRIPTION**

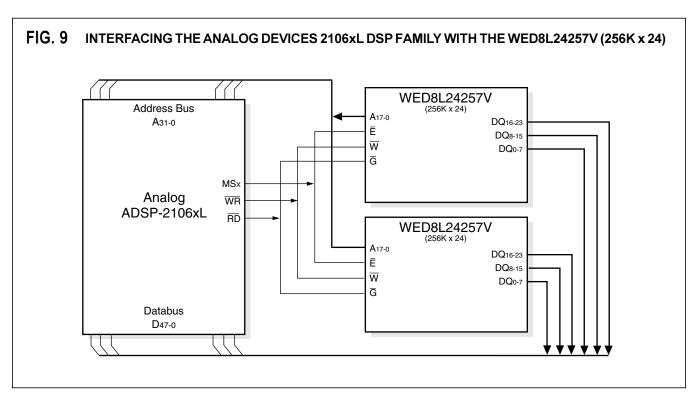

The WED8L24257VxxBC is a 3.3V, twelve megabit SRAM constructed with three 256Kx8 die mounted on a multi-layer laminate substrate. With 10 to 15ns access times, x24 width and a 3.3V operating voltage, the WED8L24257V is ideal for creating a single chip memory solution for the Motorola DSP5630x (Figure 8) or a two chip solution for the Analog Devices SHARC™ DSP (Figure 9).

The single or dual chip memory solutions offer improved system performance by reducing the length of board traces and the number of board connections compared to using multiple monolithic devices.

The JEDEC Standard 119 lead BGA provides a 69% space savings over using six 256Kx4, 300 mil wide SOJs and the BGA package has a maximum height of 110 mils compared to 148 mils for the SOJ packages. The BGA package also allows the use of the same manufacturing and inspection techniques as the Motorola DSP, which is also in a BGA package.

# FIG. 1 PIN CONFIGURATION PIN SYMBOLS

|   | 1     | 2   | 3   | 4   | 5   | 6   | 7     |

|---|-------|-----|-----|-----|-----|-----|-------|

| Α | NC    | AO  | A1  | A2  | А3  | A4  | NC    |

| В | NC    | A5  | A6  | Ē   | A7  | 8A  | NC    |

| С | 1/012 | NC  | NC  | NC  | NC  | NC  | 1/00  |

| D | 1/013 | VCC | GND | GND | GND | VCC | I/01  |

| E | 1/014 | GND | VCC | GND | VCC | GND | 1/02  |

| F | 1/015 | VCC | GND | GND | GND | VCC | 1/03  |

| G | 1/016 | GND | VCC | GND | VCC | GND | 1/04  |

| Н | I/017 | VCC | GND | GND | GND | VCC | 1/05  |

| J | NC    | GND | VCC | GND | VCC | GND | NC    |

| K | 1/018 | VCC | GND | GND | GND | VCC | 1/06  |

| L | 1/019 | GND | VCC | GND | VCC | GND | 1/07  |

| М | 1/020 | VCC | GND | GND | GND | VCC | 1/08  |

| N | 1/021 | GND | VCC | GND | VCC | GND | 1/09  |

| Р | 1/022 | VCC | GND | GND | GND | VCC | 1/010 |

| R | 1/023 | NC  | NC  | NC  | NC  | A17 | I/011 |

| Т | NC    | Α9  | A10 | W   | A11 | A12 | NC    |

| U | NC    | A13 | A14 | G   | A15 | A16 | NC    |

#### PIN NAMES

| A0-17  | Address Inputs           |  |  |  |

|--------|--------------------------|--|--|--|

| Ē      | Chip Enable              |  |  |  |

| W      | Master Write Enable      |  |  |  |

| G      | Master Output Enable     |  |  |  |

| DQ0-23 | Common Data Input/Output |  |  |  |

| VCC    | Power (3.3V ±5%)         |  |  |  |

| GND    | Ground                   |  |  |  |

| NC     | No Connection            |  |  |  |

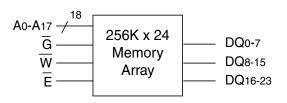

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage on any pin relative to VSS | -0.5V to 4.6V   |

|------------------------------------|-----------------|

| Operating Temperature TA (Ambient) |                 |

| Commercial                         | 0°C to +70°C    |

| Industrial                         | -40°C to +85°C  |

| Storage Temperature                | -55°C to +125°C |

| Power Dissipation                  | 1.5 Watts       |

| Output Current                     | 50 mA           |

<sup>\*</sup>Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

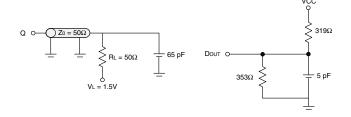

#### **ACTEST CONDITIONS**

| Input Pulse Levels             | VSS to 3.0V |

|--------------------------------|-------------|

| Input Rise and Fall Times      | 5ns         |

| Input and Output Timing Levels | 1.5V        |

| Output Load                    | Figure 2    |

NOTE: For TEHQZ,TGHQZ and TWLQZ, Figure 3

#### RECOMMENDED DC OPERATING CONDITIONS

| Parameter          | Sym | Min   | Тур | Max     | Units |  |

|--------------------|-----|-------|-----|---------|-------|--|

| Supply Voltage     | VCC | 3.135 | 3.3 | 3.465   | V     |  |

| Supply Voltage     | VSS | 0     | 0   | 0       | V     |  |

| Input High Voltage | VIH | 2.2   | _   | VCC+0.3 | V     |  |

| Input Low Voltage  | VIL | -0.3  | _   | 8.0     | V     |  |

FIG. 2 FIG. 3

#### DC ELECTRICAL CHARACTERISTICS

| Parameter                           | Sym Conditions |                                                 | Min | М    | Max     |    |  |

|-------------------------------------|----------------|-------------------------------------------------|-----|------|---------|----|--|

|                                     | ,              |                                                 |     | 10ns | 12-15ns | 1  |  |

| Operating Power Supply Current      | ICC1           | W = VIL, II/O = 0mA,<br>Min Cycle               |     | 500  | 480     | mA |  |

| Standby (TTL) Supply Current        | ICC2           | E > VIH, VIN < VIL or<br>VIN > VIH, f=ØMHz      |     | 150  | 150     | mA |  |

| Full Standby CMOS<br>Supply Current | ICC3           | E > VCC-0.2V<br>VIN > VCC-0.2V or<br>VIN < 0.2V |     | 90   | 90      | mA |  |

| Input Leakage Current               | ILI            | VIN = 0V to VCC                                 |     | ±10  | ±10     | μΑ |  |

| Output Leakage Current              | ILO            | V I/O = 0V to VCC                               |     | ±10  | ±10     | μΑ |  |

| Output High Volltage                | VOH            | IOH = -4.0mA                                    | 2.4 |      |         | V  |  |

| Output Low Voltage                  | VOL            | IOL = 4.0mA                                     |     | 0.4  | 0.4     | V  |  |

#### **TRUTHTABLE**

| G | Ē | W | Mode            | Output | Power     |

|---|---|---|-----------------|--------|-----------|

| Χ | Н | Χ | Standby         | High Z | ICC2,ICC3 |

| Н | L | Н | Output Deselect | High Z | ICC1      |

| L | L | Н | Read            | DOUT   | ICC1      |

| Χ | L | L | Write           | DIN    | ICC1      |

## CAPACITANCE (f=1.0MHz, VIN=VCC or VSS)

| Parameter                   | Sym                           | Max | Unit |

|-----------------------------|-------------------------------|-----|------|

| Address Lines               | ČA                            | 8   | pF   |

| Data Lines                  | CD/Q                          | 10  | pF   |

| Write & Output Enable Lines | $\overline{W}, \overline{G}$  | 8   | pF   |

| Chip Enable Lines           | <del>EØ</del> - <del>E2</del> | 8   | pF   |

These parameters are sampled, not 100% tested.

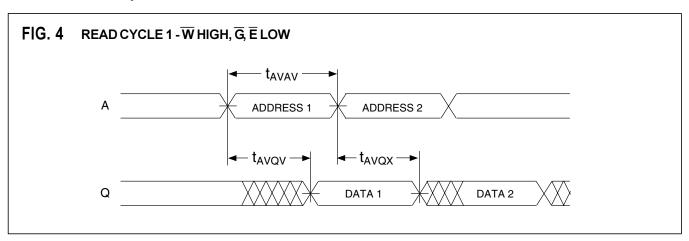

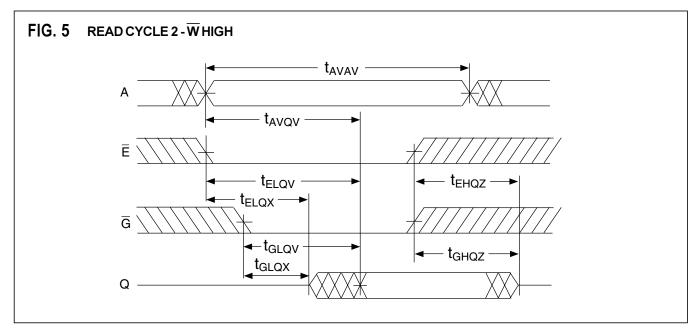

#### AC CHARACTERISTICS READ CYCLE

|                                       | Symbol |      | 10  | ns  | 12ns |     | 15ns |     |       |

|---------------------------------------|--------|------|-----|-----|------|-----|------|-----|-------|

| Parameter                             | JEDEC  | Alt. | Min | Max | Min  | Max | Min  | Max | Units |

| Read Cycle Time                       | TAVAV  | TRC  | 10  |     | 12   |     | 15   |     | ns    |

| Address Access Time                   | TAVQV  | TAA  |     | 10  |      | 12  |      | 15  | ns    |

| Chip Enable Access Time               | TELQV  | TACS |     | 10  |      | 12  |      | 15  | ns    |

| Chip Enable to Output in Low Z (1)    | TELQX  | TCLZ | 3   |     | 3    |     | 3    |     | ns    |

| Chip Disable to Output in High Z (1)  | TEHQZ  | TCHZ |     | 5   |      | 6   |      | 7   | ns    |

| Output Hold from Address Change       | TAVQX  | TOH  | 3   |     | 3    |     | 3    |     | ns    |

| Output Enable to Output Valid         | TGLQV  | TOE  |     | 5   |      | 6   |      | 7   | ns    |

| Output Enable to Output in Low Z (1)  | TGLQX  | TOLZ | 0   |     | 0    |     | 0    |     | ns    |

| Output Disable to Output in High Z(1) | TGHQZ  | TOHZ |     | 5   |      | 6   |      | 7   | ns    |

NOTE 1: Parameter is guaranteed, but not tested.

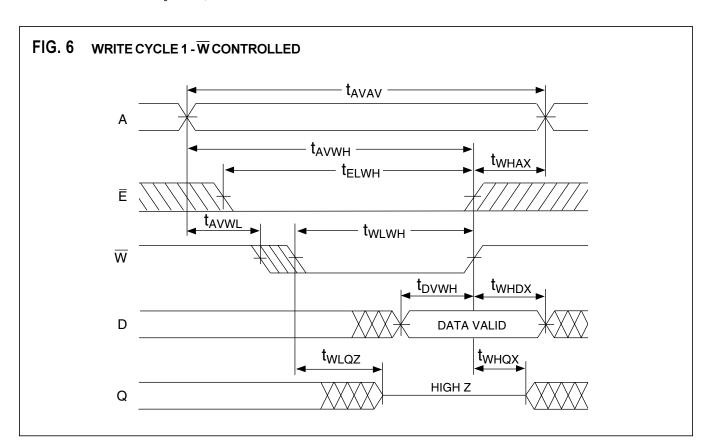

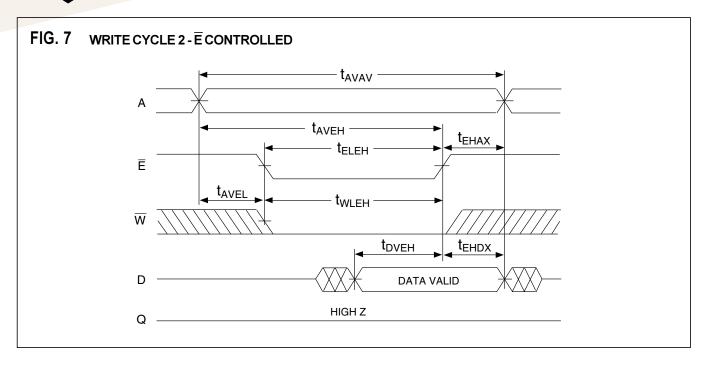

#### AC CHARACTERISTICS WRITE CYCLE

|                                     | Sym   | bol  | 10  | ns  | 121 | ns  | 15r | าร  |       |

|-------------------------------------|-------|------|-----|-----|-----|-----|-----|-----|-------|

| Parameter                           | JEDEC | Alt. | Min | Max | Min | Max | Min | Max | Units |

| Write Cycle Time                    | TAVAV | TWC  | 10  |     | 12  |     | 15  |     | ns    |

| Chip Enable to End of Write         | TELWH | TCW  | 8   |     | 9   |     | 9   |     | ns    |

|                                     | TELEH | TCW  | 8   |     | 9   |     | 9   |     | ns    |

| Address Setup Time                  | TAVWL | TAS  | 0   |     | 0   |     | 0   |     | ns    |

|                                     | TAVEL | TAS  | 0   |     | 0   |     | 0   |     | ns    |

| Address Valid to End of Write       | TAVWH | TAW  | 8   |     | 9   |     | 10  |     | ns    |

|                                     | TAVEH | TAW  | 8   |     | 9   |     | 10  |     | ns    |

| Write Pulse Width                   | TWLWH | TWP  | 8   |     | 10  |     | 11  |     | ns    |

|                                     | TWLEH | TWP  | 8   |     | 10  |     | 11  |     | ns    |

| Write Recovery Time                 | TWHAX | TWR  | 0   |     | 0   |     | 0   |     | ns    |

|                                     | TEHAX | TWR  | 0   |     | 0   |     | 0   |     | ns    |

| Data Hold Time                      | TWHDX | TDH  | 0   |     | 0   |     | 0   |     | ns    |

|                                     | TEHDX | TDH  | 0   |     | 0   |     | 0   |     | ns    |

| Write to Output in High Z (1)       | TWLQZ | TWHZ | 0   | 5   | 0   | 6   | 0   | 7   | ns    |

| Data to Write Time                  | TDVWH | TDW  | 6   |     | 6   |     | 7   |     | ns    |

|                                     | TDVEH | TDW  | 6   |     | 6   |     | 7   |     | ns    |

| Output Active from End of Write (1) | TWHQX | TWLZ | 3   |     | 3   |     | 3   |     | ns    |

NOTE 1: Parameter is guaranteed, but not tested.

#### **ORDERING INFORMATION**

Commercial (0°C to +70°C)

| Part Number     | Speed<br>(ns) | Package<br>No. |  |

|-----------------|---------------|----------------|--|

| WED8L24257V10BC | 10            | 391            |  |

| WED8L24257V12BC | 12            | 391            |  |

| WED8L24257V15BC | 15            | 391            |  |

Industrial (-40°C to +85°C)

| Part Number     | Speed<br>(ns) | Package<br>No. |

|-----------------|---------------|----------------|

| WED8L24257V12BI | 12            | 391            |

| WED8L24257V15BI | 15            | 391            |

5

#### FIG. 8 INTERFACING THE MOTOROLA DSP5630x DSP FAMILY WITH THE WED8L24257V (256K x 24) WED8L24257V A<sub>17-0</sub> •••• Ē DQ0-23 Address Bus $\overline{\mathsf{W}}$ A23-0 G AAc AA<sub>1</sub> AAa WED8L24257V ААз Motorola A<sub>17-0</sub> WR DSP5630x Ē RD DQ0-23 $\overline{\mathsf{W}}$ G WED8L24257V Databus A17-0 D23-0 Ē DQ0-23 . . . . $\overline{\mathsf{W}}$ G Notes: 1. In this example three 256K x 24 external memory arrays are shown, one for X data, one for Y data and one for Program. Specific applications may require one, two, or all three arrays. 2. Any combination of AA0-AA3 may be used as chip selects. However, each chip select may only be used to select one memory array.