# TC9142P

0 0.25 M

$19.25 \pm 0.2$

$0.95 \pm 0.1$

0.735TYP

JEDEC

TOSHIBA

#### QUARTZ PLL MOTOR CONTROL

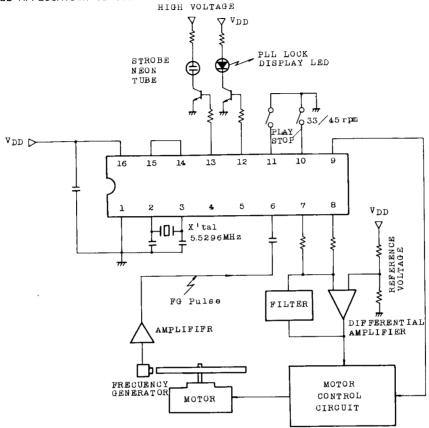

The TC9142P is a  $C^2$ -MOS LSI developed for controlling the motor of a quartz-lock D.D. record player. Since an 8-bit D/A converter system has been employed for each of the speed control system (AFC) and the phase control system (APC), a wide reduction of external parts can be made in comparison with conventional capacitor-type S/H systems, thus having realized adjustment free operation.

- . Has built-in AFC and APC, for each of which 8-bit D/A converter system has been employed.

- . Speed-changeover positions are available at 33 1/3 and 45-rpm.

- . Crystal can be used up to 12 MHz, and crystal reference dividing frequency is selectable from three positions of 1/4, 1/32 and 1/128 to increase the degree of freedom in the number

- to increase the degree of freedom in the number of FG pulses of motor or crystal frequency, which allows a wide range of design to be made.

- . External oscillator makes possible fine adjustment of speed.

- . Provided with strobe reference output and reverse signal output.

## MAXIMUM RATINGS (Ta=25°C)

| CHARACTERISTIC        | SYMBOL            | RATING                   | UNIT |

|-----------------------|-------------------|--------------------------|------|

| Supply Voltage        | $v_{\mathrm{DD}}$ | -0.3 ~ 10.0              | v    |

| Input Voltage         | $v_{IN}$          | $-0.3 \sim V_{DD} + 0.3$ | v    |

| Power Dissipation     | PD                | 300                      | mW   |

| Operating Temperature | Topr              | -30 ∿ 75                 | °C   |

| Storage Temperature   | Tstg              | -55 ∿ 125                | °C   |

# PIN CONNECTIONS

Package width and length do not

Allowable mold protrusion is 0.15mm.

DIP16-P-300A

include mold protrusion.

TOSHIBA CORPORATION

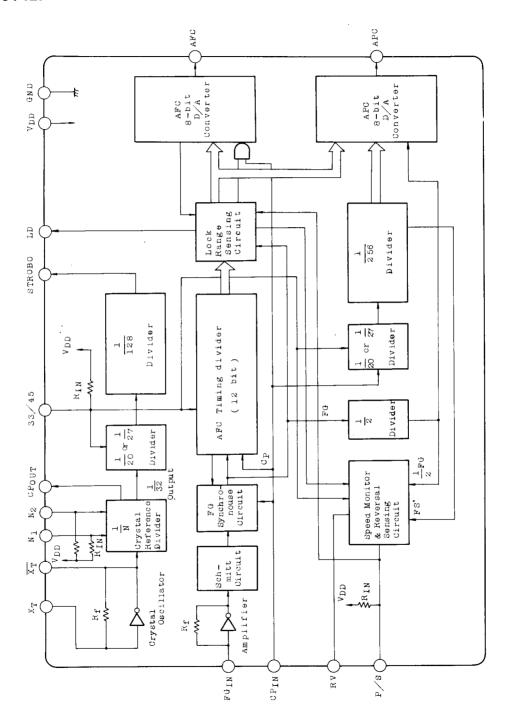

BLOCK DIACRAM

ELECTRICAL CHARACTERISTICS (Unless otherwise specified VDD=7.5V, Ta=25°C)

| CHARACTERISTIC                  |                                       | SYMBOL                               | TEST<br>CIR-<br>CUIT | TEST CONDITIONS                                          | MIN.         | TYP.                    | MAX.                    | UNIT         |

|---------------------------------|---------------------------------------|--------------------------------------|----------------------|----------------------------------------------------------|--------------|-------------------------|-------------------------|--------------|

| Operating Supply                |                                       | V <sub>DD(1)</sub>                   |                      | X'tal=6MHz,CP <sub>IN</sub> =1.5MHz, *                   | 5.0          | ^                       | 9.5                     | V            |

| Voltage                         | Зирріу                                | V <sub>DD</sub> (2)                  |                      | X'tal=12MHz,CP <sub>IN</sub> =3.0MHz,*                   | 7.5          | ح                       | 9.5                     | V            |

| Operating<br>Current            | Supply                                | $I_{\mathrm{DD}}$                    | 1                    | X'tal=12MHz,CP <sub>IN</sub> =3.0MHz,*                   | -            | 5.5                     | 12                      | mA           |

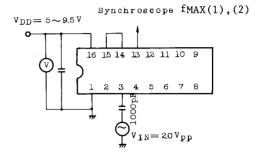

| 0012                            |                                       | f <sub>MAX</sub> (1)                 |                      | $V_{DD}$ =5.0 $\sim$ 7.5 $V$ , *                         | 1.0          | ~                       | 6.0                     | MHz          |

| Operating                       | X <sub>T</sub>                        | fMAX(2)                              | 2                    | V <sub>DD</sub> =7.5 ~ 9.5V, *                           | 1.0          | >                       | 12.0                    | MHz          |

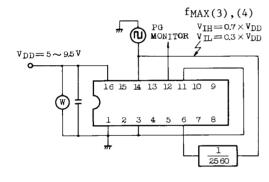

| Frequency<br>Range              |                                       | f <sub>MAX</sub> (3)                 | _                    | V <sub>DD</sub> =5.0 ∿7.5V, *                            | -            | ~                       | 1.5                     | MHz          |

| Kalige                          | CPIN                                  | f <sub>MAX</sub> (4)                 | 3                    | V <sub>DD</sub> =7.5 ~9.5V, *                            | _            | ~                       | 3.0                     | MHz          |

| FG <sub>IN</sub> Opera          |                                       | f <sub>FG</sub>                      |                      | $V_{DD}$ =5.0 \(\sigma 9.5V\), $V_{IN}$ =0.5 $V_{pp}$ ,* | _            | ^                       | 10                      | kHz          |

| FG <sub>IN</sub><br>Input       | Operation                             | V <sub>IN(1)</sub>                   |                      | VDD=5.0 $\sim$ 9.5V, fFG $\sim$ 10kHz Sine Wave *        | 0.5          | ~                       | v <sub>DD</sub><br>-0.5 | Vpp          |

| Amplitude<br>Voltage            | Non-<br>Operation                     | V <sub>IN(2)</sub>                   | 4                    | $f_{FG}\sim 10$ kHz, Sine Wave *                         | 0            | ~                       | 30                      | $mV_{ m pp}$ |

| FGIN Threshold<br>Voltage Range |                                       | V <sub>TH</sub> (FG)                 |                      | $VDD=5.0 \sim 9.5V$ ,<br>At time of DC connection        | 0.2<br>× VDD | _                       | $^{0.8}_{	imes v_{DD}}$ | V            |

| , volume and                    | Max.<br>Deviation                     |                                      |                      | V <sub>DD</sub> =5.0 ~ 9.5V, I <sub>OUT</sub> =0         | -            | <u>+</u> 2.5            | <u>+</u> 6.5            | LSB          |

| AFC, APC<br>D/A<br>Converter    | Resolution                            |                                      | 1                    |                                                          |              | V <sub>DD</sub><br>/256 | -                       | V            |

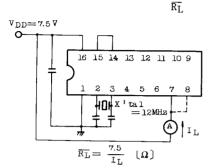

|                                 | Ladder<br>Resistor                    | $\overline{\mathtt{R}_{\mathtt{L}}}$ | 7                    |                                                          | 35           | 55                      | 80                      | kΩ           |

|                                 | Temperature<br>Drift                  |                                      |                      | V <sub>DD</sub> =5.0 ∿ 9.5V, *                           | -            | <u>+</u> 1              | -                       | LSB          |

|                                 | Ladder Resistor<br>Temperature Factor |                                      |                      | *                                                        | -            | +0.55                   | +0.8                    | % /deg.      |

|                                 | Amplifier Feedback                    |                                      | 5                    |                                                          | 100          | 200                     | 500                     | kΩ           |

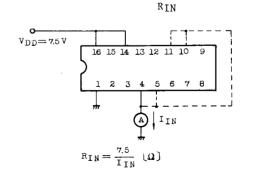

N1, N2, 33/45, P/S, CPIN

| Pullup Res | sistor    | RIN              | 6 | Except CP <sub>IN</sub> Terminal | 15                                                  | 35 | 70                                | kΩ |

|------------|-----------|------------------|---|----------------------------------|-----------------------------------------------------|----|-----------------------------------|----|

| Input      | "H" Level | VIH              |   | $V_{DD}$ =5.0 $\sim$ 9.5V        | $\begin{array}{c} 0.7 \\ \times V_{DD} \end{array}$ | 1  | V <sub>DD</sub><br>+0.3           | V  |

| Voltage    | "L" Level | V <sub>TT,</sub> |   | Except $N_1$ and $N_2$ Terminal  | -0.3                                                | _  | $^{0.3}_{\times V_{\mathrm{DD}}}$ | v  |

RV, LD, STROBE, CPOUT

| Output  | "H" Level | I <sub>OH</sub> | 8 | V <sub>OH</sub> =6.5V | <b>-</b> 0.5 | - | - | m.A |

|---------|-----------|-----------------|---|-----------------------|--------------|---|---|-----|

| Current | "L" Level | IOL             | 9 | V <sub>OL</sub> =1.0V | 0.5          | - | - | mA  |

<sup>\* :</sup> Ta=Range of  $-30 \circ +75$ °C

# — TC9142P

### FUNCTIONAL EXPLANATION OF EACH TERMINAL

| PIN<br>NO. | SYMBOL                                     | TERMINAL NAME                                             | FUNCTIONAL & OPERATION EXPLANATION                                                                                | REMARKS                                 |

|------------|--------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 16         | $v_{\mathrm{DD}}$                          | Power Termianl                                            | V <sub>DD</sub> =5-9.5V is applied                                                                                |                                         |

| 1          | GND                                        | Ground Terminal                                           | Ground.                                                                                                           |                                         |

| 2 3        | $\overline{X_{	extbf{T}}}$ $X_{	extbf{T}}$ | Crystal<br>Oscillation<br>Terminal                        | Crystal Oscillator is connected.                                                                                  | With a built-in<br>feedback<br>resistor |

| 6          | ${\tt FG}_{	ext{IN}}$                      | FG Pulse<br>Input<br>Terminal                             | Input terminal for pulse showing motor speed.                                                                     | With a built-in amplifier.              |

| 10         | <sup>33</sup> / <sub>45</sub>              | Speed Switching<br>Terminal                               | Terminal for switching motor speed.<br>L=33 1/3rpm, H or NC=45rpm.                                                | With a built-in pull-up resistor.       |

| 11         | P/S                                        | PLAY/STOP<br>Input Terminal                               | Motor PLAY/STOP signal input terminal L=PLAY, H or NC=STOP                                                        | With a built-in pull-up resistor.       |

| 14         | CP <sub>IN</sub>                           | Reference<br>Frequency<br>Input Terminal                  | Normally connected to CPOUT. For external fine adjustment input from an external oscillator.                      |                                         |

| 15         | CPOUT                                      | Reference<br>Frequency<br>Output Terminal                 | Terminal for divided output from the crystal reference frequency divider. Normally connected to CPIN.             |                                         |

| 13         | STROBE                                     | Strobe Output<br>Terminal                                 | Reference frequency output termianl for strobe. Duty is 1/8.                                                      |                                         |

| 12         | LD                                         | Lock Detecting<br>Terminal                                | This termianl becomes H when the motor speed is within the lock range and otherwise L.                            |                                         |

| 8          | AFC                                        | AFC Output<br>Terminal                                    | Output terminal for motor speed control system. Output of 8bit D/A converter.                                     |                                         |

| 7          | APC                                        | APC Output<br>Terminal                                    | Output terminal for motor phase control system. Output of 8bit D/A converter.                                     |                                         |

| 9          | RV                                         | Reverse Signal<br>Cutput Treminal                         | Terminal for motor reverse signal Output.                                                                         |                                         |

| 4<br>5     | N <sub>1</sub><br>N <sub>2</sub>           | Reference Di-<br>vided Frequency<br>Switching<br>Terminal | Switching of divided frequency from the crystal reference frequency divider into 1/4, 1/32 and 1/128 is possible. | With a built-in pull-up resistor.       |

#### EXPLANATION OF OPERATION

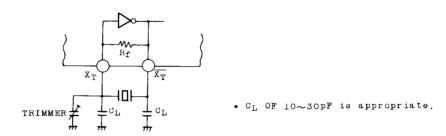

- (1) Crystal oscillation terminals  $(X_T, \overline{X_T})$

- . The crystal oscillator is used by connecting as shown below.

. Crystal oscillation frequency is calculated by the following equation according to number of FG pulses of a motor to be used.

$$f_X = 3/4 \text{ FG'} \times 128 \times 20 \times \text{N} = 5/9 \text{ FG'} \times 128 \times 27 \times \text{N} = 1920 \text{ FG'} \cdot \text{N}$$

(Hz)

(Note) 3/4 FG': FG<sub>IN</sub> frequency at 45rpm.

5/9 FG': FG<sub>IN</sub> frequency at 33 1/3rpm.

Further, fx: Crystal oscillation frequency, FG': No. of FG pulses generated per revolution of motor.

- N : Ratio of frequency division of the crystal reference frequency divider. (Refer to Item (10).)

- . Maximum operating frequency is above 12MHz and crystals up to 12MHz can be used.

- (2) Reference frequency input/output terminals (CPOUT, CPIN)

- . Divided output  $\frac{f_X}{N}$  from the crystal reference frequency divider is available at CP<sub>OUT</sub>, which is normally connected to CP<sub>TN</sub>.

- . When an external oscillator (CR oscillator, etc.) is connected to  $\mbox{CP}_{\mbox{\footnotesize{IN}}},$  motor speed can be finally adjusted.

# TC9142P

- (3) Strobe reference frequency output terminal (STROBE)

- . This is the reference output terminal for strobe and  $\frac{1}{32 \times (20 \text{ or } 27) \times 128}$  of crystal oscillation frequency is available at this terminal.

- . Duty is 1/8 and suited to a single stripe strobe.

- (4) FG pulse input terminal (FGIN)

- . This is the input terminal of FG pulse that shows the motor speed. This FG pulse becomes comparison frequency.

- . This terminal has built-in Amplifier and Schmitt circuit.

FG pulses are applied through capacitor coupling and small amplitude is enough for proper operation.

- (5) Speed switching terminal (33/45)

- . This terminal is for switching the motor speed  $33\ 1/3$  and  $45 \mathrm{rpm}$ , with a pull-up resistor and chattering preventive circuit.

(TRUTH TABLE)

| 33/45   | DIVIDED<br>FREQUENCY | SPEED               |  |

|---------|----------------------|---------------------|--|

| L       | 1<br>27              | $33\frac{1}{3}$ rpm |  |

| H or NC | 20                   | 45rpm               |  |

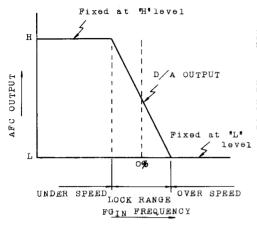

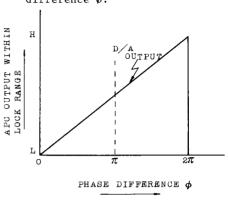

- (6) APC, AFC output terminal (APC, AFC)

- . AFC (speed control output) is a F-V converter for FG frequency, and is consisting of a 8bit D/A converter.

- . APC (phase control output) is a phase comparator (φ-V converter) that compares phase difference φ between 1/2 FG and reference frequency FS', and is also consisting of a 8bit D/A converter.

- . Both APC and AFC perform the following 3 operations according to  ${\tt FG_{TN}}$  frequency.

a. When  ${\rm FG}_{\rm IN}$  frequency is within the lock range: Both APC and AFC perform the normal operation for FGIN. Further, the Lock range is,

$$\begin{cases} \text{at } 45\text{rpm}.....\text{Reference cycle } \frac{1}{\text{FS}} \begin{cases} +4.6 \\ -5.3 \end{cases} \% \\ \text{at } 33 \text{ } 1/3\text{rpm } .....\text{Reference cycle } \frac{1}{\text{FS}} \begin{cases} +3.4 \\ -3.9 \end{cases} \%$$

(Note)

Reference frequency FS=  $\frac{f_X}{N (20 \text{ or } 27) 128} \text{ (Hz)}, \text{ FS'} = \frac{1}{2} \text{ FS}$

- b. When  $FG_{

m IN}$  frequency is below the lock range (under speed): APC and AFC outputs are both fixed at "H" level.

- c. When  $FG_{\mbox{IN}}$  frequency is above the lock range (over speed): APC and AFC outputs are both fixed at "L" level.

- . When a motor is in STOP state (P/S=H or NC), both AFC and APC are fixed "L" level.

AFC Output change status for FGIN frequency

APC Output change status for phase difference  $\phi$ .

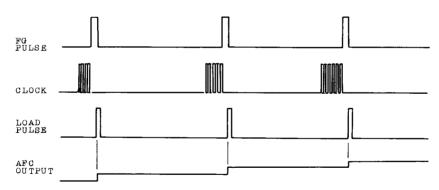

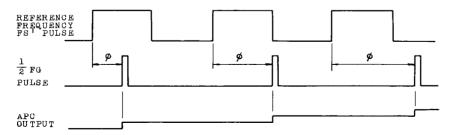

- . AFC and APC timing chart within lock range.

- a. AFC (SPEED CONTROL SYSTEM)

b. APC (PHASE CONTROL SYSTEM)

- (7) Lock detecting terminal (LD)

- . This terminal is the lock detecting output and is placed at "H" level when FG<sub>IN</sub> frequency is within the lock range and otherwise, placed at "L" level.

- (8) PLAY/STOP input terminal (P/S)

- . PLAY/STOP signals of the motor are input to this terminal.  $\label{eq:play-loop} \text{PLAY-L, STOP-H or NC.}$

- . This terminal has a pull-up resistor and a chattering proventive circuit.

- . During PLAY (P/S=L), AFC, APC and LD perform the above-mentioned operations for  $FG_{\rm IN}$  frequency, and during STOP (P/S=H or NC), AFC, APC and LD are all fixed at "L" level.

- (9) Reverse signal output terminal (RV)

- . Reverse signal for braking the motor at time of switching of motor speed

- . from  $45 \mathrm{rpm}$  to  $33~1/3 \mathrm{rpm}$  or the operation from PLAY to STOP is output through this terminal.

- . Change of RV output status

| PREVIOUS STATUS                                                         | RV OUTPUT CHANGE                                          | RV OUTPUT CHANGE TO "L" LEVEL                                                                                                        |

|-------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| During normal rotation (during lock) at 45rpm.                          | When the motor speed is switched from 45rpm to 33 1/3rpm. | When the motor speed is locked at 33 1/3rpm, or When FGIN $\leq$ 1/8 FS, or When the motor speed is switched from 33 1/3rpm to 45rpm |

| During normal ro-<br>tation (during<br>lock) at 33 1/3<br>rpm.or 45rpm. | When the operation is switched from PLAY to STOP.         | When FG $_{IN} \le 1/8\mathrm{FS}$ or When the operation is switched from STOP to PLAY.                                              |

- . In other cases than above, RV output is not changed and fixed at "L" level.

- . Further, if FG frequency rises up to 1.5 times of normal rotation at 45rpm. (2 times of normal rotation at 33rpm), RV output is reset.

# TC9142P

- (10) Reference divided frequency switching terminal (N1, N2)

- . Divided frequency 1/N of the crystal reference frequency divider can be switched to 1/4, 1/32 or 1/128 by number of FG pulses or a crystal used.

- . This terminal has a built-in pull-up resistor.

#### ( TRUTH TABLE )

| N <sub>1</sub> | N2 | $\frac{1}{N}$ | STROBE OUTPUT FREQUENCY                      |

|----------------|----|---------------|----------------------------------------------|

| н              | Н  | 1 32          | f <sub>X</sub> [Hz]  32×(20 or 27)×128       |

| L              | н  | 128           | f <sub>X</sub> (Hz)  32 × (20 or 27) × 128   |

| Н              | Ŀ  | 1 4           | f <sub>X</sub> [Hz]<br>32 × (20 or 27) × 128 |

T : CRISTAL REFERENCE DIVIDED FREQUENCY

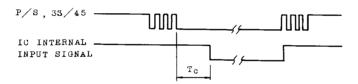

(11) Chattering preventing time of P/S, 33/45 terminal: Tc

| N <sub>1</sub> N <sub>2</sub> | CHATTERING PREVE                              | NTING TIME TC (S)                                                                                          |  |

|-------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

| 12                            | At 33rpm                                      | At 45rpm                                                                                                   |  |

| н                             | 1728                                          | 1280 × (1~2)                                                                                               |  |

| н н                           | f <sub>CPIN</sub> ×(1-2)                      | fCPIN                                                                                                      |  |

| н                             | H 432                                         | 320<br>×(1~2)                                                                                              |  |

|                               | fCPIN                                         | fCPIN                                                                                                      |  |

| ь                             | $\frac{6912}{f_{\rm CPTN}} \times (1 \sim 2)$ | $\frac{5120}{f_{CP_{IN}}} \times (1\sim2)$                                                                 |  |

|                               | N <sub>2</sub> H                              | $N_2$ At 33rpm  H $\frac{1728}{f_{CP_{1N}}} \times (1\sim 2)$ H $\frac{432}{f_{CP_{1N}}} \times (1\sim 2)$ |  |

fCPIN: CPIN INPUT FREQUENCY (Hz)

#### CHARACTERISTIC TEST CIRCUIT

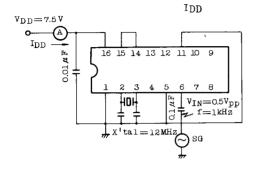

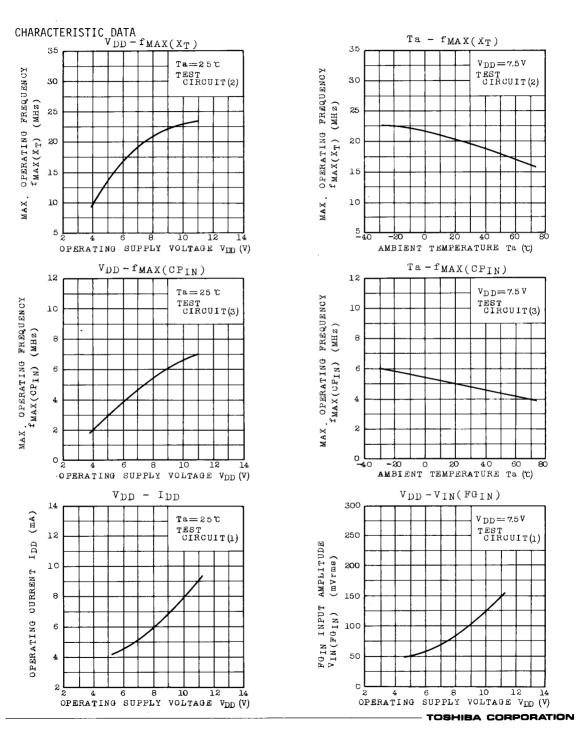

(1) Operating supply current

(2) X<sub>T</sub> Operating frequency range

(3)  $CP_{IN}$  Operating frequency range (4)  $FG_{IN}$  Input sensitivity

MONITOR  $V_{DD} = 5 \sim 9.5 V$ 16 15 14 13 12 11 10 Synchroscope

VIN

X'tal=6MHz

Vin(1),(2)

(5) Amplifier feedback resistor

$v_{DD} = 7.5 \text{ V}$ 16 15 14 13 12 11 10 9  $R_{f} = \frac{7.5}{I_{f}} (\Omega)$

Rf

(6) Pullup resistor

(7) D/A Converter ladder resistor

(8) Output current ("H" level)

VDD=7.5V

Set input so that output may attain "H" level.

IOH

VOH=6.5V

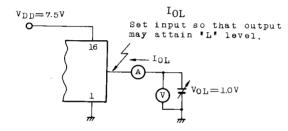

(9) Output current ("L" level)

Example of crystal oscillation frequency calculation

When FG' (number of FG pulse)=90 pulses, if the dividing frequency of reference divider is set at N=32 dividing frequency, the crystal oscillation frequency fx is as follows:

$$f_X = 1920.FG'N = 1920 \times 90 \times 32 = 5,5296MHz$$

#### CAUTION IN APPLICATION

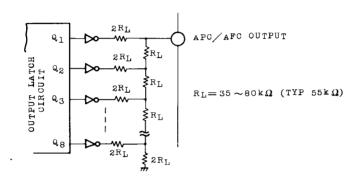

. APC and AFC terminals are for the 8-bit D/A converter outputs, which are directly output from the R-2R ladder type resistor network as shown in the following diagram. Impedance of these outputs becomes equal to the ladder resistor value  $R_{\rm L}$ . Terefore, input impedance at the receiving side of these terminals shall be designed accordingly.

. A filter for an externally mounted differential amplifier on an application circuit shall be selected to meet the response characteristic of a motor to be used.