# SMSxxxAF SMSxxxFF, SMSxxxBF

64 MByte, 128 MByte, 256 MByte 512 MByte and 1 GByte, 3.3V Supply Secure Digital™ Card

### **Features**

- SD Memory Card Specification Version 1.01compliant

- Up to 1 Gbyte of Formatted Data Storage

- Bus Mode

- SD Protocol (1 to 4 Data Lines)

- SPI Protocol

- Operating Voltage Range:

- Basic Communication (CMD0, CMD15, CMD55 and ACMD41): 2.0V to 3.6V

- Other Commands and Memory Access:

2.7V to 3.6V

- Variable Clock Rate: 0 to 25 MHz

- Read Access (using 4 Data Lines)

- Sustained Multiple Block: 6.3 Mb/s

- Write Access (using 4 Data Lines)

- Sustained Multiple Block: 3.0 Mb/s

- Maximum Data Rate with up to 10 Cards

- Aimed at Portable and Stationary Applications

- Communication Channel Protocol Attributes:

- Six-wire communication channel (clock, command, 4 data lines)

- Error-proof data transfer

- Single or Multiple block oriented data transfer

- Memory Field Error Correction

- Safe Card Removal during Read

- Write Protect Feature using Mechanical Switch

- Built-in Write Protection Features (Permanent and Temporary)

- SD, MiniSD and MicroSD Packages

- ECOPACK<sup>®</sup> compliant

- Halogen free

- Antimony free

Table 1. Device summary

| Part Number | Package Form Factor | Operating Voltage Range |

|-------------|---------------------|-------------------------|

| SMS128AF    |                     |                         |

| SMS256AF    | SD (full size)      |                         |

| SMS512AF    | SD (Iuli size)      | 2.7V to 3.6V            |

| SMS01GAF    |                     |                         |

| SMS064BF    | MiniSD              |                         |

| SMS128BF    | Williad             |                         |

| SMS064FF    |                     |                         |

| SMS128FF    | MicroSD             |                         |

| SMS256FF    | WIICIOSE            |                         |

| SMS512FF    |                     |                         |

# **Contents**

| 1 | Desc | cription                 |                                                      |    |  |  |

|---|------|--------------------------|------------------------------------------------------|----|--|--|

| 2 | Mem  | mory array partitioning1 |                                                      |    |  |  |

| 3 | Secu | ure digita               | al memory card interface                             | 13 |  |  |

|   | 3.1  | Secure                   | digital memory card bus topology                     | 15 |  |  |

|   | 3.2  | SD bus                   | protocol                                             | 16 |  |  |

|   | 3.3  | SD Mer                   | mory Card Functional Description                     | 19 |  |  |

|   | 3.4  | Operati                  | on Modes                                             | 19 |  |  |

|   |      | 3.4.1                    | Card Identification Mode                             | 20 |  |  |

|   |      | 3.4.2                    | Data Transfer Mode                                   |    |  |  |

|   | 3.5  | Comma                    | ands                                                 | 23 |  |  |

|   | 3.6  | Respon                   | ises                                                 | 24 |  |  |

| 4 | SD r | nemory (                 | card hardware interface                              | 26 |  |  |

|   | 4.1  | SD mer                   | mory card bus circuitry                              | 26 |  |  |

|   | 4.2  | Power-l                  | Jp                                                   | 27 |  |  |

|   | 4.3  | Hot Inse                 | ertion/Removal                                       | 28 |  |  |

|   | 4.4  | Power F                  | Protection                                           | 28 |  |  |

|   | 4.5  | Electric                 | al Specifications                                    | 28 |  |  |

| 5 | Card | l registe                | rs                                                   | 31 |  |  |

|   | 5.1  | OCR R                    | egister                                              | 31 |  |  |

|   | 5.2  | CID Re                   | gister                                               | 32 |  |  |

|   | 5.3  | CSD Re                   | egister                                              | 33 |  |  |

|   | 5.4  | RCA Re                   | egister                                              | 34 |  |  |

|   | 5.5  | DSR Re                   | egister (Optional)                                   | 34 |  |  |

|   | 5.6  | SCR R                    | egister                                              | 34 |  |  |

| 6 | Timi | ngs                      |                                                      | 35 |  |  |

|   | 6.1  | Comma                    | and and Response                                     | 35 |  |  |

|   |      | 6.1.1                    | Card Identification and Operating Conditions Timings |    |  |  |

|   |      | 6.1.2                    | Card Relative Address Timings                        | 36 |  |  |

|   |      |                          |                                                      |    |  |  |

| 36<br>36<br>37 |

|----------------|

|                |

| 37             |

|                |

| 37             |

| 37             |

| 37             |

| 38             |

| 38             |

| 39             |

| 39             |

| 41             |

| 41             |

| 41             |

|                |

| 42             |

| 42             |

| 43             |

| 43             |

| 44             |

| 44             |

| 45             |

| 45             |

| 46             |

| 46             |

| 46             |

| 46             |

| 46             |

| 46             |

| 47             |

| 47             |

| 48             |

| 48             |

| 48             |

| 48             |

| 48             |

| 50             |

|                |

|          | 7.6.2 Data Write Timings51 |

|----------|----------------------------|

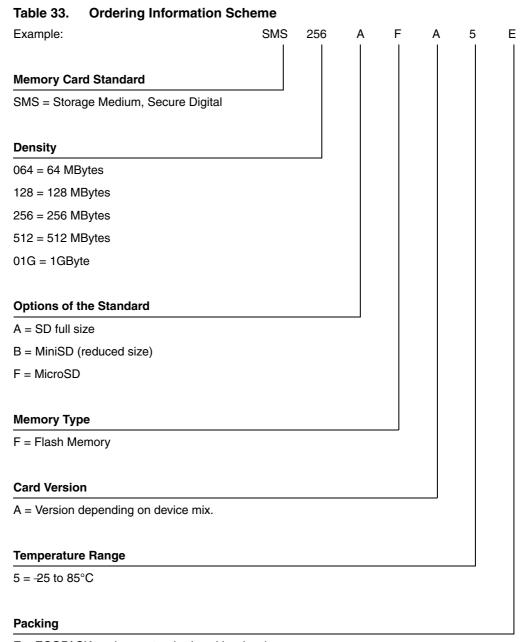

| 8        | Package mechanical data 53 |

| 9        | Part numbering             |

| Appendix | A Power supply decoupling  |

| 10       | Revision history           |

# **List of tables**

| Table 1.  | Device summary                                                            | 1  |

|-----------|---------------------------------------------------------------------------|----|

| Table 2.  | System performance                                                        | 8  |

| Table 3.  | Power consumption                                                         | 9  |

| Table 4.  | Environmental specifications                                              | 9  |

| Table 5.  | Physical dimensions                                                       | 9  |

| Table 6.  | System reliability and maintenance                                        | 10 |

| Table 7.  | Memory array structures                                                   | 11 |

| Table 8.  | Full-size SD Memory Card pin assignment                                   | 13 |

| Table 9.  | MicroSD Contact Pad Assignment                                            |    |

| Table 10. | Card States vs. Operation Modes                                           | 19 |

| Table 11. | SD Card Command Format                                                    | 24 |

| Table 12. | Response R1                                                               | 25 |

| Table 13. | Response R2                                                               | 25 |

| Table 14. | Response R3                                                               | 25 |

| Table 15. | Response R6                                                               |    |

| Table 16. | Bus Operating Conditions                                                  |    |

| Table 17. | Bus Signal Condition - I/O Signal Voltages                                |    |

| Table 18. | Bus Timings                                                               |    |

| Table 19. | SD Memory Card Registers                                                  |    |

| Table 20. | OCR Register Definition                                                   |    |

| Table 21. | CID Fields                                                                |    |

| Table 22. | CSD Fields Compatible with CSD Structure V1 / MM Card Specification V2.11 |    |

| Table 23. | SCR Fields                                                                |    |

| Table 24. | Timing Diagram Symbols                                                    |    |

| Table 25. | Timing Values                                                             |    |

| Table 26. | Command Format                                                            |    |

| Table 27. | Command Classes in SPI Mode                                               |    |

| Table 28. | SPI Timing Symbols                                                        |    |

| Table 29. | SPI Timing Values                                                         |    |

| Table 30. | Full-Size Secure Digital Memory Card Mechanical Data                      |    |

| Table 31. | MiniSD package mechanical data                                            |    |

| Table 32. | MicroSD package mechanical data                                           |    |

| Table 33. | Ordering Information Scheme                                               |    |

| Table 34. | Document Revision History                                                 | 60 |

# **List of figures**

| Figure 1.  | Write Protection hierarchy                                        | 12 |

|------------|-------------------------------------------------------------------|----|

| Figure 2.  | Full size Secure Digital Memory Card form factor                  |    |

| Figure 3.  | MicroSD pin assignment                                            |    |

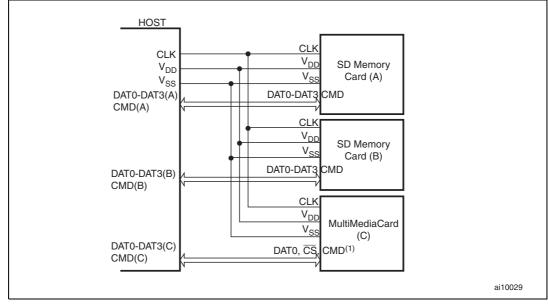

| Figure 4.  | Secure Digital Memory Card system bus topology                    |    |

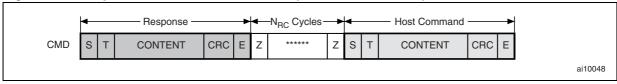

| Figure 5.  | "No Response" and "No Data" operations                            | 17 |

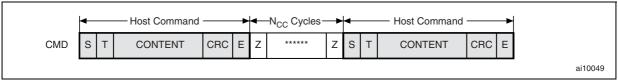

| Figure 6.  | (Multiple) Block Read operation                                   |    |

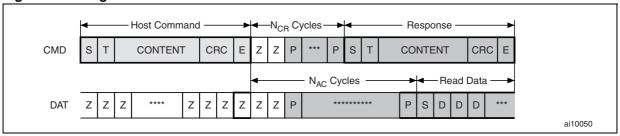

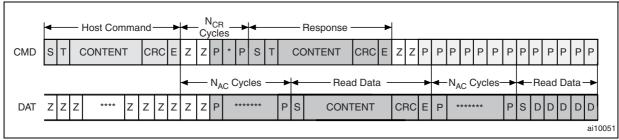

| Figure 7.  | (Multiple) Block Write operation                                  |    |

| Figure 8.  | Command Token format                                              |    |

| Figure 9.  | response token format                                             |    |

| Figure 10. | Data Packet format                                                |    |

| Figure 11. | SD Memory Card State Diagram (Card Identification Mode)           |    |

| Figure 12. | SD Memory Card State Diagram (Data Transfer Mode)                 |    |

| Figure 13. | Full Size SD Memory Card Circuitry                                |    |

| Figure 14. | Power-Up Diagram                                                  |    |

| Figure 15. | Bus Signal levels                                                 |    |

| Figure 16. | Data Input/Output Timings Referenced to Clock                     |    |

| Figure 17. | Identification Sequence                                           |    |

| Figure 18. | SEND_RELATIVE_ADDRESS Command                                     |    |

| Figure 19. | Response (Data Transfer Mode)                                     |    |

| Figure 20. | Response End To Next CMD Start (Data Transfer Mode)               |    |

| Figure 21. | Command Sequence (All Modes)                                      |    |

| Figure 22. | Single Block Read Command                                         |    |

| Figure 23. | Multiple Block Read Command                                       |    |

| Figure 24. | STOP_TRANSMISSION Command (CMD12, Data Transfer Mode)             |    |

| Figure 25. | Block Write Command                                               |    |

| Figure 26. | Multiple Block Write Command                                      | 39 |

| Figure 27. | STOP_TRANSMISSION During Data Transfer From The Host              |    |

| Figure 28. | STOP_TRANSMISSION During CRC Status Transfer From Card            |    |

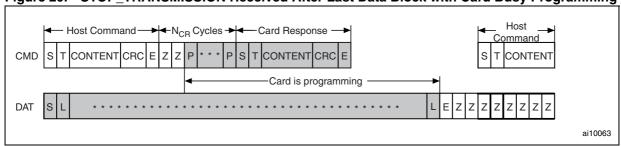

| Figure 29. | STOP_TRANSMISSION Received After Last Data Block with Card Busy . |    |

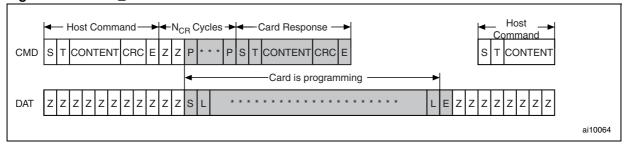

| Figure 30. | STOP_TRANSMISSION Received After Last Data Block with Card Idle   | •  |

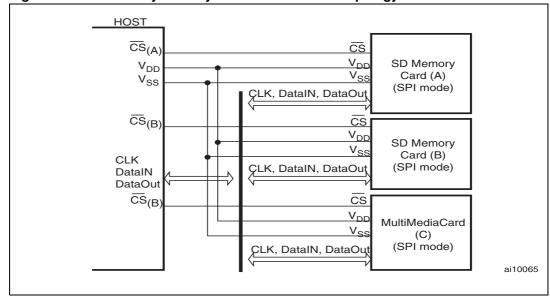

| Figure 31. | SD Memory Card System SPI Mode Bus Topology                       |    |

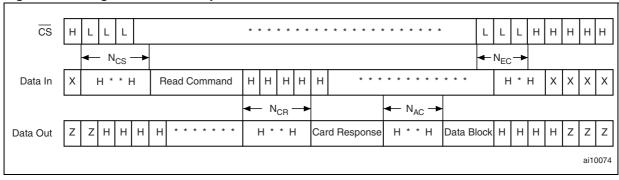

| Figure 32. | Read Operation Mechanism                                          |    |

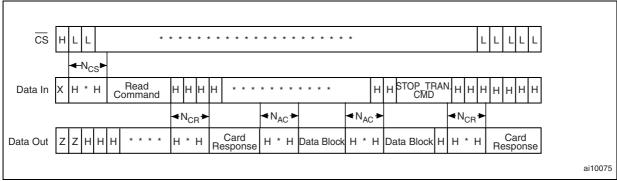

| Figure 33. | Multiple Block Read Operation                                     |    |

| Figure 34. | Read Data Error                                                   |    |

| Figure 35. | Write Operation.                                                  |    |

| Figure 36. | Erase & Write Protect Operations                                  |    |

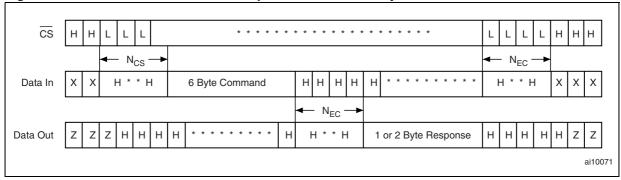

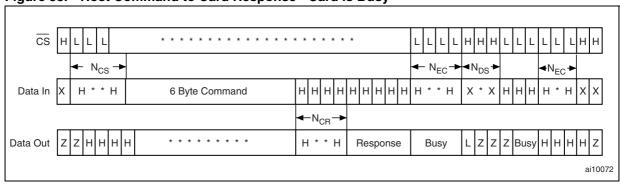

| Figure 37. | Host Command to Card Response - Card is Ready                     |    |

| Figure 38. | Host Command to Card Response - Card is Busy                      |    |

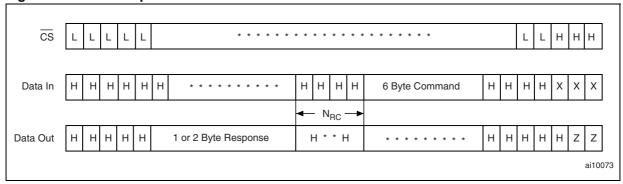

| Figure 39. | Card Response to Host Command                                     |    |

| Figure 40. | Single Block Read Operation                                       |    |

| Figure 41. | STOP_TRANSMISSION between Blocks During Multiple Block Read       |    |

| Figure 42. | STOP_TRANSMISSION within a Block During Multiple Block Read       |    |

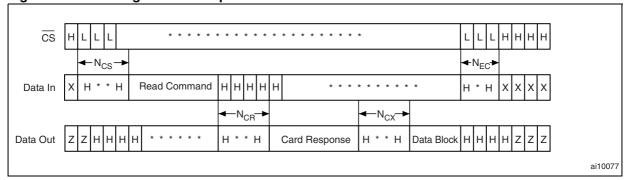

| Figure 43. | CSD Register Read Operation                                       |    |

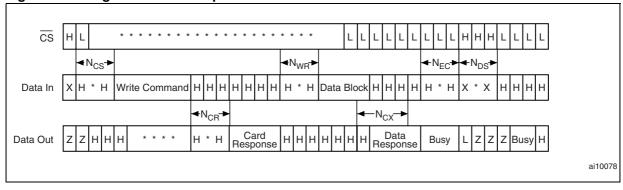

| Figure 44. | Single Block Write Operation                                      |    |

| Figure 45. | Multiple Block Write Operation                                    |    |

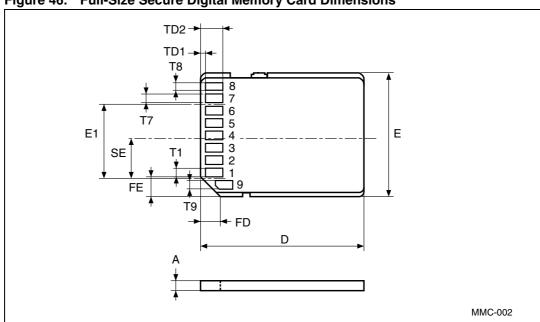

| Figure 46. | Full-Size Secure Digital Memory Card Dimensions                   |    |

| Figure 47. | mini Secure Digital Card Dimensions                               |    |

| Figure 48. | MicroSD card mechanical dimensions                                |    |

| SMSxxxAF, SMSxxxFF, SMSxxxBF |                          | List of figures |

|------------------------------|--------------------------|-----------------|

| Figure 49                    | Power supply decoupling  | 59              |

| i igaio io.                  | Tower supply associating |                 |

N numonyx 7/761

## 1 Description

The Secure Digital Memory Card (SD Memory Card) is a Flash-Based Memory Card. It is specifically designed to meet the security, capacity, performance and environmental requirements of the latest-generation audio and video consumer electronic devices, that is mobile phones, digital cameras, digital recorders, PDAs, organizers, electronic toys, etc.

The Secure Digital Memory Card is a high-mobility, high-performance, low-cost and low-power consumption device that features high data throughput at the memory card interface. It includes a copyright protection mechanism that complies with the security of the SDMI (Secure Digital Music Initiative) standard. The Secure Digital Memory Card security system uses mutual authentication and a "cipher algorithm" that protects the card from illegal use. Unsecured access to the user's personal content is also available.

The Secure Digital Memory Cards have an advanced communication interface designed to operate in a low voltage range. The full-size Secure Digital Memory Card has a 9-pin interface whereas the Mini Secure Digital Memory Card has a 11-pin interface but can be fitted with a 9-pin adapter. Only the 9-pin interface is described in this document. The MicroSD Memory Card has an 8-pin interface, and can also be fitted with a 9-pin adapter.

*Table 2, Table 3, Table 4, Table 5*, and *Table 6* give an overview of the Secure Digital Memory Card features.

In order to meet environmental requirements, the devices are offered in ECOPACK® packages. ECOPACK packages are Lead-free. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

The SD, MiniSD and MicroSD packages are also Halogen free and Antimony free.

#### **Related documentation**

- Secure Digital Memory Card Specifications: Part 1 Physical Layer Specification, Version 1.01

- MiniSd Memory Card Specifications: Addendum to SD Memory Card Specifications Part 1 Physical layer Specification, Version 1.02

- MicroSD Memory Card Specifications: Addendum to SD Memory Card Specifications Part 1, Physical Layer Specification, Version 1.00

Table 2. System performance

| System performance                            | Max. | Тур.      | Unit     |

|-----------------------------------------------|------|-----------|----------|

| Sleep to Ready                                | 30   |           | μs       |

| Sustained Multiple Block Read <sup>(1)</sup>  |      | 6.3 (43X) | MBytes/s |

| Burst Single Block Read <sup>(1)</sup>        |      | 1.8 (12X) | MBytes/s |

| Sustained Multiple Block Write <sup>(1)</sup> |      | 3.0 (20X) | MBytes/s |

| Burst Single Block Write <sup>(1)</sup>       |      | 0.8 (5X)  | MBytes/s |

| Power-up to Ready                             | 150  |           | ms       |

<sup>1. 43</sup>X, 20X, 12X and 5X Speed grade markings where 1X = 150 KBytes/s.

Table 3. Power consumption<sup>(1)</sup>

| Mode    | Max. Current Consumption |

|---------|--------------------------|

| Standby | 200 μΑ                   |

| Read    | 30 mA                    |

| Write   | 30 mA                    |

<sup>1.</sup> T<sub>A</sub>= 25°C, V<sub>DD</sub>= 3.6V.

Table 4. Environmental specifications<sup>(1)</sup>

| Environmental specifications |                | Operating        | Non-Operating                                              |                                 |

|------------------------------|----------------|------------------|------------------------------------------------------------|---------------------------------|

| Temperature                  |                | –25°C to<br>85°C | −40°C to 85°C                                              |                                 |

| Humidity (nor                | n- condensing) | NA               | 85°C - 85%RH                                               |                                 |

|                              | Contact Pads   | NA               | ±4kV, Human body model according to ANSI EOS/ESD-S5.1-1998 |                                 |

| ESD<br>Protection            | Other          |                  |                                                            | ±8kV (coupling plane discharge) |

|                              |                |                  | ±15kV (air discharge) Human body model per IEC61000-4-2    |                                 |

| Salt Water Spray             |                | NA               | T <sub>A</sub> = 35 °C 3% NaCl (MIL Std Method 1009)       |                                 |

| Vibration (pea               | ak-to-peak)    | NA               | 15 Gmax                                                    |                                 |

| Shock                        |                | NA               | 1,000G                                                     |                                 |

| Drop                         |                |                  | 2000G                                                      |                                 |

| Bending                      |                | NA               | 20N (middle of the card)                                   |                                 |

|                              |                | INA              | 20N (border of the card)                                   |                                 |

| UV light exposure            |                |                  | 254nm, 15Ws/cm2                                            |                                 |

<sup>1.</sup> NA = Not Applicable; RH = Relative Humidity; ESD = ElectroStatic Discharge

Table 5. Physical dimensions

| Parameter      | SD        | MiniSD    | MicroSD                       | Unit |

|----------------|-----------|-----------|-------------------------------|------|

| Width          | 24        | 20        | 11                            | mm   |

| Height         | 32        | 21.5      | 15                            | mm   |

|                |           |           | Inter Connect<br>Area 0.7±0.1 |      |

| Thickness      | 2.1       | 1.4       | Max. Card<br>Thickness 0.95   | mm   |

|                |           |           | Max. Pull Area<br>1.0±0.1     |      |

| Weight         | Approx. 2 | Approx. 1 | <1                            | g    |

| Number of Pins | 9         | 11        | 8                             | N/A  |

Table 6. System reliability and maintenance

| MTBF <sup>(1)</sup>    | >1,000,000hrs                                      |  |

|------------------------|----------------------------------------------------|--|

| Preventive Maintenance | None                                               |  |

| Data Reliability       | 1 non-recoverable bit in 10 <sup>14</sup> bit read |  |

| Endurance              | >2,000,000 Program/Erase Cycles                    |  |

<sup>1.</sup> MTBF = Mean Time Between Failures.

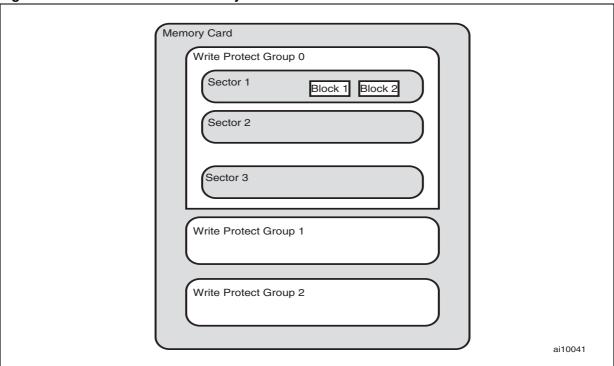

# 2 Memory array partitioning

The basic unit of data transfer to/from the SD Memory Card is the Byte. The memory array is divided into several structures as described below and summarized in *Table 17*.

#### **Block**

The Block is the unit structure related to block-oriented read and write commands. Its size is the number of Bytes that are transferred when a block-oriented read or write command is sent by the host. The SD Memory Card Block size is either programmable or fixed. The information about allowed block sizes and programmability is stored in the CSD Register. The details of the Memory Array Structure and the number of addressable Blocks are shown in *Table 17*.

#### Sector

The sector is the unit structure related to the erase commands. Its size is the number of blocks that are erased at any one time. The sector size is fixed for each device. The information about the sector size (in blocks) is stored in the CSD register.

### **Write Protect Group (WP-Group)**

The WP-Group is the smallest structure that may be individually protected. Its size is the number of Sectors that are Write Protected with one bit. The information about the Write Protect Group size is stored in the CSD Register.

Table 7. Memory array structures

| Type of<br>Structure | Number of structures in device |                     |                     |                      |                      |                      |                    |  |  |

|----------------------|--------------------------------|---------------------|---------------------|----------------------|----------------------|----------------------|--------------------|--|--|

|                      | Unit                           | 32 MByte<br>Devices | 64 MByte<br>Devices | 128 MByte<br>Devices | 256 MByte<br>Devices | 512 MByte<br>Devices | 1 GByte<br>Devices |  |  |

| Blocks               | 512 Bytes                      | 59776               | 122624              | 248320               | 499712               | 1002496              | 1999872            |  |  |

| Sector               | Block                          | 128                 | 128                 | 128                  | 128                  | 128                  | 128                |  |  |

| WP-Groups            | Sector                         | 1                   | 2                   | 4                    | 8                    | 16                   | 32                 |  |  |

Write Protection hierarchy Figure 1.

## 3 Secure digital memory card interface

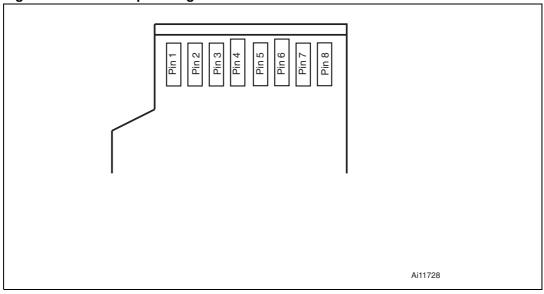

This section applies to the full-size SD Memory Card only, or to the MiniSD and MicroSD card when used with an adapter.

Details on the 11-pin communication interface of the MiniSD card used without an adapter are still to be announced. *Figure 3: MicroSD pin assignment* shows the MicroSD pinout.

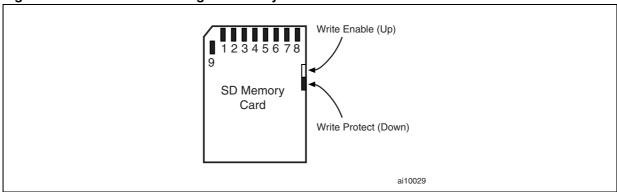

The Secure Digital Memory Card has an advanced 9-pin communication interface (Clock, Command, 4 Data pins and 3 Power Supply pins) designed to operate in a low voltage range. The Secure Digital Card has its nine pins exposed on one side (see *Figure 2*). The signal/pin assignments are listed in *Table 8* The pin types are Power Supply, Input, Output and Push-Pull. The signals include six communication lines CMD, DAT0, DAT1, DAT2, DAT3, CLK and three supply lines  $V_{DD}$ ,  $V_{SS1}$  and  $V_{SS2}$ .

Figure 2. Full size Secure Digital Memory Card form factor

Table 8. Full-size SD Memory Card pin assignment

| Pin #  |                        | SD mode               |                                 |                  | SPI mode |                          |  |  |  |

|--------|------------------------|-----------------------|---------------------------------|------------------|----------|--------------------------|--|--|--|

| FIII # | Name                   | Type <sup>(1)</sup>   | Description                     | Name             | Туре     | Description              |  |  |  |

| 1      | CD/DAT3 <sup>(2)</sup> | I/O/PP <sup>(3)</sup> | Card Detect / Data Line [Bit 3] | CS               | I        | Chip Select (active Low) |  |  |  |

| 2      | CMD                    | PP                    | Command/Response                | DI               | I        | Data In                  |  |  |  |

| 3      | V <sub>SS1</sub>       | S                     | Supply voltage ground           | $V_{SS}$         | S        | Supply voltage ground    |  |  |  |

| 4      | $V_{DD}$               | S                     | Supply voltage                  | $V_{DD}$         | S        | Supply voltage           |  |  |  |

| 5      | CLK                    | I                     | Clock                           | SCLK             | I        | Clock                    |  |  |  |

| 6      | $V_{SS2}$              | S                     | Supply voltage ground           | V <sub>SS2</sub> | S        | Supply voltage ground    |  |  |  |

| 7      | DAT0                   | I/O/PP                | Data Line [Bit 0]               | DO               | O/PP     | Data Out                 |  |  |  |

| 8      | DAT1 <sup>(2)</sup>    | I/O/PP                | Data Line [Bit 1]               | Reserved         |          |                          |  |  |  |

| 9      | DAT2 <sup>(2)</sup>    | I/O/PP                | Data Line [Bit 2]               | Reserved         |          |                          |  |  |  |

<sup>1.</sup> S: power supply; I: input; O: output using push-pull drivers; PP: I/O using push-pull drivers.

<sup>2.</sup> The extended DAT lines (DAT1-DAT3) are input on power-up. They start to operate as DAT lines after SET\_BUS\_WIDTH command.

After power-up this line is input with 50kW pull-up (can be used for card detection or SPI mode selection). The pull-up should be disconnected by the user, during regular data transfer, with SET\_CLR\_CARD\_DETECT (ACMD42) command.

Figure 3. MicroSD pin assignment

Table 9. MicroSD Contact Pad Assignment

| Pin  |                            | s                   | D Mode                             |          |      | SPI Mode               |

|------|----------------------------|---------------------|------------------------------------|----------|------|------------------------|

| PIII | Name                       | Type <sup>(1)</sup> | Description                        | Name     | Туре | Description            |

| 1    | DAT2                       | I/O/PP              | Data Line [Bit 2]                  | RSV      |      | Reserved               |

| 2    | CD/DA<br>T3 <sup>(2)</sup> | I/O/PP<br>(3)       | Card Detect / Data Line<br>[Bit 3] | CS       | I    | Chip Select (neg true) |

| 3    | CMD                        | PP                  | Command/Response                   | DI       | I    | Data In                |

| 4    | $V_{DD}$                   | S                   | Supply voltage                     | $V_{DD}$ | S    | Supply voltage         |

| 5    | CLK                        | I                   | Clock                              | SCLK     | I    | Clock                  |

| 6    | $V_{SS}$                   | S                   | Supply voltage ground              | $V_{SS}$ | S    | Supply voltage ground  |

| 7    | DAT0                       | I/O/PP              | Data Line [Bit 0]                  | DO       | O/PP | Data Out               |

| 8    | DAT1                       |                     |                                    | RSV      |      | Reserved               |

- 1. S: power supply; I: input; O: output using push-pull drivers; PP: I/O using push-pull drivers.

- 2. The extended DAT lines (DAT1-DAT3) are input on power up. They start to operate as DAT lines after SET\_BUS\_WIDTH command. The Host shall keep its own DAT1-DAT3 lines in input mode, as well, while they are not used. It is defined so, in order to keep compatibility to MultiMediaCards.

- After power up this line is input with 50KOhm pull-up (can be used for card detection or SPI mode selection). The pull-up should be disconnected by the user, during regular data transfer, with SET\_CLR\_CARD\_DETECT (ACMD42) command.

## 3.1 Secure digital memory card bus topology

The Secure Digital Memory Card system defines two alternative communications protocols: SD and SPI that correspond to two operating modes.

Either mode can be selected in the application, mode selection is transparent to the host. The host automatically detects the operating mode of the card by issuing the Reset command (refer to *Section 7.2.1: Mode Selection*) and will expect all further communications to use the same mode. Therefore, applications that use only one communication mode do not have to be aware of the other.

The SD bus includes the following signals:

- CLK: Host to card clock signal

- CMD: Bi-directional Command/Response signal

- DAT0 DAT3: 4 Bi-directional data signals.

- V<sub>DD</sub>, V<sub>SS1</sub>, V<sub>SS2</sub>: Power and ground signals.

The SD Memory Card bus has a synchronous star topology (refer to *Figure 4: Secure Digital Memory Card system bus topology*) with a single master (the application) and multiple slaves (the cards). The Clock, power and ground signals are common to all cards. The command (CMD) and data (DATO - DAT3) signals are dedicated to the cards, they provide continuous point-to-point connection to all the cards.

During the initialization process, commands are sent to each card individually, allowing the application to detect the cards and assign logical addresses to the physical slots. Data is always sent (received) to (from) each card individually. However, in order to simplify the handling of the card stack, after the initialization process, all commands may be sent concurrently to all cards. Addressing information is provided in the command packet.

The SD bus allows dynamic configuration of the number of data lines. After power-up the SD Memory Card defaults to using only DAT0 for data transfer. After initialization the host can change the bus width (number of active data lines). This feature is an easy trade off between hardware cost and system performance.

Figure 4. Secure Digital Memory Card system bus topology

DAT1 and DAT2 not connected.

## 3.2 SD bus protocol

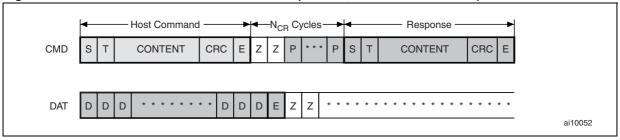

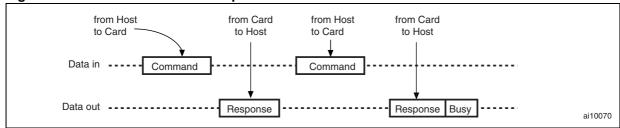

Communication over the SD bus is based on command and data bit streams which are initiated by a start bit and terminated by a stop bit.

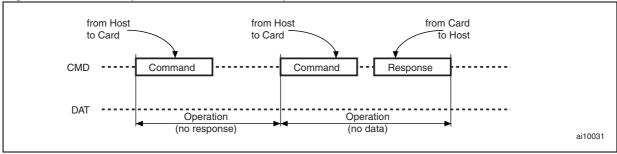

- Command: a command is a token which starts an operation. A command is sent from

the host either to a single card (addressed command) or to all connected cards

(broadcast command). Commands are transferred serially on the CMD line. See

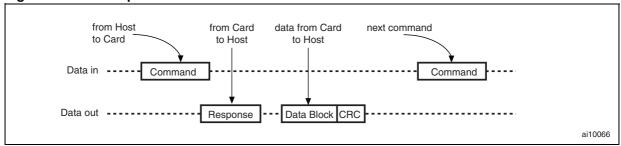

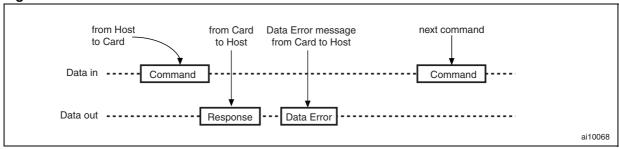

Figure 5: "No Response" and "No Data" operations.

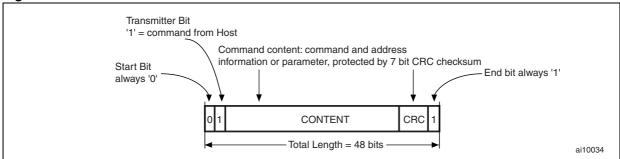

The Command token format is shown in Figure 8

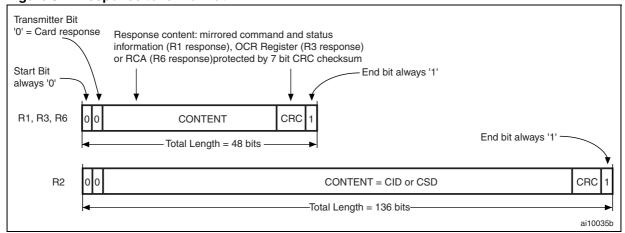

- Response: a response is a token which is sent from an addressed card, or (simultaneously) from all connected cards, to the host, as an answer to a previously received command. Responses are transferred serially on the CMD line. A response is illustrated in *Figure 5: "No Response" and "No Data" operations*.

The Response token format is shown in *Figure 9*

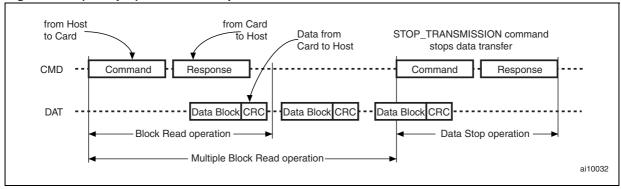

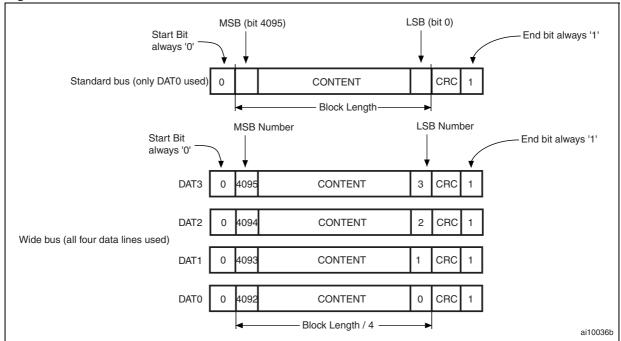

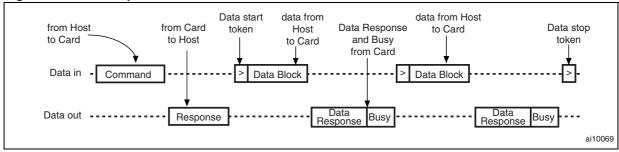

- **Data:** data can be transferred from the card to the host or from the host to the card. Data is transferred via the data lines. See *Figure 6: (Multiple) Block Read operation* for an illustration.

- The Data Packet format is shown in Figure 10

Card addressing is implemented using a session address assigned to the card during the initialization phase (See SD Memory Card Specification, Chapter 4). The basic transaction on the SD bus is the command/response transaction. In this type of bus transactions, the information is directly transferred within the command or response structure. In addition, some operations have a data token. Data transfers to/from the SD Memory Card are done in blocks. Data blocks are always followed by CRC bits.

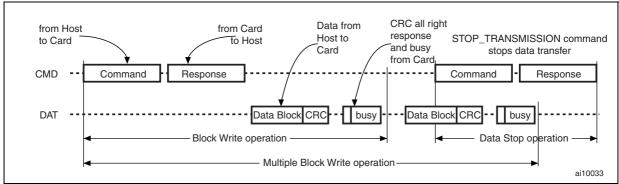

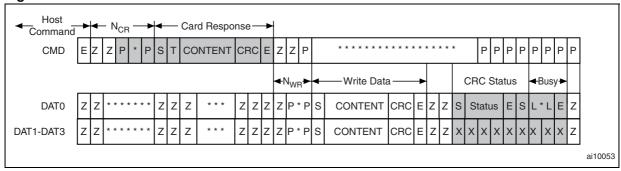

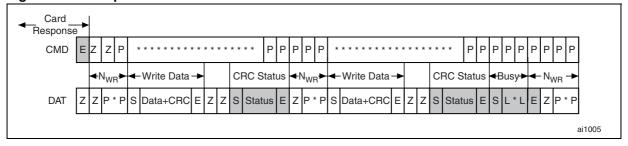

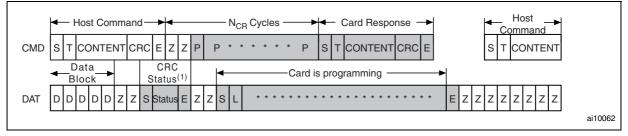

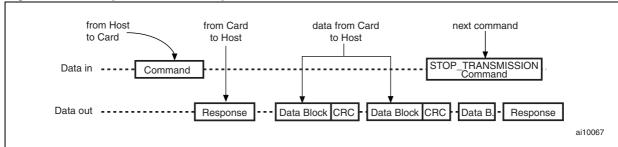

Single and Multiple Block operations are supported. Note that the Multiple Block operation mode improves the speed of write operations. A Multiple Block transmission is terminated by issuing a STOP\_TRANSMISSION command on the CMD line (See *Figure 6* and *Figure 7*).

Data transfer can be configured by the host to use single or multiple data lines (provided that the card supports this feature).

A busy signal on DAT0 is used to indicate that a Block Write operation is ongoing (see *Figure 7*). The same busy signaling is used regardless of the number of data lines used to transfer the data.

Response tokens (see *Figure 9*) have four coding schemes depending on their content. The token length is either 48 or 136 bits (See SD Memory Card Specification, Chapter 4.5 for detailed definitions of the commands and responses). The CRC protection algorithm for data block is a 16-bit CCITT polynomial (see SD Memory Card Specification, chapter 4.5).

On the CMD line, the MSB bit is transmitted first and the LSB bit last. When the wide bus option is used, the data is transferred 4 bits at a time (refer to *Figure 10*). Start bits, End bits and CRC bits, are transmitted on all the DAT lines used. CRC bits are calculated and checked for every DAT line individually. The CRC status response and Busy indication are sent by the card to the host on DATO only (DAT1-DAT3 are Don't Care).

Figure 5. "No Response" and "No Data" operations

Figure 6. (Multiple) Block Read operation

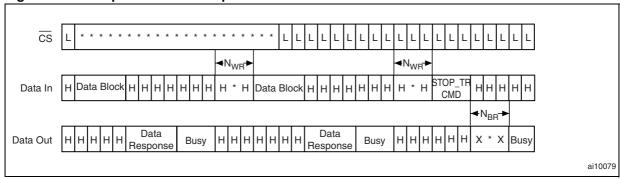

Figure 7. (Multiple) Block Write operation

Figure 8. Command Token format

Figure 9. response token format

Figure 10. Data Packet format

## 3.3 SD Memory Card Functional Description

All communications between the host and the cards are controlled by the host (master).

The host sends commands of two types:

- **Broadcast commands** which are intended for all cards. Some of these commands require a response.

- Addressed (point-to-point) commands that are sent to the addressed card and are followed by a response from the card.

## 3.4 Operation Modes

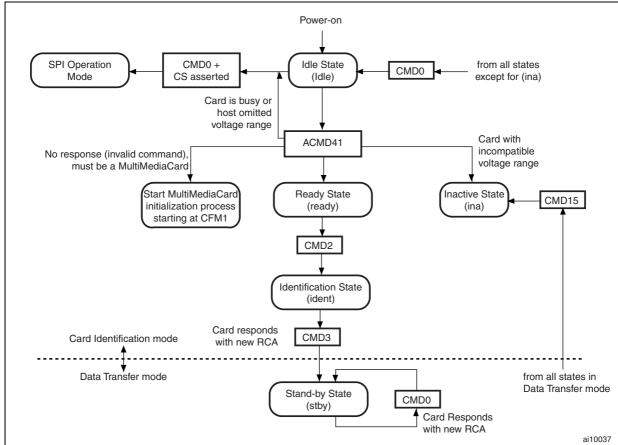

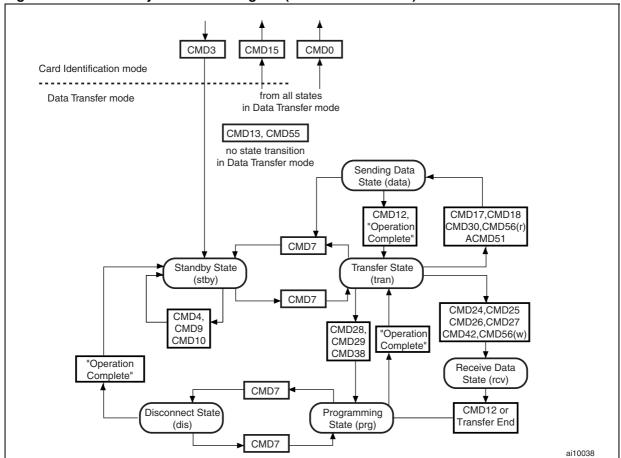

*Figure 11* and *Figure 12* show an overview of the command flow for the Card Identification mode and the Data Transfer mode, respectively.

*Table 10* shows the relationship between operation modes and card states. Each state in the SD Memory Card state diagram (see *Figure 16* and *Figure 17*) is associated with one operation mode.

Table 10. Card States vs. Operation Modes

| Card state           | Operation mode           |

|----------------------|--------------------------|

| Inactive State       | Inactive                 |

| Idle State           |                          |

| Ready State          | Card Identification Mode |

| Identification State |                          |

Card state

Stand-by State

Transfer State

Sending-data State

Receive-data State

Programming State

Disconnect State

Table 10. Card States vs. Operation Modes (continued)

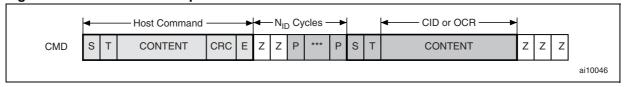

#### 3.4.1 Card Identification Mode

The host enters the Card Identification mode after reset and remains in this mode until it has finished searching for new cards on the bus.

Cards enter the Card Identification mode after reset and remain in this mode until they receive the SEND\_RCA command (CMD3) (or the SET\_RCA command for MultiMediaCards).

While in Card Identification mode the host resets all the cards that are in Card Identification mode, validates the operation voltage range, identifies every card and asks them to publish their Relative Card Addresses (RCA). This operation is done separately for each card on its own CMD line. In this mode, all data communications use the command line (CMD) only.

The host starts the card identification process at the identification clock rate  $f_{OD}$ . The SD Memory Card has push-pull CMD line output drives.

Once the bus has been activated the host asks each card to send their valid operation conditions (ACMD41 preceded by APP CMD - CMD55 with RCA=0000h).

The response to ACMD41 is the Operation Condition Register of the card. The same command is sent to all the new cards in the system. Incompatible cards are switched to Inactive State.

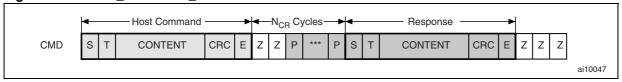

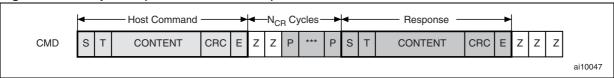

The host then issues the ALL\_SEND\_CID command (CMD2), to every card to get their unique card identification (CID) numbers. All unidentified cards (which are in Ready State) answer by sending their CID numbers (on the CMD line) and switch to the Identification State. Then the host issues a CMD3 (SEND\_RELATIVE\_ADDR) command to ask the cards to publish a relative card address (RCA). The RCA is shorter than the CID, and will be used to address the card (typically at a clock rate higher than  $f_{\text{OD}}$ ) once this is in Data Transfer mode. Once the RCA is received the card state changes to Standby. At this point, the host may ask the card to publish another RCA number by sending another SEND\_RELATIVE\_ADDR command to the card. The last published RCA is the actual RCA of the card.

The host repeats the identification process, that is the cycles with CMD2 and CMD3, for each card in the system. Once all the SD Memory Cards have been initialized, the host initializes the MultiMediaCards that are in the system (if any) by issuing CMD2 and CMD3 as explained in the MultiMediaCard specification. Note that in the SD system all the cards are connected separately so each MultiMediaCard has to be initialized individually.

Figure 11. SD Memory Card State Diagram (Card Identification Mode)

#### 3.4.2 Data Transfer Mode

Cards enter the Data Transfer mode once their Relative Card Addresses (RCA) have been published.

The host enters the Data Transfer mode after identifying all the cards on the bus.

The host issues SEND\_CSD (CMD9) to obtain the contents of the Card Specific Data (CSD) Register for each card. The CSD Register contains information like the block length and the card storage.

Until the host knows the contents of all the CSD Registers, the  $f_{PP}$  clock rate must remain at  $f_{OD}$  because some cards may have operating frequency limitations.

The broadcast command SET\_DSR (CMD4) configures the driver stages of all identified cards. It programs their Driver Stage Registers (DSR) according to the application bus layout (length), the number of cards on the bus and the data transfer frequency. The clock rate is changed from  $f_{OD}$  to  $f_{PP}$  at that point. The SET\_DSR command is an option for the card and the host.

CMD7 is used to select one card and switch it to the Transfer State. Only one card can be in Transfer State at a given time. If a previously selected card is still in Transfer State when the host uses CMD7 to switch another card to the Transfer state, then the connection between the previously selected card and the host is released and the card reverts to the Standby State.

When CMD7 is issued with the reserved relative card address "0000h", all cards revert to the Standby State. This function may be used before identifying new cards, to avoid resetting already registered cards. When in Standby state the cards that already have an RCA do not respond to identification commands (CMD41, CMD2, CMD3).

Note that a card is deselected when it receives a CMD7 with an RCA that does not match. Card deselection is automatic if another card in a system is selected and the cards share the same CMD lines.

So, in an SD Memory Card system, the host may either have a common CMD line for all SD Memory Cards (in which case card deselection is automatic just like in a MultiMediaCard system) or the host may have separate CMD lines, in which case it must be aware of the necessity of deselecting cards.

All data communications in the Data Transfer Mode are point-to point between the host and the selected card (using addressed commands). All addressed commands are acknowledged by a response on the CMD line.

The relationships between the various states in the Data Transfer mode are summarized below (see *Figure 12*):

- All Data Read commands (CMD17, CMD18, CMD30, CMD56, ACMD51) can be aborted at any time using the Stop command (CMD12). The data transfer will terminate and the card will return to the Transfer State.

- All Data Write commands (CMD24,CMD25, CMD26, CMD27, CMD42, CMD56) can be aborted at any time using the Stop command (CMD12). The write commands must be stopped prior to deselecting the card using CMD7.

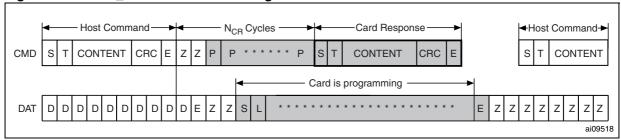

- As soon as the data transfer has completed, the card switches from the Data Write state to either the Programming state (if the transfer was successful) or the Transfer state (if the transfer failed).

- If a Block Write operation is stopped and the block length and CRC of the last block are valid, the data will be programmed.

- The card can provide buffering during Block Write. This means that the data to be programmed to the next block can be sent to the card while the previous block is being programmed.

If all write buffers are full, the DAT0 line will remain Low (BUSY) as long as the card is in the Programming state (see *Figure 12*).

- There is no buffering option for Write CSD, Write CID, Write Protection and erase. This

means that while the card is busy with any one of these commands, no other Data

Transfer command will be accepted. The DATO line will remain Low as long as the card

is busy and in the Programming state.

- Parameter Set commands (CMD16, CMD32, CMD33) are not allowed while the card is programming.

- Read commands are not allowed while the card is programming.

- Switching another card from the Standby to the Transfer state (using CMD7) will not terminate erase and programming operations. The card will switch to the Disconnect state and release the DAT line.

- A card in the Disconnect state can be reselected using CMD7. The card will then revert to the Programming state and reactivate the busy signaling.

- Resetting a card (using CMD0 or CMD15) will terminate any pending or ongoing programming operation. This may result in the loss of card contents. It is up to the host to prevent possible data loss.

Figure 12. SD Memory Card State Diagram (Data Transfer Mode)

### 3.5 Commands

Four types of commands are used to control the SD Memory Card:

- Broadcast commands (bc), no response: The broadcast feature is available only if all the CMD lines are interconnected at the level of the host. If they are not interconnected then each individual card will accept the command in turn.

- 2. **Broadcast commands with response (bcr):** Since there is no Open Drain mode in SD Memory Cards, this type of command is used only if the host does not use a common CMD line. The command is accepted by every individual Card and the responses from all cards are sent simultaneously.

- 3. addressed (point-to-point) commands (ac): There is no data transfer on DAT.

- 4. **addressed (point-to-point) data transfer commands (adtc):** There is a data transfer on DAT.

All commands have a fixed code length of 48 bits for a transmission time of 2.4µs at 20MHz. All commands and responses are sent over the CMD line of the SD Memory Card. Command transmission always starts with the most significant bit (MSB) of the command codeword. All commands are protected by a CRC. All Command codewords are terminated by the end bit (always '1'). *Table 11* shows the command format. All commands and their arguments are specified in the SD Memory Card Specification.

Table 11. SD Card Command Format

| Bit position | 47        | 46               | 45:40         | 39:8     | 7:1  | 0       |

|--------------|-----------|------------------|---------------|----------|------|---------|

| Width        | 1         | 1                | 6             | 32       | 7    | 1       |

| Value        | '0        | "1               | 'X            | Х        | Х    | '1'     |

| Description  | Start bit | Transmission bit | Command index | Argument | CRC7 | End bit |

## 3.6 Responses

All responses are sent via the command line CMD. Response transmission always starts with the leftmost bit of the response codeword. The code length depends on the response type. A response always starts with a start bit (always '0'), followed by the bit indicating the direction of transmission (from card = '0').

A value denoted by 'X' in *Table 12*, *Table 13*, *Table 14* and *Table 15* indicates a variable entry.

All responses (except for R3 Responses) are protected by a CRC. All response codewords are terminated by the end bit (always '1').

There are five types of responses. Their formats are defined as follows:

- 1. **R1 (normal response command):** the code length is 48 bits. Bits 45 to 40 indicate the index of the command to respond to. The index is a binary coded number (between 0 and 63). The status of the card is coded in 32 bits (see *Table 12*).

- Note that if data transfer to the card takes place, then a busy signal may appear on the data line after the transmission of each block of data. The host has to check for busy after data block transmission.

- 2. **R1b** is identical to R1 with an optional busy signal transmitted on the data line. The card may become busy after receiving these commands, depending on the state it was in prior to receiving the command. The Host has to check for busy in the response.

- 3. **R2 (CID, CSD Register):** the code length is 136 bits. The contents of the CID Register are sent as a response to the CMD2 and CMD10 commands. The contents of the CSD Register are sent as a response to CMD9. Only the bits [127...1] of the CID and CSD Registers are transferred, the reserved bit [0] of these registers is replaced by the end bit of the response (see *Table 13*).

- 4. **R3 (OCR register):** the code length is 48 bits. The contents of the OCR register are sent as a response to ACMD41 (see *Section Table 14. on page 25*).

- 5. **R6 (Published RCA response):** the code length is 48 bits. Bits 45 to 40 indicate the index of the command to respond to. In this case it is '000011' (together with bit 5 in the status bits it means = CMD3) as shown in *Table 15* The 16 MSB bits of the argument field are used for the Published RCA number.

For more details about Response formats, please refer to the SD Memory Card Specification.

Table 12. Response R1

| Bit Position | 47          | 46                  | [45:40]          | [39:8]      | [7:1] | 0          |

|--------------|-------------|---------------------|------------------|-------------|-------|------------|

| Width (bits) | 1           | 1                   | 6                | 32          | 7     | 1          |

| Value        | <b>'</b> 0' | '0'                 | Х                | Х           | Х     | <b>'1'</b> |

| Description  | Start Bit   | Transmission<br>Bit | Command<br>Index | Card Status | CRC7  | End Bit    |

### Table 13. Response R2

| Bit Position | 135       | 134              | [133:128] | [127:1]                                       | 0       |

|--------------|-----------|------------------|-----------|-----------------------------------------------|---------|

| Width (bits) | 1         | 1                | 6         | 127                                           | 1       |

| Value        | '0'       | '0'              | '111111'  | Х                                             | '1'     |

| Description  | Start Bit | Transmission Bit | Reserved  | CID or CSD<br>register incl.<br>internal CRC7 | End Bit |

### Table 14. Response R3

| Bit Position | 47        | 46                  | [45:40]  | [39:8]       | [7:1]    | 0       |

|--------------|-----------|---------------------|----------|--------------|----------|---------|

| Width (bits) | 1         | 1                   | 6        | 32           | 7        | 1       |

| Value        | '0'       | '0'                 | '111111' | Х            | '111111' | '1'     |

| Description  | Start Bit | Transmission<br>Bit | Reserved | OCR Register | Reserved | End Bit |

### Table 15. Response R6

| Bit Position | 47          | 46                   | [45:40]                        | [39:8] Argu                                    | ıment Field                                              | [7:1] | 0       |

|--------------|-------------|----------------------|--------------------------------|------------------------------------------------|----------------------------------------------------------|-------|---------|

| Width (bits) | 1           | 1                    | 6                              | 16                                             | 16                                                       | 7     | 1       |

| Value        | <b>'</b> 0' | '0'                  | Х                              | Х                                              | Х                                                        | Х     | '1'     |

| Description  | Start Bit   | Transmissio<br>n Bit | Command<br>Index<br>('000011') | New<br>published<br>RCA [31:16]<br>of the card | [15:0] Card<br>Status Bits:<br>23, 22, 19<br>and 12 to 0 | CRC7  | end bit |

#### SD memory card hardware interface 4

#### SD memory card bus circuitry 4.1

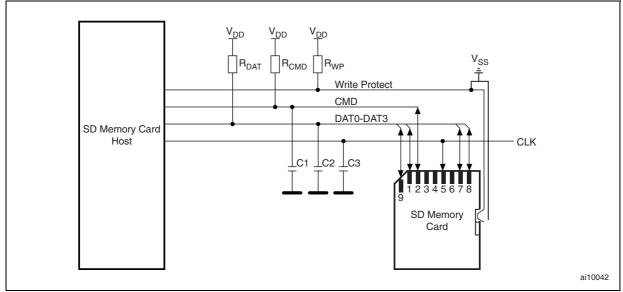

Figure 13 shows the internal bus circuitry required for the Full Size SD Memory Card.

The SD Memory Card may also feature two additional contacts, that are not part of the internal circuitry. When present in the device, these contacts are located at the level of the Write Protect/Card Detect switch in the socket, and should be connected as illustrated in Figure 13.

When DAT3 is used for card detection, the R<sub>DAT</sub> resistor connected to DAT3 should be disconnected and another resistor should be connected to Ground.

R<sub>DAT</sub> and R<sub>CMD</sub> are pull-up resistors used to protect the DAT and CMD lines, respectively, against bus floating when no card is inserted or when all card drivers are high impedance. R<sub>WP</sub> is used to protect the Write Protect/Card Detection switch.

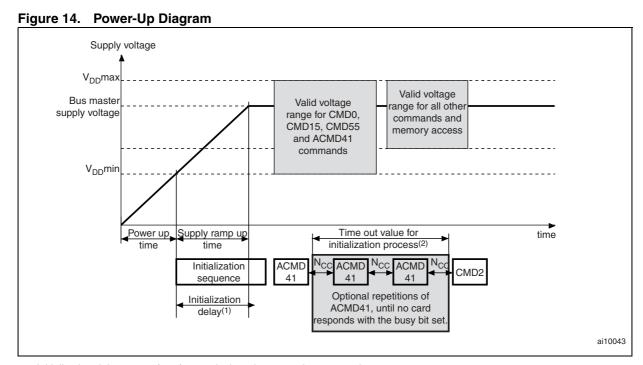

## 4.2 Power-Up

The power-up of the SD Memory Card bus is handled locally in each SD Memory Card and in the bus master. After power-up (or after hot insertion) the SD Memory Card enters the Idle state. When in this state, the SD Memory Card ignores all bus transactions until ACMD41 is received (ACMD command type should always be preceded by CMD55).

ACMD41 is a special synchronization command used to negotiate the operating voltage range and to poll the cards until they are out of their power-up sequence. In addition to the operating voltage profile of the cards, the response to ACMD41 contains a busy flag that indicates that the power-up sequence has not completed and the card is not ready for identification. The host has to wait (and continue polling the cards in turn) until the bit is cleared ('0'). The power-up sequence of an individual card should not exceed 1 second.

After power-up the host starts the clock and sends the initializing sequence on the CMD line. This sequence is a contiguous stream of logical 1's. It does not exceed 1ms, 74 clocks or the supply-ramp-up-time.

Note that the maximum duration is fixed to 74 clocks which is ten clock cycles more than the 64 clocks after which the card is normally ready for communication to eliminate all power-up synchronization problems.

- 1. Initialization delay = 1ms (max) + 74 clock cycles + supply ramp-up time.

- 2. Timeout value for initialization process is 1s.

### 4.3 Hot Insertion/Removal

To guarantee a reliable initialization during hot insertion, some measures must be taken on by the host.

For example, a special hot-insertion capable card connector may be used to guarantee the sequence of the card pin connection.

The card contacts are connected in three steps:

- 1. Ground V<sub>SS</sub> (pin 3) and supply voltage V<sub>DD</sub> (pin 4).

- 2. CLK, CMD, DAT0, DAT1, DAT2 and V<sub>SS</sub> (pin 6).

- 3. CD / DAT3 (pin 1).

Pins 3 and 4 should be connected first on insertion, and be disconnected last on extraction.

Another method is a switch which could ensure that the power is switched on only after all card pads are connected.

Inserting a Card in or removing it from the SD Memory Card bus with the power on will not damage the card. Data transfer operations are protected by CRC codes, therefore any bit changes induced by card insertion and removal can be detected by the SD Memory Card bus master.

- The inserted card must be properly reset even when the clock frequency is fpp

- Each card should be fitted with a protection from the power supply to prevent damage to the card (and host).

- Data transfer failures induced by removal/insertion are detected by the bus master.

They must be corrected by the application, which may repeat the issued command.

### 4.4 Power Protection

Cards have to be inserted in or removed from the bus without being damaged. If one of the supply pins ( $V_{DD}$  or  $V_{SS}$ ) is not connected properly, then the current is drawn through a data line. All the card outputs should also be able to withstand shortcuts to either supply. If the hot insertion feature is implemented in the host, then the host has to be able to withstand an instant shortcut between  $V_{DD}$  and  $V_{SS}$  without being damaged.

## 4.5 Electrical Specifications

*Table 16* defines the Bus Operating Conditions for the SD Memory Card. The total capacitance  $C_L$  of the CLK line of the SD Memory Card bus is the sum of the bus master capacitance  $C_{HOST}$ , the bus capacitance  $C_{BUS}$  and the capacitances  $C_{CARD}$  of all the cards connected to this line.

$C_L = C_{HOST} + C_{BUS} + N \times C_{CARD}$ , where:

- N is the number of cards connected to the line.

- C<sub>HOST</sub> + C<sub>BUS</sub> must be lower than 30pF for up to 10 cards and lower than 40pF for up to 30 cards.

- The values in *Table 16* should not be exceeded.

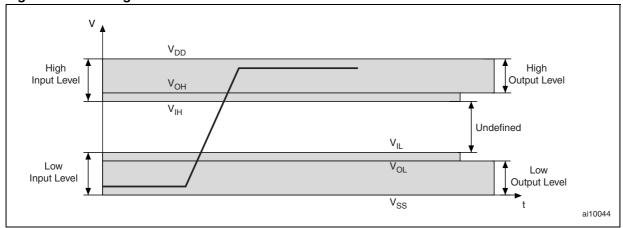

As the bus can be supplied with a variable supply voltage, all signal levels are related to the supply voltage. See *Figure 15: Bus Signal levels* and *Table 17: Bus Signal Condition - I/O Signal Voltages*.

**Bus Operating Conditions** Table 16.

| Symbol                              | Parameter                                | Min  | Max.                 | Unit | Remark                              |

|-------------------------------------|------------------------------------------|------|----------------------|------|-------------------------------------|

|                                     | Peak voltage on all lines                | -0.3 | V <sub>DD</sub> +0.3 | V    |                                     |

|                                     | Input Leakage Current                    | -10  | 10                   | Α    |                                     |

|                                     | Output Leakage Current                   | -10  | 10                   | Α    |                                     |

| V <sub>DD</sub>                     | Supply voltage                           | 2.0  | 3.6                  | V    |                                     |

|                                     | Supply voltage specified in OCR register |      |                      |      |                                     |

| V <sub>SS1</sub> , V <sub>SS2</sub> | Supply voltage differentials             | -0.3 | 0.3                  | V    |                                     |

|                                     | power-up time                            |      | 250                  | ms   |                                     |

| R <sub>CMD</sub> , R <sub>DAT</sub> | Pull-up resistance                       | 10   | 100                  | ΚΩ   |                                     |

| C <sub>L</sub>                      | Bus signal line capacitance              |      | 250                  | pF   | f <sub>PP</sub> < 5MHz<br>21 Cards  |

| OL.                                 | bus signal line capacitance              |      | 100                  | pF   | f <sub>PP</sub> < 20MHz<br>21 Cards |

| C <sub>CARD</sub>                   | Single Card capacitance                  |      | 10                   | pF   |                                     |

|                                     | Maximum signal line Inductance           |      | 16                   | nH   | f <sub>PP</sub> < 20MHz             |

| R <sub>DAT3</sub>                   | Pull-up resistance inside card (pin1)    | 10   | 90                   | ΚΩ   |                                     |

Figure 15. Bus Signal levels

Table 17. **Bus Signal Condition - I/O Signal Voltages**

| Symbol          | Parameter           | Conditions                          | Min                  | Max.                  | Unit |

|-----------------|---------------------|-------------------------------------|----------------------|-----------------------|------|

| $V_{OH}$        | HIGH Output voltage | $I_{OH} = 400\mu A$ at $V_{DD}$ min | 0.75V <sub>DD</sub>  |                       | V    |

| V <sub>OL</sub> | LOW Output voltage  | $I_{OL} = 100\mu A$ at $V_{DD}$ min |                      | 0.125V <sub>DD</sub>  | V    |

| $V_{IH}$        | HIGH Input voltage  |                                     | 0.625V <sub>DD</sub> | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IL</sub> | LOW Input voltage   |                                     | V <sub>SS</sub> -0.3 | 0.25V <sub>DD</sub>   | V    |

**Numonyx** 29/61

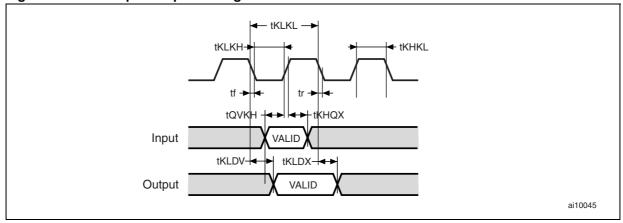

Figure 16. Data Input/Output Timings Referenced to Clock

Table 18. Bus Timings (1)

| Symbol            | Alt               | Parameter                                                                                             | Condition                         | Min | Max. | Unit |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------|-----|------|------|

| t <sub>KLKL</sub> | f <sub>PP</sub>   | Clock frequency Data Transfer Mode                                                                    | C <sub>L</sub> = 100pF (7 cards)  | 0   | 25   | MHz  |

| f <sub>OD</sub>   |                   | Clock Frequency Identification Mode (the low frequency is required for MultiMediaCard compatibility). | C <sub>L</sub> = 250pF (21 cards) | 0   | 400  | kHz  |

| t                 | t                 | Clock low time                                                                                        | C <sub>L</sub> = 100pF (7 cards)  | 10  |      | ns   |

| t <sub>KLKH</sub> | t <sub>WL</sub>   | Clock low time                                                                                        | C <sub>L</sub> = 250pF (21 cards) | 50  |      | ns   |

| +                 |                   | Clock high time                                                                                       | C <sub>L</sub> = 100pF (7 cards)  | 10  |      | ns   |

| t <sub>KHKL</sub> | t <sub>WH</sub>   | Clock high time                                                                                       | C <sub>L</sub> = 250pF (21 cards) | 50  |      | ns   |

|                   |                   | Clock rise time                                                                                       | C <sub>L</sub> = 100pF (7 cards)  |     | 10   | ns   |

| t <sub>r</sub>    | t <sub>TLH</sub>  | Clock rise time                                                                                       | C <sub>L</sub> = 250pF (21 cards) |     | 50   | ns   |

|                   |                   | Clock fall time                                                                                       | C <sub>L</sub> = 100pF (7 cards)  |     | 10   | ns   |

| t <sub>f</sub>    | t <sub>THL</sub>  | Clock fall time                                                                                       | C <sub>L</sub> = 250pF (21 cards) |     | 50   | ns   |

| Inputs CMD        | , DAT (refe       | erenced to CLK)                                                                                       |                                   |     |      |      |

| t <sub>QVKH</sub> | t <sub>ISU</sub>  | Input set-up time                                                                                     | C <sub>L</sub> = 25pF (1 card)    | 5   |      | ns   |

| t <sub>KHQX</sub> | t <sub>IH</sub>   | Input hold time                                                                                       | C <sub>L</sub> =25pF (1 card)     | 5   |      | ns   |

| Outputs CM        | D, DAT (re        | eferenced to CLK)                                                                                     |                                   |     |      |      |

| t <sub>KLDX</sub> | t <sub>ODLY</sub> | Output Delay time                                                                                     | C <sub>L</sub> =25pF (1 card)     |     | 14   | ns   |

<sup>1.</sup> Clock CLK: All values are referred to min (V  $_{\rm IL})$  and max (V  $_{\rm IH}).$

## 5 Card registers

Six registers are defined in the card interface: OCR, CID, CSD, RCA, DSR and SCR. See *Table 19* for a description.

The registers are accessed by using the corresponding commands. The OCR, CID, CSD and SCR registers contain the card/content specific information, whereas the RCA and DSR registers are configuration registers that store the actual configuration parameters.

For more details about the register structure, please refer to the SD Memory Card Specification v.1.01.

Table 19. SD Memory Card Registers

| Name               | Width | Description                                                                                                                                                                                  |  |

|--------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CID                | 128   | Card IDentification number register. It contains the card's individual identification number. It is mandatory.                                                                               |  |

| RCA <sup>(1)</sup> | 16    | Relative Card Address register. It contains the local system address of the card, that is dynamically suggested by the card and approved by the host during initialization. It is mandatory. |  |

| DSR                | 16    | <b>Driver Stage Register</b> . It is used to configure the card's output drivers. It is optional.                                                                                            |  |

| CSD                | 128   | Card Specific Data register. It contains the information about the card's operation conditions. It is mandatory.                                                                             |  |

| SCR                | 64    | SD Configuration Register. It contains the information about the SD Memory Card's Special Feature capabilities. It is mandatory                                                              |  |

| OCR                | 32    | Operation Condition Register. It is mandatory.                                                                                                                                               |  |

<sup>1.</sup> The RCA Register is not used (available) in SPI mode.

## 5.1 OCR Register

The 32-bit Operation Conditions Register contains the  $V_{DD}$  voltage profile of the card. It also includes a status information bit that goes High (set to '1') once the card power-up sequence has completed. The OCR register is used by the cards that do not support the full operating voltage range of the SD Memory Card bus, or by cards whose power-up sequence does not match the definition given in *Figure 14: Power-Up Diagram*.

Table 20. OCR Register Definition

| OCR Bit Position | V <sub>DD</sub> Voltage Range |

|------------------|-------------------------------|

| 0-3              | reserved                      |

| 4                | 1.6V to 1.7V                  |

| 5                | 1.7V to 1.8V                  |

| 6                | 1.8V to 1.9V                  |

| 7                | 1.9V to 2.0V                  |

| 8                | 2.0V to 2.1V                  |

Table 20. OCR Register Definition (continued)

| OCR Bit Position | V <sub>DD</sub> Voltage Range                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------|

| 9                | 2.1V to 2.2V                                                                                                  |

| 10               | 2.2V to 2.3V                                                                                                  |

| 11               | 2.3V to 2.4V                                                                                                  |

| 12               | 2.4V to 2.5V                                                                                                  |

| 13               | 2.5V to 2.6V                                                                                                  |

| 14               | 2.6V to 2.7V                                                                                                  |

| 15               | 2.7V to 2.8V                                                                                                  |

| 16               | 2.8V to 2.9V                                                                                                  |

| 17               | 2.9V to 3.0V                                                                                                  |

| 18               | 3.0V to 3.1V                                                                                                  |

| 19               | 3.1V to 3.2V                                                                                                  |

| 20               | 3.2V to 3.3V                                                                                                  |

| 21               | 3.3V to 3.4V                                                                                                  |

| 22               | 3.4V to 3.5V                                                                                                  |

| 23               | 3.5V to 3.6V                                                                                                  |

| 24-30            | reserved                                                                                                      |

| 31               | Card Power-up Status bit (busy). This bit is Low during the card power-up routine. It goes High on completion |

## 5.2 CID Register

The Card IDentification (CID) Register contains the card identification information used during the card identification phase. Each Flash memory card should have a unique identification number. The structure of the CID register is defined in *Figure 16*.

Table 21. CID Fields

| Name                  | Field | Width | CID-slice |

|-----------------------|-------|-------|-----------|

| Manufacturer ID       | MID   | 8     | [127:120] |

| OEM/Application ID    | OID   | 16    | [119:104] |

| Product name          | PNM   | 40    | [103:64]  |

| Product revision      | PRV   | 8     | [63:56]   |

| Product serial number | PSN   | 32    | [55:24]   |

| Reserved              |       | 4     | [23:20]   |

| Manufacturing date    | MDT   | 12    | [19:8]    |

| CRC7 checksum         | CRC   | 7     | [7:1]     |

| not used, always '1'  |       | 1     | [0:0]     |

## 5.3 CSD Register

The Card Specific Data Register provides information on how to access the card contents. The CSD Register defines the data format, error correction type, maximum data access time, data transfer speed, whether the DSR register can be used etc. The programmable register parameters (entries with cell type W or R, listed in *Table 22*) can be changed using CMD27.

Table 22. CSD Fields Compatible with CSD Structure V1 / MM Card Specification V2.11

| Name                                             | Field              | Width | Cell Type <sup>(1)</sup> | CSD-slice |

|--------------------------------------------------|--------------------|-------|--------------------------|-----------|

| CSD structure                                    | CSD_STRUCTURE      | 2     | R                        | [127:126] |

| reserved                                         | -                  | 6     | R                        | [125:120] |

| data read access-time-1                          | TAAC               | 8     | R                        | [119:112] |

| data read access-time-2 in CLK cycles (NSAC*100) | NSAC               | 8     | R                        | [111:104] |

| Max. data transfer rate                          | TRAN_SPEED         | 8     | R                        | [103:96]  |

| card command classes                             | CCC                | 12    | R                        | [95:84]   |

| Max. read data block length                      | READ_BL_LEN        | 4     | R                        | [83:80]   |

| partial blocks for read allowed                  | READ_BL_PARTIAL    | 1     | R                        | [79:79]   |

| write block misalignment                         | WRITE_BLK_MISALIGN | 1     | R                        | [78:78]   |

| read block misalignment                          | READ_BLK_MISALIGN  | 1     | R                        | [77:77]   |

| DSR implemented                                  | DSR_IMP            | 1     | R                        | [76:76]   |

| reserved                                         | -                  | 2     | R                        | [75:74]   |

| device size                                      | C_SIZE             | 12    | R                        | [73:62]   |

| Max. read current @VDD min                       | VDD_R_CURR_MIN     | 3     | R                        | [61:59]   |

| Max. read current @VDD max                       | VDD_R_CURR_MAX     | 3     | R                        | [58:56]   |

| Max. write current @VDD min                      | VDD_W_CURR_MIN     | 3     | R                        | [55:53]   |

| Max. write current @VDD max                      | VDD_W_CURR_MAX     | 3     | R                        | [52:50]   |

| device size multiplier                           | C_SIZE_MULT        | 3     | R                        | [49:47]   |

| erase single block enable                        | ERASE_BLK_EN       | 1     | R                        | [46:46]   |

| sector size                                      | SECTOR_SIZE        | 7     | R                        | [45:39]   |

| write protect group size                         | WP_GRP_SIZE        | 7     | R                        | [38:32]   |

| write protect group enable                       | WP_GRP_ENABLE      | 1     | R                        | [31:31]   |

| reserved for MultiMediaCard compatibility        | -                  | 2     | R                        | [30:29]   |

| write speed factor                               | R2W_FACTOR         | 3     | R                        | [28:26]   |

| Max. write data block length                     | WRITE_BL_LEN       | 4     | R                        | [25:22]   |

| partial blocks for write allowed                 | WRITE_BL_PARTIAL   | 1     | R                        | [21:21]   |

| reserved                                         | -                  | 5     | R                        | [20:16]   |

| File format group                                | FILE_FORMAT_GRP    | 1     | R/W(1)                   | [15:15]   |

| copy flag (OTP)                                  | COPY               | 1     | R/W(1)                   | [14:14]   |

| permanent write protection                       | PERM_WRITE_PROTECT | 1     | R/W(1)                   | [13:13]   |

Table 22. CSD Fields Compatible with CSD Structure V1 / MM Card Specification V2.11

| Name                       | Field             | Width | Cell Type <sup>(1)</sup> | CSD-slice |

|----------------------------|-------------------|-------|--------------------------|-----------|

| temporary write protection | TMP_WRITE_PROTECT | 1     | R/W                      | [12:12]   |

| File format                | FILE_FORMAT       | 2     | R/W(1)                   | [11:10]   |

| reserved                   | -                 | 2     | R/W                      | [9:8]     |

| CRC                        | CRC               | 7     | R/W                      | [7:1]     |

| not used, always'1         | -                 | 1     | -                        | [0:0]     |

<sup>1.</sup> R = readable, W(1) = can be written once, W = can be written several times.

## 5.4 RCA Register

The writable 16-bit Relative Card Address Register contains the card address published by the card during the identification phase. This address is used for addressed host-card communications after the card identification phase. The default value of the RCA register is 0000h. This value is reserved, the CMD7 command uses it to set all the cards to the Standby state.

## 5.5 DSR Register (Optional)

The 16-bit Driver Stage Register is not used in Numonyx Cards.

## 5.6 SCR Register

The SD Card Configuration Register (SCR) is a configuration register. The SCR provides information on the special features that are configured in the SD Memory Card. The size of SCR Register is 64 bit.

This register is programmed in the factory by the SD Memory Card manufacturer. *Table 23* describes the SCR contents.

Table 23. SCR Fields

| Description                                | Field                 | Width | Cell Type <sup>(1)</sup> | SCR Slice |

|--------------------------------------------|-----------------------|-------|--------------------------|-----------|

| SCR Structure                              | SCR_STRUCTURE         | 4     | R                        | [63:60]   |

| SD Memory Card - Specification.<br>Version | SD_SPEC               | 4     | R                        | [59:56]   |

| data_status_after erases                   | DATA_STAT_AFTER_ERASE | 1     | R                        | [55:55]   |

| SD Security Support                        | SD_SECURITY           | 3     | R                        | [54:52]   |

| DAT Bus width supported                    | SD_BUS_WIDTHS         | 4     | R                        | [51:48]   |

| reserved                                   | -                     | 16    | R                        | [47:32]   |

| reserved for manufacturer usage            | -                     | 32    | R                        | [31:0]    |

<sup>1.</sup> R = readable.

## 6 Timings

The symbols listed in *Table 24* are used in all timing diagrams.

The difference between P-bits and Z-bits is that P-bits are actively driven to High by the card or the host output driver whereas Z-bits are driven to High and kept High by the pull-up resistors  $R_{CMD}$  and  $R_{DAT}$ . P-bits, which are actively driven High, are less sensitive to noise. All timing values are defined in *Table 25*

Table 24. Timing Diagram Symbols

| Symbol | Description                              |