**Headphone Driver IC**

PT2309

#### **DESCRIPTION**

The PT2309 is a headphone driver IC, it can working on wide supply range. Utilizing CMOS Technology, it has very low power consumption is in stand-by mode. Total harmonic distortion is lower than 0.03% ( $32\Omega$  load) and the also has low noise output. Built-in mute function can prevents popping sounds happen when power is turned ON or OFF. It is also has built-in over-temperature protection, minimum package size for space saving and suitable for small or portable products.

#### **FEATURES**

- CMOS Technology

- Stereo Input

- Drive 32Ω impedance load

- Low noise, Low distortion

- Suppress the pop and click noise when mode changed

- Built-in mute function

- Available in 8 Pins, DIP or SOP Package

## **APPLICATIONS**

- Portable VCD/DVD

- CD-ROM

- PDA

- Sound Card

PT2309 V1.2 - 1 - August, 2006

**Headphone Driver IC**

PT2309

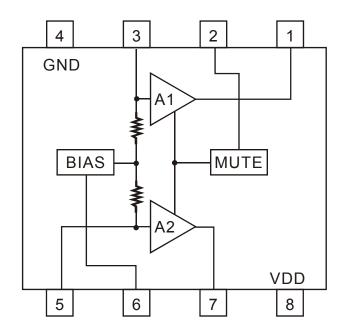

# **BLOCK DIAGRAM**

PT2309

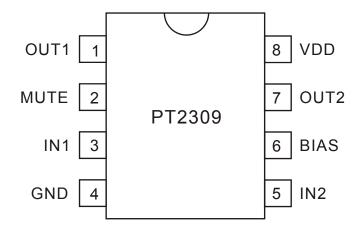

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| Pin Name | 1/0 | Description | Pin No. |

|----------|-----|-------------|---------|

| OUT1     | 0   | CH1 Output  | 1       |

| MUTE     | Ι   | Mute Pin    | 2       |

| IN1      | -   | CH1 Input   | 3       |

| GND      | -   | Ground      | 4       |

| IN2      | -   | CH2 Input   | 5       |

| BIAS     | -   | Bias Pin    | 6       |

| OUT2     | 0   | CH2 Output  | 7       |

| VDD      | -   | Power Input | 8       |

**Headphone Driver IC**

PT2309

### **FUNCTION DESCRIPTION**

#### **POWER SUPPLY**

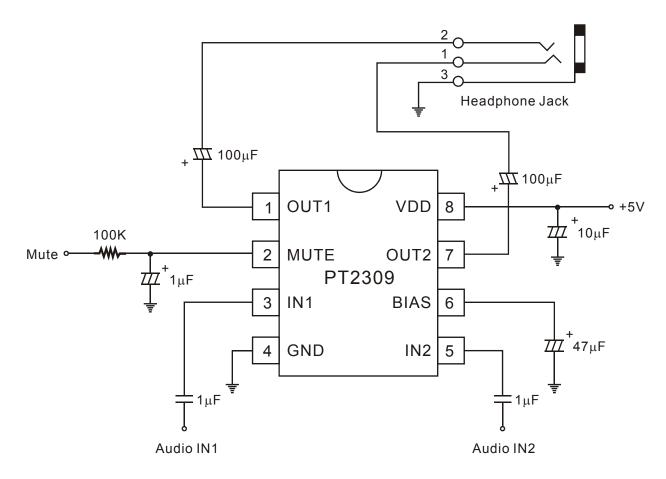

The operating voltage of PT2309 is from 3V to 5V, In general operation 5V is recommended. It should connect a modest bias capacitor nearby the power source terminal. It can improve IC stability and decrease the noise output. Suggestion value of capacitor is from 0.1µF to 10µF.

#### POP AND CLICK SUPPRESS

For normal operation, the Input/Output port of a power amplifier powered by a single supply voltage must have a stable DC bias. Each time turn on the Vcc the input/output pins will present 1/2 Vcc DC bias voltage. For blocking the DC bias flowing to another circuit, each input/output port should have a DC blocking capacitor, it will charge/discharge when power on or off, the capacitance is relative with the pop noise. In general condition to prevent the pop noise, the time constant of bypass cap (CB) on the bypass pin will be set to maximum. Higher CB value will extend the stable time, and also can suppress the noise heard when power-on. In supply voltage=5V and CB=10µF, stable time is approx 1s. The value of CB also relative with the value of the DC blocking capacitor connected in input terminal. In general condition the time constant of DC blocking capacitor should be less than CB stable time. Recommend parts values please refer to application circuit.

### INPUT CAPACITOR

Input capacitor decide the bandwidth and charge time constant, due to there is a  $50K\Omega$  impedance, so input terminal charge period constant is:

Tin=  $(2\pi \times 50K\Omega \times Cin)$

If Cin=1 $\mu$ F, Tin=0.3s, Low frequency lower limit is 3Hz. This capacitor can use a non-polarity SMD capacitor  $\circ$

#### **OUTPUT CAPACITOR**

The headphone driver is designed to drive  $32\Omega$  headphone load, it needs a larger capacitance to extending the lower frequency cut off point. If driving a small headphone a  $100\mu\text{F}$  capacitor is a good choice and the low frequency limit is around 50Hz; for better low frequency performance a  $220\mu\text{F}$  capacitor is recommended and it's low frequency can extend to 22Hz. Due to charge/discharge time constant is shorter than CB stable time, so it will not have pop and click noise.

PT2309 V1.2 - 4 - August, 2006

### **Headphone Driver IC**

PT2309

#### MUTE

When the mute pin is connected to the GND, all of outputs signal will be muted immediately. Connecting the external R/C components on here could prevent the power—on "POP" noises, the mute function also can be active by the external DC voltage.

Due to the built-in pull down resistor (150K $\Omega$ ), a larger value series resistor connecting to the mute pin may causes mute malfunction because of mute voltage divided by the resistor network. For the detailed connection description please refer to the application circuit.

The attenuation of mute is relation with CB, we suggest CB must be higher then  $10\mu$ F, the recommend value is  $47\mu$ F. Higher CB will have better mute characteristic.

PT2309 V1.2 - 5 - August, 2006

**Headphone Driver IC**

PT2309

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol | Condition | Min. | Max.    | Unit                    |

|-----------------------|--------|-----------|------|---------|-------------------------|

| Supply Voltage        | VDD    |           | 0    | 7       | V                       |

| Operating Temperature | Topr   |           | -40  | +85     | $^{\circ}\! \mathbb{C}$ |

| Storage Temperature   | Tstg   |           | -65  | +150    | $^{\circ}\! \mathbb{C}$ |

| Maximum Input Voltage | Vimax  |           | -0.3 | Vcc+0.3 | V                       |

| Maximum Input Current | limax  | *         | -10  | +10     | mA                      |

Note: \* Input pins surge current can reach 100mA does not induce the CMOS latched up.

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise, Vcc=5V , CB=47µF , bandwidth=22~22KHz

| Parameter                       | Symbol  | Conditions                             | Min.  | Тур.  | Max. | Unit                                                             |  |

|---------------------------------|---------|----------------------------------------|-------|-------|------|------------------------------------------------------------------|--|

| Supply Voltage                  | VDD     |                                        | 3     | 5     | 6    | V                                                                |  |

| Operating Current               | Is      | Normal Mode                            | 6     | 7.5   | 9    | 6 V 9 mA 7.5 mA +1 dB +0.5 0.06 % 0.01 55 mW 110 dB 105 dB 65 dB |  |

|                                 | 13      | Mute Mode                              | 4.5   | 6     | 7.5  |                                                                  |  |

| Voltage Gain                    | Vg      |                                        | -1    | 0     | +1   | dB                                                               |  |

| Two Channels Gain Error         | Vgerr   |                                        | -0.5  | 0     | +0.5 |                                                                  |  |

| TUDAN                           | TUD     | Vin = 1Vrms $\cdot$ RL = 32 $\Omega$   | 0.01  | 0.03  | 0.06 | 0/                                                               |  |

| THD+N                           | THD     | Vin = 1Vrms $\cdot$ RL = 5.1K $\Omega$ | 0.003 | 0.005 | 0.01 | %                                                                |  |

| Power Output                    | Ро      | THD=0.1% <sup>,</sup> RL=32Ω           | 35    | 45    | 55   | m\\\                                                             |  |

| Power Output                    | P0      | THD=0.1% <sup>,</sup> RL=16Ω           | 65    | 75    | 85   | 11100                                                            |  |

| Signal-to-Noise Ratio           | SNR     | Input=GND · A-Weighted                 | 102   | 105   | 110  | dB                                                               |  |

| Channel Separation              | CS      | F=1KHz                                 | 90    | 100   | 105  | ЧD                                                               |  |

|                                 | CS      | F=100~20KHz                            | 80    | 90    | 95   | ив                                                               |  |

| Power Supply<br>Rejection Ratio | PSRR    | Vr=100mVrms,F=100Hz                    | 45    | 55    | 65   | dB                                                               |  |

| Mute                            | mute    | MUTE=GND, F=1KHz                       | 60    | 75    | 80   | dB                                                               |  |

| Mute Voltage                    | Vmute   | VIH, MUTE= OFF                         | 1     | 1.1   | 1.4  | 1.4 Vcc                                                          |  |

|                                 | villule | VIL, MUTE= ON                          | 0.8   | 0.9   | 1 1  | VCC                                                              |  |

PT2309

## **APPLICATION CIRCUIT**

## **Headphone Driver IC**

PT2309

# **ORDER INFORMATION**

| Valid Part Number | Package Type       | Top Code |

|-------------------|--------------------|----------|

| PT2309-D          | 8-Pin, DIP, 300mil | PT2309-D |

| PT2309-S          | 8-Pin, SOP, 150mil | PT2309-S |

| PT2309-D (L)      | 8-Pin, DIP, 300mil | PT2309-D |

| PT2309-S (L)      | 8-Pin, SOP, 150mil | PT2309-S |

#### Notes:

- 1. (L), (C) or (S) = Lead Free.

- 2. The Lead Free mark is put in front of the date code.

PT2309 V1.2 - 8 - August, 2006

PT2309

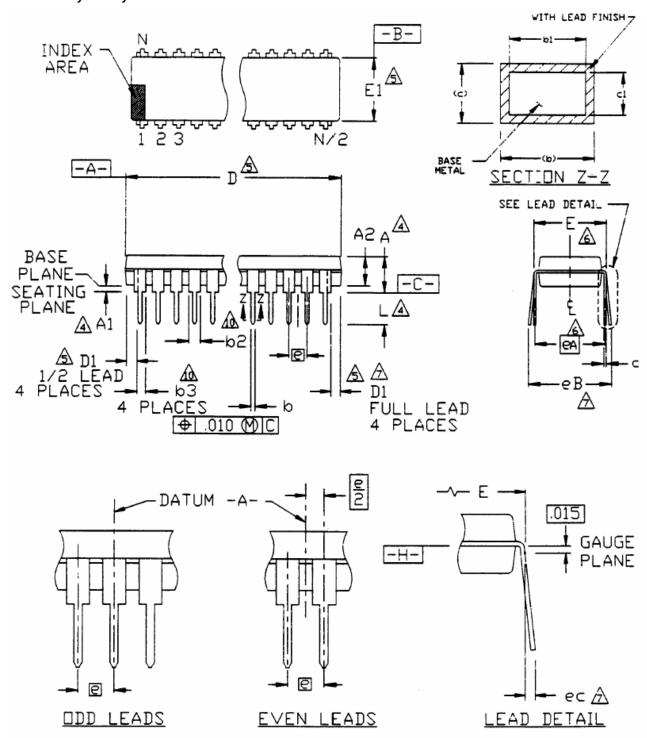

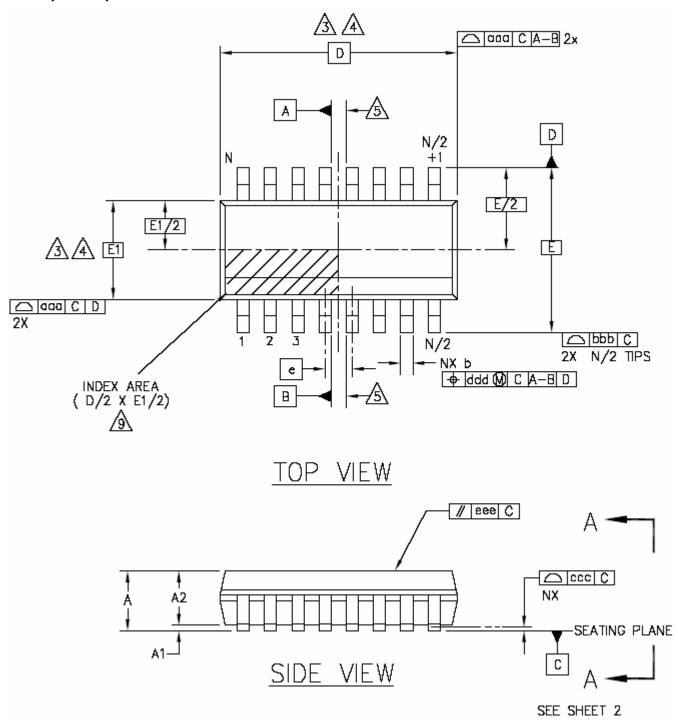

## **PACKAGE INFORMATION**

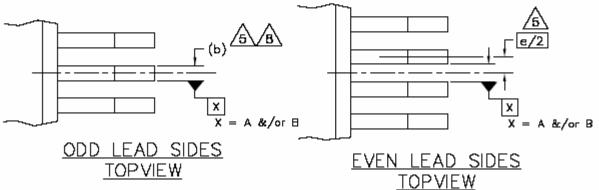

8 PINS, DIP, 300MIL

## **Headphone Driver IC**

PT2309

| Symbol | Min.       | Nom.  | Max.  |  |

|--------|------------|-------|-------|--|

| Α      | -          | -     | 0.210 |  |

| A1     | 0.015      | -     | -     |  |

| A2     | 0.115      | 0.130 | 0.195 |  |

| b      | 0.014      | 0.018 | 0.022 |  |

| b1     | 0.014      | 0.018 | 0.020 |  |

| b2     | 0.045      | 0.060 | 0.070 |  |

| b3     | 0.030      | 0.039 | 0.045 |  |

| С      | 0.008      | 0.010 | 0.014 |  |

| c1     | 0.008      | 0.010 | 0.011 |  |

| D      | 0.355      | 0.365 | 0.400 |  |

| D1     | 0.005      | -     |       |  |

| E      | 0.300      | 0.310 | 0.325 |  |

| E1     | 0.240      | 0.250 | 0.280 |  |

| е      | 0.100 bsc. |       |       |  |

| eA     | 0.300 bsc. |       |       |  |

| eB     | -          | -     | 0.430 |  |

| eC     | 0.000      | -     | 0.060 |  |

| L      | 0.115      | 0.130 | 0.150 |  |

#### Note:

- 1. Controlling Dimensions: INCHES.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol LIST" in Section 2.2 of Publication No.95.

- 4. Dimension A, A1 and L are measured with the package seated in JEDEC Seating Plane Gauge GS-3.

- 5. D, D1 and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch.

- 6. E and eA measured with the leads constrained to be perpendicular to data -c- .

- 7. eB and eC are measured at the lead tips with the leads unconstrained.

- 8. N is the number of leads (N=8)

- 9. Pointed or rounded lead tips are preferred to ease insertion.

- 10.b2 and b3 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm)

- 11. Variation BA has a b3 dimension and is 1/2 lead package.

- 12. Distance between the leads including dambar protrusions to be 0.005 inch minimum.

- 13. Datum plane -H- coincident with the bottom of lead, where lead exits the body.

- 14. Refer to JEDEC MS-001, Variation BA.

JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.

PT2309 V1.2 - 10 - August, 2006

**Headphone Driver IC**

PT2309

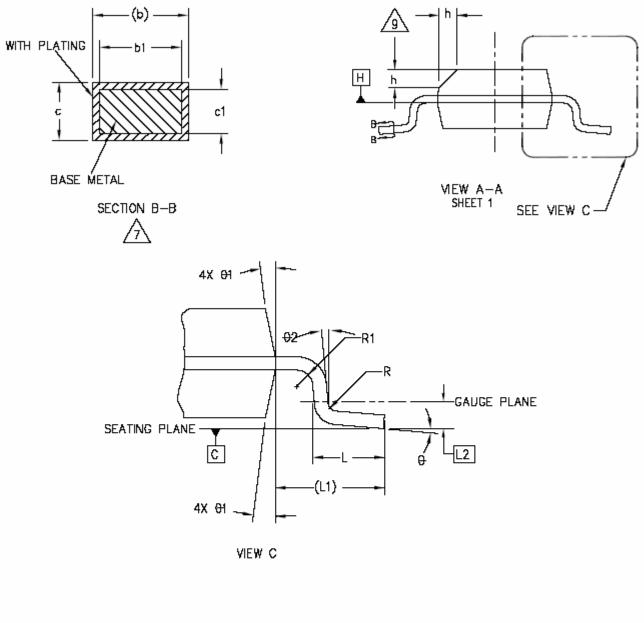

## 8 PINS, SOP, 150 MIL

# 普誠科技股份有限公司 Princeton Technology Corp.

Tel:886-2-66296288 Fax:886-2-29174598 URL:http://www.princeton.com.tw

## **Headphone Driver IC**

PT2309

PT2309

| Symbol | Min.        | Тур.      | Max. |

|--------|-------------|-----------|------|

| Α      | 1.35        | -         | 1.75 |

| A1     | 0.10        | -         | 0.25 |

| A2     | 1.25        | -         | 1.65 |

| b      | 0.31        | -         | 0.51 |

| b1     | 0.28        | -         | 0.48 |

| С      | 0.17        | -         | 0.25 |

| c1     | 0.17        | -         | 0.23 |

| D      |             | 4.90 BSC. |      |

| Е      |             | 6.00 BSC. |      |

| E1     |             | 3.90 BSC. |      |

| е      | 1.27 BSC.   |           |      |

| L      | 0.40 - 1.27 |           |      |

| L1     | 1.04 REF.   |           |      |

| L2     | 0.25 BSC.   |           |      |

| R      | 0.07        | -         | -    |

| R1     | 0.07        |           | -    |

| h      | 0.25        | -         | 0.50 |

| θ      | 0°          | -         | 8°   |

| θ1     | 5°          | -         | 15°  |

| θ2     | 0°          | -         | -    |

#### Note:

- 1. Dimensioning and tolerancing per ANSI Y 14.5M-1994

- 2. Controlling Dimension: MILLIMETERS.

- 3. Dimension D does not include mold flash protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 mm (0.006 in) per end. Dimension E1 does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25mm per side. D and E1 dimensions are determined at datum H.

- 4. The package top may be smaller than the package bottom. Dimensions D and E1 are determined at the outermost extremes of the plastic body exclusive of mold flash, tie bar burrs, gate burrs and interlead flash, but including any mismatch between the top and bottom of the plastic body.

- 5. Datums A & B to be determined at datum H.

- 6. N is the number of terminal positions. (N=8)

- 7. The dimensions apply to the flat section of the lead between 0.10 to 0.25mm from the lead tip.

- 8. Dimension "b" does not include dambar protrusion. Allowable dambar protrusion shall be 0.10mm total in excess of the "b" dimension at maximum material condition. The dambar cannot be located on the lower radius of the foot.

- 9. This chamfer feature is optional. If it is not present, then a pin 1 identifier must be located within the index area indicated.

- 10. Refer to JEDEC MS-012, Variation AA. JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.

PT2309 V1.2 - 13 - August, 2006