# D16550

# Configurable UART with FIFO ver 2.08

# OVERVIEW

The D16550 is a soft Core of a Universal Asynchronous Receiver/Transmitter (UART) functionally identical to the TL16C550A. The D16550 allows serial transmission in two modes: UART mode and FIFO mode. In FIFO mode internal FIFOs are activated allowing 16 bytes (plus 3 bits of error data per byte in the RCVR FIFO) to be stored in both receive and transmit directions. D16550 performs serial-toparallel conversion on data characters received from a peripheral device or a MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the complete status of the UART at any time during the functional operation. Status information includes the type and condition of the transfer operations being performed by the UART, as well as any error conditions (parity, overrun, framing, or break interrupt). D16550 includes a programmable baud rate generator that is capable of dividing the timing reference clock input by divisors of 1 to (2<sup>16</sup>-1), and producing a 16 × clock for driving the internal transmitter logic. Provisions are also included to use this 16 × clock to drive the receiver logic. The D16550 has complete MODEM control capability, and a processor-interrupt system. Interrupts can be programmed to the user's requirements, minimizing the computing required to handle the communications link.

The separate BAUD CLK line allow to set an exact transmission speed, while the UART

All trademarks mentioned in this document are trademarks of their respective owners.

internal logic is clocked with the CPU frequency.

Two DMA modes are supported: single transfer and multi-transfer. These modes allow UART to interface to higher performance DMA units, which can interleave their transfers between CPU cycles or execute multiple byte transfers.

The configuration capability allows user to enable or disable during Synthesis process the Modem Control Logic and FIFO's Control Logic, change the FIFO size. So in applications with area limitation and where the UART works only in 16450 mode, disabling Modem Control and FIFO's allow to save about 50% of logic resources.

The D16550 has universal microcontroller interface, allows correct communication with D16550 no matter how D16550 clock is related to microcontroller clock. The core is perfect for applications, where the UART Core and microcontroller are clocked by the same clock signal and are implemented inside the same ASIC or FPGA chip, as well as for standalone implementation, where several UARTs are required to be implemented inside a single chip, and driven by some off-chip devices. Thanks to universal interface D16550 core implementation and verification are very simply, by eliminating a number of clock trees in complete system.

# **APPLICATIONS**

- Serial Data communications applications

- Modem interface

#### KEY FEATURES

- Software compatible with 16450 and 16550 UARTs

- Configuration capability

- Separate configurable BAUD clock line

- Two modes of operation: UART mode and FIFO mode

- Majority Voting Logic

- In the FIFO mode transmitter and receiver are each buffered with 16 byte FIFO to reduce the number of interrupts presented to the CPU

- Adds or deletes standard asynchronous communication bits (start, stop, and parity) to or from the serial data

- In UART mode receiver and transmitter are double buffered to eliminate a need for precise synchronization between the CPU and serial data

- Independently controlled transmit, receive, line status, and data set interrupts

- False start bit detection

- 16 bit programmable baud generator

- MODEM control functions (CTS, RTS, DSR, DTR, RI, and DCD)

- Fully programmable serial-interface characteristics:

- 5-, 6-, 7-, or 8-bit characters

- Even, odd, or no-parity bit generation and detection

- 1-, 1½-, or 2-stop bit generation

- Baud generation

- Complete status reporting capabilities

- Line break generation and detection.

Internal diagnostic capabilities:

- Loop-back controls for communications link fault isolation

- Break, parity, overrun, framing error simulation

- Two DMA Modes allows single and multitransfer

All trademarks mentioned in this document are trademarks of their respective owners.

- Technology independent HDL Source Code

- Full prioritized interrupt system controls

- Fully synthesizable static design with no internal tri-state buffers

# **DESIGN FEATURES**

The functionality of the D16550 core was based on the Texas Instruments TL16C550A. The following characteristics differentiate the D16550 from Texas Instruments devices:

- The bi-directional data bus has been split into two separate buses: datai(7:0), datao(7:0)

- Signals rd2 and wr2, xin, and xout have been removed from interface

- Signal ADS and address latch have been removed

- The DLL, DLM and THR registers are reset to all zeros

- TEMT and THRE bits of Line Status Register, are reset during the second clock rising edge following a THR write

- RCLK clock is replaced by global clock CLK, internally divided by BAUD factor.

- Asynchronous microcontroller interface is replaced by equivalent Universal interface

- All latches implemented in original 16550 devices are replaced by equivalent flip-flop registers, with the same functionality

#### **DELIVERABLES**

- Source code:

- ♦ VHDL Source Code or/and

- ◊ VERILOG Source Code or/and

- ♦ Encrypted, or plain text EDIF netlist

- VHDL & VERILOG test bench environment

- Active-HDL automatic simulation macros

- ModelSim automatic simulation macros

- ♦ Tests with reference responses

- Technical documentation

- Installation notes

- HDL core specification

- ◊ Datasheet

- Synthesis scripts

- Example application

- Technical support

- ◊ IP Core implementation support

- ♦ 3 months maintenance

- Delivery the IP Core updates, minor and major versions changes

- Delivery the documentation updates

- Phone & email support

#### LICENSING

Comprehensible and clearly defined licensing methods without royalty fees make using of IP Core easy and simply.

<u>Single Design</u> license allows use IP Core in single FPGA bitstream and ASIC implementation.

<u>Unlimited Designs</u>, <u>One Year</u> licenses allow use IP Core in unlimited number of FPGA bitstreams and ASIC implementations.

In all cases number of IP Core instantiations within a design, and number of manufactured chips are unlimited. There is no time restriction except <u>One Year</u> license where time of use is limited to 12 months.

- Single Design license for

- VHDL, Verilog source code called <u>HDL</u> Source

- Encrypted, or plain text EDIF called <u>Netlist</u>

- One Year license for

- Encrypted Netlist only

- Unlimited Designs license for

- HDL Source

- Netlist

- Upgrade from

All trademarks mentioned in this document are trademarks of their respective owners.

- HDL Source to Netlist

- Single Design to Unlimited Designs

#### CONFIGURATION

The following parameters of the D16550 core can be easy adjusted to requirements of dedicated application and technology. Configuration of the core can be prepared by effortless changing appropriate constants in package file. There is no need to change any parts of the code.

enable Baud generator disable enable External RCLK source disable enable External BAUDCLK source disable enable Modem Control logic disable enable SCR Register disable enable FIFO Control logic disable

#### **APPLICATION**

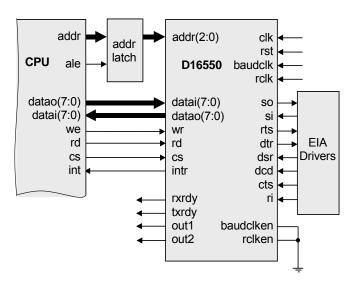

Typical D16550 and processor connection is shown in figure above.

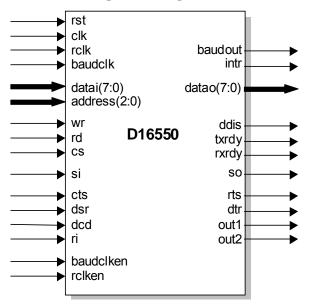

# SYMBOL

# PINS DESCRIPTION

| PIN        | TYPE   | DESCRIPTION                 |

|------------|--------|-----------------------------|

| rst        | input  | Global reset                |

| clk        | input  | Global clock                |

| datai[7:0] | input  | Parallel data input         |

| addr[2:0]  | input  | Address bus                 |

| cs         | input  | Chip select input           |

| wr         | input  | Write input                 |

| rd         | input  | Read input                  |

| rclk       | input  | Receiver clock              |

| baudclk    | input  | Baud generator clock        |

| si         | input  | Serial data input           |

| cts        | input  | Clear to send input         |

| dsr        | input  | Data set ready input        |

| dcd        | input  | Data carrier detect input   |

| ri         | input  | Ring indicator input        |

| baudclken  | input  | Baud generator clock enable |

| rclken     | input  | Receiver clock enable       |

| baudout    | output | Baud generator output       |

| datao[7:0] | output | Parallel data output        |

| so         | output | Serial data output          |

| ddis       | output | Driver disable output       |

| txrdy      | output | Transmitter ready output    |

| rxrdy      | output | Receiver ready output       |

| rts        | output | Request to send output      |

| dtr        | output | Data terminal ready output  |

| out1       | output | Output 1                    |

| out2       | output | Output 2                    |

| intr       | output | Interrupt request output    |

**Note**: When enabled RCLK and BAUDCLK pins frequency should be at least two times lower than CLK,  $2*f_{RCLK} < f_{CLK}$

All trademarks mentioned in this document are trademarks of their respective owners.

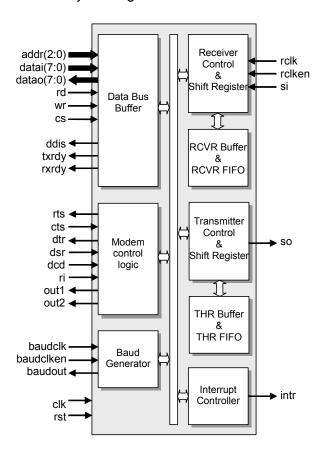

#### **BLOCK DIAGRAM**

Data Bus Buffer - The data Bus Buffer accepts inputs from the system bus and generates control signals for the other D16550 functional blocks. Address bus ADDR(2:0) selects one of the register to be read from/written into. Both RD and WE signals are active low, and are qualified by CS; RD and WE are ignored unless the D16550 has been selected by holding CS low.

**Baud Generator** - The D16550 contains a programmable 16 bit baud generator that divides clock input by a divisor in the range between 1 and (2<sup>16</sup>–1). The output frequency of the baud generator is 16× the baud rate. The formula for the divisor is:

$$divisor = \frac{frequency}{baudrate * 16}$$

Two 8-bit registers, called divisor latches DLL and DLM, store the divisor in a 16-bit binary format. These divisor latches must be loaded during initialization of the D16550 in order to ensure desired operation of the baud generator. When either of the divisor latches is loaded, a 16-bit baud counter is also loaded on the CLK rising edge following the write to

DLL or DLM to prevent long counts on initial load.

**Modem Control Logic** controls the interface with the MODEM or data set (or a peripheral device emulating a MODEM).

Interrupt Controller - D16550 consists fully prioritized interrupt system controller. It controls interrupt requests to the CPU and interrupt priority. Interrupt controller contains Interrupt Enable (IER) and Interrupt Identification (IIR) registers.

Receiver Control - Receiving starts when the falling edge on Serial Input (SI) during IDLE State is detected. After starting the SI input is sampled every 16 internal baud cycles as it is shown in figure below. When the logic 1 state is detected during START bit it means that the False Start bit was detected and receiver back to the IDLE state.

Receiver FIFO - The Rx FIFO is 16 levels deep, it receives data until the number of bytes in the FIFO equals the selected interrupt trigger level. At that time if Rx interrupts are enabled, the UART will issue an interrupt to the CPU. The Rx FIFO will continue to store bytes until it holds 16 of them. It will not accept any more data when it is full. Any more data entering the Rx shift register will set the Overrun Error flag.

**Transmitter Control** module controls transmission of written to THR (Transmitter Holding register) character via serial output SO. The new transmission starts on the next overflow signal of internal baud generator, after writing to THR register or Transmitter FIFO. Transmission control contains THR register and transmitter shift register.

Transmitter FIFO - the Tx portion of the UART transmits data through SO as soon as the CPU loads a byte into the Tx FIFO. The UART will prevent loads to the Tx FIFO if it currently holds 16 characters. Loading to the Tx FIFO will again be enabled as soon as the next character is transferred to the Tx shift register. These capabilities account for the largely autonomous operation of the Tx. The UART starts the above operations typically with a Tx interrupt.

#### PERFORMANCE

The following table gives a survey about the Core area and performance in the ALTERA® devices after Place & Route:

| Device           | Speed grade | Logic Cells      | F <sub>max</sub> |  |  |  |

|------------------|-------------|------------------|------------------|--|--|--|

| CYCLONE          | -6          | 452 <sup>1</sup> | 153 MHz          |  |  |  |

| CYCLONE 2        | -6          | 461 <sup>1</sup> | 165 MHz          |  |  |  |

| STRATIX          | -5          | 452 <sup>1</sup> | 189 MHz          |  |  |  |

| STRATIX 2        | -3          | 388 <sup>1</sup> | 241 MHz          |  |  |  |

| STRATIXGX        | -5          | 452 <sup>1</sup> | 184 MHz          |  |  |  |

| MERCURY          | -5          | 513 <sup>1</sup> | 134 MHz          |  |  |  |

| <b>EXCALIBUR</b> | -1          | 479 <sup>1</sup> | 131 MHz          |  |  |  |

| APEX II          | -7          | 480 <sup>1</sup> | 157 MHz          |  |  |  |

| APEX20KC         | -7          | 479 <sup>1</sup> | 141 MHz          |  |  |  |

| APEX20KE         | -1          | 479 <sup>1</sup> | 123 MHz          |  |  |  |

| APEX20K          | -1V         | 479 <sup>1</sup> | 94 MHz           |  |  |  |

| ACEX1K           | -1          | 500 <sup>1</sup> | 104 MHz          |  |  |  |

| FLEX10KE         | -1          | 500 <sup>1</sup> | 102 MHz          |  |  |  |

1- FIFOs implemented in EAB's – 304 Bits

Core performance in ALTERA® devices

# D16X50 UARTS FAMILY OVERVIEW

The family of DCD D16X50 UART IP Cores combine a high–performance, low cost, and small compact size, offering the best price/performance ratio in the IP Market. The DCD's Cores are dedicated for use in cost-sensitive consumer products, computer peripherals, office automation, automotive control systems, security and telecommunication applications.

The D16X50 IP Cores are written in pure VHDL/VERILOG HDL languages which make them technologically independent. All of the D16X50 IP Cores can be fully customized according to customer needs.

| Design | UARTS number | UART Mode | FIFO Mode of operation | FIFO Size (Bytes) | Majority voting<br>logic | Separate BAUD<br>Clock line | Software Flow<br>Control | RTS/CTS Flow<br>Control | MODEM Control | False START Bit detection | Complete status reporting | Internal diagnostic<br>capabilities | Prioritized interrupt system | Break generation<br>and detection | IRDA Port    | 1284 Parallel Port |

|--------|--------------|-----------|------------------------|-------------------|--------------------------|-----------------------------|--------------------------|-------------------------|---------------|---------------------------|---------------------------|-------------------------------------|------------------------------|-----------------------------------|--------------|--------------------|

| D16450 | 1            | ✓         | -                      | -                 | ✓                        | ✓                           | -                        | -                       | ✓             | <b>√</b>                  | ✓                         | ✓                                   | ✓                            | ✓                                 | _*           | -*                 |

| D16550 | 1            | ✓         | $\checkmark$           | 2* 16             | ✓                        | $\checkmark$                | -                        | -                       | $\checkmark$  | $\checkmark$              | $\checkmark$              | $\checkmark$                        | $\checkmark$                 | $\checkmark$                      | -*           | -*                 |

| D16750 | 1            | ✓         | ✓                      | 2* 64             | ✓                        | $\checkmark$                | -                        | $\checkmark$            | $\checkmark$  | $\checkmark$              | $\checkmark$              | $\checkmark$                        | ✓                            | $\checkmark$                      | -*           | -*                 |

| D16552 | 2            | ✓         | ✓                      | 4* 16             | ✓                        | $\checkmark$                | -                        | -                       | $\checkmark$  | $\checkmark$              | $\checkmark$              | $\checkmark$                        | ✓                            | $\checkmark$                      | $\checkmark$ | $\checkmark$       |

| D16752 | 2            | ✓         | ✓                      | 4* 64             | ✓                        | ✓                           | ✓                        | $\checkmark$            | ✓             | ✓                         | ✓                         | ✓                                   | $\checkmark$                 | $\checkmark$                      | -*           | -*                 |

| D16754 | 4            | ✓         | <b>✓</b>               | 8* 64             | ✓                        | $\checkmark$                | $\checkmark$             | $\checkmark$            | $\checkmark$  | $\checkmark$              | $\checkmark$              | $\checkmark$                        | $\checkmark$                 | $\checkmark$                      | _*           | -*                 |

<sup>\*-</sup>Optional

D16X50 family of Configurable UARTs with FIFO IP Cores

# CONTACTS

For any modification or special request please contact to Digital Core Design or local distributors.

# **Headquarters:**

Wroclawska 94

41-902 Bytom, POLAND

e-mail: info@dcd.pl

tel. : +48 32 282 82 66 fax : +48 32 282 74 37

#### **Distributors:**

Please check http://www.dcd.pl/apartn.php