SPSS030A - DECEMBER 2000 - REVISED FEBRUARY 2001

- Advanced, Catalog Speech Processor for High-Quality Sound, Capable of Unlimited Speech Duration Using External Memory

- Operates up to 12.32 MIPS

- Supports High-Quality Algorithms Such as MELP (1.0 Kbps – 3.5 Kbps at 8 kHz), CELP (3.0 Kbps – 11.2 kHz at 8 kHz Sampling Rate), ADPCM, Single Channel FM With CELP or MELP

- Speed and Pitch Shifting in MELP for Various Voice Effects

- Six Level Digital Gain Control

- 4 User Configurable I/O's

- Very Low-Power Operation, Ideal for Hand-Held Devices

- Low-Voltage Operation, Sustainable by Three (3) Batteries

- Three Reduced Power Standby Modes, Less Than 10 μA in Deep-Sleep Mode

- Resistor-Trimmed Oscillator or 32.768-kHz

Crystal Reference Oscillator

- Direct Speaker Drive (32 Ω) (PDM)

- Interrupt Driven, 4- or 8-Bit Parallel Data Transfer Protocol

- Available in Die Form or 64-Pin PM Package

#### description

The MSP53C691 is a standard slave synthesizer from Texas Instruments that accepts compressed speech data from other microprocessors/microcontrollers and converts it to speech. This allows the TI MSP53C691 to be used with a master microprocessor/microcontroller in various speech-related products such as security systems, learning aids, games, and toys. High quality, low bit-rate coders, easy interface with the master microcontroller, digital gain control, low power sleep mode, and low voltage operation makes this device ideal for products requiring long duration speech, less development cycle times, and peripheral device control through the slave device.

This device supports several speech synthesis algorithms that permit tradeoffs to meet the price performance requirements of various markets. The MSP53C691 implements a unique feature of playing a single channel FM music along with CELP or MELP speech data concurrently. This feature allows the user to speak a certain phrase in MELP or CELP with single channel music in the background.

The MSP53C691 is optimized to support a 4-bit wide data transfer protocol. The device has two status bits and three control bits that control the communication protocol between the master and the slave. The MSP53C691 also has 1 bit (command/data) which differentiates between a command or speech data feeding into the slave. In 4-bit mode, various commands are sent to the slave during speech to perform various tasks.

The MSP53C691 also supports the 8-bit wide data transfer but the support for commands is disabled during speaking-a-phrase. When speaking-a-phrase in 8-bit mode is complete, the MSP53C691 switches back to the 4-bit mode to receive the next command. Switching between 4-bit mode or 8 bit mode is permitted between speech data files.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

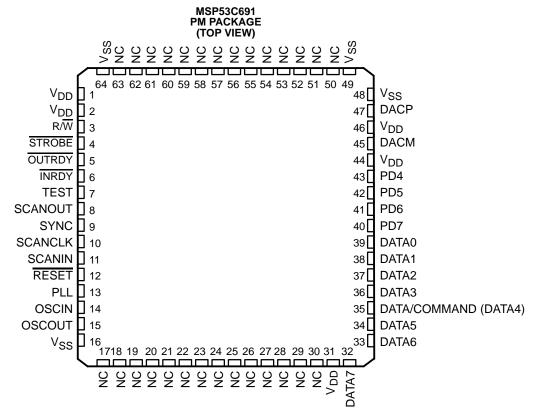

# pin assignments

NC - No internal connection

NOTE: Pin 35 is DATA4 in 8-bit mode, or DATA/COMMAND in 4-bit mode.

MSP53C691

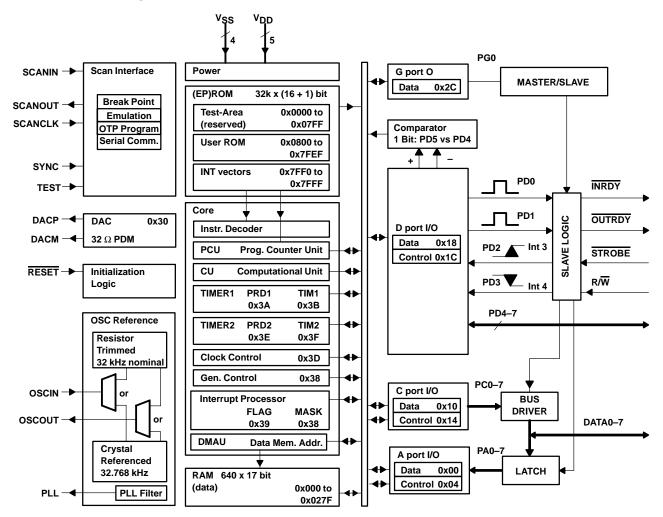

# functional block diagram

## **Terminal Functions**

| NAME                     | PIN<br>NO.                       | PAD<br>NO.                       | I/O | DESCRIPTION                                                                                                                                                                                                                                                |  |  |  |

|--------------------------|----------------------------------|----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DATA0-DATA3              | 39–36                            | 25–22                            | I/O | Data bits 0 through 3 (in 4-bit or 8-bit mode)                                                                                                                                                                                                             |  |  |  |

| DATA4 or<br>DATA/COMMAND | 35                               | 21                               | I/O | Data bit 4 (in 8-bit mode) Data/command control bit (in 4-bit mode). Low signal indicates command and high signal indicates data.                                                                                                                          |  |  |  |

| DATA5-DATA7              | 34–32                            | 20–18                            | I/O | Data bits 5 through 7 (8-bit mode only) Not used (4-bit mode only)                                                                                                                                                                                         |  |  |  |

| INRDY                    | 6                                | 6                                | 0   | An output signal from the slave to the microcontroller. A low signal indicates that the MSP53C691 is ready to accept data or command. A high signal indicates that the MSP53C691 is busy and the microcontroller must not write any data or command to it. |  |  |  |

| OUTRDY                   | 5                                | 5                                | 0   | An output signal from the slave to the microcontroller. A low signal indicates that the MSP53C691 is ready to send data or command to the microcontroller.                                                                                                 |  |  |  |

| PD4-PD7                  | 43–40                            | 29–26                            | I/O | General-purpose I/O bus                                                                                                                                                                                                                                    |  |  |  |

| R/W                      | 3                                | 3                                | ı   | An input signal to the slave from the microcontroller. Read/write select signal which is set high for read operations or set low for write operations by the microcontroller.                                                                              |  |  |  |

| STROBE                   | 4                                | 4                                | I   | An input signal to the slave from the microcontroller. STROBE sequences read or write operations in conjunction with the R/W signal. This signal is pulsed high-low-high for read or write operations sequencing.                                          |  |  |  |

|                          |                                  |                                  |     | Reference Oscillator Signals                                                                                                                                                                                                                               |  |  |  |

| OSCOUT                   | 15                               | 15                               | 0   | Output of resistor/crystal oscillator                                                                                                                                                                                                                      |  |  |  |

| OSCIN                    | 14                               | 14                               | I   | Input to resistor/crystal oscillator                                                                                                                                                                                                                       |  |  |  |

| PLL                      | 13                               | 13                               | 0   | Output of phase-lock-loop filter                                                                                                                                                                                                                           |  |  |  |

|                          |                                  | _                                |     | Scan Port Control Signals                                                                                                                                                                                                                                  |  |  |  |

| SCANIN†                  | 11                               | 39                               | I   | Scan port data input                                                                                                                                                                                                                                       |  |  |  |

| SCANOUT <sup>†</sup>     | 8                                | 35                               | 0   | Scan port data output                                                                                                                                                                                                                                      |  |  |  |

| SCANCLK <sup>†</sup>     | 10                               | 38                               | I   | Scan port clock                                                                                                                                                                                                                                            |  |  |  |

| SYNCT                    | 9                                | 37                               | I   | Scan port synchronization                                                                                                                                                                                                                                  |  |  |  |

| TEST <sup>†</sup>        | 7                                | 36                               | ı   | C604: test modes                                                                                                                                                                                                                                           |  |  |  |

|                          |                                  |                                  |     | Digital-to-Analog Sound Output                                                                                                                                                                                                                             |  |  |  |

| DACP                     | 47                               | 33                               | 0   | Digital-to-analog plus output (+)                                                                                                                                                                                                                          |  |  |  |

| DACM                     | 45                               | 31                               | 0   | Digital-to-analog minus output(–)                                                                                                                                                                                                                          |  |  |  |

|                          | Initialization                   |                                  |     |                                                                                                                                                                                                                                                            |  |  |  |

| RESET                    | 12                               | 12                               | I   | Device initialization                                                                                                                                                                                                                                      |  |  |  |

|                          |                                  |                                  |     | Power Signals‡                                                                                                                                                                                                                                             |  |  |  |

| V <sub>DD</sub>          | 1, 2, 31,<br>44, 46 <sup>‡</sup> | 1, 2, 17,<br>30, 32 <sup>‡</sup> |     | Processor power, 5 V nominal supply voltage                                                                                                                                                                                                                |  |  |  |

| VSS                      | 16, 48,<br>49 <sup>‡</sup> , 64  | 16, 34 <sup>‡</sup> ,<br>35, 36  |     | Ground pin                                                                                                                                                                                                                                                 |  |  |  |

<sup>†</sup> All pins must be N.C.

‡ Marked pins are V<sub>DD</sub> and V<sub>SS</sub> connections which service the DAC circuitry. These pins tend to sustain a higher current draw. A dedicated decoupling capacitor across these pins is therefore required.

SPSS030A - DECEMBER 2000 - REVISED FEBRUARY 2001

|                                       | MSP53C691<br>(4-bit mode)     | MSP53C691<br>(8-bit mode) |

|---------------------------------------|-------------------------------|---------------------------|

| Number of data lines                  | 4                             | 8                         |

| Number of control lines               | 3 (strobe, R/W, data/command) | 2 (strobe, R/W)           |

| Number of status lines                | 2 (INRDY, OUTRDY)             | 2 (INRDY, OUTRDY)         |

| Number of general-purpose I/O lines   | 4                             | 4                         |

| Support for commands (while speaking) | Yes                           | No                        |

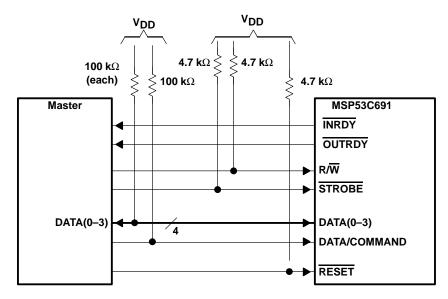

NOTE: STROBE Active low strobe signal from microcontroller Read/write signal from microcontroller RESET Active low reset signal from microcontroller

DATA0-DATA3 Data bits 0 through 3

PD4-PD7 General-purpose I/O bus

DACP Output to speaker/amplifier

DACM Output to speaker/amplifier

DATA/COMMAND This bit determines if the data sent by the microcontroller is data or command.

Figure 1. MSP53C691 Interfacing Diagram—4-Bit Mode

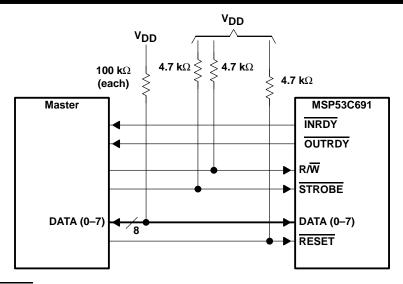

NOTE: STROBE: Active low strobe signal from microcontroller Red/write signal from microcontroller RESET Active low reset signal from microcontroller.

INRDY:

Active low indicates that the MSP53C691 is ready to accept data.

OUTRDY:

Active low indicates that the MSP53C691 is ready to send data.

DATA0-DATA7 Data bits 0 through 7

PD4-PD7 General-purpose I/O bus

DACP Output to speaker/amplifier

DACM Output to speaker/amplifier

Figure 2. MSP53C691 Interfacing Diagram—8-Bit Mode

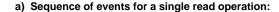

# read operation by the master

The process for the read operation by the master is the same in either 4-bit or 8-bit mode. The read operation by the master happens when the slave wants to send something to the master. The read process is initiated by the slave by pulling OUTRDY low when it is ready.

The following events take place during the read operation:

- The MSP53C691 puts the data to be sent to the master on the internal bus.

- The MSP53C691 sets OUTRDY low to indicate that it is ready to send data to the microcontroller.

- The microcontroller sets R/W high to indicate a read operation.

- The microcontroller sets STROBE low. The data is available on the external data-bus at this point.

- The microcontroller reads the data from the bus.

- The microcontroller sets STROBE high. The MSP53C691 also pulls OUTRDY high at the rising edge of STROBE.

- The data is taken from the external data-bus after STROBE goes high.

The microcontroller should latch or read in the data while STROBE is low. When the microcontroller sets STROBE high, the MSP53C691 sets OUTRDY high to indicate that the data has been successfully transferred.

Figure 3 shows the sequence of events of the read operation.

MSP53C691

## read operation by the master (continued)

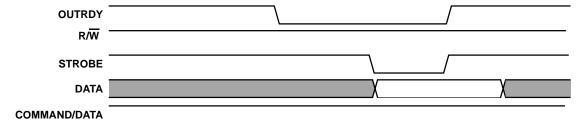

#### b) Read—Two speech data transfer sequences:

Figure 3. Data Transfer - Read

## write operation by the master

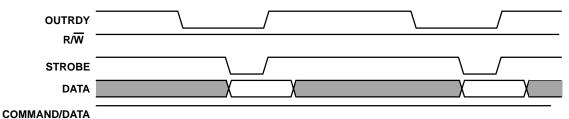

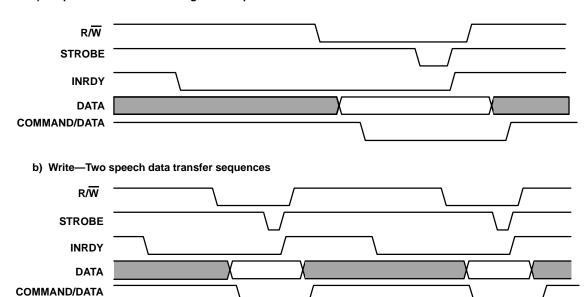

The process for the write operation by the master is the same in either 4-bit or 8-bit mode. The write operation by the master happens when the slave is ready to request data or command from the master. The write process is initiated by the slave by pulling  $\overline{\text{INRDY}}$  low when the slave is ready to receive data.

The following events take place during the write operation:

- The MSP53C691 sets INRDY low to indicate that it is ready to receive data from the microcontroller.

- The microcontroller sets  $R/\overline{W}$  low to indicate a write operation.

- The microcontroller puts the data in the external data-bus.

- The microcontroller sets STROBE low after the data is valid.

- The microcontroller sets STROBE high after a minimum of 300 ns. The MSP53C691 also pulls INRDY high at the rising edge of STROBE.

- The data is latched in the MSP53C691 at the rising edge of STROBE.

# write operation by the master (continued)

When the microcontroller sets  $\overline{\text{STROBE}}$  high, the MSP53C691 sets  $\overline{\text{INRDY}}$  high to indicate that the MSP53C691 is not ready to receive any more data.

#### a) Sequence of events for a single write operation

Figure 4. Data Transfer - Write

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, V <sub>DD</sub> (see Note 1)     | 0.3 V to 7 V                              |

|--------------------------------------------------|-------------------------------------------|

| Supply current, I <sub>DD</sub> (see Note 2)     | 35 mA                                     |

| Input voltage range, V <sub>I</sub> (see Note 1) | $0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Output voltage range, VO (see Note 1)0           | .3 V to V <sub>DD</sub> + 0.3 V           |

| Storage temperature range, $T_{\Delta}$          | –30°C to 125°C                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## recommended operating conditions

|                                                                    |                      | MIN | MAX    | UNIT |

|--------------------------------------------------------------------|----------------------|-----|--------|------|

| Supply voltage, V <sub>DD</sub> (with respect to V <sub>SS</sub> ) | 3                    | 5.2 | V      |      |

| CPU clock rate, f(CPU) (as programmed)                             |                      | 64  | 12,320 | kHz  |

| Load resistance between DACP and DACM, R(DAC)                      |                      | 32  |        | Ω    |

| Operating free-air temperature, T <sub>A</sub>                     | Device functionality | 0   | 70     | °C   |

# timing requirements

|                 |                                                                                   | MIN | MAX | UNIT               |

|-----------------|-----------------------------------------------------------------------------------|-----|-----|--------------------|

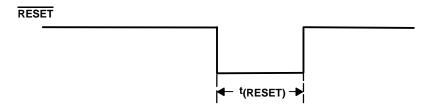

| t(RESET)        | Reset pulsed low, while 'C691 has power applied                                   | 100 |     | ns                 |

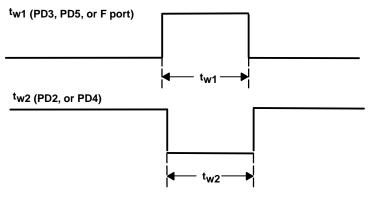

| t <sub>w1</sub> | Pulse width required prior to a negative transition at pin (PD3 or PD5 interrupt) | 2   |     | 1/F <sub>CPU</sub> |

| t <sub>w2</sub> | Pulse width required prior to a positive transition at pin (PD2 or PD4 interrupt) | 2   |     | 1/F <sub>CPU</sub> |

Figure 5. Initialization Timing Diagram

Figure 6. MSP53C691 External Interrupt Pin Pulse Width Requirements tw1 and tw2

NOTES: 1. Unless otherwise noted, all voltages are measured with respect to VSS.

<sup>2.</sup> The total supply current includes the current out of all the I/O pins as well as the operating current of the device.

# dc electrical characteristics over recommended operating free-air temperature range, $T_A=0^\circ C-70^\circ C$ (unless otherwise noted)

| PARAMETER             |                                                     |                                                                              | TEST CONDITIONS                                                                             | MIN | TYP <sup>†</sup> | MAX  | UNIT |

|-----------------------|-----------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|------------------|------|------|

|                       |                                                     |                                                                              | Positive going threshold                                                                    |     | 2.4              |      |      |

|                       |                                                     | V <sub>DD</sub> = 3 V                                                        | Negative going threshold                                                                    |     | 1.8              |      | V    |

|                       |                                                     |                                                                              | Hysteresis                                                                                  |     | 0.6              |      |      |

| RESET                 | Threshold changes                                   |                                                                              | Positive going threshold                                                                    |     | 3.3              |      |      |

|                       |                                                     | $V_{DD} = 5.2 \text{ V}$                                                     | Negative going threshold                                                                    |     | 2.9              |      | V    |

|                       |                                                     |                                                                              | Hysteresis                                                                                  |     | 0.4              |      |      |

|                       | LPak Javal Sanut                                    | V <sub>DD</sub> = 3 V                                                        |                                                                                             | 2   |                  | 3    |      |

| VIH                   | High-level input voltage                            | V <sub>DD</sub> = 4.5 V                                                      |                                                                                             | 3   |                  | 4.5  | V    |

|                       | voltage                                             | V <sub>DD</sub> = 5.2 V                                                      |                                                                                             |     |                  |      |      |

|                       |                                                     | V <sub>DD</sub> = 3 V                                                        |                                                                                             | 0   |                  | 1    |      |

| VIL                   | Low-level input voltage                             | V <sub>DD</sub> = 4.5 V                                                      |                                                                                             | 0   |                  | 1.5  | V    |

|                       | voltago                                             | V <sub>DD</sub> = 5.2 V                                                      |                                                                                             | 0   |                  | 1.7  |      |

| I <sub>OH</sub> §     | High-level output<br>current per pin of<br>I/O port |                                                                              | V <sub>OH</sub> = 4 V                                                                       |     |                  | -2   | mA   |

| I <sub>OL</sub> §     | Low-level output<br>current per pin of<br>I/O port  | V <sub>DD</sub> = 4.5 V                                                      | V <sub>OL</sub> = 0.5 V                                                                     |     |                  | 5    | mA   |

| IOH (DAC)             | High-level output DAC current                       |                                                                              | V <sub>OH</sub> = 4 V                                                                       |     |                  | -10  | mA   |

| IOL (DAC)             | Low-level output DAC current                        |                                                                              | V <sub>OL</sub> = 0.5 V                                                                     |     |                  | 20   | mA   |

| l <sub>lkg</sub>      | Input leakage<br>current                            | Excludes OSC <sub>IN</sub>                                                   |                                                                                             |     | 1                | μА   |      |

| I(STANDBY)            | Standby current                                     | RESET is low                                                                 |                                                                                             |     | 0.05             | 10   | μΑ   |

| I <sub>DD</sub>       | Operating current                                   | $V_{DD} = 4.5 V$ ,                                                           | FCLOCK = 12.32 MHz                                                                          |     | 15               |      | mA   |

| I(SLEEP-deep)         |                                                     | $V_{DD} = 4.5 V$ ,                                                           | DAC off, ARM set, OSC disabled                                                              |     | 0.05             | 10   |      |

| I(SLEEP-mid)          | Supply current                                      | $V_{DD} = 4.5 V$ ,                                                           | DAC off, ARM set, OSC enabled                                                               |     | 40               | 60   | μΑ   |

| I(SLEEP-light)        |                                                     | $V_{DD} = 4.5 V$ ,                                                           | DAC off, ARM clear, OSC enabled                                                             |     | 60               | 100  |      |

| $V_{IO}$              | Input offset voltage                                | $V_{DD} = 4.5 V$ ,                                                           | Vref = 1 to 4.25 V                                                                          |     | 25               | 50   | mV   |

| R(PULLUP)             | F port pullup resistance                            | V <sub>DD</sub> = 5 V                                                        |                                                                                             | 70  | 150              |      | kΩ   |

| $\Delta f$ (RTO–trim) | Trim deviation                                      | \ - /                                                                        | $V_{DD} = 4.5 \text{ V},  T_A = 25^{\circ}\text{C},$ Hz (PLL setting = 7 Ch) <sup>‡</sup>   |     | ±1%              | ±3%  |      |

| $\Delta f$ (RTO-volt) | Voltage deviation                                   | $R_{RTO} = 470 \text{ k}\Omega$                                              | $V_{DD}$ = 3.5 to 5.2 V, $T_A$ = 25°C, Hz (PLL setting = 7 Ch)‡                             |     |                  | ±1.5 | %/V  |

| Δf(RTO-temp)          | Temperature deviation                               |                                                                              | $V_{DD} = 4.5 \text{ V},  T_A = 0 \text{ to } 70^{\circ}\text{C},$ Hz (PLL setting = 7 Ch)‡ |     | ±0.03            |      | %/°C |

| $\Delta f$ (RTO-res)  | Resistance deviation                                | V <sub>DD</sub> = 4.5 V,                                                     | $T_A = 25$ °C, $R_{OSC} = 470 \text{ k}\Omega \text{ at } \pm 1\%$ ,                        |     | ±1               |      | %/R  |

| † Tomical caltage     |                                                     | $f(RTO) = 8.192 \text{ MHz} (PLL \text{ setting} = 7 \text{ Ch})^{\ddagger}$ |                                                                                             |     |                  |      |      |

<sup>†</sup> Typical voltage and current measurements taken at 25°C,

# external component absolute values

| PARAMETER          |                          | TEST CONDITIONS        |               | MIN | MAX  | UNIT |

|--------------------|--------------------------|------------------------|---------------|-----|------|------|

| R <sub>(RTO)</sub> | RTO external resistance  | T <sub>A</sub> = 25°C, | 1% tolerance  |     | 470  | kΩ   |

| C <sub>(PLL)</sub> | PLL external capacitance | T <sub>A</sub> = 25°C, | 10% tolerance |     | 3300 | pF   |

<sup>&</sup>lt;sup>‡</sup> The best trim value is selected at nominal temperature and voltage but the deviation due to the trim error is ignored.

<sup>§</sup> This parameter cannot exceed 15 mA total per internal VDD pin. Port C and port D share 1 internal VDD. Ports A and G0 are used internally.

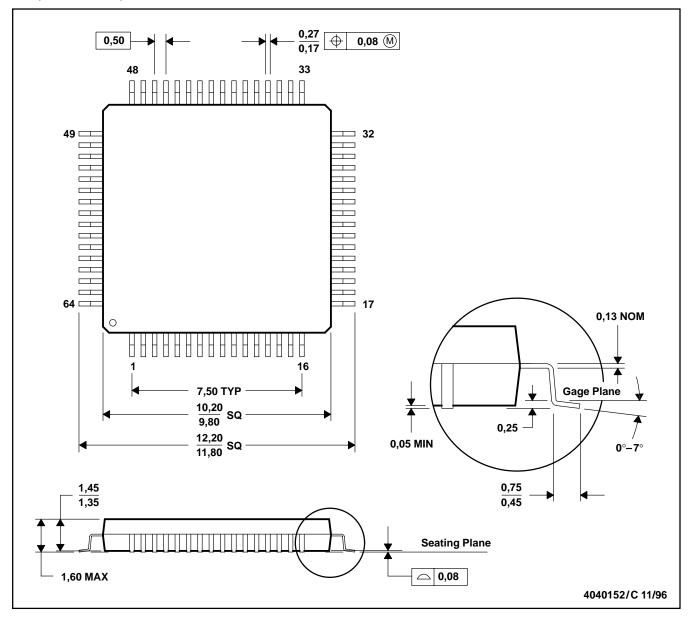

## **MECHANICAL DATA**

## PM (S-PQFP-G64)

#### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-026

- D. May also be thermally enhanced plastic with leads connected to the die pads.

#### PACKAGE OPTION ADDENDUM

30-Mar-2005

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|------------------------------|

| MSP53C691PM      | OBSOLETE              | LQFP            | PM                 | 64                  | TBD                     | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check <a href="http://www.ti.com/productcontent">http://www.ti.com/productcontent</a> for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

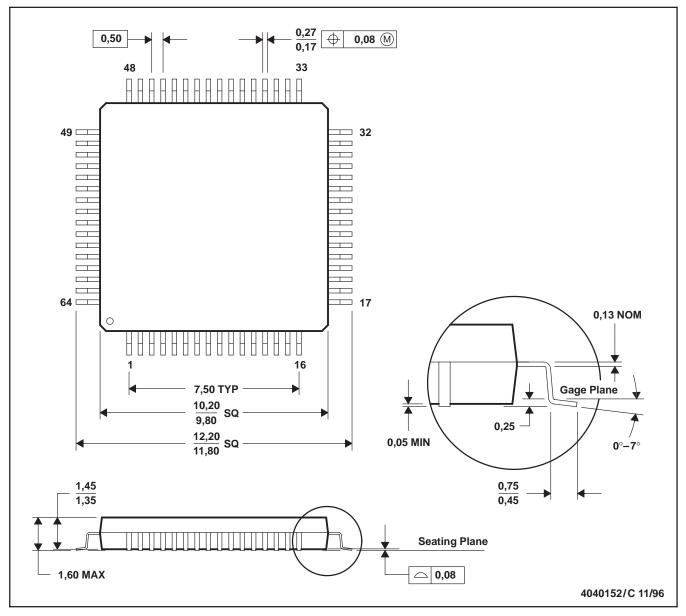

# PM (S-PQFP-G64)

#### PLASTIC QUAD FLATPACK

1

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-026

- D. May also be thermally enhanced plastic with leads connected to the die pads.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated