# OKI Semiconductor MSM7620

Echo Canceler

# **GENERAL DESCRIPTION**

The MSM7620 is an improved version of the MSM7520 with the same basic configuration. The MSM7620 includes following improvements: a modified through mode, timing control of the control pin input, and a thinner package. The MSM7620 also provides a pin-for-pin replacement with the MSM7520.

The MSM7620 is a low-power CMOS IC device for canceling echo (in an acoustic system or telephone line) generated in a speech path.

Echo is canceled (in digital signal processing) by estimating the echo path and generating a pseudo-echo signal.

Used as an acoustic echo canceler, the MSM7620 cancels the acoustic echo between the loud speaker and the microphone which occurs during hands free communication, such as on a car phone or a conference system phone.

Used as a line echo canceler, the device cancels the line echo impedance mismatching in a hybrid. In addition, a quality conversation is made possible by controlling the level and preventing howling with a howling detector, double talk detector, attenuation function and a gain control function, and by controlling the low level noise with a center clipping function.

The MSM7620 I/O interface supports  $\mu$ -law PCM. The use of a single chip CODEC, such as the MSM7543, allows the configuration an economic and efficient echo canceler to be configured.

Note: If the object is to cancel line echo, the use of the MSM7602 is recommended, for the MSM7602 is provided with a howling detect control pin. In addition, the MSM7602, while having characteristics equivalent to the MSM7620, is packaged small.

# FEATURES

- Handles both acoustic echoes and telephone line echoes.

- Cancelable echo delay time:

| MSM7620-001                           | For a single chip: 23 ms (max.)                               |

|---------------------------------------|---------------------------------------------------------------|

| MSM7620-011                           | For a cascade connection (can also be used for a single chip) |

|                                       | Master chip: 23 ms (max.)                                     |

|                                       | Slave chip: 31 ms (max.)                                      |

|                                       | Cancelable up to 213 ms (one master plus six slaves)          |

|                                       | For a single chip: 23 ms (max.)                               |

| <ul> <li>Echo attenuation</li> </ul>  | : 30 dB (typ.)                                                |

| <ul> <li>Clock frequency</li> </ul>   | : 18 MHz (36 MHz cannot be used)                              |

|                                       | External input and internal oscillator circuit are provided.  |

| • Power supply voltage                | : 5 V (4.5 V to 5.5 V)                                        |

| <ul> <li>Power consumption</li> </ul> | : 150 mW (typ.) When powered down: 20 mW (typ.)               |

| <ul> <li>Package options:</li> </ul>  |                                                               |

| 32-pin plastic SSOP (SS               | GOP32-P-640-0.80-K) (Product name : MSM7620-001GS-K)          |

| 64-pin plastic QFP (QF                | P64-P-1414-0.80-BK) (Product name : MSM7620-011GS-BK)         |

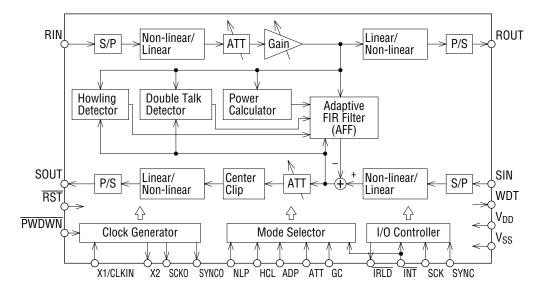

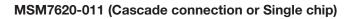

# BLOCK DIAGRAM MSM7620-001 (Single chip only)

\* If the MSM7620-011 is used in the slave mode, only the diagonally hatched blocks and the pins marked with \* are used.

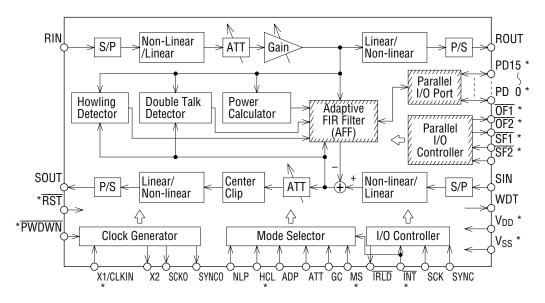

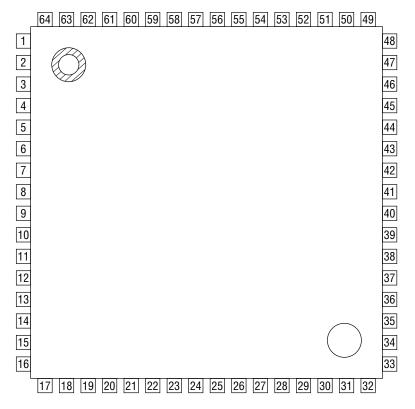

# **PIN CONFIGURATION (TOP VIEW)**

# 32-Pin Plastic SSOP

| Pin | Symbol          | Pin | Symbol          | Pin | Symbol   | Pin | Symbol          |

|-----|-----------------|-----|-----------------|-----|----------|-----|-----------------|

| 1   | *               | 9   | SIN             | 17  | *        | 25  | SCKO            |

| 2   | NLP             | 10  | RIN             | 18  | *        | 26  | *               |

| 3   | HCL             | 11  | SCK             | 19  | *        | 27  | RST             |

| 4   | ADP             | 12  | SYNC            | 20  | X1/CLKIN | 28  | WDT             |

| 5   | V <sub>SS</sub> | 13  | SOUT            | 21  | X2       | 29  | GC              |

| 6   | ATT             | 14  | ROUT            | 22  | *        | 30  | *               |

| 7   | INT             | 15  | *               | 23  | PWDWN    | 31  | *               |

| 8   | ĪRLD            | 16  | V <sub>SS</sub> | 24  | SYNCO    | 32  | V <sub>DD</sub> |

\*: No connect pin

Note: Pin 26 of the MSM7520 is CKSEL, while that of the MSM7620 is in open state. It is possible to replace the MSM7520 with the MSM7620.

### 64-Pin Plastic SSOP

| Pin | Symbol          | Pin | Symbol | Pin | Symbol          | Pin | Symbol          |

|-----|-----------------|-----|--------|-----|-----------------|-----|-----------------|

| 1   | NLP             | 17  | *      | 33  | PD12            | 49  | *               |

| 2   | HCL             | 18  | *      | 34  | PD13            | 50  | *               |

| 3   | ADP             | 19  | PD0    | 35  | X1/CLKIN        | 51  | PD14            |

| 4   | MS              | 20  | PD1    | 36  | X2              | 52  | PD15            |

| 5   | ATT             | 21  | PD2    | 37  | *               | 53  | *               |

| 6   | INT             | 22  | PD3    | 38  | PWDWN           | 54  | SF2             |

| 7   | *               | 23  | PD4    | 39  | *               | 55  | 0F1             |

| 8   | IRLD            | 24  | PD5    | 40  | SYNCO           | 56  | *               |

| 9   | *               | 25  | PD6    | 41  | SCKO            | 57  | *               |

| 10  | SIN             | 26  | PD7    | 42  | *               | 58  | *               |

| 11  | RIN             | 27  | PD8    | 43  | *               | 59  | SF1             |

| 12  | SCK             | 28  | PD9    | 44  | RST             | 60  | 0F2             |

| 13  | SYNC            | 29  | PD10   | 45  | WDT             | 61  | *               |

| 14  | SOUT            | 30  | PD11   | 46  | GC              | 62  | V <sub>DD</sub> |

| 15  | ROUT            | 31  | *      | 47  | V <sub>DD</sub> | 63  | *               |

| 16  | V <sub>SS</sub> | 32  | *      | 48  | V <sub>DD</sub> | 64  | *               |

\*: No connect pin

Note: Pins 43, 53, and 61 of the MSM7520 are CKSEL, V<sub>DD</sub>, and TST2 respectively. While these pins of the MSM7620 are in open state, it is possible to replace the MSM7520 with the MSM7620.

# **PIN DESCRIPTIONS (1/5)**

| Pin            |               |        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------------|---------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 32-pin<br>SSOP | 64-pin<br>QFP | Symbol | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 2              | 1             | NLP    | 1    | The control pin for the center clipping function. This forces the SOUT<br>output to a minimum value (FF) when the SOUT signal is below -54<br>dBm0. Effective for reducing low-level noise.<br>• Single Chip or Master Chip in a Cascade Connection<br>"H": Center clip ON<br>"L": Center clip OFF<br>• Slave Chip in a Cascade Connection<br>Fixed at "L"<br>This input signal is loaded in synchronization with the falling edge of<br>the INT signal or the rising edge of the RST signal.                                                                                                                                                                                                        |  |  |

| 3              | 2             | HCL    | 1    | <ul> <li>The through mode control.</li> <li>When this pin is in the through mode, RIN and SIN data are output to ROUT and SOUT. At the same time, the coefficient of the adaptive FIR filter is cleared.</li> <li>Single Chip or Master Chip in a Cascade Connection <ul> <li>"H": Through mode</li> <li>"L": Normal mode (echo canceler operates)</li> </ul> </li> <li>Slave Chip in a Cascade Connection <ul> <li>Same as master</li> </ul> </li> <li>This input signal is loaded in synchronization with the falling edge of the INT signal or the rising edge of the RST signal.</li> </ul>                                                                                                      |  |  |

| 4              | 3             | ADP    | 1    | <ul> <li>AFF coefficient control pin. This pin stops updating of the adaptive FIR filter (AFF) coefficient and sets the coefficient to a fixed value, when this pin is configured to be the coefficient fix mode.</li> <li>This pin is used when holding the AFF coefficient which has been once converged.</li> <li>Single Chip or Master Chip in a Cascade Connection <ul> <li>"H": Coefficient fix mode</li> <li>"L": Normal mode (coefficient update)</li> </ul> </li> <li>Slave Chip in a Cascade Connection <ul> <li>Fixed at "L"</li> </ul> </li> <li>This input signal is loaded in synchronization with the falling edge of the INT signal or the rising edge of the RST signal.</li> </ul> |  |  |

| _              | 4             | MS     | I    | Selection of the Master Chip and slave chip when used in a cascade<br>connection.<br>"L": Single chip or master chip<br>"H": Slave chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| (2/5) |

|-------|

|-------|

| P              | 'n            |        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|---------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-pin<br>SSOP | 64-pin<br>QFP | Symbol | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6              | 5             | ATT    | 1    | Control for the ATT function that prevents howling by attenuators (ATT)<br>for the RIN input and SOUT output.<br>If there is input only to RIN, then the ATT for the SOUT output is<br>activated.<br>If there is no input to SIN, or if there is input to both SIN and RIN, the<br>ATT for the RIN input is activated.<br>Either the ATT for the RIN output or the ATT for the SOUT is always<br>activated in all cases, and the attenuation of ATT is 6 dB.<br>• Single Chip or Master Chip in a Cascade Connection<br>"H": ATT OFF<br>"L": ATT OFF<br>"L" is recommended for echo cancellation.<br>• Slave Chip in a Cascade Connection<br>• Fixed at "L"<br>This input signal is loaded in synchronization with the falling edge of the<br>INT signal or the rising edge of the RST signal. |

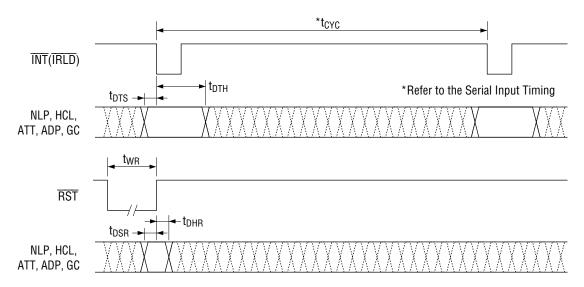

| 7              | 6             | ĪNT    | Ι    | <ul> <li>Interrupt signal which starts 1 cycle (8 kHz) of the signal processing.</li> <li>Signal processing starts when H-to-L transition is detected.</li> <li>Single Chip or Master Chip in a Cascade Connection<br/>Connect the IRLD pin.</li> <li>Slave Chip in a Cascade Connection<br/>Connect the IRLD pin of the master chip.</li> <li>INT input is invalid for 100 μs after reset due to initialization. Refer to the control pin connection example.</li> </ul>                                                                                                                                                                                                                                                                                                                      |

| 8              | 8             | ĪRLD   | 0    | <ul> <li>Load detection signal when the SIN and RIN serial input data is loaded in the internal registers.</li> <li>Single Chip Connect to the INT pin.</li> <li>Master Chip in a Cascade Connection Connect to the INT pin of the master chip and all the slave chips.</li> <li>Slave Chip in a Cascade Connection Leave open.</li> <li>Refer to the control pin connection example.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |

| 9              | 10            | SIN    | I    | Transmit serial data. Input the $\mu$ -law PCM signal synchronized to SYNC and SCK. Data is read in at the fall of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | in            |          |      |                                                                                                                |  |  |  |

|----------------|---------------|----------|------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| 32-pin<br>SSOP | 64-pin<br>QFP | Symbol   | Туре | Description                                                                                                    |  |  |  |

| 10             | 11            | RIN      | I    | Receive serial data.                                                                                           |  |  |  |

|                |               |          |      | Input the $\mu\text{-}\text{law}$ PCM signal synchronized to SYNC and SCK. Data is read in at the fall of SCK. |  |  |  |

| 11             | 12            | SCK      |      | Clock pin for transmit/receive serial data. This pin uses the external                                         |  |  |  |

|                |               |          |      | SCK or the SCKO.                                                                                               |  |  |  |

|                |               |          |      | Input the PCM CODEC transmit/receive clock (64 to 2048 kHz).                                                   |  |  |  |

| 12             | 13            | SYNC     | I    | Sync signal for transmit/receive serial data. This pin uses the external                                       |  |  |  |

|                |               |          |      | SYNC or SYNCO.                                                                                                 |  |  |  |

|                |               |          |      | Input the PCM CODEC transmit/receive sync signal (8 kHz).                                                      |  |  |  |

| 13             | 14            | SOUT     | 0    | Transmit serial data.                                                                                          |  |  |  |

|                |               |          |      | This pin outputs the $\mu\text{-law}$ PCM signal synchronized to SYNC and SCK.                                 |  |  |  |

|                |               |          |      | This pin is in a high impedance state while there is no data output.                                           |  |  |  |

| 14             | 15            | ROUT     | 0    | Receive serial data.                                                                                           |  |  |  |

|                |               |          |      | This pin outputs the $\mu$ -law PCM signal synchronized to SYNC and SCK.                                       |  |  |  |

|                |               |          |      | This pin is in a high impedance state while there is no data output.                                           |  |  |  |

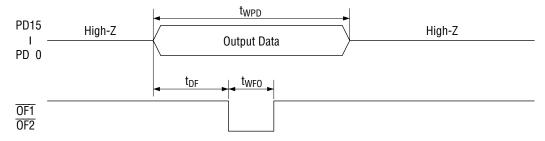

| _              | 19            | PD0      | I/0  | Bidirectional bus for parallel data transfer between the Master Chip and                                       |  |  |  |

|                |               |          |      | Slave Chip when used in a cascade connection.                                                                  |  |  |  |

| _              | 30            | PD11     |      | The PD15 pin corresponds to MSB.                                                                               |  |  |  |

| _              | 33            | PD12     |      | This pin is in a high impedance state while there is no data output. Dat                                       |  |  |  |

| _              | 34            | PD13     |      | is loaded in at the falling edge of SFx.                                                                       |  |  |  |

| _              | 51            | PD14     |      |                                                                                                                |  |  |  |

| _              | 52            | PD15     |      |                                                                                                                |  |  |  |

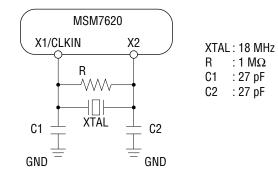

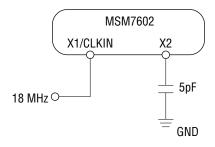

| 20             | 35            | X1/CLKIN |      | External input for the basic clock or for the crystal oscillator.                                              |  |  |  |

|                |               |          |      | Input the basic clock (18 MHz).                                                                                |  |  |  |

|                |               |          |      | Refer to the internal clock generator circuit example.                                                         |  |  |  |

| 21             | 36            | X2       | 0    | Crystal oscilator.                                                                                             |  |  |  |

|                |               |          |      | Used to configure the oscillation circuit.                                                                     |  |  |  |

|                |               |          |      | Refer to the internal clock generator circuit example.                                                         |  |  |  |

|                |               |          |      | When inputting the basic clock externally, insert a 5 pF capacitor with                                        |  |  |  |

|                |               |          |      | excellent high frequency characteristics between X2 and GND.                                                   |  |  |  |

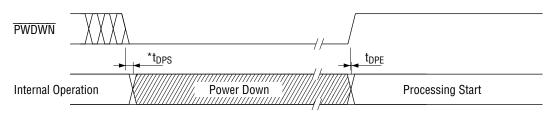

| 23             | 38            | PWDWN    |      | Power-down mode control.                                                                                       |  |  |  |

|                |               |          |      | "L": Power-down mode                                                                                           |  |  |  |

|                |               |          |      | "H": Normal operation mode                                                                                     |  |  |  |

|                |               |          |      | During power-down, all input pins are disabled and output pins are in                                          |  |  |  |

|                |               |          |      | the following sates :                                                                                          |  |  |  |

|                |               |          |      | High impedance : SOUT, ROUT, PD0 to 15                                                                         |  |  |  |

|                |               |          |      | "L": SYNCO, SCKO                                                                                               |  |  |  |

|                |               |          |      | "H": 0F1, 0F2                                                                                                  |  |  |  |

|                |               |          |      | Holds the last state : WDT, IRLD                                                                               |  |  |  |

|                |               |          |      | Not affected: X2, MCKO                                                                                         |  |  |  |

|                |               |          |      | Reset after power-down is released.                                                                            |  |  |  |

(4/5)

| P              | in            |        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|----------------|---------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 32-pin<br>SSOP | 64-pin<br>QFP | Symbol | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 24             | 40            | SYNCO  | 0    | 8 kHz sync signal for the PCM CODEC.<br>Connect this pin to the SYNC pin and the PCM CODEC transmit/receive<br>sync pin.<br>Leave it open if using an external SYNC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 25             | 41            | SCKO   | 0    | Transmit clock signal (200 kHz) for the PCM CODEC.<br>Connect this pin to the SCK pin and the PCM CODEC transmit/receive<br>clock pin.<br>Not affected by reset. Outputs "0" during power-down.<br>Leave it open if using an external SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 27             | 44            | RST    | 1    | Reset signal.<br>"L": Reset mode<br>"H": Normal operation mode<br>During initialization, input signals, except for <u>PWDWN</u> are disabled for<br>100 μs after reset (after <u>RST</u> is returned from "L" to "H").<br>Input the basic clock during the reset.<br>Output pins during reset are in the following sates :<br>High impedance: SOUT, ROUT, PD0 to 15<br>"L": WDT<br>"H": <u>OF1</u> , <u>OF2</u><br>Not affected: X2, SYNCO, SCKO, <u>IRLD</u> , MCKO                                                                                                                                                                                                                                                                                 |  |  |  |

| 28             | 45            | WDT    | 0    | Test pin.<br>Leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 29             | 46            | GC     | Ι    | Input signal for the gain controller when RIN input is controlled and the<br>RIN input level is controlled and howling is prevented.<br>The gain controller adjusts the RIN input level when it is -20 dBm0 or<br>above. RIN input levels from -20 to -11.5 dBm0 will be suppressed to<br>-20 dBm0 in the attenuation range from 0 to 8.5 dB.<br>RIN input levels above -11.5 dBm0 will always be attenuated by 8.5 dB.<br>• Single Chip or Master Chip in a Cascade Connection<br>"H": Gain control ON<br>"L": Gain control OFF<br>"H" is recommended for echo cancellation.<br>• Slave Chip in a Cascade Connection<br>Fixed at "L"<br>This pin is loaded in synchronization with the falling edge of the INT<br>signal or the rising edge of RST. |  |  |  |

| (5/5 | 5) |

|------|----|

|------|----|

| P      | Pin    |        |      |                                                                   |

|--------|--------|--------|------|-------------------------------------------------------------------|

| 32-pin | 64-pin | Symbol | Туре | Description                                                       |

| SSOP   | QFP    |        |      |                                                                   |

| _      | 54     | SF2    |      | Parallel data transfer flag.                                      |

|        |        |        |      | • Single Chip                                                     |

|        |        |        |      | Fixed at "H"                                                      |

|        |        |        |      | Master Chip in a Cascade Connection                               |

|        |        |        |      | Fixed at "H"                                                      |

|        |        |        |      | Slave Chip in a Cascade Connection                                |

|        |        |        |      | Connect OF2 of the master chip to the first stage slave chip.     |

|        |        |        |      | Connect OF1 of the previous stage slave chip to the second and    |

|        |        |        |      | later stage slave chips.                                          |

|        |        |        |      | Refer to the control pin connection example.                      |

|        | 55     | 0F1    | 0    | Parallel data transfer flag.                                      |

|        |        |        |      | Single Chip                                                       |

|        |        |        |      | Leave this pin open.                                              |

|        |        |        |      | Master Chip in a Cascade Connection                               |

|        |        |        |      | Connect to the SF1 of all slaves.                                 |

|        |        |        |      | <ul> <li>Slave chip in a Cascade Connection</li> </ul>            |

|        |        |        |      | Connect to the $\overline{SF2}$ of the next stage slave chip.     |

|        |        |        |      | Connect the last stage slave chip to the SF1 of the master chip.  |

|        |        |        |      | Refer to the control pin connection example.                      |

|        | 59     | SF1    | 1    | Parallel data transfer flag.                                      |

|        |        |        |      | • Single Chip                                                     |

|        |        |        |      | Connect OF2.                                                      |

|        |        |        |      | Master Chip in a Cascade Connection                               |

|        |        |        |      | Connect OF1 of the last stage slave chip.                         |

|        |        |        |      | Slave Chip in a Cascade Connection                                |

|        |        |        |      | Connect OF1 of master chip for all slave chips.                   |

|        |        |        |      | Refer to the control pin connection example.                      |

| _      | 60     | 0F2    | 0    | Parallel data output flag.                                        |

|        |        |        |      | Single Chip                                                       |

|        |        |        |      | Connect to SF1.                                                   |

|        |        |        |      | Master Chip in a Cascade Connection                               |

|        |        |        |      | Connect to $\overline{\text{SF2}}$ of the first stage slave chip. |

|        |        |        |      | Slave Chip in a Cascade Connection                                |

|        |        |        |      | Leave open.                                                       |

|        |        |        |      | Refer to the control pin connection example.                      |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol           | Condition | Rating                        | Unit |

|----------------------|------------------|-----------|-------------------------------|------|

| Power Supply Voltage | V <sub>DD</sub>  |           | -0.3 to +7                    | V    |

| Input Voltage        | VIN              | Ta = 25°C | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Power Dissipation    | PD               |           | 1                             | W    |

| Storage Temperature  | T <sub>STG</sub> | _         | -55 to +150                   | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol          | Condition          | Min. | Тур. | Max.            | Unit |

|-----------------------|-----------------|--------------------|------|------|-----------------|------|

| Power Supply Voltage  | V <sub>DD</sub> | —                  | 4.5  | 5    | 5.5             | V    |

| Power Supply Voltage  | V <sub>SS</sub> | —                  | _    | 0    | _               | V    |

| Input High Voltage    | N               | Pins other than X1 | 2.4  | _    | V <sub>DD</sub> | V    |

| Input High Voltage    | VIH             | X1 pin             | 3.5  | _    | V <sub>DD</sub> | V    |

| Input Low Voltage     | VIL             | _                  | 0    | _    | 0.8             | V    |

| Operating Temperature | Та              | _                  | -40  | +25  | +85             | °C   |

# ELECTRICAL CHARACTERISTICS DC Characteristics

#### $(Ta = -40^{\circ}C to +85^{\circ}C)$ Parameter Symbol Condition Min. Max. Unit Тур. **Output High Voltage** Vон $I_{OH} = 40 \ \mu A$ 4.2 V \_\_\_\_ $V_{DD}$ Output Low Voltage V<sub>OL</sub> 0 0.4 V $I_{0L} = 1.6 \text{ mA}$ \_ High Level Input Current $V_{IH} = V_{DD}$ \_\_\_\_ 10 IIH 0.1 μA SF1, SF2 VIL = -100 -50 -10 μA Vss to Vpp with pull-up Low Level Input Current Ι<sub>ΙL</sub> Input other than -10 -0.1 \_\_\_\_ μA the above High Level Output Current I<sub>OZH</sub> $V_{OH} = V_{DD}$ 0.1 10 μA — $V_{01} =$ PD15 to PD0 -100 -50 +10 μA V<sub>SS</sub> to V<sub>DD</sub> with pull-up Low Level Output Current I<sub>OZL</sub> Input other than -10 -0.1 μA \_\_\_\_ the above Power Supply Current 30 40 IDDO mΑ (Operating) When extarnal input is used Power Supply Current(Stand-by) 5 4 mΑ as basic clock IDDS When oscillation circuit is PWDWN="L" 6 8 mΑ \_\_\_\_ used as basic clock Input Capacitance CI \_\_\_\_ 15 pF \_\_\_\_ \_\_\_\_ Output Load Capacitance 20 рF CLOAD

| Parameter                                                                        | Symbol           | Condition                                                                                                                                      | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

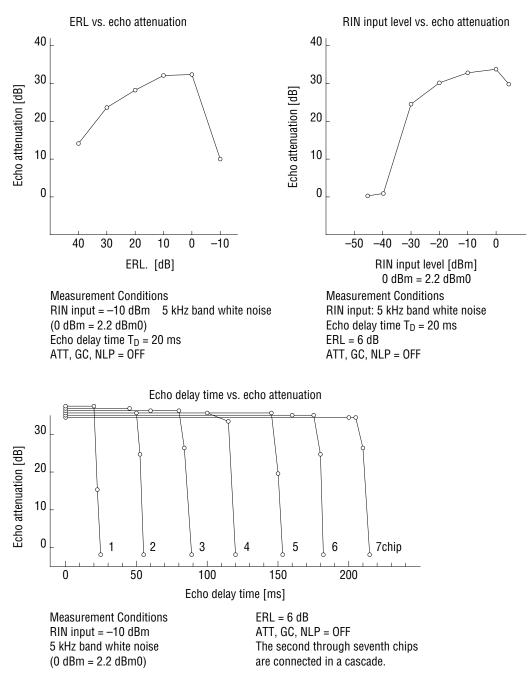

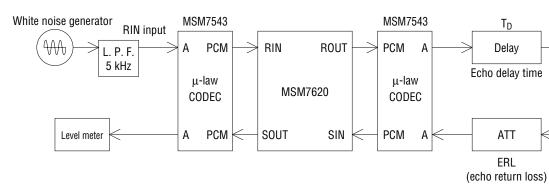

| Echo Attenuation                                                                 | L <sub>RES</sub> | R <sub>IN</sub> = -10 dBm0<br>(5 kHz band white noise)<br>E. R. L. (echo return loss)<br>= 6 dB<br>T <sub>D</sub> = 20 ms<br>ATT, GC, NLP: OFF | _    | 30   | _    | dB   |

| Cancelable Echo Delay Time for a<br>Single Chip or a Master Chip in a<br>Cascade | TD               | R <sub>IN</sub> = -10 dBm0<br>(5 kHz band white noise)<br>E.R.L. = 6 dB<br>ATT, GC, NLP: OFF                                                   |      | _    | 23   | ms   |

| Cancelable Echo Delay Time for a Slave Chip in a Cascade                         | T <sub>DS</sub>  |                                                                                                                                                |      | _    | 31   | ms   |

# Echo Canceler Characteristics (Refer to Characteristics Diagram)

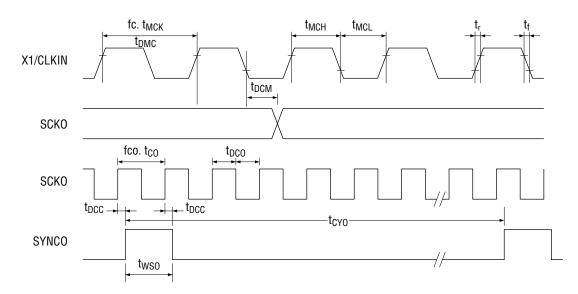

# **AC Characteristics**

| Parameter                                  | Symbol           | Condition               | Min.             | Тур.              | Max.                               | Unit |

|--------------------------------------------|------------------|-------------------------|------------------|-------------------|------------------------------------|------|

| Clock Frequency                            | f <sub>C</sub>   | _                       | 17.5             | 18.0              | 18.5                               | MHz  |

| Clock Cycle Time                           | t <sub>MCK</sub> | _                       | 54.1             | 55.56             | 57.1                               | ns   |

| Clock Duty Ratio                           | t <sub>DMC</sub> | _                       | 40               | 50                | 60                                 | %    |

| Clock "H" Level Pulse Width                | t <sub>MCH</sub> | _                       | 23.5             | _                 | _                                  | ns   |

| Clock "L" Level Pulse Width                | t <sub>MCL</sub> | _                       | 23.5             | _                 | _                                  | ns   |

| Clock Rise Time                            | tr               | _                       | _                | _                 | 5                                  | ns   |

| Clock Fall Time                            | t <sub>f</sub>   | _                       | _                | _                 | 5                                  | ns   |

| Sync Clock Output Time                     | t <sub>DCM</sub> | _                       | _                | _                 | 100                                | ns   |

| Internal Sync Clock Frequency              | f <sub>CO</sub>  | f <sub>c</sub> = 18 MHz | _                | 200               | _                                  | kHz  |

| Internal Sync Clock Output Cycle Time      | t <sub>CO</sub>  | f <sub>c</sub> = 18 MHz | _                | 5                 | _                                  | μs   |

| Internal Sync Clock Duty Ratio             | t <sub>DCO</sub> | f <sub>c</sub> = 18 MHz | _                | 50                | _                                  | %    |

| Internal Sync Signal Output Delay Time     | t <sub>DCC</sub> | f <sub>c</sub> = 18 MHz | _                | _                 | 5                                  | ns   |

| Internal Sync Signal Period                | t <sub>CYO</sub> | f <sub>c</sub> = 18 MHz | _                | 125               | _                                  | μs   |

| Internal Sync Signal Output Width          | t <sub>WS0</sub> | f <sub>c</sub> = 18 MHz | _                | t <sub>CO</sub>   | _                                  | μs   |

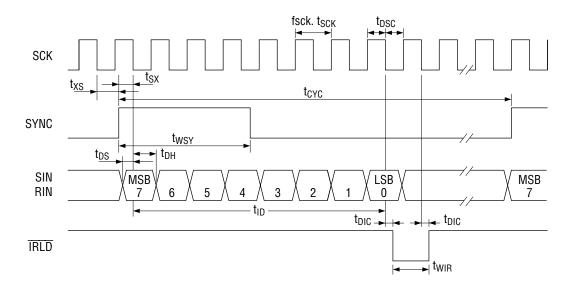

| Transmit/receive Operation Clock Frequency | f <sub>SCK</sub> | _                       | 64               | _                 | 2048                               | kHz  |

| Transmit/receive Sync Clock Cycle Time     | t <sub>SCK</sub> | _                       | 0.488            | _                 | 15.6                               | μs   |

| Transmit/receive Sync Clock Duty Ratio     | t <sub>DSC</sub> | _                       | 40               | 50                | 60                                 | %    |

| Transmit/receive Sync Signal Period        | t <sub>CYC</sub> | _                       | 123              | 125               | _                                  | μs   |

| Sync Timing                                | t <sub>XS</sub>  | _                       | 45               | _                 | _                                  | ns   |

|                                            | t <sub>SX</sub>  | _                       | 45               | _                 | _                                  | ns   |

| Sync Signal Width                          | t <sub>WSY</sub> | _                       | t <sub>SCK</sub> | _                 | t <sub>CYC</sub> -t <sub>SCK</sub> | μs   |

| Receive Signal Setup Time                  | t <sub>DS</sub>  | _                       | 45               | _                 | _                                  | ns   |

| Receive Data Hold Time                     | t <sub>DH</sub>  | _                       | 45               | _                 | _                                  | ns   |

| Receive Data Input Time                    | t <sub>ID</sub>  | _                       | _                | 7t <sub>SCK</sub> | _                                  | μs   |

| IRLD Signal Output Delay Time              | t <sub>DIC</sub> | _                       | _                | _                 | 138                                | ns   |

| IRLD Signal Output Width                   | t <sub>WIR</sub> | _                       | _                | tscк              | _                                  | μs   |

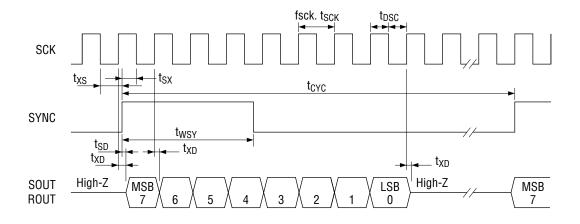

| Serial Output Delay Time                   | t <sub>SD</sub>  | _                       |                  | _                 | 90                                 | ns   |

|                                            | t <sub>XD</sub>  | _                       | _                | _                 | 90                                 |      |

# **AC Characteristics (Continued)**

|                                   | lueuj            |                                                              | (Ta = -40°C to +85°C) |                     |      |      |

|-----------------------------------|------------------|--------------------------------------------------------------|-----------------------|---------------------|------|------|

| Parameter                         | Symbol           | Condition                                                    | Min.                  | Тур.                | Max. | Unit |

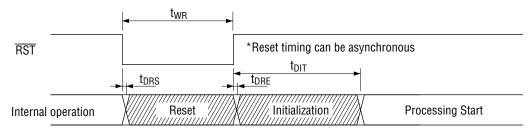

| Reset Signal Input Width          | t <sub>WR</sub>  | _                                                            | 1                     | _                   |      | μs   |

| Reset Start Time                  | t <sub>DRS</sub> | _                                                            | 5                     | _                   |      | ns   |

| Reset End Time                    | t <sub>DRE</sub> | _                                                            | —                     | _                   | 52   | ns   |

| Processing Operation Start Time   | t <sub>DIT</sub> | _                                                            | 100                   | _                   |      | μs   |

| Power Down Start Time             | t <sub>DPS</sub> | —                                                            | —                     | —                   | 111  | ns   |

| Power Down End Time               | t <sub>DPE</sub> | _                                                            | _                     | _                   | 15   | ns   |

| Control Pin Setup Time (INT)      | t <sub>DTS</sub> | _                                                            | 20                    | _                   |      | ns   |

| Control Pin Hold Time (INT)       | t <sub>DTH</sub> | _                                                            | 120                   | _                   |      | ns   |

| Control Pin Setup Time (RST)      | t <sub>DSR</sub> | _                                                            | 20                    | _                   |      | ns   |

| Control Pin Hold Time (RST)       | t <sub>DHR</sub> | —                                                            | 10                    | —                   |      | ns   |

| Parallel Data Output Signal Width | t <sub>WPD</sub> | —                                                            | —                     | 2t <sub>MCK</sub>   |      | ns   |

| Flag Signal Output Time           | t <sub>DF</sub>  | _                                                            | _                     | t <sub>MCK</sub>    |      | ns   |

| Flag Signal Output Width          | t <sub>WFO</sub> | _                                                            | —                     | t <sub>MCK</sub> /2 |      | ns   |

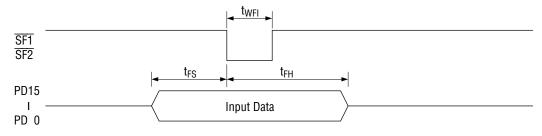

| Flag Signal Input Width           | t <sub>WFI</sub> | $\overline{\text{OFz}}$ connected to $\overline{\text{SFx}}$ | _                     | t <sub>WFO</sub>    |      | ns   |

| Data Read Setup Time              | t <sub>FS</sub>  | —                                                            | —                     | 20                  |      | ns   |

| Data Read Hold Time               | t <sub>FH</sub>  | —                                                            | _                     | 10                  |      | ns   |

# TIMING DIAGRAM Clock Timing

# **Serial Input Timing**

# **Serial Output Timing**

# **Operation Timing After Reset**

Note: INT is invalid in the diagonally shaded interval.

# **Power Down Timing**

\*Input MCK in the t<sub>DPS</sub> interval.

# **Control Pin Load-in Timing**

# **Parallel Output Timing**

**Parallel Input Timing**

# HOW TO USE THE MSM7620

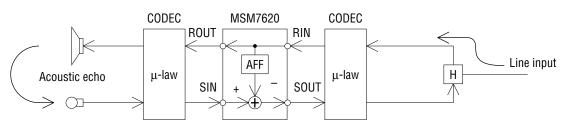

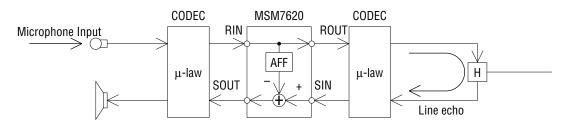

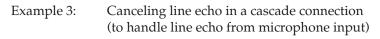

The MSM7620 cancels the echo which returns to SIN using the RIN signal. Connect the base signal to the R-side and the echo generated signal to the S-side.

# **Connection Methods According to Echos**

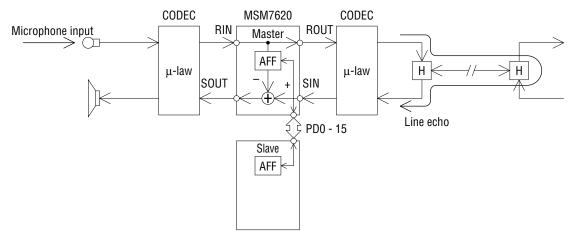

Example 1: Canceling acoustic echo (to handle acoustic echo from line input)

Example 2: Canceling line echo (to handle line echo from microphone input)

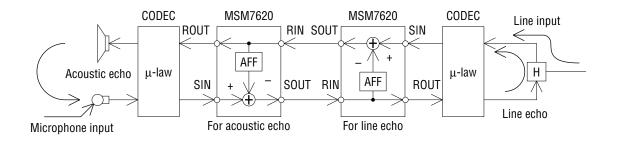

Example 4: Canceling of both acoustic echo and line echo

(to handle both acoustic echo from line input and line echo from microphone input)

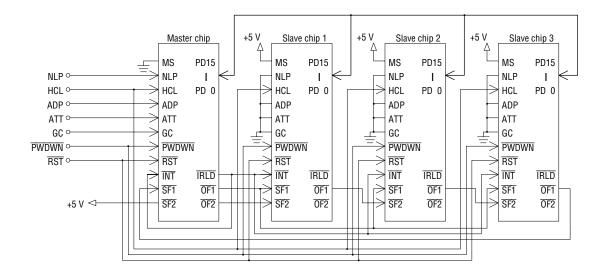

# **Control Pin Connection Example**

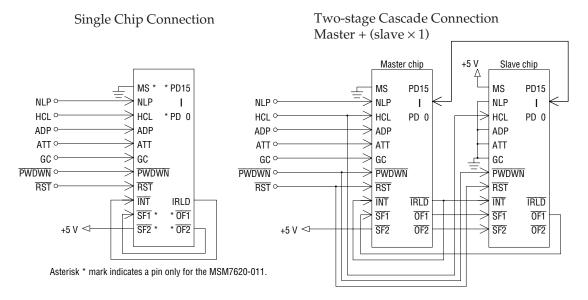

# Four-stage Cascade Connection Master + (slave $\times$ 3)

# Internal clock generator circuit

# External clock input circuit

# ECHO CANCELER CHARACTERISTICS DIAGRAM

# Measurement System Block Diagram

MSM7543GS-VK

AIN+

VFRO

PCMOUT

PCMIN

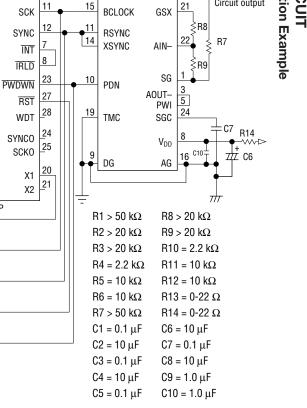

# **Bidirectional Connection Example APPLICATION CIRCUIT**

Circuit input C5 ●│├──RIN

OSOUT

Circuit output

MSM7543GS-VK

PCMOUT

PCMIN

BCLOCK

RSYNC

XSYNC

PDN

тмс

DG

Mike input

SIN()-

ROUT

Speaker output

R13 C3 ⊲-√√--

C2 1

CLKC

EXT. SCK

EXT. SYNC

RST()

PWDWNC

T

C1

23

21

22

3 AOUT-PWI

5 24

8

R2≶

R3≷

R1 {

AIN+

VFRO

GSX

AIN-

SG

SGC

$V_{DD}$

AG

R4≶

13

12

15

11

14

10

19

9

-**Č**-

≷R5

9

14

11

12

7

8

23

27

28

24 25

20 21

SIN

ROUT

SCK

SYNC

ĪNT

IRLD

RST

WDT

SYNCO

SCKO

X1

X2

PWDWN

For cancellation of acoustic echo R6

MSM7620-001GS-K

32-Pin SSOP

R12 For cancellation of line echo

MSM7620-001GS-K

32-Pin SSOP

13

10

2

3

4

6

29

32

т<u>щ</u>

÷

SOUT

RIN

NLP

HCL

ADP

ATT

GC

$V_{DD}$ C8 5 16

$V_{SS}$

$V_{SS}$

13

10

2

3

6

29

32

5

16

÷

Δ

С4<u>7</u>д

÷

SOUT

RIN

NLP

HCL

ADP

ATT

GC

$V_{DD}$

V<sub>SS</sub> V<sub>SS</sub>

R11≦

9

14

SIN

ROUT

≶R10

13

12

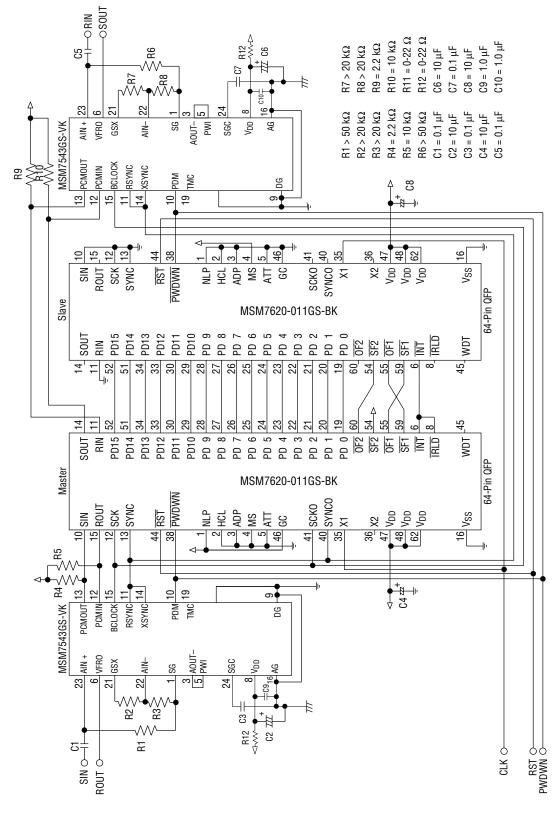

# **Cascade Connection Example**

24/28

# NOTES ON USE

- Set echo return loss (ERL) to be attenuated. If the echo return loss is set to be amplified, the echo can not be eliminated. Refer to the characteristics diagram for ERL vs. echo attenuation quantity.

- 2. Set the level of the analog input so that the PCM CODEC does not overflow.

- 3. The recommended input level is -10 to -20 dBm0. Refer to the characteristics diagram for the RIN input level vs. echo attenuation quantity.

- 4. Applying the tone signal to this echo canceler will decrease echo attenuation. If the tone signal is input to the SIN pin during the time that a signal is input to the RIN pin, this echo canceler operates faultily. A signal must be input to either the RIN pin or the SIN pin. The ADP or HCL pin must be driven at "H" if the tone signal is input to the SIN pin during the time that a signal is input to the RIN pin.

- For changes in the echo path (retransmit, circuit switching during transmission, and so on), convergence may be difficult. Perform a reset to make it converge. If the state of the echo path changes after a reset, convergence may again be difficult. In cases such as a change in the echo path, perform a reset when possible.

- When turning the power ON, set the PWDWN pin to "1" and input the basic clock simultaneouly with power ON. If powering down immediately after power ON, be sure first input 10 or more clocks of the basic clock.

- 7. After powering ON, be sure to reset.

- 8. After the power down pin is changed to a "1" from a "0", be sure to reset.

- 9. If this canceler is used to cancel acoustic echoes, an echo attenuation may be less than 30 dB.

# **EXPLANATION OF TERMS**

| Attenuating Function :     | This function prevents howling and controls the noise level with an attenuator for the RIN input and SOUT output. Refer to the                                                                                                                |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | explanation of pins (ATT pin).                                                                                                                                                                                                                |

| Echo Attenuation :         | If there is talking (input only to RIN) in the path of a rising echo<br>arises, the echo attenuation refers to the difference in the echo<br>return loss (canceled amount) when the echo canceler is not used                                 |

|                            | and when it is used.                                                                                                                                                                                                                          |

|                            | Echo attenuation = (SOUT level during through mode operation)<br>- (SOUT level during echo canceler operation) [dB]                                                                                                                           |

| Echo Delay Time :          | This is the time from when the signal is output from ROUT until it returns to SIN as an echo or other similar device.                                                                                                                         |

| Acoustic Echo :            | When using a hands free phone, and so on, the signal output from<br>the speaker echoes and is input again to the microphone. The                                                                                                              |

| Talashana Ita - Dahara     | return signal is referred to as acoustic echo.                                                                                                                                                                                                |

| Telephone Line Echo :      | This is a signal which is delayed midway in a telephone line and<br>returns as an echo, due to reasons such as a hybrid impedance<br>mismatch.                                                                                                |

| Gain Control Function :    | This function prevents howling and controls the sound level by with a gain controller for the RIN input. Refer to the explanation of pins (GC pin).                                                                                           |

| Center Clipping Function : | This function forces the SOUT output to a minimum value when the signal is below –57 dBm0. Refer to the explanation of pins (NLP pin).                                                                                                        |

| Double Talk Detection :    | Double talk refers to a state in which the SIN and RIN signals are<br>input simultaneously. In a double talk state, a signal outside the<br>echo signal which is to be canceled can be input to the SIN input,<br>resulting in misoperation.  |

|                            | The double talk detector prevents such misoperations of the canceler.                                                                                                                                                                         |

| Howling Detection :        | This is the oscillating state caused by the acoustic coupling between<br>the loud speaker and the microphone during hands free talking.<br>Howling not only interferes with talking, but can also cause<br>misoperation of the echo canceler. |

|                            | The howling detector prevents such misoperation and prevents                                                                                                                                                                                  |

|                            | howling.                                                                                                                                                                                                                                      |

| Echo Return Loss (ERL) :   | When the signal output from ROUT returns to SIN as an echo, ERL refers to how much loss there is in the signal level during ROUT. ERL = (ROUT level) – (SIN level of the ROUT signal which returns as an echo) [dB]                           |

|                            | If ERL is positive (ROUT > SIN), the system is an attenuator system. If ERL is negative (ROUT < SIN), the system is an amplifier system.                                                                                                      |

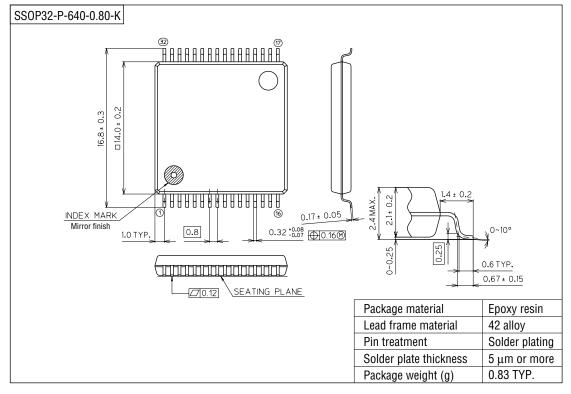

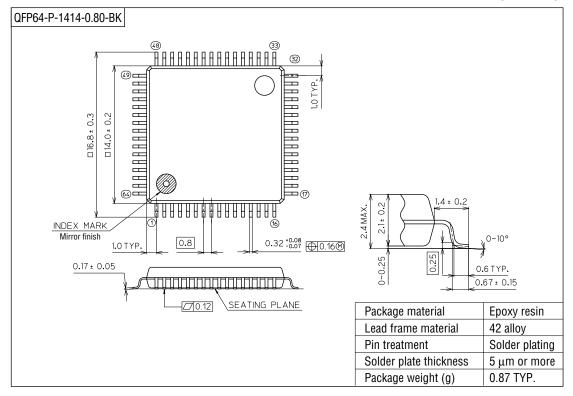

# PACKAGE DIMENSIONS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).