SBOS403-JUNE 2007

# High-Side Measurement, Bi-Directional Current/Power Monitor with I<sup>2</sup>C™ Interface

#### **FEATURES**

- SENSES BUS VOLTAGES FROM 0V TO +26V

- REPORTS CURRENT, VOLTAGE, AND POWER; STORES PEAKS

- TRIPLE WATCHDOG LIMITS:

- Lower Warning with Delay

- Upper Over-limit, No Delay

- Fast Analog Critical

- HIGH ACCURACY: 1% MAX OVER TEMP

# **APPLICATIONS**

- SERVERS

- TELECOM EQUIPMENT

- AUTOMOTIVE

- POWER MANAGEMENT

- BATTERY CHARGERS

- WELDING EQUIPMENT

- POWER SUPPLIES

- TEST EQUIPMENT

#### **DESCRIPTION**

The INA209 is a high-side current shunt and power monitor with an I<sup>2</sup>C interface. The INA209 monitors both shunt drop and shunt bus voltage. A programmable calibration value, combined with an internal multiplier, enables direct readouts in amperes. An additional multiplying register calculates power in watts. The INA209 features two separate, watchdog capabilities: onboard comparator and an over-limit comparator. The warning comparator is useful for monitoring lower warning limits and incorporates a user-defined delay. The over-limit comparator assists with monitoring upper limits that could require immediate system shutdown.

The INA209 also includes an analog-to-digital converter (ADC) comparator and a programmable digital-to-analog converter (DAC) that combine to provide the fastest possible responses to current overload conditions.

The INA209 can be used together with hot swap controllers that already use a current sense resistor. The INA209 full-scale range can be selected to be either within the hot-swap controller sense limits, or wide enough to include them.

The INA209 senses across shunts on buses that can vary from 0V to 26V. The device uses a single +3V to +5.5V supply, drawing a maximum of 1.5mA of supply current. It is specified for operation from  $-25^{\circ}$ C to  $+85^{\circ}$ C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

I2C is a trademark of NXP Semiconductors.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

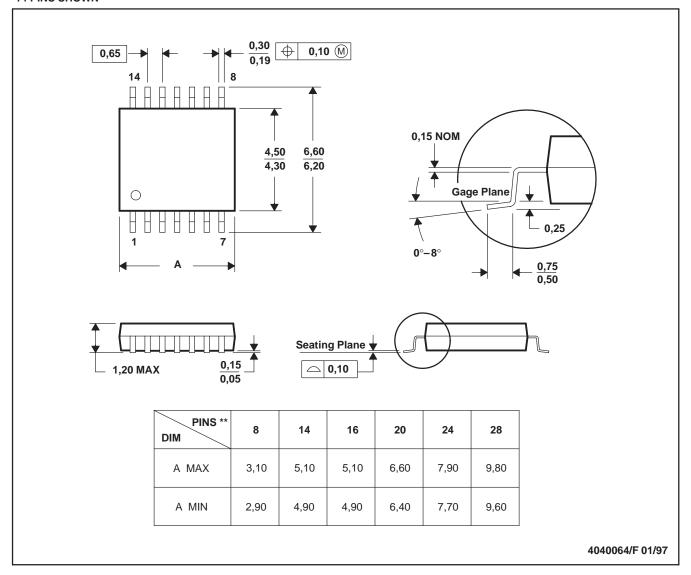

#### ORDERING INFORMATION(1)

| PRODUCT | PRODUCT PACKAGE-LEAD |    | PACKAGE MARKING |  |

|---------|----------------------|----|-----------------|--|

| INA209  | TSSOP-16             | PW | INA209A         |  |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

# ABSOLUTE MAXIMUM RATINGS(1)

Over operating free-air temperature range (unless otherwise noted).

|                                     |                                                                       | INA209                            | UNIT |

|-------------------------------------|-----------------------------------------------------------------------|-----------------------------------|------|

| Supply Voltage,                     | V <sub>S</sub>                                                        | 6                                 | V    |

| Analog Inputs,                      | Differential (V <sub>IN+</sub> ) – (V <sub>IN</sub> –) <sup>(2)</sup> | -26 to +26                        | V    |

| V <sub>IN+</sub> , V <sub>IN-</sub> | Common-Mode                                                           | -0.3 to +26                       | V    |

| Open-Drain Digi                     | tal Outputs                                                           | GND - 0.3 to +6                   | V    |

| GPIO, Convert I                     | Pins                                                                  | GND – 0.3 to V <sub>S</sub> + 0.3 | V    |

| Input Current Into Any Pin          |                                                                       | 5                                 | mA   |

| Open-Drain Digi                     | tal Output Current                                                    | 10                                | mA   |

| Operating Temp                      | erature                                                               | -40 to +125                       | °C   |

| Storage Temper                      | rature                                                                | -40 to +150                       | °C   |

| Junction Tempe                      | rature                                                                | +150                              | °C   |

|                                     | Human Body Model                                                      | 2000                              | V    |

| ESD Ratings                         | Charged-Device Model                                                  | 1000                              | V    |

|                                     | Machine Model (MM)                                                    | 150                               | V    |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

<sup>(2)</sup> V<sub>IN+</sub> and V<sub>IN-</sub> may have a differential voltage of –26V to +26V; however, the voltage at these pins must not exceed the range –0.3V to +26V.

# **ELECTRICAL CHARACTERISTICS:** V<sub>S</sub> = +3.3V

**Boldface** limits apply over the specified temperature range,  $T_A = -25^{\circ}C$  to +85°C. At  $T_A = +25^{\circ}C$ ,  $V_{IN+} = 12V$ ,  $V_{SENSE} = (V_{IN+} - V_{IN-}) = 32\text{mV}$ , PGA =  $\div$  1, and BRNG<sup>(1)</sup> = 1, unless otherwise noted.

|                                               |      |                                |     | INA209    |      |                |  |

|-----------------------------------------------|------|--------------------------------|-----|-----------|------|----------------|--|

| PARAMETER                                     |      | TEST CONDITIONS                | MIN | TYP       | MAX  | UNIT           |  |

| INPUT                                         |      |                                |     |           |      |                |  |

| Full-Scale Current Sense (Input) Voltage Rang | je   | PGA = ÷ 1                      | 0   |           | ±40  | mV             |  |

|                                               |      | PGA = ÷ 2                      | 0   |           | ±80  | mV             |  |

|                                               |      | $PGA = \div 4$                 | 0   |           | ±160 | mV             |  |

|                                               |      | PGA = ÷ 8                      | 0   |           | ±320 | mV             |  |

| Bus Voltage (Input Voltage) Range (2)         |      | BRNG = 1                       | 0   |           | 32   | V              |  |

|                                               |      | BRNG = 0                       | 0   |           | 16   | V              |  |

| Common-Mode Rejection                         | CMRR | $V_{IN+} = 0V \text{ to } 26V$ | 100 | 120       |      | dB             |  |

| Offset Voltage, RTI(3)                        | Vos  | PGA = ÷ 1                      |     | ±10       | ±100 | μV             |  |

|                                               |      | PGA = ÷ 2                      |     | ±20       | ±125 | μV             |  |

|                                               |      | $PGA = \div 4$                 |     | ±30       | ±150 | μV             |  |

|                                               |      | $PGA = \div 8$                 |     | ±40       | ±200 | μV             |  |

| vs Temperature                                |      |                                |     | 0.1       |      | μ <b>V/</b> °C |  |

| vs Power Supply                               | PSRR | $V_S = 3V \text{ to } 5.5V$    |     | 10        |      | μV/V           |  |

| Current Sense Gain Error                      |      |                                |     | ±40       |      | m%             |  |

| vs Temperature                                |      |                                |     | 10        |      | ppm/°C         |  |

| Input Impedance                               |      | Active Mode                    |     |           |      |                |  |

| V <sub>IN+</sub> Pin                          |      |                                |     | 20        |      | μΑ             |  |

| V <sub>IN</sub> _ Pin                         |      |                                |     | 20    320 |      | μA    kΩ       |  |

| Input Leakage                                 |      | Power-Down Mode                |     |           |      |                |  |

| V <sub>IN+</sub> Pin                          |      |                                |     | 0.1       | ±0.5 | μΑ             |  |

| V <sub>IN</sub> _ Pin                         |      |                                |     | 0.1       | ±0.5 | μΑ             |  |

| DC ACCURACY                                   |      |                                |     |           |      |                |  |

| ADC Basic Resolution                          |      |                                |     | 12        |      | Bits           |  |

| 1 LSB Step Size                               |      |                                |     |           |      |                |  |

| Shunt Voltage                                 |      |                                |     | 10        |      | μV             |  |

| Bus Voltage                                   |      |                                |     | 4         |      | mV             |  |

| Current Measurement Error                     |      |                                |     | ±0.2      | ±0.5 | %              |  |

| over Temperature                              |      |                                |     |           | ±1   | %              |  |

| Bus Voltage Measurement Error                 |      |                                |     | ±0.2      | ±0.5 | %              |  |

| over Temperature                              |      |                                |     |           | ±1   | %              |  |

| Differential Nonlinearity                     |      |                                |     | ±0.1      |      | LSB            |  |

| Critical DAC Full-Scale Range                 |      |                                |     | 255       |      | mV             |  |

| Critical DAC Accuracy                         |      |                                |     | ±0.5      | ±1   | %              |  |

| Critical DAC Resolution                       |      |                                |     | 8         |      | Bits           |  |

| Critical DAC 1 LSB Step Size                  |      |                                |     | 1         |      | mV             |  |

| Critical DAC Comparator Offset                |      |                                |     | ±0.3      | ±1.6 | mV             |  |

| Critical DAC Comparator Hysteresis (4)        |      |                                |     | See (4)   |      |                |  |

| Critical DAC Comparator Delay                 |      |                                |     | 5         |      | μs             |  |

<sup>(1)</sup> BRNG is bit 13 of the Configuration Register.

<sup>(2)</sup> This parameter only expresses the full-scale range of the ADC scaling. In no event should more than 26V be applied to this device.

(3) Referred-to-input (RTI).

<sup>(4)</sup> User-programmable. See the Critical Comparator and Register sections.

# ELECTRICAL CHARACTERISTICS: $V_S = +3.3V$ (continued)

**Boldface** limits apply over the specified temperature range,  $T_A = -25^{\circ}C$  to +85°C. At  $T_A = +25^{\circ}C$ ,  $V_{IN+} = 12V$ ,  $V_{SENSE} = (V_{IN+} - V_{IN-}) = 32mV$ ,  $PGA = \div 1$ , and BRNG = 1, unless otherwise noted.

|                                                                           |                            |                       | INA209         |                       |      |

|---------------------------------------------------------------------------|----------------------------|-----------------------|----------------|-----------------------|------|

| PARAMETER                                                                 | TEST CONDITIONS            | MIN                   | TYP            | MAX                   | UNIT |

| ADC TIMING                                                                |                            |                       |                |                       |      |

| ADC Conversion Time                                                       | 12-Bit                     |                       | 532            | 586                   | μs   |

|                                                                           | 11-Bit                     |                       | 276            | 304                   | μs   |

|                                                                           | 10-Bit                     |                       | 148            | 163                   | μs   |

|                                                                           | 9-Bit                      |                       | 84             | 93                    | μs   |

| Minimum Convert Input Low Time                                            |                            | 4                     |                |                       | μs   |

| SMBus                                                                     |                            |                       |                |                       |      |

| SMBus Timeout (5)                                                         |                            |                       | 28             | 35                    | ms   |

| DIGITAL INPUTS<br>(Convert, GPIO and SDA as Input, SCL, A0, A1)           |                            |                       |                |                       |      |

| Input Capacitance Leakage                                                 |                            |                       | 3              |                       | pF   |

| Input Current                                                             | $0 \leq V_{IN} \leq V_{S}$ |                       | 0.1            | 1                     | μΑ   |

| Input Logic Levels:                                                       |                            |                       |                |                       |      |

| V <sub>IH</sub>                                                           |                            | 0.7 (V <sub>S</sub> ) |                | 6                     | V    |

| $V_{IL}$                                                                  |                            | -0.3                  |                | 0.3 (V <sub>S</sub> ) | V    |

| Hysteresis                                                                |                            |                       | 500            |                       | mV   |

| DIGITAL OUTPUTS                                                           |                            |                       |                |                       |      |

| GPIO Pin Output Low                                                       | $I_{SINK} = 3mA$           |                       | 0.15           | 0.4                   | V    |

| GPIO Pin Output High                                                      | $I_{SOURCE} = 3mA$         | $V_{S} - 0.4$         | $V_{S} - 0.15$ |                       | V    |

| OPEN-DRAIN DIGITAL OUTPUTS<br>(Critical, Over-Limit, Warning, Alert, SDA) |                            |                       |                |                       |      |

| Logic '0' Output Level                                                    | $I_{SINK} = 3mA$           |                       | 0.15           | 0.4                   | V    |

| High-Level Output Leakage Current                                         | $V_{OUT} = V_{S}$          |                       | 0.1            | 1                     | μΑ   |

| POWER SUPPLY                                                              |                            |                       |                |                       |      |

| Operating Supply Range                                                    |                            | +3                    |                | +5.5                  | V    |

| Quiescent Current                                                         |                            |                       | 1              | 1.5                   | mA   |

| Quiescent Current, Power-Down Mode                                        |                            |                       | 6              | 15                    | μΑ   |

| Power-On Reset Threshold                                                  |                            |                       | 2              |                       | V    |

| TEMPERATURE RANGE                                                         |                            |                       |                |                       |      |

| Specified Temperature Range                                               |                            | -25                   |                | +85                   | °C   |

| Operating Temperature Range                                               |                            | -40                   |                | +125                  | °C   |

| Thermal Resistance $$\theta_{JA}$$                                        |                            |                       |                |                       |      |

| TSSOP-16                                                                  |                            |                       | +150           |                       | °C/W |

<sup>(5)</sup> SMBus timeout in the INA209 resets the interface any time SCL is low for over 28ms.

# **PIN CONFIGURATIONS**

#### INA209 Top View SMBus Alert $V_{\text{IN}-}$ 15 Α1 A0 Convert 3 14 13 SDA GND 4 $V_{S+}$ SCL 5 12 GPIO 6 11 GND 10 V<sub>S+</sub> Critical

# **PIN DESCRIPTIONS**

Overlimit 8

9 Warning

| PIN NO. | NAME              | DESCRIPTION                                                                                                                                                                                                                                                                                                                       |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>IN+</sub>  | Positive differential shunt voltage. Connect to positive side of shunt resistor.                                                                                                                                                                                                                                                  |

| 2       | V <sub>IN</sub> _ | Negative differential shunt voltage. Connect to negative side of shunt resistor. Bus voltage is measured from this pin to ground.                                                                                                                                                                                                 |

| 3       | Convert           | Used to trigger conversions in triggered mode. In triggered mode, this pin should normally be high and taken low to initiate conversion. It may be returned high after 4µs. If held low, the ADC converts each time a triggered mode command is written via the I <sup>2</sup> C bus. If not used, this line should be tied high. |

| 4       | GND               | Connect together with pin 11 to ground.                                                                                                                                                                                                                                                                                           |

| 5       | V <sub>S+</sub>   | Connect together with pin 10 to supply, 3V to 5.5V.                                                                                                                                                                                                                                                                               |

| 6       | GPIO              | General-purpose, user-programmable input/output. Totem-pole output. Connect to ground or supply if not used. Default condition is as an input.                                                                                                                                                                                    |

| 7       | Critical          | Open-drain critical watchdog output (filter set in Critical DAC- Register). Default condition is disabled; active-low; transparent (non-latched).                                                                                                                                                                                 |

| 8       | Overlimit         | Open-drain over-limit watchdog output. Default condition is disabled; active-low; transparent (non-latched).                                                                                                                                                                                                                      |

| 9       | Warning           | Open-drain warning watchdog output (delay set in Critical DAC- Register). Default condition is disabled; active-low; transparent (non-latched).                                                                                                                                                                                   |

| 10      | V <sub>S+</sub>   | Connect together with pin 5 to supply, 3V to 5.5V.                                                                                                                                                                                                                                                                                |

| 11      | GND               | Connect together with pin 4 to ground.                                                                                                                                                                                                                                                                                            |

| 12      | SCL               | Serial bus clock line.                                                                                                                                                                                                                                                                                                            |

| 13      | SDA               | Serial bus data line.                                                                                                                                                                                                                                                                                                             |

| 14      | A0                | Address pin. Table 1 shows pin settings and corresponding addresses.                                                                                                                                                                                                                                                              |

| 15      | A1                | Address pin. Table 1 shows pin settings and corresponding addresses.                                                                                                                                                                                                                                                              |

| 16      | SMBus Alert       | Open-drain SMBus alert output. Controlled in SMBus Alert Mask Register. Default is disabled.                                                                                                                                                                                                                                      |

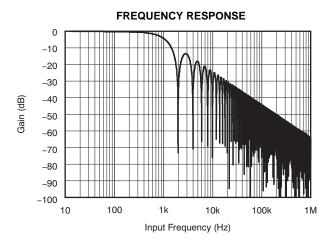

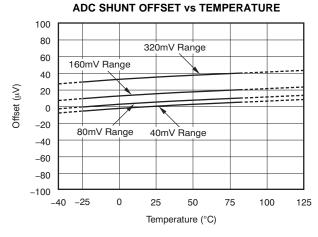

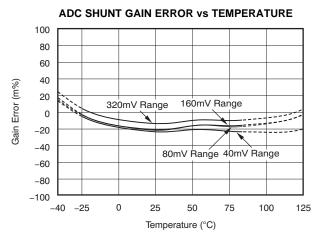

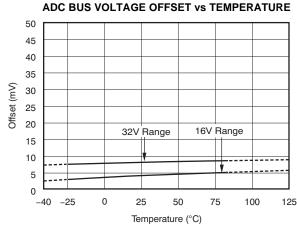

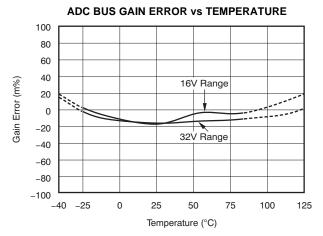

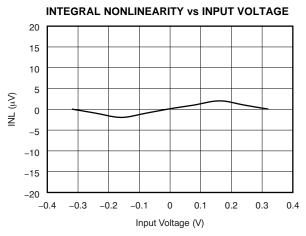

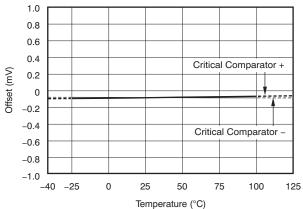

# **TYPICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$ ,  $V_{IN+} = 12V$ ,  $V_{SENSE} = (V_{IN+} - V_{IN-}) = 32mV$ , PGA =  $\div$  1, and BRNG = 1, unless otherwise noted.

Figure 1.

Figure 2.

Figure 3.

Figure 4.

Figure 5.

Figure 6.

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A$  = +25°C,  $V_{IN+}$  = 12V,  $V_{SENSE}$  = ( $V_{IN+}$  -  $V_{IN-}$ ) = 32mV, PGA =  $\div$  1, and BRNG = 1, unless otherwise noted.

# CRITICAL COMPARATOR OFFSET vs TEMPERATURE

Figure 7.

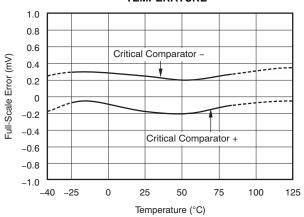

#### CRITICAL COMPARATOR FULL-SCALE ERROR vs TEMPERATURE

Figure 8.

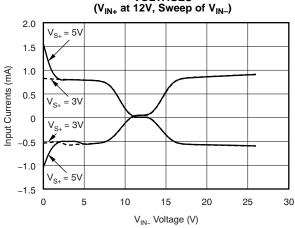

# INPUT CURRENTS WITH LARGE DIFFERENTIAL VOLTAGES (V<sub>IN+</sub> at 12V, Sweep of V<sub>IN-</sub>)

Figure 9.

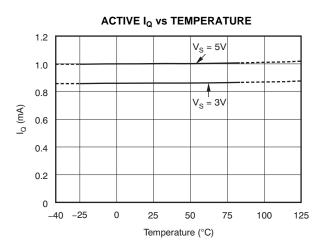

Figure 10.

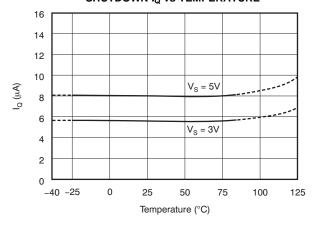

# SHUTDOWN IQ vs TEMPERATURE

Figure 11.

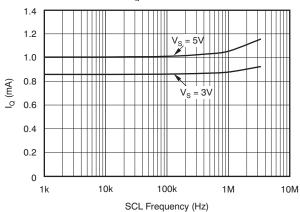

#### ACTIVE IQ vs I2C FREQUENCY

Figure 12.

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A$  = +25°C,  $V_{IN+}$  = 12V,  $V_{SENSE}$  = ( $V_{IN+}$  –  $V_{IN-}$ ) = 32mV, PGA =  $\div$  1, and BRNG = 1, unless otherwise noted.

### SHUTDOWN IQ vs I2C FREQUENCY 400 350 300 250 200 150 100 50 0 1k 10k 100k 1M 10M SCL Frequency (Hz)

Figure 13.

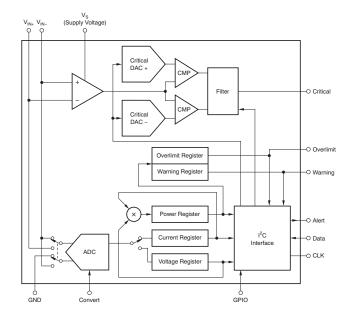

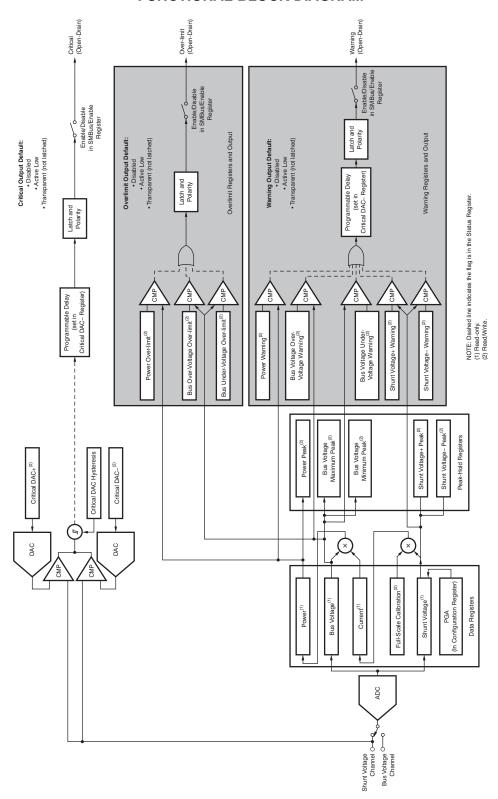

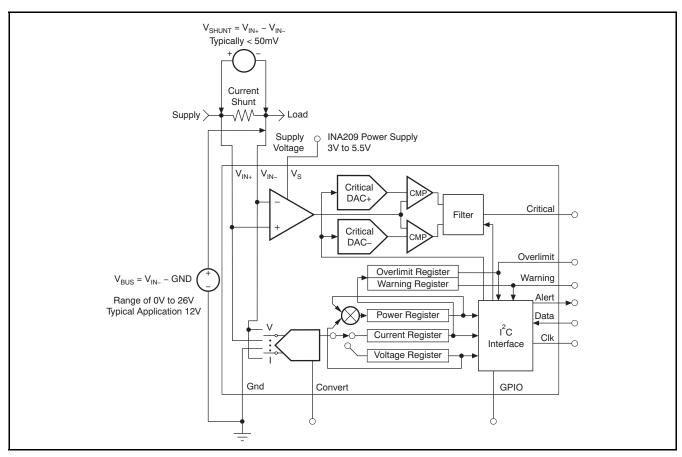

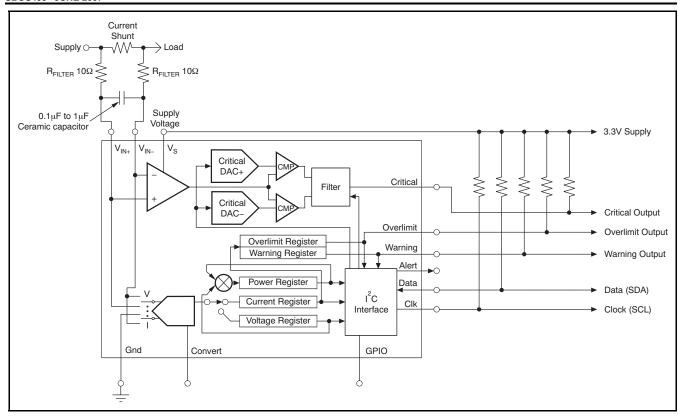

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 14.

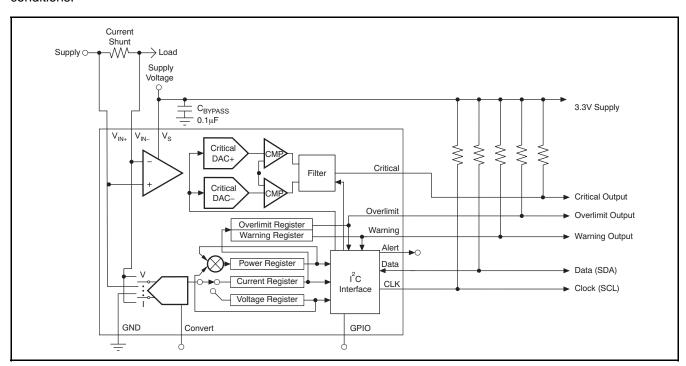

#### **APPLICATION INFORMATION**

The INA209 is a digital current-shunt monitor with an I<sup>2</sup>C and SMBus-compatible interface. It provides digital current, voltage, and power readings necessary for accurate decision-making precisely-controlled systems. Programmable registers allow flexible configuration for setting limits. measurement resolution. continuous-versus-triggered operation. Detailed register information appears at the end of this data sheet, beginning with Table 2. See the Functional Block Diagram for a block diagram of the INA209.

The INA209 offers compatability with I<sup>2</sup>C and SMBus interfaces. The I<sup>2</sup>C and SMBus protocols are essentially compatible with each other. I<sup>2</sup>C will be used throughout this document, with SMBus being specified only when a difference between the two systems is being addressed. Two bi-directional lines, SCL and SDA, connect the INA209 to the bus. Both SCL and SDA are open-drain connections. Figure 15 shows a typical application circuit.

#### **BUS OVERVIEW**

The device that initiates the transfer is called a *master*, and the devices controlled by the master are *slaves*. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates START and STOP conditions.

To address a specific device, the master initiates a START condition by pulling the data signal line (SDA) from a HIGH to a LOW logic level while SCL is HIGH. All slaves on the bus shift in the slave address byte on the rising edge of SCL, with the last bit indicating whether a read or write operation is intended. During the ninth clock pulse, the slave being addressed responds to the master by generating an Acknowledge and pulling SDA LOW.

Data transfer is then initiated and eight bits of data are sent, followed by an *Acknowledge* bit. During data transfer, SDA must remain stable while SCL is HIGH. Any change in SDA while SCL is HIGH is interpreted as a START or STOP condition.

Once all data have been transferred, the master generates a STOP condition, indicated by pulling SDA from LOW to HIGH while SCL is HIGH. The INA209 includes a 28ms timeout on its interface to prevent locking up an SMBus.

Figure 15. Typical Application Circuit

#### **Serial Bus Address**

To communicate with the INA209, the master must first address slave devices via a slave address byte. The slave address byte consists of seven address bits, and a direction bit indicating the intent of executing a read or write operation.

The INA209 has two address pins, A0 and A1. Table 1 describes the pin logic levels for each of the 16 possible addresses. The state of pins A0 and A1 is sampled on every bus communication and should be set before any activity on the interface occurs. The address pins are read at the start of each communication event.

Table 1. INA209 Address Pins and Slave Addresses

| A1              | A0              | ADDRESS |

|-----------------|-----------------|---------|

| GND             | GND             | 1000000 |

| GND             | V <sub>S+</sub> | 1000001 |

| GND             | SDA             | 1000010 |

| GND             | SCL             | 1000011 |

| V <sub>S+</sub> | GND             | 1000100 |

| V <sub>S+</sub> | V <sub>S+</sub> | 1000101 |

| V <sub>S+</sub> | SDA             | 1000110 |

| V <sub>S+</sub> | SCL             | 1000111 |

| SDA             | GND             | 1001000 |

| SDA             | V <sub>S+</sub> | 1001001 |

| SDA             | SDA             | 1001010 |

| SDA             | SCL             | 1001011 |

| SCL             | GND             | 1001100 |

| SCL             | V <sub>S+</sub> | 1001101 |

| SCL             | SDA             | 1001110 |

| SCL             | SCL             | 1001111 |

#### **Serial Interface**

The INA209 operates only as a slave device on the  $I^2C$  bus and SMBus. Connections to the bus are made via the open-drain I/O lines SDA and SCL. The SDA and SCL pins feature integrated spike suppression filters and Schmitt triggers to minimize the effects of input spikes and bus noise. The INA209 supports the transmission protocol for fast (1kHz to 400kHz) and high-speed (1kHz to 3.4MHz) modes. All data bytes are transmitted most significant byte first.

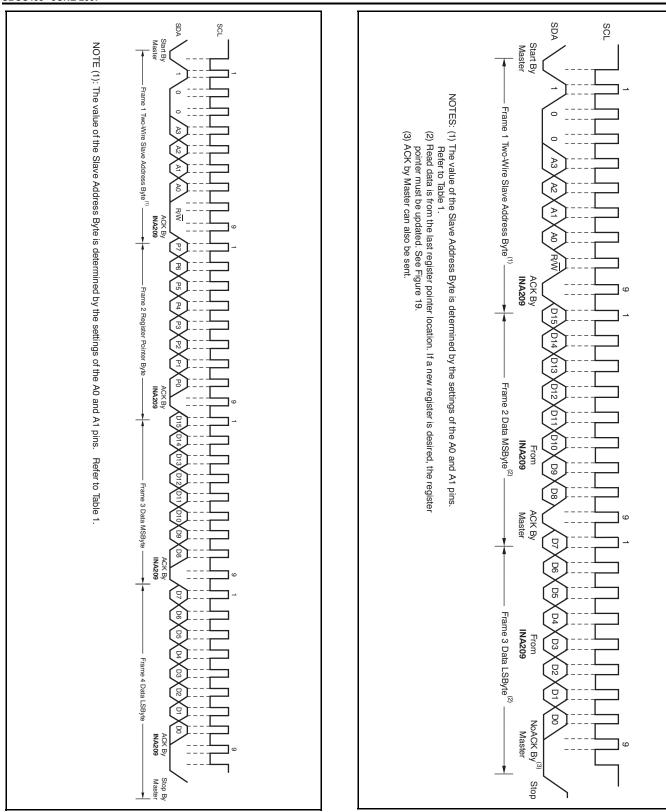

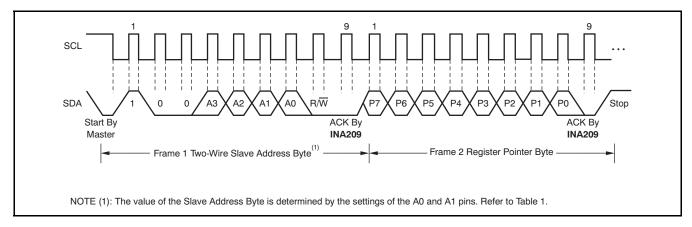

#### WRITING TO/READING FROM THE INA209

Accessing a particular register on the INA209 is accomplished by writing the appropriate value to the register pointer. Refer to Table 2 for a complete list of registers and corresponding addresses. The value for the register pointer as shown in Figure 19 is the first byte transferred after the slave address byte with the  $R/\overline{W}$  bit LOW. Every write operation to the INA209 requires a value for the register pointer.

Writing to a register begins with the first byte transmitted by the master. This byte is the slave address, with the  $R/\overline{W}$  bit LOW. The INA209 then acknowledges receipt of a valid address. The next byte transmitted by the master is the address of the register to which data will be written. This register address value updates the register pointer to the desired register. The next two bytes are written to the register addressed by the register pointer. The INA209 acknowledges receipt of each data byte. The master may terminate data transfer by generating a START or STOP condition.

When reading from the INA209, the last value stored in the register pointer by a write operation determines which register is read during a read operation. To change the register pointer for a read operation, a new value must be written to the register pointer. This write is accomplished by issuing a slave address byte with the R/W bit LOW, followed by the register pointer byte. No additional data are required. The master then generates a START condition and sends the slave address byte with the R/W bit HIGH to initiate the read command. The next byte is transmitted by the slave and is the most significant byte of the register indicated by the register pointer. This byte is followed by an Acknowledge from the master; then the slave transmits the least significant byte. The master acknowledges receipt of the data byte. The master may terminate data transfer by generating a Not-Acknowledge after receiving any data byte, or generating a START or STOP condition. If repeated reads from the same register are desired, it is not necessary to continually send the register pointer bytes; the INA209 retains the register pointer value until it is changed by the next write operation.

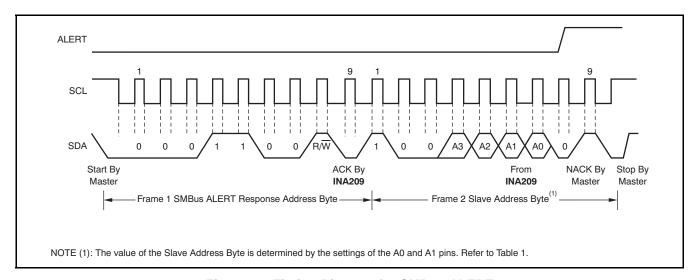

Figure 16 and Figure 17 show read and write operation timing diagrams. Note that register bytes are sent most-significant byte first, followed by the least significant byte. Figure 18 shows the timing diagram for the SMBus Alert operation. Figure 19 illustrates a typical register pointer configuration.

Figure 16. Timing Diagram for Write Word Format

Figure 17. Timing Diagram for Read Word Format

Figure 18. Timing Diagram for SMBus ALERT

Figure 19. Typical Register Pointer Set

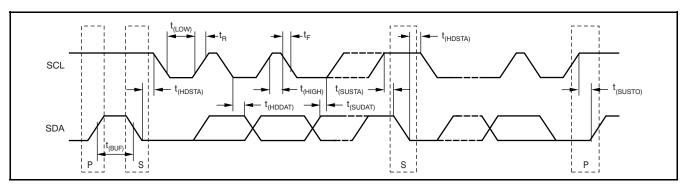

# High-Speed I<sup>2</sup>C Mode

When the bus is idle, both the SDA and SCL lines are pulled high by the pull-up devices. The master generates a start condition followed by a valid serial byte containing High-Speed (HS) master code 00001XXX. This transmission is made in fast (400kbps) or standard (100kbps) (F/S) mode at no more than 400kbps. The INA209 does not acknowledge the HS master code, but does recognize it and switches its internal filters to support 3.4Mbps operation.

The master then generates a repeated start condition (a repeated start condition has the same timing as the start condition). After this repeated start condition, the protocol is the same as F/S mode, except that transmission speeds up to 3.4Mbps are

allowed. Instead of using a stop condition, repeated start conditions should be used to secure the bus in HS-mode. A stop condition ends the HS-mode and switches all the internal filters of the INA209 to support either F/S mode transmission.

The master then generates a repeated start condition (a repeated start condition has the same timing as the start condition). After this repeated start condition, the protocol is the same as F/S mode, except that transmission speeds up to 3.4Mbps are allowed. Instead of using a stop condition, repeated start conditions should be used to secure the bus in HS-mode. A stop condition ends the HS-mode and switches all the internal filters of the INA209 to support the F/S mode.

Figure 20. Bus Timing Diagram

#### **Bus Timing Diagram Definitions**

|                                                                                               | FAST                 | MODE  | HIGH-SPE | ED MODE |       |     |

|-----------------------------------------------------------------------------------------------|----------------------|-------|----------|---------|-------|-----|

| PARAMETER                                                                                     | MIN                  | MAX   | MIN      | MAX     | UNITS |     |

| SCL Operating Frequency                                                                       | f <sub>(SCL)</sub>   | 0.001 | 0.4      | 0.001   | 3.4   | MHz |

| Bus Free Time Between STOP and START Condition                                                | t <sub>(BUF)</sub>   | 600   |          | 160     |       | ns  |

| Hold time after repeated START condition.<br>After this period, the first clock is generated. | t <sub>(HDSTA)</sub> | 100   |          | 100     |       | ns  |

| Repeated START Condition Setup Time                                                           | t <sub>(SUSTA)</sub> | 100   |          | 100     |       | ns  |

| STOP Condition Setup Time                                                                     | t <sub>(SUSTO)</sub> | 100   |          | 100     |       | ns  |

| Data Hold Time                                                                                | t <sub>(HDDAT)</sub> | 0     |          | 0       |       | ns  |

| Data Setup Time                                                                               | t <sub>(SUDAT)</sub> | 100   |          | 10      |       | ns  |

| SCL Clock LOW Period                                                                          | t <sub>(LOW)</sub>   | 1300  |          | 160     |       | ns  |

| SCL Clock HIGH Period                                                                         | t <sub>(HIGH)</sub>  | 600   |          | 60      |       | ns  |

| Clock/Data Fall Time                                                                          | t <sub>F</sub>       |       | 300      |         | 160   | ns  |

| Clock/Data Rise Time                                                                          | t <sub>R</sub>       |       | 300      |         | 160   | ns  |

| Clock/Data Rise Time for SCLK ≤ 100kHz                                                        | $t_R$                |       | 1000     |         |       | ns  |

# **Power-Up Conditions**

Power-up conditions apply to software reset via the RST bit (bit 15) in the Configuration Register, or the I<sup>2</sup>C bus General Call Reset. At device power up, all Status bits are masked. Warning, Over-Limit, Critical, and SMBus Alert functions are disabled. All watchdog outputs default to active low and transparent (non-latched) modes.

#### **BASIC ADC FUNCTIONS**

The two analog inputs to the INA209,  $V_{\rm IN+}$  and  $V_{\rm IN-}$ , connect to a shunt resistor in the bus of interest. The INA209 is typically powered by a separate supply from +3V to +5.5V. The bus being sensed can vary from 0V to 26V. There are no special considerations for power-supply sequencing (for example, a bus voltage can be present with the supply voltage off, and vice-versa). The INA209 senses the small drop across the shunt for shunt voltage, and senses the voltage with respect to ground from  $V_{\rm IN-}$  for the bus voltage. Figure 21 illustrates this operation.

Figure 21. INA209 Configured for Shunt and Bus Voltage Measurement

When the INA209 is in the normal operating mode (that is, MODE bits of the Configuration Register are set to '111'), it continuously converts the shunt voltage up to the number set in the shunt voltage averaging function (Configuration Register, SADC bits). The device then converts the bus voltage up to the number set in the bus voltage averaging (Configuration Register, BADC bits). The Mode control in the Configuration Register also permits selecting modes to convert only voltage or current, either continuously or in response to an event (triggered).

All current and power calculations are performed in the background and do not contribute to conversion time; conversion times shown in the Electrical Characteristics table can be used to determine the actual conversion time.

Power-Down mode reduces the quiescent current and turns off current into the INA209 inputs, avoiding any supply drain. Full recovery from Power-Down requires  $40\mu s$ . ADC Off mode (set by the Configuration Register, MODE bits) stops all conversions.

In triggered mode, the external Convert line becomes active. Convert commands are initiated by taking the Convert line low for a minimum of 4µs. The Convert line may be connected high when unused. Any re-trigger of the Convert line during a conversion is ignored, and the Convert line state is disregarded until the conversion ends. There are several available triggered modes; however, all conversions are performed repeatedly up to the number set in the Averaging function (Configuration Register, BADC and SADC bits).

If the Convert line is held low, writing any of the triggered convert modes into the Configuration Register (even if the desired mode is already programmed into the register) triggers a single-shot conversion.

Although the INA209 can be read at any time, and the data from the last conversion remain available, the Conversion Ready bit (Status Register, CNVR bit) is provided to help co-ordinate one-shot or triggered conversions. The Conversion Ready bit is set after all conversions, averaging, and multiplication operations are complete.

The Conversion Ready bit clears under these conditions:

- Writing to the Configuration Register, except when configuring the MODE bits for Power Down or ADC off (Disable) modes;

- 2. Reading the Status Register; or

- Triggering a single-shot conversion with the Convert pin.

#### **Power Measurement**

Current and bus voltage are converted at different points in time, depending on the resolution and averaging mode settings. For instance, when configured for 12-bit and 128 sample averaging, up to 68ms in time between sampling these two values is possible. Again, these calculations are performed in the background and do not add to the overall conversion time.

#### **Peak-Hold Registers**

Shunt voltage peak registers hold the lowest and highest converted reading for the shunt value. The shunt value may be either positive or negative; as a result, there is a need for a sign bit in either register. For instance, the Shunt Voltage Positive Peak Register in most systems records a positive voltage; most unidirectional current measurement applications, the Shunt Voltage Negative Peak Register also records a positive voltage. However, certain conditions can occur in normally unidirectional systems that cause a negative polarity across the shunt; these events are recorded in the Shunt Voltage Negative Peak Register.

Peak-hold registers do not record conditions that trigger a Critical Comparator shutdown. A Critical Comparator shutdown occurs within  $5\mu s$  of detecting a critical condition, while the ADC conversion necessary to record a peak-hold requires  $532\mu s$ . Therefore, a system shutdown removes the fault before the ADC can record it.

# **Critical Comparator**

The Critical Comparator function is included to provide the fastest possible response to overload events. This function bypasses the digital circuit by capturing the event in the analog domain.

The Critical Comparator responds only to shunt voltage, and can be programmed for a value from 0mV to 255mV (in 1mV increments) in the Critical DAC+ and Critical DAC- Registers. Two thresholds are provided, allowing users to set different thresholds in systems where bi-directional current measurement occurs. For example, a power supply may readily allow sourcing of 10A, but must alarm whenever sinking more than 1A. The SMBus Alert Mask/Enable Control Register allows the user to enable or disable the Critical pin output through the CREN bit. The CREN bit affects only the Critical pin; it does not affect the CRIT+ or CRIT- flags within the Status Register.

The DAC Comparator output filter is set by the CF bits of the Critical DAC- Register. This filter determines the duration of time that the CMP output must be continuously active (not toggling) to propagate to the Critical pin output and set the CRIT+ or CRIT- flags within the Status Register.

While the DAC Comparator output filter provides settings from 0ms to 0.96ms, the CMP is actually strobed every  $4\mu s$ , providing multiple samples per delay period. For the Critical output pin to become active, the critical condition must be true for every sample during the specified delay period.

When using the Critical Comparator in unidirectional applications, where the Critical DAC- Register is unused, the Comparator could trip in error if the input is near zero, because the comparator can have an offset of up to ±1.5mV. Noise also contributes to false tripping. To avoid false tripping in unidirectional applications, the Critical DAC- should be programmed to a value beyond -2mV to account for the offset, and an additional amount to provide a noise margin. Alternatively, the Critical DAC- can be programmed to negative full-scale range (-255mV), in order to eliminate false tripping.

#### **PGA Function**

If larger full-scale shunt voltages are desired, the INA209 provides a PGA function that increases the full-scale range up to 2, 4, or 8 times (320mV). Additionally, the bus voltage measurement has two full-scale ranges: 16V or 32V.

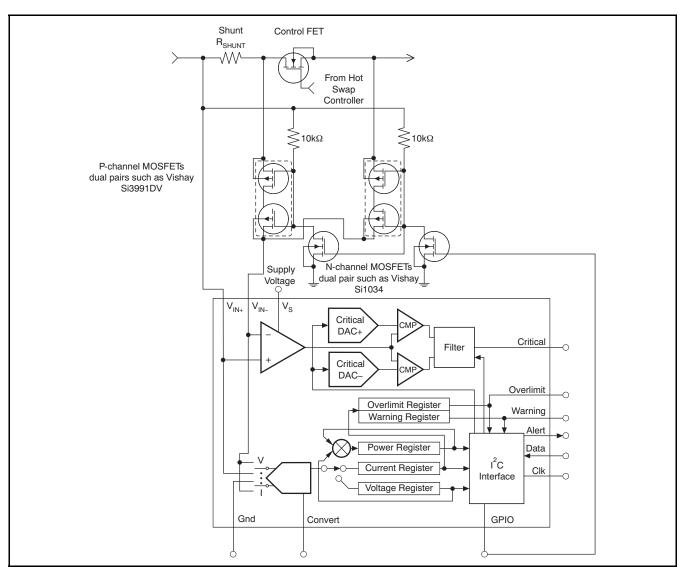

## **Compatibility with TI Hot Swap Controllers**

The INA209 is designed for compatibility with hot swap controllers such the TI TPS2490. The TPS2490 uses a high-side shunt with a limit at 50mV; the INA209 full-scale range of 40mV enables the use of the same shunt for current sensing below this limit. When sensing is required at (or through) the 50mV sense point of the TPS2490, the PGA of the INA209 can be set to ÷2 to provide an 80mV full-scale range.

A typical application connects the Critical pin output to the TPS2490 enable line; this configuration enables user-programmable current limits. Note that the latched mode should be used for the Critical pin output to avoid oscillation at the trip level.

# **Filtering and Input Considerations**

Measuring current is often noisy, and such noise can be difficult to define. The INA209 offers several options for filtering by choosing resolution and averaging in the Configuration Register. These filtering options can be set independently for either voltage or current measurement.

The internal ADC is based on a delta-sigma  $(\Delta\Sigma)$  front-end with a 500kHz (±30%) typical sampling rate. This architecture has good inherent noise rejection; however, transients that occur at or very close to the sampling rate harmonics can cause problems. Because these signals are at 1MHz and higher, they can be dealt with by incorporating filtering at the input of the INA209. The high frequency enables the use of low-value series resistors on the filter for negligible effects on measurement accuracy. Figure 22 shows the INA209 with an additional filter added at the input.

Figure 22. INA209 with Input Filtering

Overload conditions are another consideration for the INA209 inputs. The INA209 inputs are specified to tolerate 26V across the inputs. A large differential scenario might be a short to ground on the load side of the shunt. This type of event can result in full power-supply voltage across the shunt (as long the power supply or energy storage capacitors support it). It must be remembered that removing a short to ground can result in inductive kickbacks that could exceed the 26V differential and common-mode rating of the INA209. Inductive kickback voltages are best dealt with by zener-type transient-absorbing devices (commonly called *transzorbs*) combined with sufficient energy storage capacitance.

In applications that do not have large energy storage electrolytics on one or both sides of the shunt, an input overstress condition may result from an excessive dV/dt of the voltage applied to the input. A hard physical short is the most likely cause of this event, particularly in applications with no large electrolytics present. This problem occurs because an excessive dV/dt can activate the ESD protection in the INA209 in systems where large currents are available. Testing has demonstrated that the addition of  $10\Omega$  resistors in series with each input of the INA209 sufficiently protects the inputs against dV/dt failure up to the 26V rating of the INA209. These resistors have no significant effect on accuracy.

#### **SMBus Alert Response**

The ALERT interrupt pin is set whenever Warning, Over-Limit, Critical faults, or Conversion Ready states (in triggered modes) occur. The ALERT interrupt output signal is latched and can be cleared only by either reading the Status Register or by successfully responding to an alert response address. If the fault is still present, the ALERT pin re-asserts. Asserting the ALERT pin does not halt automatic conversions that are already in progress. The ALERT output pin is open-drain, allowing multiple devices to share a common interrupt line. The ALERT output can be disabled via the SMBus Alert Mask/Enable Control Register using the SMAEN bit. When disabled, the ALERT pin goes to a high state.

The INA209 responds to the SMBus alert response address, an interrupt pointer return-address feature. The SMBus alert response interrupt pointer provides quick fault identification for simple slave devices. When an ALERT occurs, the master can broadcast the alert response slave address (0001 100). Following this alert response, any slave devices that generated interrupts identify themselves by putting the respective addresses on the bus.

The alert response can activate several different slave devices simultaneously, similar to the I<sup>2</sup>C General Call. If more than one slave attempts to respond, bus arbitration rules apply; the device with the lower address code wins. The losing device does not generate an Acknowledge and continues to hold the ALERT line low until the interrupt is cleared. Successful completion of the read alert response protocol clears the SMBus ALERT pin, provided that the condition causing the alert no longer exists. The SMBus Alert flag is cleared separately by either reading the Status Register or by disabling the SMBus Alert function.

The Status Register flags indicate which (if any) of the watchdogs have been activated. After power-on reset (POR), the normal state of all flag bits is '0', assuming that no alarm conditions exist. The flags are cleared by any successful read of the Status Register, after a conversion is complete and the fault no longer exists.

#### **All Other Latches**

The latches in the Configuration Register for the Warning, Over-Limit, and Critical outputs are not associated with the SMBus alert response, and are cleared whenever the Status Register is read. If the fault remains, they continue to set (they may also be cleared by setting the latch enable to transparent, and then returning it to latch mode).

The values in the Peak-Hold Registers must be cleared by writing a '1' to the respective LSBs.

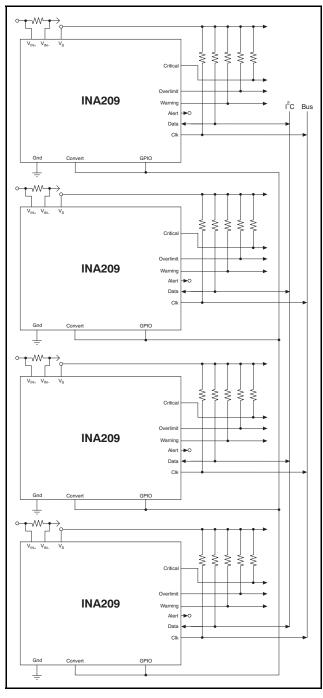

#### **Multichannel Data Acquisition**

The INA209 can be used in multiple current measurement channels where the controlling processor sums the currents of all the channels for a total current. Often these current measurements must occur simultaneously. Use the GPIO output from one of the INA209s and connect it to the Convert pin of the other INA209s. This architecture allows for sending conversion commands via the I<sup>2</sup>C bus to the master device, and all devices will convert simultaneously. Figure 23 illustrates this architecture using four INA209s.

Figure 23. Multichannel Data Acquisition with Simultaneous Sampling

# External Circuitry for Additional V<sub>BUS</sub> Input

The INA209 GPIO can be used to control an external circuit to switch the  $V_{\text{BUS}}$  measurement to an alternate location. Switching is most often done to perform bus voltage measurements on the opposite side of a MOSFET switch in series with the shunt resistor.

Consideration must be given to the typical  $11\mu A$  input current of each INA209 input, along with the  $320k\Omega$  impedance present at the  $V_{\text{IN}-}$  input where the bus voltage is measured. These effects can

create errors through the resistance of any external switching method used. The easiest way to avoid these errors is by reducing this resistance to a minimum; select switching MOSFETs with the lowest possible  $R_{\text{DS(on)}}$  values.

The circuit shown in Figure 24 uses MOSFET pairs to reduce package count. Back-to-back MOSFETs must be used in each leg because of the built-in back diodes from source-to-drain. In this circuit, the normal connection for  $V_{\text{IN}-}$  is at the shunt, with the optional voltage measurement at the output of the control FET.

Figure 24. External Circuitry for Additional V<sub>BUS</sub> Input

#### PROGRAMMING THE INA209 POWER MEASUREMENT ENGINE

#### **Calibration Register and Scaling**

The Calibration Register makes it possible to set the scaling of the Current and Power Registers to whatever values are most useful for a given application. One strategy may be to set the Calibration Register such that the largest possible number is generated in the Current Register or Power Register at the expected full-scale point; this approach yields the highest resolution. The Calibration Register can also be selected to provide values in the Current and Power Registers that either provide direct decimal equivalents of the values being measured, or yield a round LSB number. After these choices have been made, the Calibration Register also offers possibilities for end user system-level calibration, where the value is adjusted slightly to cancel total system error.

Follow these steps to select a proper value for the the Calibration Register.

- 1. Establish the following parameters (for a given application):

- Maximum bus voltage, V<sub>BUS</sub>

- Shunt resistance, R<sub>SHUNT</sub>

- Desired maximum drop across the shunt, V<sub>SHUNT</sub> (≥ 40mV recommended)

- 2. Determine maximum possible current using Equation 1:

$$MaxI = \frac{V_{SHUNT}}{R_{SHUNT}}$$

(1)

- 3. Choose the desired maximum current value: Max\_Expected\_I, ≤ MaxI

- 4. Calculate the possible range of current LSBs. The general form of this calculation is given by Equation 2:

$$Current\_LSB = \frac{max\_expected\_i}{CurrentRegisterh}$$

(2)

where CurrentRegister represents the value in the INA209 Current Register.

There are several ways to determine an appropriate Current Register value. One method is to fill the Current Register to the largest possible value at Max\_Expected\_I for highest accuracy and resolution, as shown in Equation 3.

$$Current\_LSB = \frac{Max\_Expected\_I}{7FFFh} = \frac{Max\_Expected\_I}{32767}$$

(3)

A second method uses a selected LSB based on a required 12-bit resolution, as illustrated by Equation 4:

$$Current\_LSB = \frac{Max\_Expected\_I}{1FFFh} = \frac{Max\_Expected\_I}{8191}$$

(4)

A third possible way to determine a proper Current Register value is to choose a decimal value for the register that corresponds to the known current. For example, Equation 5 uses **4000d** to representa 4A or 40A current:

$$Current\_LSB = \frac{Max\_Expected\_I}{FA0h} = \frac{Max\_Expected\_I}{4000d}$$

(5)

A final option is to simply use a current LSB of your own choice. The selected value must be less than that specified by Equation 2.

5. Compute the Calibration Register value using Equation 6:

$$Cal = trunc \left[ \frac{0.04096}{Current\_LSB \times R_{SHUNT}} \right]$$

(6)

6. Calculate the Power LSB, using Equation 7. Equation 7 shows a general formula; because the bus voltage measurement LSB is always 4mV, the general formula reduces to the calculated result.

$$Power\_LSB = Volt\_LSB \times Current\_LSB \times 5000 = Power\_LSB = 20 \times Current\_LSB$$

(7)

7. Compute the maximum current and shunt voltage values (before overflow), as shown by Equation 8 and Equation 9:

$$Max\_Current = Current\_LSB \times 7FFFh = Current\_LSB \times 32767$$

(8)

$$Max\_ShuntVoltage = Max\_Current \times R_{SHUNT}$$

(9)

## **Typical Design Example**

This section presents a typical design example for the INA209 using the process described in the previous section. For this example, we will use a nominal 12V system.

- 1. Establish the following parameters:

- Maximum bus voltage: V<sub>BUS</sub> = 16V

- Shunt resistance:  $R_{SHUNT} = 0.01\Omega$

- Desired maximum drop across the shunt,  $V_{SHUNT} = 40 \text{mV}$  (based on the option of programming the INA209 for a 40 mV full-scale range)

- 2. Determine maximum possible current using Equation 10:

$$MaxI = \frac{V_{SHUNT}}{R_{SHUNT}} = \frac{0.04}{0.01} = 4A$$

(10)

- 3. Choose the desired maximum current value: Max\_Expected\_I, ≤ MaxI. For this example, we will use 2A.

- 4. Calculate the possible range of current LSBs. The general form of this calculation is given by Equation 2. In this example, we will calculate a Current Register value using three of the four possible methods.

First, use Equation 11 to fill the Current Register to the largest possible value at Max\_Expected\_I for highest accuracy and resolution:

$$Current\_LSB = \frac{Max\_Expected\_I}{7FFFh} = \frac{Max\_Expected\_I}{32767} = \frac{2}{32767} = 61.037^{-6} A$$

(11)

The second method, using Equation 12, generates a selected LSB based on a required 12-bit resolution:

Current\_LSB =

$$\frac{\text{Max} - \text{Expected} - \text{I}}{1 \text{FFFh}} = \frac{\text{Max} - \text{Expected} - \text{I}}{8191} = \frac{2}{8191} = 244.17^{-6} \text{ A}$$

(12)

The third option uses a current LSB that must be less than that specified by Equation 2; in this instance, we choose to set the current LSB equal to:

This option provides a straighforward LSB that eases our remaining calculations. This value is also within the range of the other two results given by Equation 11 and Equation 12.

5. Now we compute the Calibration Register value according to Equation 13:

Cal = trunc

$$\left[ \frac{0.04096}{\text{Current\_LSB} \times \text{R}_{\text{SHUNT}}} \right] = \text{trunc} \left[ \frac{0.04096}{100^{-6} \times 0.01} \right] = 20480d = 5000h$$

(13)

6. Then we calculate the Power LSB, using Equation 14:

Power\_LSB = Volt\_LSB

$$\times$$

Current\_LSB  $\times$  5000 = Power\_LSB = 20  $\times$  Current\_LSB =  $2^{-3}$  A (14)

7. Finally, we compute the maximum current and shunt voltage values (before overflow), as shown by Equation 15 and Equation 16:

$$Max\_Current = Current\_LSB \times 7FFFh = Current\_LSB \times 32767 = 2^{-3} \times 32767 = 3.2767A$$

(15)

$$Max\_ShuntVoltage = Max\_Current \times R_{SHUNT} = 3.2767 \times 0.01 = 32.767^{-3}$$

(16)

# **REGISTER INFORMATION**

The INA209 uses a bank of registers for holding configuration settings, measurement results, maximum/minimum limits, and status information. Table 2 summarizes the INA209 registers; Figure 14 illustrates them.

Register contents are updated  $4\mu s$  after completion of the write command. Therefore, a  $4\mu s$  delay is required between completion of a write to a given register and a subsequent read of that register (without changing the pointer) when using SCL frequencies in excess of 1MHz.

Table 2. Summary of Register Set

| POINTER<br>ADDRESS        |                                             |                                                                                                                                                                                                                      | POWER-ON RES      | SET  |         |

|---------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|---------|

| HEX                       | REGISTER NAME                               | FUNCTION                                                                                                                                                                                                             | BINARY            | HEX  | TYPE(1) |

| 00 Configuration Register |                                             | All-register reset, settings for bus voltage range, PGA Gain, ADC resolution/averaging.                                                                                                                              | 00111001 10011111 | 399F | R/W     |

| 01                        | Status Register                             | Status flags for warnings,<br>over-/under-limits, conversion ready,<br>math overflow, and SMBus Alert.                                                                                                               | 00000000 00000000 | 0000 | R       |

| 02                        | SMBus Alert Mask/Enable<br>Control Register | Enables/disables flags in the Status<br>Register                                                                                                                                                                     | 00000000 00000000 | 0000 | R/W     |

| 03                        | Shunt Voltage                               | Shunt voltage measurement data.                                                                                                                                                                                      | 00000000 00000000 | 0000 | R       |

| 04                        | Bus Voltage                                 | Bus voltage measurement data.                                                                                                                                                                                        | 00000000 00000000 | 0000 | R       |

| 05                        | Power                                       | Power measurement data.                                                                                                                                                                                              | 00000000 00000000 | 0000 | R       |

| 06                        | Current/PGA <sup>(2)</sup>                  | Contains the value of the current flowing through the shunt resistor.                                                                                                                                                | 00000000 00000000 | 0000 | R       |

| 07                        | Shunt Voltage Positive<br>Peak              | Contains most positive voltage reading of Shunt Voltage Register.                                                                                                                                                    | 10000000 00000000 | 8000 | R/W     |

| 08                        | Shunt Voltage Negative<br>Peak              | Contains most negative voltage reading of Shunt Voltage Register.                                                                                                                                                    | 01111111 11111111 | 7FFF | R/W     |

| 09                        | Bus Voltage Maximum<br>Peak                 | Contains highest voltage reading of Bus Voltage Register.                                                                                                                                                            | 00000000 00000000 | 0000 | R/W     |

| 0A                        | Bus Voltage Minimum<br>Peak                 | Contains lowest voltage reading of Bus Voltage Register.                                                                                                                                                             | 11111111 11111000 | FFF8 | R/W     |

| 0B                        | Power Peak                                  | Contains highest power reading of Power Register.                                                                                                                                                                    | 00000000 00000000 | 0000 | R/W     |

| 0C                        | Shunt Voltage Positive<br>Warning           | Warning watchdog register. Sets positive shunt voltage limit that triggers a warning flag in the Status Register, and activates Warning pin.                                                                         | 00000000 00000000 | 0000 | R/W     |

| 0D                        | Shunt Voltage Negative<br>Warning           | Warning watchdog register. Sets<br>negative shunt voltage limit that triggers<br>a warning flag in the Status Register,<br>and activates Warning pin.                                                                | 00000000 00000000 | 0000 | R/W     |

| 0E                        | Power Warning                               | Warning watchdog register. Sets power limit that triggers a warning flag in the Status Register, and activates Warning pin.                                                                                          | 00000000 00000000 | 0000 | R/W     |

| 0F                        | Bus Over-Voltage<br>Warning                 | Warning watchdog register. Sets high<br>Bus voltage limit that triggers a warning<br>flag in the Status Register, and activates<br>Warning pin. Also contains bits to set<br>Warning pin polarity and latch feature. | 00000000 00000000 | 0000 | R/W     |

<sup>(1)</sup> Type:  $\mathbf{R} = \text{Read-Only}$ ,  $\mathbf{R}/\overline{\mathbf{W}} = \text{Read/Write}$ .

<sup>(2)</sup> Current Register defaults to '0' because the Calibration Register defaults to '0', yielding a zero current value until the Calibration Register is programmed.

# Table 2. Summary of Register Set (continued)

| POINTER ADDRESS HEX REGISTER NAME |                                                                |                                                                                                                                                                                                                         | POWER-ON RES      | SET  |         |

|-----------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|---------|

|                                   |                                                                | FUNCTION                                                                                                                                                                                                                | BINARY            | HEX  | TYPE(1) |

| 10                                | Bus Under-Voltage<br>Warning                                   | Warning watchdog register. Sets low<br>Bus voltage limit that triggers a warning<br>flag in the Status Register and activates<br>Warning pin.                                                                           | 00000000 00000000 | 0000 | R/W     |

| 11                                | Power Over-Limit                                               | Over-limit watchdog register. Sets power limit that triggers an over-limit flag in the Status Register, and activates the Overlimit pin.                                                                                | 00000000 00000000 | 0000 | R/W     |

| 12                                | Bus Over-Voltage<br>Over-Limit                                 | Over-limit watchdog register. Sets Bus over-voltage limit that triggers an over-limit flag in the Status Register, and activates the Overlimit pin. Also contains bits to set Overlimit pin polarity and latch feature. | 00000000 00000000 | 0000 | R/W     |

| 13                                | Bus Under-Voltage<br>Over-Limit                                | Over-limit watchdog register. Sets Bus under-voltage limit that triggers an over-limit flag in the Status Register, and activates the Overlimit pin.                                                                    | 00000000 00000000 | 0000 | R/W     |

| 14                                | Critical DAC+ Register<br>(Critical Shunt Positive<br>Voltage) | Sets a positive limit for internal Critical DAC+. Contains bits for GPIO pin status and mode of operation, Critical Comparator latch feature and hysteresis.                                                            | 00000000 00000000 | 0000 | R/W     |

| 15                                | Critical DAC- Register<br>(Critical Shunt Negative<br>Voltage) | Sets a negative limit for internal Critical DAC+. Contains bits for Warning pin delay, and Critical Comparator output filter configuration.                                                                             | 00000000 00000000 | 0000 | R/W     |

| 16                                | Calibration                                                    | Sets full-scale range and LSB of current and power measurements. Overall system calibration.                                                                                                                            | 00000000 00000000 | 0000 | R/W     |

#### **REGISTER DETAILS**

All INA209 registers are 16-bit registers. 16-bit register data are sent in two 8-bit bytes via the I<sup>2</sup>C interface.

## Configuration Register 00h (Read/Write)

| BIT#         | D15 | D14 | D13  | D12 | D11 | D10   | D9    | D8    | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|--------------|-----|-----|------|-----|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| BIT<br>NAME  | RST | _   | BRNG | PG1 | PG0 | BADC4 | BADC3 | BADC2 | BADC1 | SADC4 | SADC3 | SADC2 | SADC1 | MODE3 | MODE2 | MODE1 |

| POR<br>VALUE | 0   | 0   | 1    | 1   | 1   | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1     | 1     | 1     | 1     |

#### **Bit Descriptions**

RST: Reset Bit

Bit 15 Setting this bit to 1 generates a system reset that is the same as power-on reset. Resets all

registers to default values, this bit self-clears.

BRNG: Bus Voltage Range

Bit 13 0 = 16V FSR

1 = 32V FSR (default value)

PG: PGA (Shunt Voltage Only)

Bits 11, 12 Sets PGA gain and range. Note that the PGA defaults to ÷8 (320mV range). Table 3 shows

the gain and range for the various PG settings.

Table 3. PG Bit Settings<sup>(1)</sup>

| PG1 | PG0 | GAIN | RANGE  |

|-----|-----|------|--------|

| 0   | 0   | 1    | ±40mV  |

| 0   | 1   | ÷2   | ±80mV  |

| 1   | 0   | ÷4   | ±160mV |

| 1   | 1   | ÷8   | ±320mV |

<sup>(1)</sup> Shaded values are default.

## BADC: BADC Bus ADC Resolution/Averaging

Bits 7–10 These bits adjust the Bus ADC resolution (9-, 10-, 11-, or 12-bit) or set the number of

samples used when averaging results for the Bus Voltage Register (04h).

SADC: SADC Shunt ADC Resolution/Averaging

Bits 3–6 These bits adjust the Shunt ADC resolution (9-, 10-, 11-, or 12-bit) or set the number of

samples used when averaging results for the Shunt Voltage Register (03h).

BADC (Bus) and SADC (Shunt) ADC resolution/averaging and conversion time settings are shown in Table 4.

Table 4. ADC Settings<sup>(1)</sup>

|      | Table 4. ADO dettings |      |      |              |                 |  |  |  |  |  |  |

|------|-----------------------|------|------|--------------|-----------------|--|--|--|--|--|--|

| ADC4 | ADC3                  | ADC2 | ADC1 | MODE/SAMPLES | CONVERSION TIME |  |  |  |  |  |  |

| 0    | X <sup>(2)</sup>      | 0    | 0    | 9-bit        | 84μs            |  |  |  |  |  |  |

| 0    | X <sup>(2)</sup>      | 0    | 1    | 10-bit       | 148μs           |  |  |  |  |  |  |

| 0    | X <sup>(2)</sup>      | 1    | 0    | 11-bit       | 276μs           |  |  |  |  |  |  |

| 0    | X <sup>(2)</sup>      | 1    | 1    | 12-bit       | 532µs           |  |  |  |  |  |  |

| 1    | 0                     | 0    | 0    | 12-bit       | 532μs           |  |  |  |  |  |  |

| 1    | 0                     | 0    | 1    | 2            | 1.06ms          |  |  |  |  |  |  |

| 1    | 0                     | 1    | 0    | 4            | 2.13ms          |  |  |  |  |  |  |

| 1    | 0                     | 1    | 1    | 8            | 4.26ms          |  |  |  |  |  |  |

| 1    | 1                     | 0    | 0    | 16           | 8.51ms          |  |  |  |  |  |  |

| 1    | 1                     | 0    | 1    | 32           | 17.02ms         |  |  |  |  |  |  |

| 1    | 1                     | 1    | 0    | 64           | 34.05ms         |  |  |  |  |  |  |

| 1    | 1                     | 1    | 1    | 128          | 68.10ms         |  |  |  |  |  |  |

<sup>(1)</sup> Shaded values are default.

MODE: Operating Mode

Bits 0–2 Selects continuous, triggered, or power-down mode of operation. These bits default to continuous shunt and bus measurement mode. The mode settings are shown in Table 5.

Table 5. Mode Settings<sup>(1)</sup>

| MODE3 | MODE2 | MODE1 | MODE                      |

|-------|-------|-------|---------------------------|

| 0     | 0     | 0     | Power-Down                |

| 0     | 0     | 1     | Shunt Voltage, Triggered  |

| 0     | 1     | 0     | Bus Voltage, Triggered    |

| 0     | 1     | 1     | Shunt and Bus, Triggered  |

| 1     | 0     | 0     | ADC Off (disabled)        |

| 1     | 0     | 1     | Shunt Voltage, Continuous |

| 1     | 1     | 0     | Bus Voltage, Continuous   |

| 1     | 1     | 1     | Shunt and Bus, Continuous |

(1) Shaded values are default.

<sup>(2)</sup> X = Don't care.

#### Status Register 01h (Read)

| BIT#         | D15 | D14 | D13 | D12 | D11 | D10  | D9   | D8  | D7    | D6    | D5   | D4   | D3  | D2 | D1 | D0 |

|--------------|-----|-----|-----|-----|-----|------|------|-----|-------|-------|------|------|-----|----|----|----|

| BIT<br>NAME  | WOV | WUV | WP  | WS+ | WS- | OLOV | OLUV | OLP | CRIT+ | CRIT- | CNVR | SMBA | OVF |    | -  | _  |

| POR<br>VALUE | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 0   | 0     | 0     | 0    | 0    | 0   | 0  | 0  | 0  |

The Status Register flags activate whenever any limit is violated, and latch when corresponding latch bits are set. These flags are cleared when the Status Register is read (unless a limit is exceeded when the flag immediately sets again).

After power-up and initial setup, the Status Register should be read once to clear any flags set as as a result of power-up values prior to setup.

## **Bit Descriptions**

WOV: Warning Bus Over-Voltage

Bit 15 This bit is set to '1' when the result in the Bus Voltage Register (04h) exceeds the level set

in the Bus Over-Voltage Warning Register (0Fh).

WUV: Warning Bus Under-Voltage

Bit 14 This bit is set to '1' when the result in the Bus Voltage Register (04h) is less than the value

set in the Bus Under-Voltage Warning Register (10h).

WP: Warning Power

Bit 13 This bit is set to '1' when the value of the Power Register (05h) exceeds the level set in the

Power Warning Register (0Eh).

WS+: Warning Shunt+ Voltage

Bit 12 This bit is set to '1' when the value of the Shunt Voltage Register (03h) exceeds the level

set in the Shunt Voltage Positive Warning Register (0Ch).

WS-: Warning Shunt- Voltage

Bit 11 This bit is set to '1' when the value of the Shunt Voltage Register (03h) exceeds the level

set in the Shunt Voltage Negative Warning Register (0Dh).

OLOV: Over-Limit Bus Over-Voltage

Bit 10 This bit is set to '1' when the result in the Bus Voltage Register (04h) exceeds the level set

in the Bus Over-Voltage Over-Limit Register (12h).

OLUV: Over-Limit Bus Under-Voltage

Bit 9 This bit is set to '1' when the result in the Bus Voltage Register (04h) is less than the level

set in the Bus Under-Voltage Over-Limit Register (13h).

OLP: Over-Limit Power

Bit 8 This bit is set to '1' when the value of the Power Register (05h) exceeds the level set in the

Power Over-Limit Register (11h).

#### **Bit Descriptions (continued)**

CRIT+: Critical Shunt Positive Voltage

Bit 7 This bit is set to '1' when the value of the shunt voltage exceeds the positive limit set in the

Critical DAC+ Register (14h).

CRIT-: Critical Shunt Negative Voltage

Bit 6 This bit is set to '1' when the value of the shunt voltage exceeds the negative limit set in the

Critical DAC- Register (15h).

CNVR: Conversion Ready

Bit 5 Although the INA209 can be read at any time, and the data from the last conversion are

available, the Conversion Ready line is provided to help coordinate one-shot or triggered conversions. The Conversion bit is set after all conversions, averaging, and multiplications

are complete. Conversion Ready clears under the following conditions:

1. Writing the Configuration Register (except for Power-Down or Disable mode

selections).

2. Reading the Status Register.

3. Trigger a single-shot conversion with the Convert pin.

SMBA: SMBus Alert

Bit 4 Clears only on reading Status Register or by disabling SMBus Alert function.

OVF: Math Overflow

Bit 3 This bit is set to '1' if an arithmetic operation resulted in an overflow error. It indicates that

current and power data may be meaningless. It does not set any watchdog outputs.

#### SMBus Alert Mask/Enable Control Register 02h (Read/Write)

| BIT#         | D15  | D14  | D13 | D12  | D11  | D10   | D9    | D8   | D7     | D6     | D5    | D4 | D3    | D2   | D1   | D0    |  |

|--------------|------|------|-----|------|------|-------|-------|------|--------|--------|-------|----|-------|------|------|-------|--|