# SILICON MMIC QUADRATURE MODULATOR

**UPC8105GR**

### **FEATURES**

- WIDE SUPPLY VOLTAGE RANGE: 2.7 ~ 5.5 V

- BROADBAND OPERATION:

MODOUT = 100 400 MHz, I/Q = DC to 10 MHz

- INTERNAL 90° PHASE SHIFTER

- POWER SAVE FUNCTION

- LOW POWER CONSUMPTION: 16 mA Typ. @ 3 V

- SMALL SSOP 16 PACKAGE

- TAPE AND REEL PACKAGING AVAILABLE

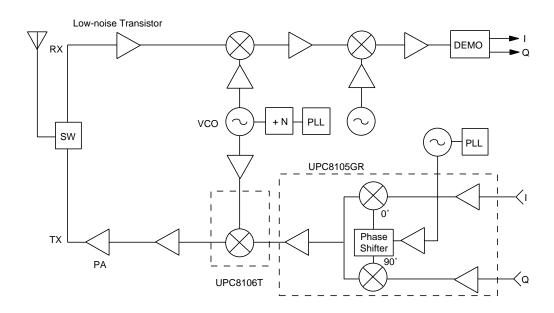

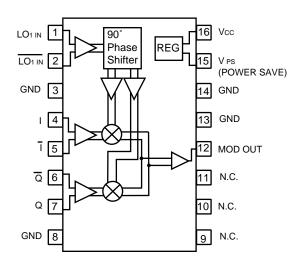

**FUNCTIONAL BLOCK DIAGRAM**

### **DESCRIPTION**

The UPC8105GR Silicon MMIC I/Q Modulator is manufactured using the NESAT III MMIC process. The NESAT III process produces transistors with ft approaching 20 GHz. The device was designed for use in Digital Mobile Communications circuits such as 900 MHz Digital Cordless and Cellular Phones, WLAN and PCN/PCS Handset Transmitters.

NEC's stringent quality assurance and test procedures ensure the highest reliability and performance.

### ELECTRICAL CHARACTERISTICS (TA = 25°C, Vcc = 3.0 V, Vps ≥ 1.8 V)

|            | PART NUMB<br>PACKAGE OUT                                  | UPC8105GR<br>S16 (SSOP 16) |     |           |         |     |

|------------|-----------------------------------------------------------|----------------------------|-----|-----------|---------|-----|

| SYMBOLS    | PARAMETERS AND C                                          | UNITS                      | MIN | TYP       | MAX     |     |

| Icc        | Total Circuit Current (no signal) VPS ≥ VPS ≤             | mA<br>μA                   | 10  | 16<br>0.1 | 21<br>5 |     |

| Рмор       | Output Power - Modulator                                  |                            | dBm | -21       | -16.5   | -12 |

| LOLEAK     | Local Oscillator Leakage                                  |                            | dBc |           | -40     | -30 |

| ImR        | Image Rejection                                           | dBc                        |     | -40       | -30     |     |

| IM3ı/Q     | I/Q 3rd Order Intermodulation Distortion + 500 mVp-p (AC) |                            | dBc |           | -50     |     |

| RLIN       | I/Q LO Input Return Loss                                  | dB                         |     | 20        |         |     |

| ZI/Q       | Input Impedance I and Q Port                              |                            | kΩ  |           | 20      |     |

| Tps(RISE)  | Power Save Rise Time VPS ≤ 1.0 V to VF                    | μS                         |     | 2         | 5       |     |

| Tps (FALL) | Power Save Fall Time Vps ≥1.8 V to Vps                    | μS                         |     | 2         | 5       |     |

# ABSOLUTE MAXIMUM RATINGS<sup>1</sup> (TA = 25°C)

| SYMBOLS | PARAMETERS                       | UNITS | RATINGS     |

|---------|----------------------------------|-------|-------------|

| Vcc     | Supply Voltage                   | V     | 6.0         |

| VPS     | Enable Voltage for<br>Power Save | V     | 6.0         |

| PD      | Power Dissipation <sup>2</sup>   | mW    | 530         |

| Тор     | Operating Temperature            | °C    | -40 to +85  |

| Tstg    | Storage Temperature              | °C    | -65 to +150 |

#### Notes:

- Operation in excess of any one of these parameters may result in permanent damage.

- Mounted on a 50x50x1.6 mm double copper clad epoxy glass PWB (TA = 85°C).

# RECOMMENDED OPERATING CONDITIONS

| SYMBOLS | PARAMETERS                       | UNITS | MIN | TYP | MAX |

|---------|----------------------------------|-------|-----|-----|-----|

| Vcc     | Supply Voltage                   | V     | 2.7 | 3.0 | 5.5 |

| Тор     | Operating Temperature            | °C    | -40 | +25 | +85 |

| fmodout | Modulator Output Frequence       | y MHz | 100 |     | 400 |

| floin   | LO1 Input Frequency <sup>1</sup> | MHz   | 100 |     | 400 |

| fi/QIN  | I/Q Input Frequency <sup>2</sup> | MHz   | DC  |     | 10  |

#### Notes:

- 1. PLOIN = -10 dBm.

- 2. PI/QIN = 600 mVp-p max.

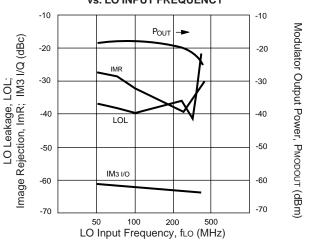

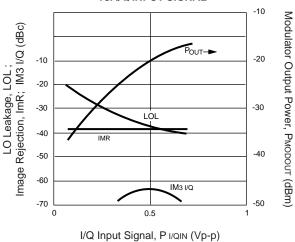

# TYPICAL PERFORMANCE CURVES (TA = 25°C, Vcc = Vps = 3 V, I/Q DC Offset = I/Q DC Offset = 1.5 V,

I/Q Input Signal = 500 mVp-p (Single-ended), PLOIN = -10 dBm unless otherwise specified)

# MODULATOR OUTPUT POWER, LO LEAKAGE, IMAGE REJECTION AND I/Q 3rd ORDER INTERMODULATION DISTORTION vs.LO INPUT POWER

# MODULATOR OUTPUT POWER, LO LEAKAGE, IMAGE REJECTION AND I/Q 3rd ORDER INTERMODULATION DISTORTION vs. LO INPUT FREQUENCY

MODULATOR

OUTPUT POWER, LO LEAKAGE , IMAGE REJECTION

AND I/Q 3rd ORDER INTERMODULATION DISTORTION

vs. I/Q INPUT SIGNAL

# **PIN FUNCTIONS**

| Pin No. | Symbol           | Supply Voltage | Pin Voltage | Description                                                                                                                                                                                                                           | Equivalent Circuit                                |

|---------|------------------|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1       | LOIN             | _              | 0           | LO input for the phase shifter. This input impedance is internally matched to 50 $\Omega$ .                                                                                                                                           | 1 ξ50 Ω                                           |

| 2       | LOIN<br>(Bypass) | _              |             | Bypass of the LO input. This pin is grounded through an internal capacitor. For a single-ended design this pin should be left open.                                                                                                   |                                                   |

| 3<br>8  | GND              |                |             | Connect to ground with minimum inductance. Track length should be kept as short as possible.                                                                                                                                          |                                                   |

| 4       | ı                | Vcc/2*2        | _           | Input for I signal. This input impedance is larger than 20 kΩ. The relationship between the amplitude and the DC bias of the input signal are as follows:    Vcc/2 (V)   Amp. (mVp-p)     ≥1.35   400     ≥1.5   600     ≥1.75   1000 | 4                                                 |

| 5       | Ī                | Vcc/2*2        | _           | Input for I signal. This input impedance is larger than 20 kΩ. Vcc/2 biased DC signal should be input.                                                                                                                                | - <del>111                                 </del> |

| 6       | Q                | Vcc/2*2        | _           | Input for Q signal. This input impedance is larger than 20 k $\Omega$ . Vcc/2 biased DC signal should be input.                                                                                                                       |                                                   |

| 7       | Q                | Vcc/z*2        | _           | Input for Q signal. This input impedance is larger than 20 k $\Omega$ . The relationship between the amplitude and the DC bias of the input signal are as follows:                                                                    | 7 — — — — — — — — — — — — — — — — — — —           |

| 12      | MODout           | _              |             | Output from the modulator. This is emitter follower output. Connect approx. 15 $\Omega$ in series to match to 50 $\Omega$ .                                                                                                           | 12                                                |

<sup>\*1:</sup> In case I/Q input signals are single ended. I/Q signal inputs can be used either single-ended or differentially with proper terminations.

\*2: Vcc/2 DC bias must be supplied to I, I, Q, Q.

# **PIN FUNCTIONS**

| Pin No.  | Symbol              | Supply Voltage | Pin Voltage | Description                                                                                                                       | Equivalent Circuit |

|----------|---------------------|----------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 13<br>14 | GND                 | 0              | _           | Connect to the ground with minimum inductance. Track length should be kept as short as possible.                                  |                    |

| 15       | VPS<br>(Power Save) | VPS            |             | Power save control pin can control the On/Sleep state with bias as follows:    VPS (V)   STATE     1.8~5.5   ON     0~1.0   SLEEP | 15                 |

| 16       | Vcc                 | 2.7~5.5        | _           | Supply voltage pin for the modulator. An internal regulator helps keep the device stable against temperature or VCC variation.    |                    |

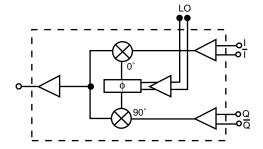

# **MODULATOR INTERNAL FUNCTIONS**

| Block                   | Function/Operation                                                                                                                                                                                                                                                                                      | Block Diagram |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 90°<br>Phase<br>Shifter | Input signal from LO is sent to a T-type flip-flop through a frequency doubler. The output signal from the T-type F/F is changed to the same frequency as LO input with a quadrature phase shift of 0°, 90°, 180°, or 270°. These circuits provide self phase correction for proper quadrature signals. | from LOin     |

| Buffer<br>Amplifier     | Buffer amplifiers for each phase signal are sent to each mixer.                                                                                                                                                                                                                                         |               |

| Mixer                   | Each signal from the buffer amps is quadrature modulated with two double-balanced mixers. High accurate phase and amplitude inputs are realized to provide excellent image rejection.                                                                                                                   |               |

| Adder                   | Output signal from each mixer is added and sent through a final amplifier stage to pin 16 for further off-chip filtering if necessary.                                                                                                                                                                  | To MODout     |

### INTERNAL BLOCK DIAGRAM

### ORDERING INFORMATION

| PART NUMBER  | QUANTITY  |

|--------------|-----------|

| UPC8105GR-E1 | 2500/Reel |

Note: Embossed Tape, 12 mm wide.

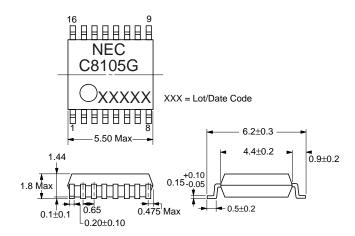

## **OUTLINE DIMENSIONS** (Units in mm)

### **PACKAGE OUTLINE SSOP 16**

#### **LEAD CONNECTIONS**

8. GND

| 1. | LOIN           | 9. N.C.              |

|----|----------------|----------------------|

| 2. | LOIN           | 10. N.C.             |

| 3. | GND            | 11. N.C.             |

| 4. | Input          | 12. MODout           |

| 5. | <u>TI</u> nput | 13. GND              |

| 6. | Q Input        | 14. GND              |

| 7. | Q Input        | 15. Vps (Power Save) |

All dimensions are typical unless specified otherwise.

16. Vcc

### **APPLICATION CIRCUIT**