## **Ultra Low Power 8-bit FLASH Microcontroller**

#### Description

The EM6812 is designed to be battery operated for extended lifetime applications. Brownout and powercheck functions ensure reliable operation at or near undervoltage conditions. offering greater reliability in complex operation modes. Each of the 16 I/Os is freely programmable and the microcontroller has a dual guartz and trimmable RC oscillator up to 10MHz. It has an 8-bit RISC architecture specially designed for very low power consumption. With 2 clocks per instruction, EM6812 executes up to 2.5 MIPS at 5MHz and achieves an astonishing 2200 MIPS/Watt.

#### **Features**

- Green mold / leadfree package

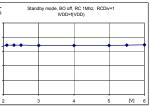

- 120 µA active mode @ 3V, 1MHz 6 µA standby mode, RC on 0.8 µA standby mode, RC off

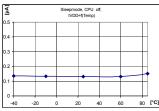

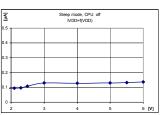

- 0.16 µA sleep mode

- Up to 2.5 MIPS at 5MHz

True low current:

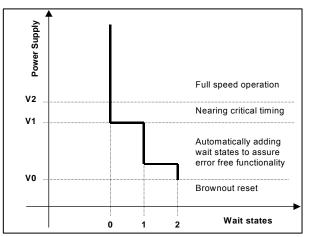

- On-chip brownout detection

- Powercheck functions at start-up

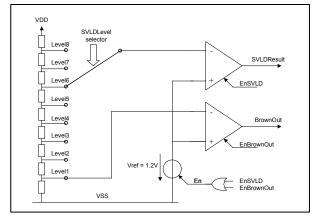

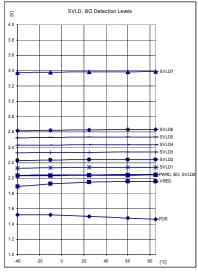

- 8-level Supply Voltage Level Detection (SVLD)

- Fast wake-up from standby mode

- 16 fully configurable I/Os

- Input / Output

- Pull-up, Pull-down

- CMOS, N-channel open drain

- 6 high currents outputs, up to 20 mA

- Wide supply voltage range 2 V 5.5 V

- Flash read monitor (allows save instruction execution at lowest voltages)

- Dual mode quartz and RC oscillators:

- 1 MHz 10 MHz RC

- . 32768 Hz crystal or external clock source

- 8-bit CoolRISC architecture

- 16 registers

- . 2 clock per instruction

- 8x8bit hardware multiplier .

- Power-On-Reset and watchdog

- Various Flash memory size:

- 2k x 22 bit (5.6k Byte)

- 4k x 22 bit (11.2k Byte)

- 8k x 22 bit (22.5k Byte)

- Fully static 512B or 256B RAM, Low power 12B RAM,

- Dual port 4B RAM

- Internal and external interrupts

- Frequency generator

- PWM functions

- 8/16-bit timers

- Prescaler:

- 10-bit RC divider

- 15-bit crystal divider

- SPI interface, UART programmable by software

- Small 24-pin TSSOP and SO packages (leadfree)

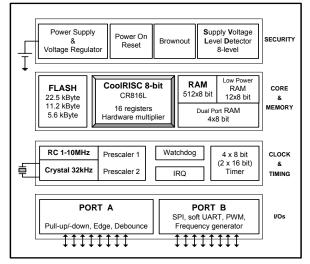

#### **Block Diagram**

#### **Tools & Services**

- □ Easy to use emulator with full debug functions, full peripheral integration, C-compiler

- Windows-based software programs

- □ Programmer from different vendors

- Dedicated team of engineers for outstanding support

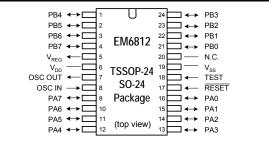

#### **Pinout Configuration**

### **Typical Applications**

- Metering

- Heat Cost Allocation

- Smoke detector

- Security

- Body care

- Sports

- Computer peripherals, Bluetooth chipset

### 1 EM6812 at a glance

#### Power supply

- Low power architecture

- Voltage regulator for internal logic supply

- External regulator capacitor

#### CPU

- 8 bit CoolRisc 816L Core

- 16 internal registers

- 4 hardware subroutine stacks

- 8 bit hardware multiplier

- refer also to the CR816L reference manual

#### **ROM / Flash**

- ROM 4096 Instructions = 11.26 Kbytes

- Flash 8192 Instructions = 22.5 Kbytes

#### RAM

- 512 x 8 bit static SRAM (for 8k Instructions)

- 256 x 8 bit static SRAM (for < 4k Instructions)</li>

- low voltage ram data retention

#### Low power RAM, 12 Byte

for lowest power calculations

#### Dual Port RAM, 4 Byte

Data IO on port B, Control on port A

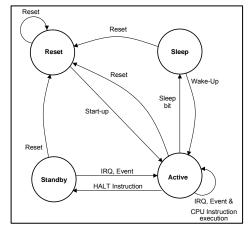

#### **Operating modes**

- Active mode: CPU and peripherals are running

- Standby mode: CPU halted, peripherals on

- Sleep mode: no clocks, reset state

- Wake Up from port A inputs

#### Resets

- Power On Reset

- Reset from watchdog timer

- External Reset Input

- Brown Out

- Reset with Port A reset combination

- Reset Flags to identify the reset source

#### **Oscillator XTAL 32kHZ**

- Oscillation clock pre-divider (1 sec)

- External clock low frequency input

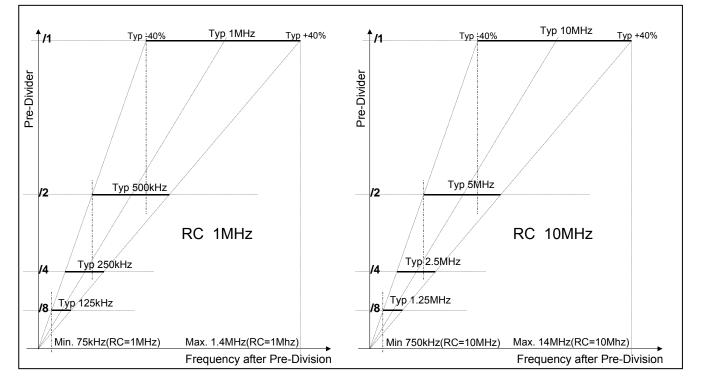

#### **Oscillator RC**

- internal RC oscillator

- External clock high frequency input

- Freq. Trimming register

- 1MHz or 10MHz Clocks

- stable over temperature and voltage

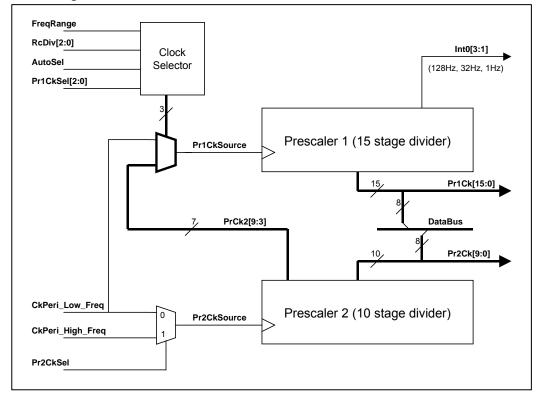

#### Prescaler's

- 2 Prescaler for RC and Xtal Oscillators

- input clock software selectable

- fix interval IRQ's (RTC and others)

- clock source to other peripherals

- Divider capture, 8 MSB's

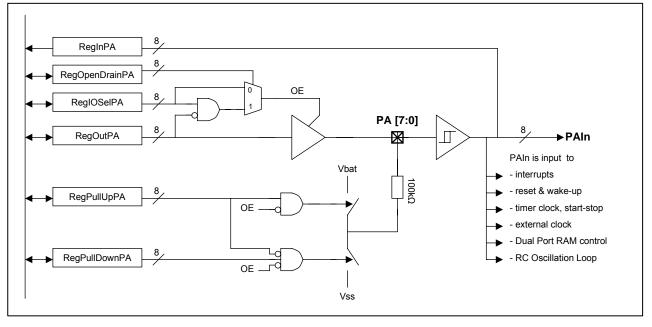

#### Parallel In/Output Port A

- 8 bit wide direct input read

- all functions bit-wise configurable

- Input , output

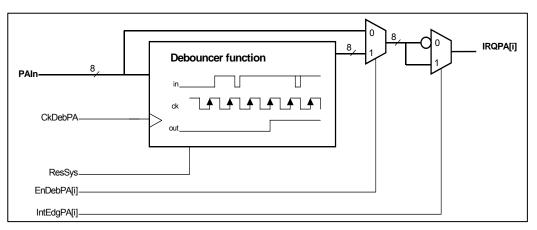

- debouncer

- IRQ on pos. or neg. edge

- Pull-up, pull-down or no pull selectable

- Freq. Input for timer

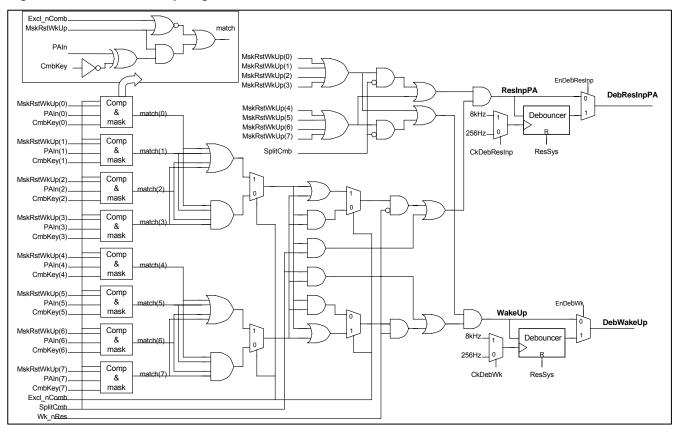

- Input combination reset

- CMOS or NCH. Open Drain outputs

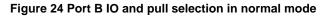

### Parallel In/Output Port B

- 8 multipurpose I/O's

- 8 bit wide direct input read

- all functions bit-wise configurable

- 4 high current outputs

- Input, output

- Pull-up, pull-down or no pull selectable

- CMOS or NCH. Open Drain outputs

- special function: Serial Interface I/O's, DP RAM

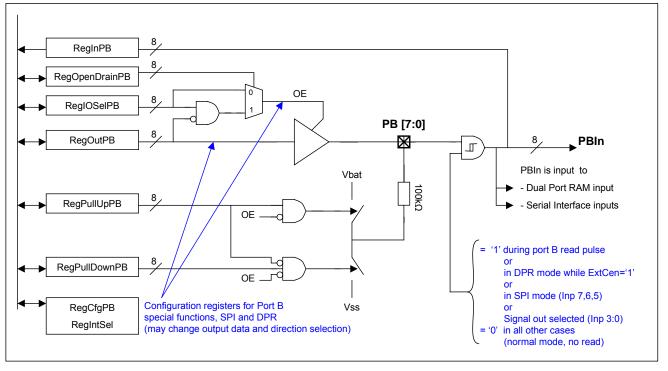

#### Serial Interface SPI

3 wire serial Interface, Sclk, Din, Dout

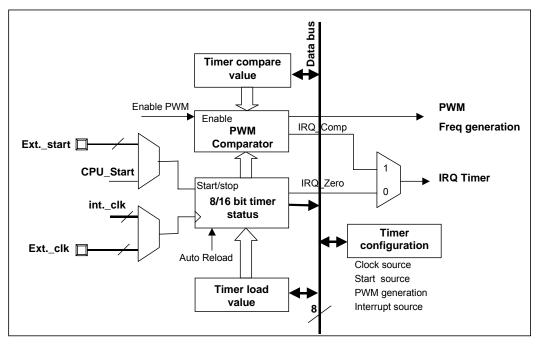

#### Timer (4 x 8 bit, or 2 x 16 bit)

- 8 (16) bit wide, Zero-Stop and Auto-Reload mode

- External signal pulse width measurement

- PWM generation

- Event Counter

- IRQ requests

#### Watchdog timer

generation of watchdog reset after time out

#### Interrupt

- external IRQ's from Port A, Comparator

- internal IRQ's from Timer, Prescaler

#### SVLD

8 levels supply voltage level check

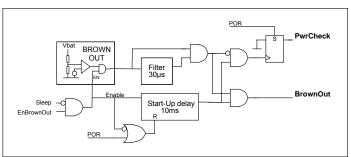

#### **Brown Out**

- On-chip Brown-Out detection, reset state

- Power check at Startup

# EM6812

### Table of contents

| 1  | EM6812 at a glance                                                                      | 2               |

|----|-----------------------------------------------------------------------------------------|-----------------|

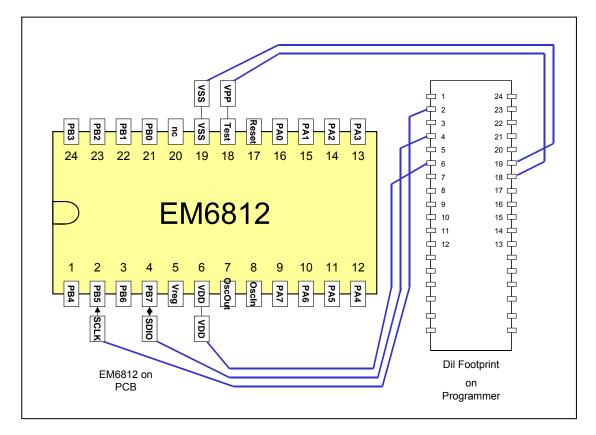

| 2  | Circuit Connectivity                                                                    | 5               |

|    | 2.1 Terminal usage                                                                      | 6               |

|    | 2.2 Programming connections                                                             | 7               |

| 3  | Operating modes                                                                         | 8               |

|    | 3.1 Active mode                                                                         | 8               |

|    | <ul><li>3.2 Standby Mode</li><li>3.3 Sleep Mode</li></ul>                               | 8<br>8          |

|    | 3.4 System registers                                                                    | 9               |

| 4  |                                                                                         | 10              |

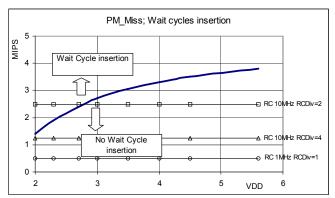

| -  | 4.1 Memory miss                                                                         | 10              |

| 5  | -                                                                                       | 12              |

| •  | 5.1 SRAM                                                                                | 12              |

|    | 5.2 General Purpose Registers, 16 Bytes                                                 | 13              |

|    | 5.3 Dual Port RAM                                                                       | 13              |

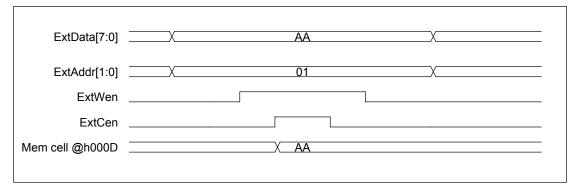

|    | 5.3.1 CPU R/W access to DPR                                                             | 13<br>14        |

|    | <ul><li>5.3.2 External Write Access to DPR</li><li>5.3.3 Read Access from DPR</li></ul> | 14              |

|    | 5.3.4 Conflict handling                                                                 | 15              |

|    | 5.3.5 Register overview                                                                 | 15              |

| 6  | CPU                                                                                     | 16              |

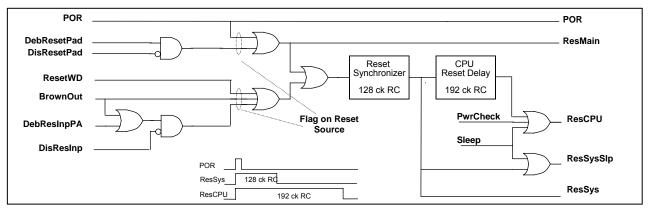

| 7  | Reset Controller                                                                        | 17              |

|    | 7.1 Basic features                                                                      | 17              |

|    | 7.1.1 Reset functions registers                                                         | 18              |

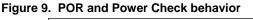

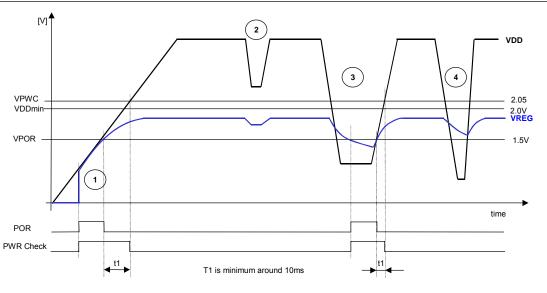

|    | <ul><li>7.2 POR and PowerCheck</li><li>7.3 Reset Pad</li></ul>                          | 19<br>20        |

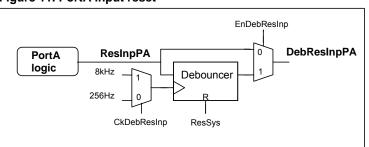

|    | 7.4 PortA Input Reset                                                                   | 20              |

|    | 7.5 BrownOut reset                                                                      | 21              |

|    | 7.5.1 BO Timings                                                                        | 21              |

|    | 7.6 Watchdog                                                                            | 22<br>22        |

|    | 7.6.1 Watchdog counter<br>7.6.2 Lock/Unlock                                             | 22              |

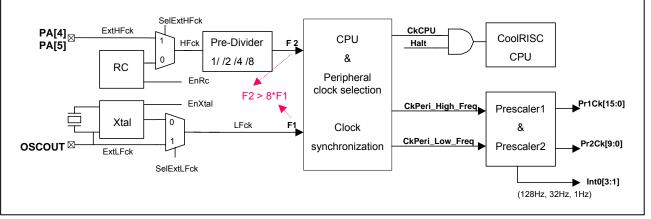

| 8  |                                                                                         | 23              |

| U  | 8.1 Basic features                                                                      | 23              |

|    | 8.1.1 Overview                                                                          | 23              |

|    | 8.2 High frequency clock source                                                         | 24              |

|    | 8.2.1 RC oscillator                                                                     | 24              |

|    | 8.2.2High frequency external clock8.3Low frequency clock source:                        | 25<br>26        |

|    | 8.3.1 Crystal oscillator                                                                | 26              |

|    | 8.3.2 Low frequency external clock                                                      | 27              |

|    | 8.3.3 Data input on OscOut                                                              | 27              |

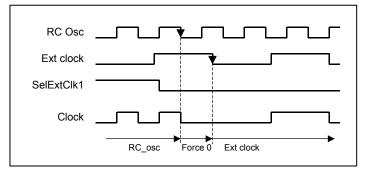

|    | <ul><li>8.4 Clock synchronization</li><li>8.5 CPU clock selection</li></ul>             | 27<br>28        |

|    | 8.6 Peripheral clocks generation                                                        | 28              |

|    | 8.6.1 Prescaler2 (10 stages)                                                            | 29              |

|    | 8.6.2 Prescaler1 (15 stages)                                                            | 30              |

|    | 8.7 RC clock trimming with Xtal oscillator                                              | 31              |

| ~  | 8.8 Registers overview                                                                  | 32              |

| 9  | Supply Voltage Level Detector (SVLD)                                                    | 33              |

| 10 | <b>D Port A</b><br>10.1 Basic features                                                  | <b>34</b><br>34 |

|    | 10.1 Dasic reatures                                                                     | 34<br>35        |

|    | 10.1.2 Register map, PA IO functions                                                    | 36              |

|    | 10.1.3 IO Operation                                                                     | 37              |

|    | 10.2 Port A Interrupt requests                                                          | 38              |

|    | 10.2.1 Debouncer<br>10.3 Reset and Wake-up                                              | 38<br>39        |

|    | 10.3.1 Register map                                                                     | 40              |

|    |                                                                                         |                 |

| 10.3.2 Input splitting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.3.3 Actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40                                                                                                                                                                                                                                     |

| 10.3.4 Condition match<br>10.3.5 Don't care bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40<br>41                                                                                                                                                                                                                               |

| 10.3.6 Debouncer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                                                                                                                                                                                                     |

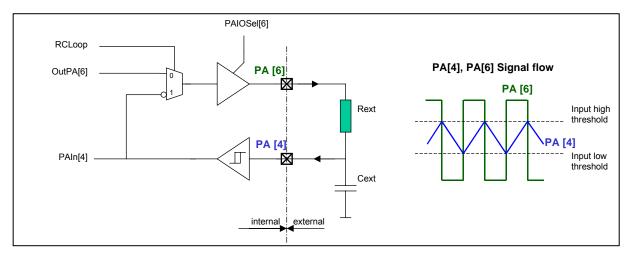

| 10.4 Oscillation Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41                                                                                                                                                                                                                                     |

| 10.4.1 Inverter function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41                                                                                                                                                                                                                                     |

| 10.5 Dual Port RAM interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41                                                                                                                                                                                                                                     |

| 11 Port B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42                                                                                                                                                                                                                                     |

| 11.1 Basic features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 42                                                                                                                                                                                                                                     |

| 11.1.1 Special function priority<br>11.1.2 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | handling 42<br>43                                                                                                                                                                                                                      |

| 11.2 Register map, PB IO functio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                        |

| 11.3 Normal IO operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45                                                                                                                                                                                                                                     |

| 11.4 Special IO operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                                                                                                                                                                                     |

| 11.4.1 Frequency Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45                                                                                                                                                                                                                                     |

| 11.4.2 SPI outputs<br>11.4.3 SPI inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46<br>46                                                                                                                                                                                                                               |

| 11.4.4 Dual Port RAM terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                        |

| 12 Serial Port Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                                                                                                                                                                                     |

| 12.1 Basic features:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47                                                                                                                                                                                                                                     |

| 12.1.1 Overview:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47                                                                                                                                                                                                                                     |

| 12.1.2 SPI terminal configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                        |

| 12.2 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48                                                                                                                                                                                                                                     |

| 12.2.1 Master and Slave mode<br>12.2.2 Fix data stream Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                        |

| 12.2.3 SPI Interruptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (Auto-Start) 48<br>48                                                                                                                                                                                                                  |

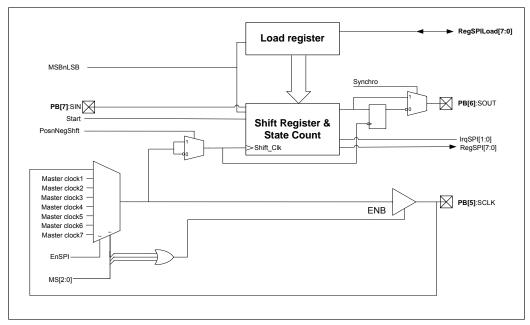

| 12.2.4 SPI edge and synchron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                        |

| 12.2.5 SPI start-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49                                                                                                                                                                                                                                     |

| 12.2.6 MSB or LSB first select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | on 49                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                        |

| 12.3 Registers overview:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50                                                                                                                                                                                                                                     |

| 13 Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50<br><b>51</b>                                                                                                                                                                                                                        |

| <b>13 Timers</b><br>13.1 Basic features:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50<br><b>51</b><br>51                                                                                                                                                                                                                  |

| <b>13 Timers</b><br>13.1 Basic features:<br>13.2 Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50<br><b>51</b>                                                                                                                                                                                                                        |

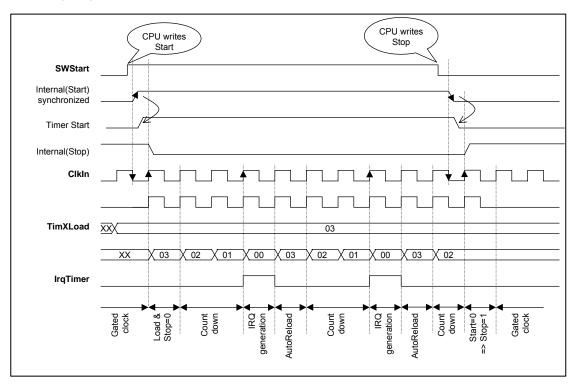

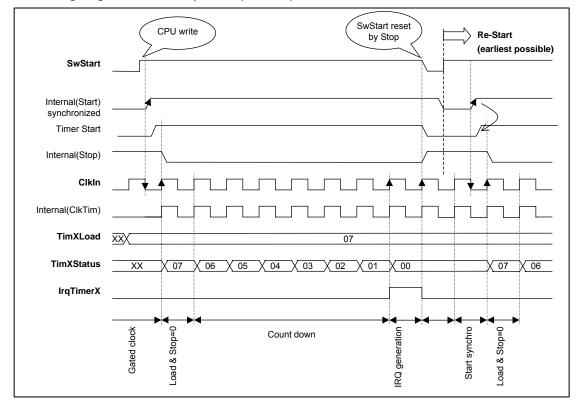

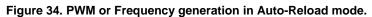

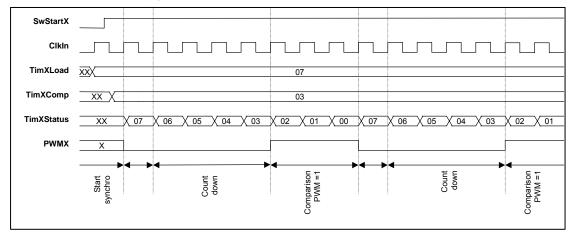

| <b>13 Timers</b><br>13.1 Basic features:<br>13.2 Functionality<br>13.2.1 Auto-Reload mode<br>13.2.2 Zero-Stop mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50<br><b>51</b><br>51<br>52<br>52<br>53                                                                                                                                                                                                |

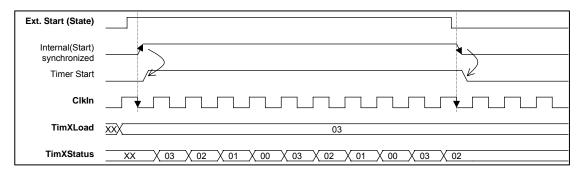

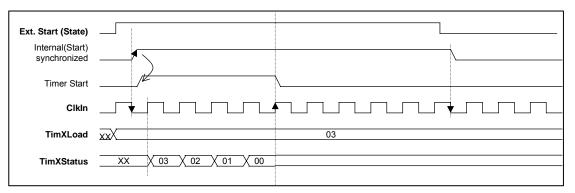

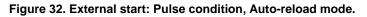

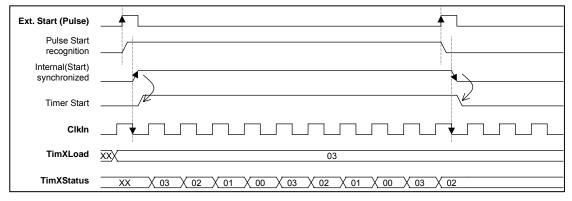

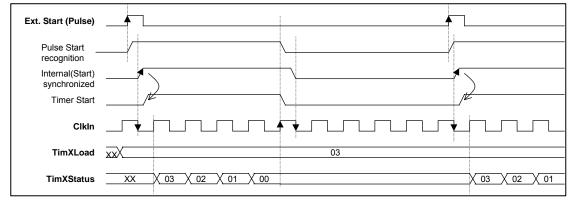

| <b>13 Timers</b><br>13.1 Basic features:<br>13.2 Functionality<br>13.2.1 Auto-Reload mode<br>13.2.2 Zero-Stop mode<br>13.2.3 Start control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50<br>51<br>51<br>52<br>52<br>53<br>54                                                                                                                                                                                                 |

| <b>13 Timers</b><br>13.1 Basic features:<br>13.2 Functionality<br>13.2.1 Auto-Reload mode<br>13.2.2 Zero-Stop mode<br>13.2.3 Start control system<br>13.2.4 Stopping the timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50<br>51<br>52<br>52<br>52<br>53<br>54<br>57                                                                                                                                                                                           |

| <b>13 Timers</b><br>13.1 Basic features:<br>13.2 Functionality<br>13.2.1 Auto-Reload mode<br>13.2.2 Zero-Stop mode<br>13.2.3 Start control system<br>13.2.4 Stopping the timer<br>13.2.5 Clock selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>57                                                                                                                                                                                           |

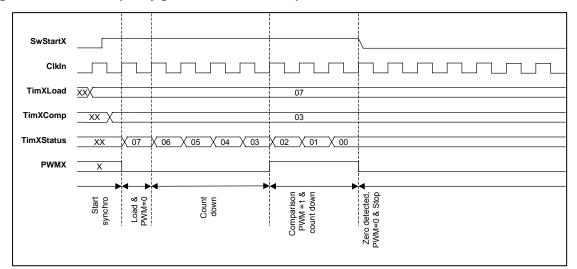

| <b>13 Timers</b><br>13.1 Basic features:<br>13.2 Functionality<br>13.2.1 Auto-Reload mode<br>13.2.2 Zero-Stop mode<br>13.2.3 Start control system<br>13.2.4 Stopping the timer<br>13.2.5 Clock selection<br>13.2.6 PWM and Frequency get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>57                                                                                                                                                                                           |

| <b>13 Timers</b><br>13.1 Basic features:<br>13.2 Functionality<br>13.2.1 Auto-Reload mode<br>13.2.2 Zero-Stop mode<br>13.2.3 Start control system<br>13.2.4 Stopping the timer<br>13.2.5 Clock selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>57<br>eneration 57                                                                                                                                                                           |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>57<br>eneration<br>57<br>58<br>59<br>g order<br>60                                                                                                                                           |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>57<br>eneration<br>57<br>58<br>59<br>g order<br>60<br>60                                                                                                                                     |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration reference</li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>57<br>eneration<br>57<br>58<br>59<br>g order<br>60<br>egisters<br>60                                                                                                                         |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>57<br>eneration<br>57<br>58<br>59<br>g order<br>60<br>60                                                                                                                                     |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration re</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                       | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>57<br>eneration 57<br>58<br>59<br>g order 60<br>60<br>egisters 60<br>61<br>62<br>63                                                                                                          |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration re</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> <li>13.4.4 Timer3 configuration</li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                  | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>eneration 57<br>58<br>59<br>g order 60<br>60<br>egisters 60<br>61<br>62<br>63<br>64                                                                                                          |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration re</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> <li>13.4.4 Timer3 configuration</li> <li>13.4.5 Timer4 configuration</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                           | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>eneration<br>57<br>58<br>59<br>g order<br>60<br>egisters<br>60<br>61<br>62<br>63<br>64<br>65                                                                                                 |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> <li>13.4.4 Timer3 configuration</li> <li>13.4.5 Timer4 configuration</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                              | 50<br>51<br>51<br>52<br>52<br>53<br>54<br>57<br>57<br>eneration<br>57<br>58<br>59<br>g order<br>60<br>egisters<br>60<br>61<br>62<br>63<br>64<br><b>65</b>                                                                              |

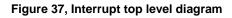

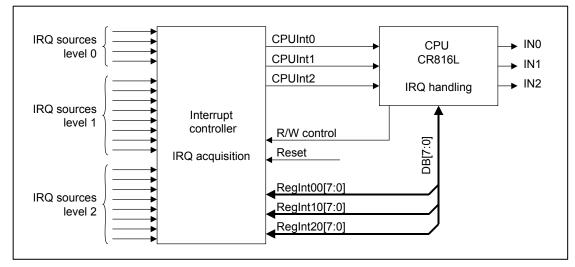

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency get</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> <li>13.4.4 Timer3 configuration</li> <li>13.4.5 Timer4 configuration</li> </ul> </li> <li>14 Interruptions <ul> <li>14.1 Basic features</li> <li>14.2 Interrupt acquisition</li> </ul> </li> </ul>                                                                                                                                                                                                                                      | 50<br>51<br>51<br>52<br>52<br>53<br>54<br>57<br>57<br>eneration 57<br>58<br>59<br>g order 60<br>egisters 60<br>61<br>62<br>63<br>64<br>65<br>65<br>65<br>66                                                                            |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> <li>13.4.4 Timer3 configuration</li> <li>13.4.5 Timer4 configuration</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                              | 50<br>51<br>51<br>52<br>52<br>53<br>54<br>57<br>eneration 57<br>58<br>59<br>g order 60<br>egisters 60<br>61<br>62<br>63<br>64<br>65<br>65<br>65<br>65<br>65                                                                            |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> <li>13.4.4 Timer3 configuration</li> <li>13.4.5 Timer4 configuration</li> <li>13.4.1 Basic features</li> <li>14.1 Basic features</li> <li>14.2 Interrupt acquisition</li> <li>14.2.1 Interrupt acquisition ma</li> <li>14.2.2 Interrupt acquisition Cle</li> <li>14.2.3 Register map, Interrupt</li> </ul> </li> </ul>                                                                                                                   | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>eneration 57<br>57<br>eneration 57<br>58<br>59<br>g order 60<br>egisters 60<br>61<br>62<br>63<br>64<br>65<br>65<br>65<br>8king. 67<br>aring 67<br>acquisition 67                             |

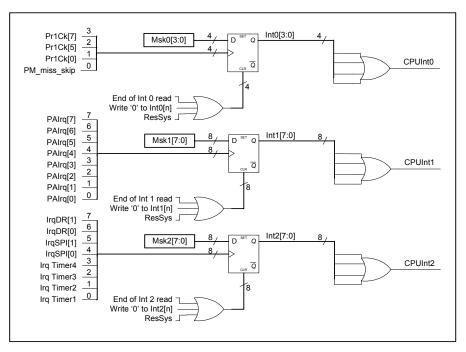

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> <li>13.4.4 Timer3 configuration</li> <li>13.4.5 Timer4 configuration</li> <li>13.4.1 Basic features</li> <li>14.1 Basic features</li> <li>14.2 Interrupt acquisition</li> <li>14.2.1 Interrupt acquisition ma</li> <li>14.2.2 Interrupt acquisition Cle</li> <li>14.2.3 Register map, Interrupt</li> <li>14.3 CPU Interrupt and Event ha</li> </ul></li></ul>                                                                            | 50<br>51<br>51<br>52<br>52<br>53<br>54<br>57<br>eneration 57<br>57<br>eneration 57<br>58<br>59<br>g order 60<br>egisters 60<br>61<br>62<br>63<br>64<br>65<br>65<br>65<br>8king. 67<br>aring 67<br>acquisition 67<br>ndling 68          |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> <li>13.4.4 Timer3 configuration</li> <li>13.4.5 Timer4 configuration</li> <li>13.4.1 Basic features</li> <li>14.1 Basic features</li> <li>14.2 Interrupt acquisition</li> <li>14.2.1 Interrupt acquisition</li> <li>14.2.2 Interrupt acquisition ma</li> <li>14.2.3 Register map, Interrupt</li> <li>14.3 CPU Interrupt and Event ha</li> <li>14.3.1 Interrupt priority</li> </ul></li></ul>                                             | 50<br>51<br>51<br>52<br>52<br>53<br>54<br>57<br>eneration 57<br>58<br>59<br>g order 60<br>egisters 60<br>61<br>62<br>63<br>64<br>65<br>65<br>65<br>8king. 67<br>aring 67<br>acquisition 67<br>indling 68<br>68                         |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> <li>13.4.4 Timer3 configuration</li> <li>13.4.5 Timer4 configuration</li> <li>13.4.1 Basic features</li> <li>14.1 Basic features</li> <li>14.2 Interrupt acquisition</li> <li>14.2.1 Interrupt acquisition</li> <li>14.2.2 Interrupt acquisition readition</li> <li>14.2.3 Register map, Interrupt</li> <li>14.3 CPU Interrupt and Event hat</li> <li>14.3.1 Interrupt priority</li> <li>14.3.2 CPU Status register</li> </ul></li></ul> | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>eneration 57<br>58<br>59<br>g order 60<br>egisters 60<br>61<br>62<br>63<br>64<br>65<br>65<br>65<br>65<br>65<br>65<br>65<br>66<br>8king. 67<br>aring 67<br>acquisition 67<br>indling 68<br>69 |

| <ul> <li>13 Timers <ul> <li>13.1 Basic features:</li> <li>13.2 Functionality</li> <li>13.2.1 Auto-Reload mode</li> <li>13.2.2 Zero-Stop mode</li> <li>13.2.3 Start control system</li> <li>13.2.4 Stopping the timer</li> <li>13.2.5 Clock selection</li> <li>13.2.6 PWM and Frequency ge</li> <li>13.2.7 16-bits configuration</li> <li>13.2.8 Interrupts</li> <li>13.3 Recommended programmin</li> <li>13.4 Registers overview:</li> <li>13.4.1 General configuration</li> <li>13.4.2 Timer1 configuration</li> <li>13.4.3 Timer2 configuration</li> <li>13.4.4 Timer3 configuration</li> <li>13.4.5 Timer4 configuration</li> <li>13.4.1 Basic features</li> <li>14.1 Basic features</li> <li>14.2 Interrupt acquisition</li> <li>14.2.1 Interrupt acquisition</li> <li>14.2.2 Interrupt acquisition ma</li> <li>14.2.3 Register map, Interrupt</li> <li>14.3 CPU Interrupt and Event ha</li> <li>14.3.1 Interrupt priority</li> </ul></li></ul>                                             | 50<br>51<br>52<br>52<br>53<br>54<br>57<br>eneration 57<br>58<br>59<br>g order 60<br>egisters 60<br>61<br>62<br>63<br>64<br>65<br>65<br>65<br>65<br>65<br>65<br>65<br>66<br>8king. 67<br>aring 67<br>acquisition 67<br>indling 68<br>69 |

| Memo | lemory mapping 7                                |    |  |  |  |  |  |  |

|------|-------------------------------------------------|----|--|--|--|--|--|--|

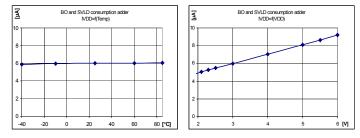

| 16 T | ypical V and T dependencies                     | 74 |  |  |  |  |  |  |

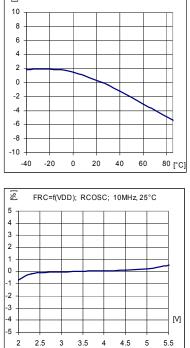

| 16.1 |                                                 | 74 |  |  |  |  |  |  |

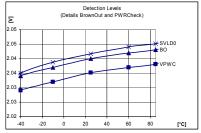

| 16.2 | SVLD, BO Detection levels                       | 75 |  |  |  |  |  |  |

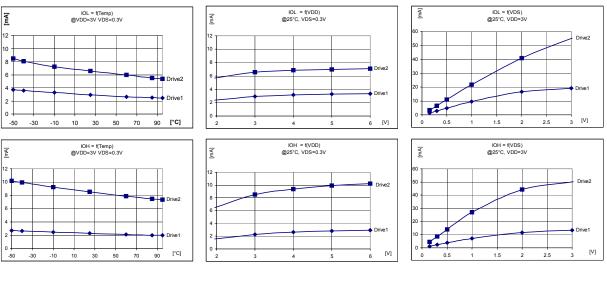

| 16.3 | IOL and IOH drives                              | 75 |  |  |  |  |  |  |

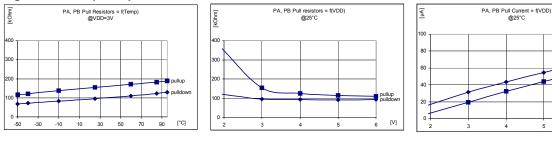

| 16.4 | Pullup and Pulldown                             | 75 |  |  |  |  |  |  |

| 17 E | lectrical Specification                         | 77 |  |  |  |  |  |  |

| 17.1 | Absolute Maximum Ratings                        | 77 |  |  |  |  |  |  |

| 17.2 | Handling Procedures                             | 77 |  |  |  |  |  |  |

| 17.3 | Standard Operating Conditions                   | 77 |  |  |  |  |  |  |

| 17.4 | Typical Crystal specification                   | 77 |  |  |  |  |  |  |

| 17.5 | 5 DC Characteristics - Power Supply Currents 3  | 77 |  |  |  |  |  |  |

| 17.6 | 5 DC Characteristics – Voltage detection levels | 78 |  |  |  |  |  |  |

| 17.7 | DC Characteristics – Oscillators                | 78 |  |  |  |  |  |  |

| 17.8 | B DC Characteristics - I/O Pins                 | 79 |  |  |  |  |  |  |

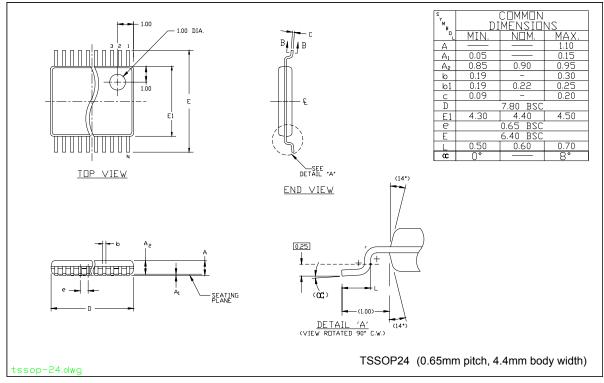

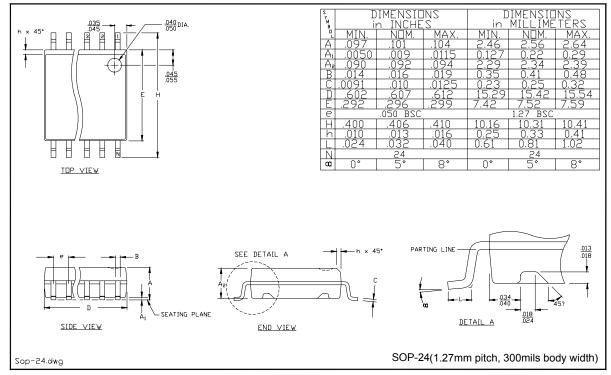

| 17.9 | Package drawings                                | 80 |  |  |  |  |  |  |

| 18 O | Prdering information Flash device               | B1 |  |  |  |  |  |  |

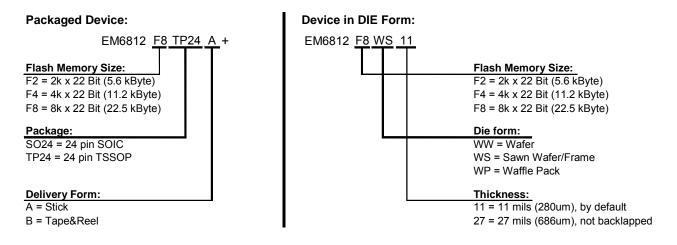

18 Ordering information Flash device

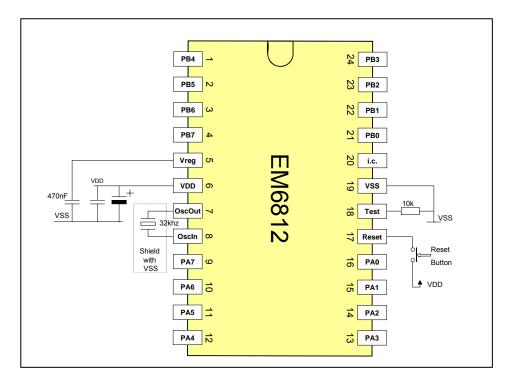

### 2 Circuit Connectivity

The EM6812 has the same pin-out in both the SO24 and TSSOP24 pin package. Minimum connectivity includes the power supply on  $V_{SS}$  and  $V_{DD}$ , a capacitor on Vreg, and de-coupling capacitance on  $V_{DD}$ .

Circuit reference terminal (substrate) is on  $V_{SS}$ .

The 32kHz Crystal is only needed for systems requiring low frequency Crystal operation.

The integrated supply voltage regulator filters supply noise and allows lowest power peripheral operations. For proper operation, a capacitor (470nF minimum) must be connected to the regulator's VREG terminal. This terminal must not be used for any other outside connection.

### Figure 1: Sample minimum connectivity

#### Note:

- ALL circuit IO's (except OscIn) are on V<sub>DD</sub> level. OscIn terminal is only used in conjunction with an quartz Crystal. The terminal input voltages must never exceed the Vreg voltage.

- The quartz crystal should be shielded with  $V_{SS}$  to keep noise away.

- When using the Crystal oscillator PA[7] and PA[6] should preferably used as static inputs only to avoid noise coupling on the OscIn and OscOut high impedance inputs.

5

### 2.1 Terminal usage

#### Table 1. Circuit terminals

| Pin | Name            |     | Description                                               | SPI & PWM                                  | Dual Port<br>RAM  | Programming connections |

|-----|-----------------|-----|-----------------------------------------------------------|--------------------------------------------|-------------------|-------------------------|

| 1   | PB4             | ю   | Standard IO                                               |                                            | DPRData[4]        |                         |

| 2   | PB5             | ю   | Standard IO                                               | SCLK                                       | DPRData[5]        | SCLK                    |

| 3   | PB6             | Ю   | Standard IO                                               | SOUT                                       | DPRData[6]        |                         |

| 4   | PB7             | ю   | Standard IO                                               | SIN                                        | DPRData[7]        | SDIO                    |