## IS24C128A IS24C256A

## 128K-bit/ 256K-bit 2-WIRE SERIAL CMOS EEPROM

## ADVANCED INFORMATION JULY 2006

#### **FEATURES**

- Two-Wire Serial Interface, I<sup>2</sup>C<sup>™</sup> compatible

Bi-directional data transfer protocol

- · Wide Voltage Operation

- -Vcc = 1.8V to 5.5V

- 400 KHz (2.5V) and 1 MHz (5.0V) compatibility

- Low Power CMOS Technology

- -Active Current less than 3 mA (2.5V)

- -Standby Current less than 20 µA (2.5V)

- · Hardware Data Protection

- -Write Protect Pin

- Sequential Read Feature

- Filtered Inputs for Noise Suppression

- · Self time write cycle with auto clear

- -5 ms @ 2.5V

- Organization:

- -16Kx8 (256 pages of 64 bytes)

- -32Kx8 (512 pages of 64 bytes)

- 64 Byte Page Write Buffer

- High Reliability

- -Endurance: 1,000,000 Cycles

- -Data Retention: 40 Years

- Industrial and Automotive temperature ranges

- 8-pin PDIP, 8-pin (JEDEC) SOIC, and 8-pin (EIAJ) SOIC packages

- · Lead-free available

#### DESCRIPTION

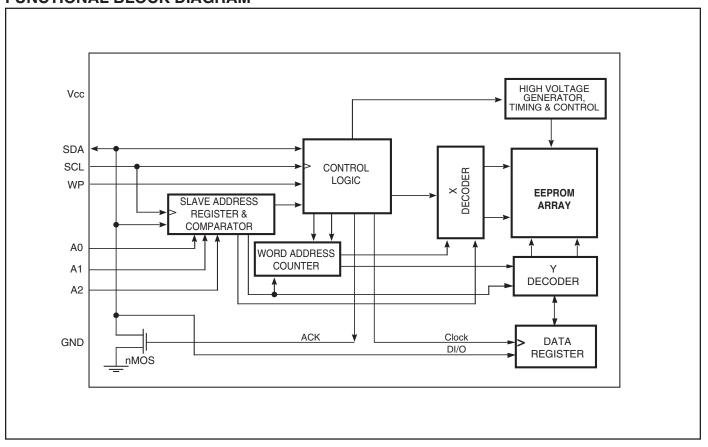

The IS24C128A/256A is an electrically erasable PROM device that uses the standard 2-wire interface for communications. The IS24C128A is 128K-bit (16Kx8) and the IS24C256A is 256K-bit (32Kx8). These EEPROM are offered in a wide operating voltage range of 1.8V to 5.5V to be compatible with most application voltages. ISSI designed the IS24C128A/256A to be an efficient 2-wire EEPROM solution. The devices are packaged in 8-pin PDIP, 8-pin (JEDEC) SOIC, and 8-pin (EIAJ) SOIC.

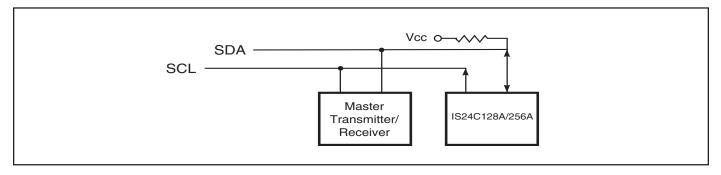

The IS24C128A/256A maintains compatibility with the popular 2-wire bus protocol, so it is easy to design into applications implementing this bus type. The simple bus consists of the Serial Clock wire (SCL) and the Serial Data wire (SDA). Using the bus, a Master device such as a microcontroller is usually connected to one or more Slave devices such as the IS24C128A/256A. The bit stream over the SDA line includes a series of bytes, which identifies a particular Slave device, an instruction, an address within that Slave device, and a series of data, if appropriate. The IS24C128A/256A has a Write Protect pin (WP) to allow blocking of any write instruction transmitted over the bus.

Copyright@2006 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

## **FUNCTIONAL BLOCK DIAGRAM**

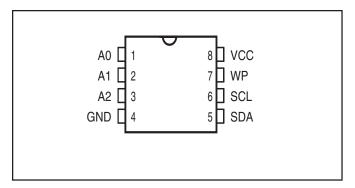

# PIN CONFIGURATION 8-Pin DIP and SOIC

#### PIN DESCRIPTIONS

| A0-A2 | Address Inputs          |  |

|-------|-------------------------|--|

| SDA   | Serial Address/Data I/O |  |

| SCL   | Serial Clock Input      |  |

| WP    | Write Protect Input     |  |

| Vcc   | Power Supply            |  |

| NC    | No Connect              |  |

| GND   | Ground                  |  |

## SCL

This input clock pin is used to synchronize the data transfer to and from the device.

#### **SDA**

The SDA is a Bi-directional pin used to transfer addresses and data into and out of the device. The SDA pin is an open drain output and can be wire Or'ed with other open drain or open collector outputs. The SDA bus *requires* a pullup resistor to Vcc.

## A0, A1, A2

The A0, A1, and A2 are the device address inputs that are hardwired or left not connected for hardware compatibility with the IS24C32A/64A. When pins are hardwired, as many as eight 256K devices may be addressed on a single bus system. When the pins are not hardwired, the default values of A0, A1, and A2 are zero.

## **WP**

WP is the Write Protect pin. If the WP pin is tied to Vcc the entire array becomes Write Protected (Read only). When WP is tied to GND or left floating, normal read/write operations are allowed to the device.

#### **DEVICE OPERATION**

The IS24C128A/256A features a serial communication and supports a bi-directional 2-wire bus transmission protocol called  $I^2C^{TM}$ .

#### 2-WIRE BUS

The two-wire bus is defined as a Serial Data line (SDA), and a Serial Clock line (SCL). The protocol defines any device that sends data onto the SDA bus as a transmitter, and the receiving devices as receivers. The bus is controlled by Master device which generates the SCL, controls the bus access and generates the Stop and Start conditions. The IS24C128A/256A is the Slave device on the bus.

#### The Bus Protocol:

- Data transfer may be initiated only when the bus is not busy

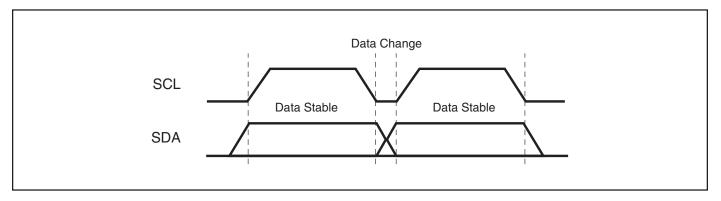

- During a data transfer, the SDA line must remain stable whenever the SCL line is high. Any changes in the data line while the SCL line is high will be interpreted as a Start or Stop condition.

The state of the SDA line represents valid data after a Start condition. The SDA line must be stable for the duration of the High period of the clock signal. The data on the SDA line may be changed during the Low period of the clock signal. There is one clock pulse per bit of data. Each data transfer is initiated with a Start condition and terminated with a Stop condition.

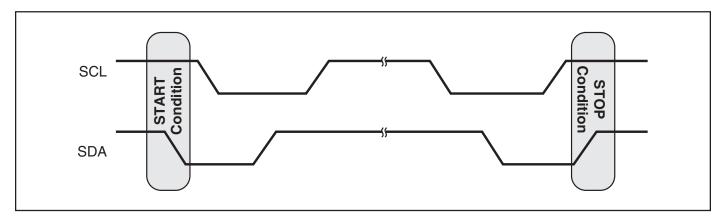

#### **Start Condition**

The Start condition precedes all commands to the device and is defined as a High to Low transition of SDA when SCL is High. The IS24C128A/256A monitors the SDA and SCL lines and will not respond until the Start condition is met.

## **Stop Condition**

The Stop condition is defined as a Low to High transition of SDA when SCL is High. All operations must end with a Stop condition.

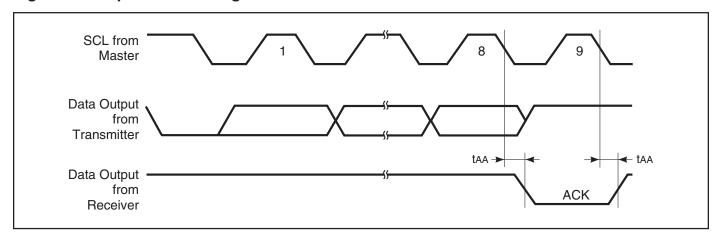

## Acknowledge (ACK)

After a successful data transfer, each receiving device is required to generate an ACK. The Acknowledging device pulls down the SDA line.

#### Reset

The IS24C128A/256A contains a reset function in case the 2-wire bus transmission is accidentally interrupted (eg. a power loss), or needs to be terminated mid-stream. The reset is caused when the Master device creates a Start condition. To do this, it may be necessary for the Master device to monitor the SDA line while cycling the

SCL up to nine times. (For each clock signal transition to High, the Master checks for a High level on SDA.)

## **Standby Mode**

Power consumption is reduced in standby mode. The IS24C128A/256A will enter standby mode: a) At Power-up, and remain in it until SCL or SDA toggles; b) Following the Stop signal if no write operation is initiated; or c) Following any internal write operation

#### **DEVICE ADDRESSING**

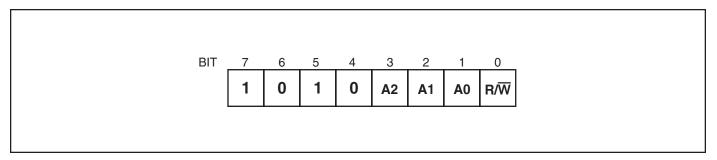

The Master begins a transmission by sending a Start condition. The Master then sends the address of the particular Slave devices it is requesting. The Slave device (Fig. 5) address is 8 bits.

The four most significant bits of the Slave device address are fixed as 1010 for the IS24C128A/256A.

This device has three address bits (A2, A1, and A0), which allows up to eight IS24C128A/256A devices to share the 2-wire bus. Upon receiving the Slave address, the device compares the three address bits with the hardwired A2, A1, and A0 input pins to determine if it is the appropriate Slave.

The last bit of the Slave address specifies whether a Read or Write operation is to be performed. When this bit is set to 1, a Read operation is selected, and when set to 0, a Write operation is selected.

After the Master transmits the Start condition and Slave address byte (Fig. 5), the appropriate 2-wire Slave (eg. IS24C128A/256A) will respond with ACK on the SDA line. The Slave will pull down the SDA on the ninth clock cycle, signaling that it received the eight bits of data. The selected IS24C128A/256A then prepares for a Read or Write operation by monitoring the bus.

#### WRITE OPERATION

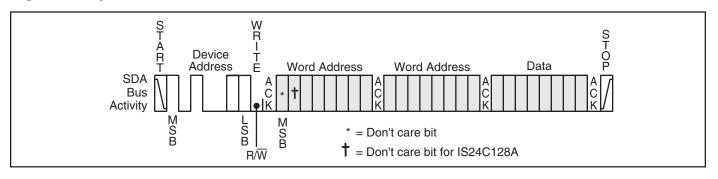

#### **Byte Write**

In the Byte Write mode, the Master device sends the Start condition and the Slave address information (with the R/ $\overline{W}$  set to Zero) to the Slave device. After the Slave generates an ACK, the Master sends the two byte address that are to be written into the address pointer of the IS24C128A/256A. After receiving another ACK from the Slave, the Master device transmits the data byte to be written into the address memory location. The IS24C128A/256A acknowledges once more and the Master generates the Stop condition, at which time the device begins its internal programming cycle. While this internal cycle is in progress, the device will not respond to any request from the Master device.

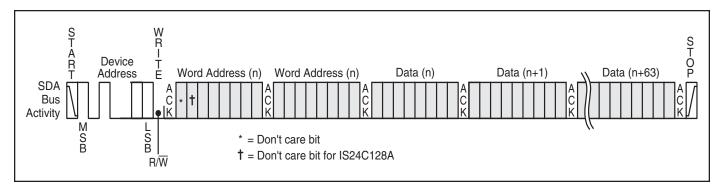

## **Page Write**

The IS24C128A/256A is capable of 64-byte Page-Write operation. A Page-Write is initiated in the same manner as a Byte Write, but instead of terminating the internal Write cycle after the first data word is transferred, the Master device can transmit up to 63 more bytes. After the receipt of each data word, the IS24C128A/256A responds immediately with an ACK on SDA line, and the six lower order data word address bits are internally incremented by one, while the higher order bits of the data word address remain constant. If a byte address is incremented from the last byte of a page, it returns to the first byte of that page. If the Master device should transmit more than 64 words prior to issuing the Stop condition, the address counter will "roll over," and the previously written data will be overwritten. Once all 64 bytes are received and the Stop condition has been sent by the Master, the internal programming cycle begins. At this point, all received data is written to the IS24C128A/256A in a single Write cycle. All inputs are disabled until completion of the internal Write cycle.

## Acknowledge (ACK) Polling

The disabling of the inputs can be used to take advantage of the typical Write cycle time. Once the Stop condition is issued to indicate the end of the host's Write operation, the IS24C128A/256A initiates the internal Write cycle. ACK polling can be initiated immediately. This involves issuing the Start condition followed by the Slave address for a Write operation. If the IS24C128A/256A is still busy with the Write operation, no ACK will be returned. If the IS24C128A/256A has completed the Write operation, an ACK will be returned and the host can then proceed with the next Read or Write operation.

#### **READ OPERATION**

Read operations are initiated in the same manner as Write operations, except that the  $(R/\overline{W})$  bit of the Slave address is set to "1". There are three Read operation options: current address read, random address read, and sequential read.

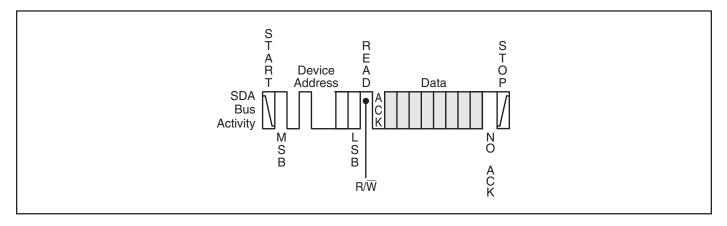

#### **Current Address Read**

The IS24C128A/256A contains an internal address counter which maintains the address of the last byte accessed, incremented by one. For example, if the previous operation is either a Read or Write operation addressed to the address location n, the internal address counter would increment to address location n+1. When the IS24C128A/256A receives the Slave Device Addressing Byte with a Read operation (R/ $\overline{\mathbf{W}}$  bit set to "1"), it will respond an ACK and transmit the 8-bit data word stored at address location n+1. The Master should not acknowledge the transfer but

should generate a Stop condition so the IS24C128A/256A discontinues transmission. If 'n' is the last byte of the memory, the data from location '0' will be transmitted. (Refer to Figure 8. Current Address Read Diagram.)

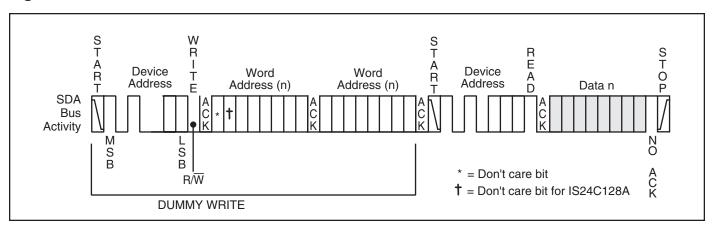

#### **Random Address Read**

Selective Read operations allow the Master device to select at random any memory location for a Read operation. The Master device first performs a 'dummy' Write operation by sending the Start condition, Slave address and word address of the location it wishes to read. After the IS24C128A/256A acknowledges the word address, the Master device resends the Start condition and the Slave address, this time with the R/ $\overline{\mathbf{W}}$  bit set to one. The IS24C128A/256A then responds with its ACK and sends the data requested. The Master device does not send an ACK but will generate a Stop condition. (Refer to Figure 9. Random Address Read Diagram.)

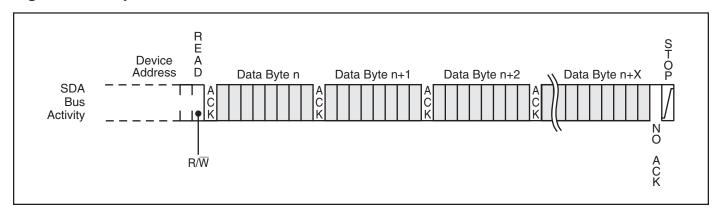

## Sequential Read

Sequential Reads can be initiated as either a Current Address Read or Random Address Read. After the IS24C128A/256A sends the initial byte sequence, the Master device now responds with an ACK indicating it requires additional data from the IS24C128A/256A. The IS24C128A/256A continues to output data for each ACK received. The Master device terminates the sequential Read operation by pulling SDA High (no ACK) indicating the last data word to be read, followed by a Stop condition.

The data output is sequential, with the data from address n followed by the data from address n+1, ... etc. The address counter increments by one automatically, allowing the entire memory contents to be serially read during sequential Read operation. When the memory address boundary of 16383 or 32767 (depending on the device) is reached, the address counter "rolls over" to address 0, and the IS24C128A/256A continues to output data for each ACK received. (Refer to Figure 10. Sequential Read Operation Starting with a Random Address Read Diagram.)

Figure 1. Typical System Bus Configuration

Figure 2. Output Acknowledge

Figure 3. Start and Stop Conditions

Figure 4. Data Validity Protocol

Figure 5. Slave Address

Figure 6. Byte Write

Figure 7. Page Write

Figure 8. Current Address Read

Figure 9. Random Address Read

Figure 10. Sequential Read

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| Symbol | ol Parameter Value     |                  | Unit |

|--------|------------------------|------------------|------|

| Vs     | Supply Voltage         | -0.5 to +6.5     | V    |

| VP     | Voltage on Any Pin     | -0.5 to Vcc +0.5 | V    |

| TBIAS  | Temperature Under Bias | -55 to +125      | °C   |

| Тѕтс   | Storage Temperature    | -65 to +150      | °C   |

| Іоит   | Output Current         | 5                | mA   |

#### Notes:

## **OPERATING RANGE (IS24C128A/256A-2)**

| Range      | Ambient Temperature | Vcc          |

|------------|---------------------|--------------|

| Industrial | -40°C to +85°C      | 1.8V to 5.5V |

Note: ISSI offers Industrial grade for Commercial application (0°C to +70°C).

## **OPERATING RANGE (IS24C128A/256A-3)**

| Range      | Ambient Temperature | Vcc          |

|------------|---------------------|--------------|

| Automotive | -40°C to +125°C     | 2.5V to 5.5V |

### CAPACITANCE(1,2)

| Symbol | Parameter          | Conditions    | Max. | Unit |

|--------|--------------------|---------------|------|------|

| CIN    | Input Capacitance  | $V_{IN} = 0V$ | 6    | рF   |

| Соит   | Output Capacitance | VOUT = $0V$   | 8    | pF   |

#### Notes:

Stresses violating the conditions listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only. Functional operation of the

device outside these conditions or those indicated in the operational sections of this

specification is not implied. Exposure to these conditions for extended periods may affect

reliability.

<sup>1.</sup> Tested initially and after any design or process changes that may affect these parameters.

<sup>2.</sup> Test conditions:  $T_A = 25^{\circ}C$ , f = 1 MHz,  $V_{CC} = 5.0V$ .

## DC ELECTRICAL CHARACTERISTICS

Industrial (TA = -40°C to +85°C), Automotive (TA = -40°C to +125°C)

| Symbol | Parameter              | Test Conditions              | Min.      | Max.      | Unit |

|--------|------------------------|------------------------------|-----------|-----------|------|

| Vol1   | Output Low Voltage     | Vcc = 1.8V, $IoL = 0.15  mA$ | _         | 0.2       | V    |

| Vol2   | Output Low Voltage     | Vcc = 2.5V, loL = 2.1 mA     | _         | 0.4       | V    |

| VIH    | Input High Voltage     |                              | Vcc x 0.7 | Vcc + 0.5 | V    |

| VIL    | Input Low Voltage      |                              | -1.0      | Vcc x 0.3 | V    |

| ILI    | Input Leakage Current  | Vin = Vcc max.               | _         | 3         | μΑ   |

| ILO    | Output Leakage Current |                              | _         | 3         | μA   |

Notes: VIL min and VIH max are reference only and are not tested.

## **POWER SUPPLY CHARACTERISTICS**

Industrial ( $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ), Automotive ( $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ )

| Symbol | Parameter             | Test Conditions               | Min. | Max. | Unit |

|--------|-----------------------|-------------------------------|------|------|------|

| Icc1   | Vcc Operating Current | Read at 400 KHz (Vcc = 2.5V)  | _    | 3.0  | mA   |

| Icc2   | Vcc Operating Current | Write at 400 KHz (Vcc = 2.5V) | _    | 3.0  | mA   |

| IsB1   | Standby Current       | Vcc = 1.8V                    | _    | 15   | μΑ   |

| IsB2   | Standby Current       | Vcc = 2.5V                    | _    | 20   | μΑ   |

| IsB3   | Standby Current       | Vcc = 5.0V                    | _    | 25   | μA   |

#### **AC ELECTRICAL CHARACTERISTICS**

Industrial ( $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ )

|               |                                                      | 1.8V≤V | cc < 2.5V | 2.5V≤V | cc < 4.5V | 4.5V≤Vo | cc≤5.5V <sup>(1)</sup> |      |

|---------------|------------------------------------------------------|--------|-----------|--------|-----------|---------|------------------------|------|

| Symbol        | Parameter                                            | Min.   | Max.      | Min.   | Max.      | Min.    | Max.                   | Unit |

| fscL          | SCL Clock Frequency                                  | 0      | 100       | 0      | 400       | 0       | 1000                   | KHz  |

| Т             | Noise Suppression Time <sup>(1)</sup>                | _      | 100       | _      | 50        | _       | 50                     | ns   |

| <b>L</b> ow   | Clock Low Period                                     | 4.7    | _         | 1.2    | _         | 0.6     | _                      | μs   |

| <b>t</b> High | Clock High Period                                    | 4      | _         | 0.6    | _         | 0.4     | _                      | μs   |

| tBUF          | Bus Free Time Before New Transmission <sup>(1)</sup> | 4.7    | _         | 1.2    | _         | 0.5     | _                      | μs   |

| tsu:sta       | Start Condition Setup Time                           | 4      | _         | 0.6    | _         | 0.25    | _                      | μs   |

| tsu:sto       | Stop Condition Setup Time                            | 4      | _         | 0.6    | _         | 0.25    | _                      | μs   |

| thd:STA       | Start Condition Hold Time                            | 4      | _         | 0.6    | _         | 0.25    | _                      | μs   |

| thd:sto       | Stop Condition Hold Time                             | 4      | _         | 0.6    | _         | 0.25    | _                      | μs   |

| tsu:dat       | Data In Setup Time                                   | 100    | _         | 100    | _         | 100     | _                      | ns   |

| thd:dat       | Data In Hold Time                                    | 0      | _         | 0      | _         | 0       | _                      | ns   |

| tsu:wp        | WP pin Setup Time                                    | 4      | _         | 0.6    | _         | 0.6     | _                      | μs   |

| thd:wp        | WP pin Hold Time                                     | 4.7    | _         | 1.2    | _         | 1.2     | _                      | μs   |

| ton           | Data Out Hold Time                                   | 100    | _         | 50     | _         | 50      | _                      | ns   |

|               | (SCL Low to SDA Data Out Change)                     |        |           |        |           |         |                        |      |

| taa           | Clock to Output (SCL Low to SDA Data Out Valid)      | 100    | 3500      | 50     | 900       | 50      | 400                    | ns   |

| tR            | SCL and SDA Rise Time <sup>(1)</sup>                 | _      | 1000      | _      | 300       | _       | 300                    | ns   |

| tF            | SCL and SDA Fall Time <sup>(1)</sup>                 |        | 300       | _      | 300       | _       | 100                    | ns   |

| twr           | Write Cycle Time                                     | _      | 10        | _      | 5         | _       | 5                      | ms   |

#### Notes

1. This parameter is characterized but not 100% tested.

## **AC ELECTRICAL CHARACTERISTICS**

Automotive ( $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ )

|                 |                                                      | 2.5V≤V | cc < 4.5V | $4.5V \le Vcc \le 5.5V^{(1)}$ |      |

|-----------------|------------------------------------------------------|--------|-----------|-------------------------------|------|

| Symbol          | Parameter                                            | Min.   | Max.      | Min. Max.                     | Unit |

| fscl            | SCL Clock Frequency                                  | 0      | 400       | 0 1000                        | KHz  |

| Т               | Noise Suppression Time <sup>(1)</sup>                | _      | 50        | — 50                          | ns   |

| <b>t</b> Low    | Clock Low Period                                     | 1.2    | _         | 0.6 —                         | μs   |

| <b>t</b> High   | Clock High Period                                    | 0.6    | _         | 0.4 —                         | μs   |

| <b>t</b> BUF    | Bus Free Time Before New Transmission <sup>(1)</sup> | 1.2    | _         | 0.5 —                         | μs   |

| tsu:sta         | Start Condition Setup Time                           | 0.6    | _         | 0.25 —                        | μs   |

| tsu:sto         | Stop Condition Setup Time                            | 0.6    | _         | 0.25 —                        | μs   |

| thd:STA         | Start Condition Hold Time                            | 0.6    | _         | 0.25 —                        | μs   |

| thd:sto         | Stop Condition Hold Time                             | 0.6    | _         | 0.25 —                        | μs   |

| tsu:dat         | Data In Setup Time                                   | 100    | _         | 100 —                         | ns   |

| thd:dat         | Data In Hold Time                                    | 0      | _         | 0 —                           | ns   |

| tsu:wp          | WP pin Setup Time                                    | 0.6    | _         | 0.6 —                         | μs   |

| thd:wp          | WP pin Hold Time                                     | 1.2    | _         | 1.2 —                         | μs   |

| to <sub>H</sub> | Data Out Hold Time (SCL Low to SDA Data Out Change)  | 50     | _         | 50 —                          | ns   |

| taa             | Clock to Output (SCL Low to SDA Data Out Valid)      | 50     | 900       | 50 550                        | ns   |

| <b>t</b> R      | SCL and SDA Rise Time <sup>(1)</sup>                 | _      | 300       | — 300                         | ns   |

| tF              | SCL and SDA Fall Time <sup>(1)</sup>                 | _      | 300       | — 100                         | ns   |

| twr             | Write Cycle Time                                     | _      | 10        | <b>—</b> 5                    | ms   |

#### Note:

1. This parameter is characterized but not 100% tested.

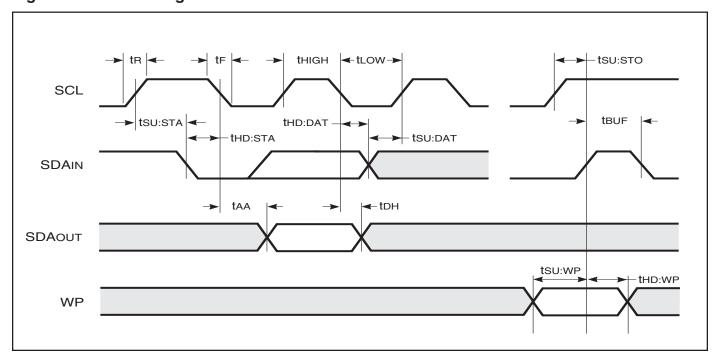

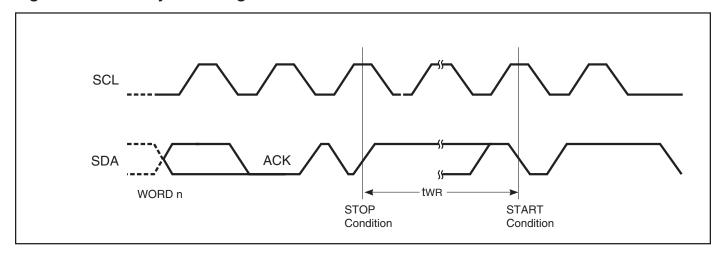

## **AC WAVEFORMS**

Figure 11. Bus Timing

Figure 12. Write Cycle Timing

ORDERING INFORMATION: IS24C128A Industrial Range: -40°C to +85°C, Lead-free

| Voltage<br>Range | Part Number    | Package                           |

|------------------|----------------|-----------------------------------|

| 1.8V             | IS24C128A-2PLI | 300-mil Plastic DIP (8-pin)       |

| to 5.5V          | IS24C128A-2GLI | Small Outline (JEDEC STD) (8-pin) |

|                  | IS24C128A-2WLI | Small Outline (EIAJ STD) (8-pin)  |

Industrial Range: -40°C to +85°C

| Voltage<br>Range | Part Number   | Package                           |

|------------------|---------------|-----------------------------------|

| nariye           | Partivullibei | Fackage                           |

| 1.8V             | IS24C128A-2PI | 300-mil Plastic DIP (8-pin)       |

| to 5.5V          | IS24C128A-2GI | Small Outline (JEDEC STD) (8-pin) |

|                  | IS24C128A-2WI | Small Outline (EIAJ STD) (8-pin)  |

ORDERING INFORMATION: IS24C256A Industrial Range: -40°C to +85°C, Lead-free

| Voltage<br>Range | Part Number    | Package                           |

|------------------|----------------|-----------------------------------|

| 1.8V             | IS24C256A-2PLI | 300-mil Plastic DIP (8-pin)       |

| to 5.5V          | IS24C256A-2GLI | Small Outline (JEDEC STD) (8-pin) |

|                  | IS24C256A-2WLI | Small Outline (EIAJ STD) (8-pin)  |

Industrial Range: -40°C to +85°C

| Voltage<br>Range | Part Number   | Package                           |

|------------------|---------------|-----------------------------------|

| 1.8V             | IS24C256A-2PI | 300-mil Plastic DIP (8-pin)       |

| to 5.5V          | IS24C256A-2GI | Small Outline (JEDEC STD) (8-pin) |

|                  | IS24C256A-2WI | Small Outline (EIAJ STD) (8-pin)  |

**ORDERING INFORMATION: IS24C128A**

Automotive Range: -40°C to +125°C, Lead-free

| Voltage |                 |                                   |

|---------|-----------------|-----------------------------------|

| Range   | Part Number     | Package                           |

| 2.5V    | IS24C128A-3PLA3 | 300-mil Plastic DIP (8-pin)       |

| to 5.5V | IS24C128A-3GLA3 | Small Outline (JEDEC STD) (8-pin) |

|         | IS24C128A-3WLA3 | Small Outline (EIAJ STD) (8-pin)  |

**ORDERING INFORMATION: IS24C256A**

Automotive Range: -40°C to +125°C, Lead-free

| Voltage<br>Range | Part Number     | Package                           |

|------------------|-----------------|-----------------------------------|

| 2.5V             | IS24C256A-3PLA3 | 300-mil Plastic DIP (8-pin)       |

| to 5.5V          | IS24C256A-3GLA3 | Small Outline (JEDEC STD) (8-pin) |

|                  | IS24C256A-3WLA3 | Small Outline (EIAJ STD) (8-pin)  |

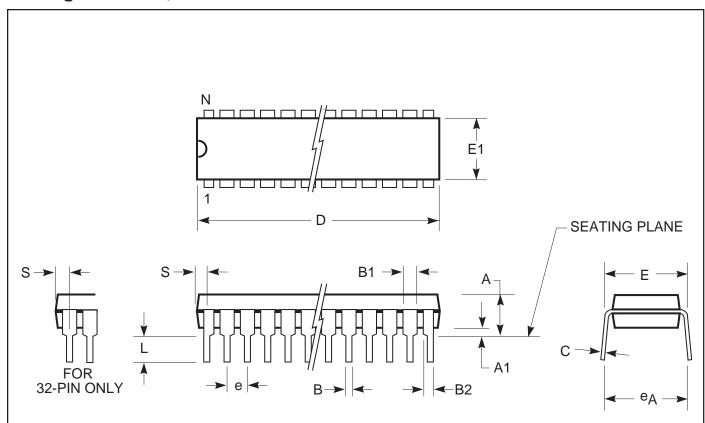

## **PACKAGING INFORMATION**

300-mil Plastic DIP Package Code: N,P

|              | MILLIMETERS |       | INCHES    |       |  |

|--------------|-------------|-------|-----------|-------|--|

| Sym.         | Min.        | Max.  | Min.      | Max.  |  |

| N0.<br>Leads |             | 8     |           |       |  |

| A            | 3.68        | 4.57  | 0.145     | 0.180 |  |

| A1           | 0.38        | _     | 0.015     | _     |  |

| В            | 0.36        | 0.56  | 0.014     | 0.022 |  |

| B1           | 1.14        | 1.52  | 0.045     | 0.060 |  |

| B2           | 0.81        | 1.17  | 0.032     | 0.046 |  |

| С            | 0.20        | 0.33  | 0.008     | 0.013 |  |

| D            | 9.12        | 9.53  | 0.359     | 0.375 |  |

| E            | 7.62        | 8.26  | 0.300     | 0.325 |  |

| E1           | 6.20        | 6.60  | 0.244     | 0.260 |  |

| ед           | 8.13        | 9.65  | 0.320     | 0.380 |  |

| е            | 2.54 BSC    |       | 0.100 BSC |       |  |

| L            | 3.18        |       | 0.125     |       |  |

| S            | 0.64        | 0.762 | 0.025     | 0.030 |  |

#### Notes:

- 1. Controlling dimension: inches, unless otherwise specified.

- 2. BSC = Basic lead spacing between centers.

- Dimensions D and E1 do not include mold flash protrusions and should be measured from the bottom of the package.

- Formed leads shall be planar with respect to one another within 0.004 inches at the seating plane.

Copyright © 2003 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

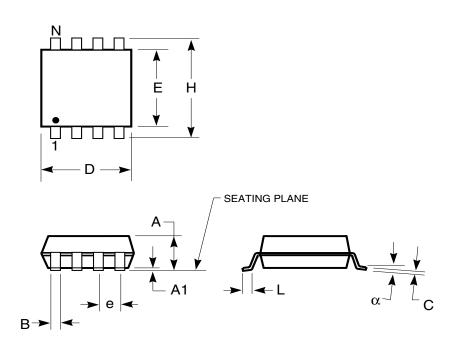

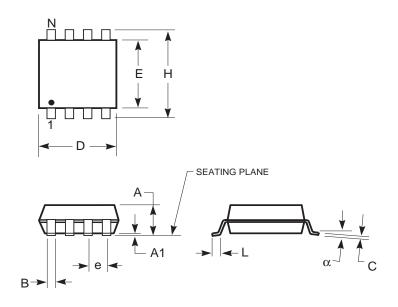

# PACKAGING INFORMATION

150-mil Plastic SOP Package Code: G, GR

| 150-mil Plastic SOP (G, GR) |           |       |         |      |

|-----------------------------|-----------|-------|---------|------|

| Symbol                      | Min       | Max   | Min     | Max  |

| Ref. Std.                   | Inches    |       | mm      |      |

| No. Leads                   | 8         |       | 8       |      |

| Α                           | _         | 0.068 | _       | 1.73 |

| A1                          | 0.004     | 0.009 | 0.1     | 0.23 |

| В                           | 0.013     | 0.020 | 0.33    | 0.51 |

| С                           | 0.007     | 0.010 | 0.18    | 0.25 |

| D                           | 0.189     | 0.197 | 4.8     | 5    |

| Е                           | 0.150     | 0.157 | 3.81    | 3.99 |

| Н                           | 0.228     | 0.245 | 5.79    | 6.22 |

| е                           | 0.050 BSC |       | 1.27 BS | SC   |

| L                           | 0.020     | 0.035 | 0.51    | 0.89 |

#### Notes:

- 1. Controlling dimension: inches, unless otherwise specified.

- 2. BSC = Basic lead spacing between centers.

- Dimensions D and E1 do not include mold flash protrusions and should be measured from the bottom of the package.

- Formed leads shall be planar with respect to one another within 0.004 inches at the seating plane.

# PACKAGING INFORMATION

200-mil Plastic SOP Package Code: W

#### Notes:

- 1. Controlling dimension: mm, unless otherwise specified.

- BSC = Basic lead spacing between centers.

Dimensions D and E1 do not include mold flash protrusions and should be measured from the bottom of the package.

| 200-mil Plastic SOP (W) |           |       |          |      |

|-------------------------|-----------|-------|----------|------|

| Symbol                  | Min       | Max   | Min      | Max  |

| Ref. Std.               | Inches    |       | mm       |      |

| No. Leads               | 8         |       | 8        |      |

| Α                       | _         | 0.085 | _        | 2.16 |

| A1                      | 0.004     | 0.009 | 0.10     | 0.23 |

| В                       | 0.014     | 0.018 | 0.35     | 0.45 |

| С                       | 0.006     | 0.014 | 0.15     | 0.35 |

| D                       | 0.203     | 0.211 | 5.15     | 5.35 |

| Е                       | 0.204     | 0.213 | 5.18     | 5.40 |

| Н                       | 0.303     | 0.325 | 7.70     | 8.26 |

| е                       | 0.050 BSC |       | 1.27 BSC |      |

| L                       | 0.020     | 0.033 | 0.51     | 0.85 |