Version : A.002

Issue Date: 2008/05/12

File Name : SP-DM632-A.002.doc

Total Pages: 25

# 16-CHANNEL CONSTANT CURRENT LED DRIVER WITH PROGRAMMABLE PWM OUTPUTS

#### **DM632**

# 16-CHANNEL CONSTANT CURRENT LED DRIVER WITH PROGRAMMABLE PWM OUTPUTS

#### **General Description**

DM632 is a 16-channel constant current sink LED driver. Each channel has adjustable 16-bits (65536 steps) grayscale PWM control current outputs. It incorporates shift registers, data latches, constant current circuitry with current value set by an external resistor, selectable oscillator source for PWM functioning, and built-in LED open detection circuit to detect error status. It is specifically designed for LED display or lighting applications.

#### **Features**

- Constant-current outputs: 5mA to 90mA adjustable by one external resistor

- 16-bit linear PWM control current outputs for each channel

- Maximum output voltage: 17V

- Maximum clock frequency: 25MHz

- Selectable internal/external PWM reference clock

- PWM free-running capability (refresh rate (~ 275Hz) with internal oscillator (~ 18 MHz))

- Build-in real-time open detection

- Package and pin assignment (except QFN32) compatible to pure LED driver series (ST2221C, DM134/5/6, DM13C)

- Power supply voltage: 3.3V to 5.5V

#### **Applications**

- Indoor/Outdoor LED Video Display

- LED Variable Message Signs (VMS) System

- LED Decorative Lighting

#### **Package Types**

• SOP24, SOP24B, SSOP24, TSSOP24E (with exposed pad), QFN32 (with exposed pad)

#### **Block Diagram**

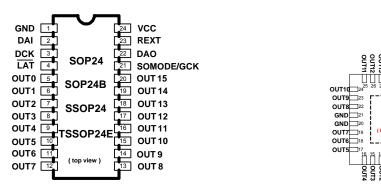

#### **Pin Connection**

**Pin Description**

| PIN No.                                                                                           | PIN NAME       | FUNCTION                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOP24/SOP24B/SSOP24/TSSOP24E: 1<br>TSSOP24E, QFN32: exposed pad<br>QFN32: 1, 2, 5, 6, 7, 8, 20,21 | GND            | Ground terminal.                                                                                                                                                                                                                |

| SOP24/SOP24B/SSOP24/TSSOP24E: 2<br>QFN32: 9                                                       | DAI            | Serial data input terminal.                                                                                                                                                                                                     |

| SOP24/SOP24B/SSOP24/TSSOP24E: 3<br>QFN32: 10                                                      | DCK            | Synchronous clock input terminal for serial data transfer. Data is sampled at the rising edge of DCK.                                                                                                                           |

| SOP24/SOP24B/SSOP24/TSSOP24E: 4<br>QFN32: 11                                                      | LAT            | Input terminal of data strobe:  'H' means data on shift register goes through latch (level trigger),  'L' means data is latched.                                                                                                |

| SOP24/SOP24B/SSOP24/TSSOP24E:<br>5~20<br>QFN32: 12~19, 22~29                                      | OUT0~15        | Sink constant-current outputs (open-drain).                                                                                                                                                                                     |

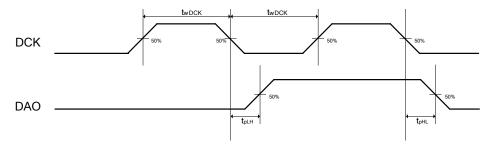

| SOP24/SOP24B/SSOP24/TSSOP24E: 21<br>QFN32: 30                                                     | SOMODE<br>/GCK | Serial Out Mode Selection(SOMODE):  'H': DAO is shifted out and synchronized to falling edge of DCK,  'L': DAO is shifted out and synchronized to rising edge of DCK.  Gray Scale Clock(GCK): Input terminal for PWM operation. |

| SOP24/SOP24B/SSOP24/TSSOP24E: 22<br>QFN32: 31                                                     | DAO            | Serial data output terminal.                                                                                                                                                                                                    |

| SOP24/SOP24B/SSOP24/TSSOP24E: 23<br>QFN32: 32                                                     | REXT           | External resistors connected between REXT and GND for output current value setting.                                                                                                                                             |

| SOP24/SOP24B/SSOP24/TSSOP24E: 24<br>QFN32: 3, 4                                                   | VCC            | Supply voltage terminal.                                                                                                                                                                                                        |

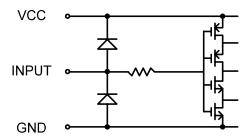

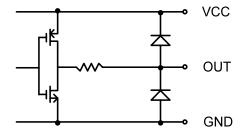

#### **Equivalent Circuit of Inputs and Outputs**

#### 1. DCK, DAI, $\overline{LAT}$ , SOMODE/GCK terminals

#### 2. DAO terminals

#### **PCB Layout Consideration**

To connect an external resistor to REXT pin and ground can determine the maximum output current. If there is any disturbance occurred to REXT pin, the constant current output may be unstable or noisy. Since REXT (pin23), DAO (pin22), and SOMODE/GCK (pin21) are next to each other, the most possible interference is caused by DAO or SOMODE/GCK signal. Accordingly, it is recommended that adding some shielding area within the above pins in PCB layout, or laying the signal line of above pins on different PCB layer will prevent the noise problems effectively.

### **Maximum Ratings** (Ta=25°C, Tj(max) = 150°C)

| CHARACTERISTIC                                  | SYMBOL   | RATING                      | UNIT |  |

|-------------------------------------------------|----------|-----------------------------|------|--|

| Supply Voltage                                  | VCC      | -0.3 ~ 7.0                  | V    |  |

| Input Voltage                                   | VIN      | -0.3 ~ VCC+0.3              | V    |  |

| Output Current                                  | IOUT     | 100                         | mA   |  |

| Output Voltage                                  | VOUT     | -0.3 ~ 17                   | V    |  |

| Input Clock Frequency                           | FDCK     | 25                          | MHz  |  |

| GND Terminal Current                            | IGND     | 1600                        | mA   |  |

|                                                 |          | 4.46 ( QFN32)               |      |  |

|                                                 |          | 4.17 (TSSOP24E exposed pad) |      |  |

| Power Dissipation                               | PD       | 2.45 ( SOP24 )              | W    |  |

| (4 layer PCB, at Ta=25°C)                       |          | 2.19 ( SOP24B )             |      |  |

|                                                 |          | 1.79 ( SSOP24 )             |      |  |

|                                                 |          | 28 ( QFN32 )                |      |  |

|                                                 |          | 30 (TSSOP24E exposed pad)   |      |  |

| Thermal Resistance<br>(4 layer PCB, at Ta=25°ℂ) | Rth(j-a) | 51 (SOP24 )                 | °C/W |  |

| (4 layer FOD, at 1a-25 ()                       |          | 57 (SOP24B )                |      |  |

|                                                 |          | 70 (SSOP24 )                | 1    |  |

| Operating Temperature                           | Тор      | -40 ~ 85                    | °C   |  |

| Storage Temperature                             | Tstg     | -55 <b>~</b> 150            | °C   |  |

|                                                 |          |                             |      |  |

Recommended Operating Condition

| CHARACTERISTIC                | SYMBOL    | CONDITION             | MIN.   | TYP. | MAX.   | UNIT       |

|-------------------------------|-----------|-----------------------|--------|------|--------|------------|

| Supply Voltage                | VCC       | _                     | 3.3    | 5.0  | 5.5    | V          |

| Output Voltage                | VOUT      | Driver On*1           | 1.0    | _    | 0.5VCC | V          |

| Output Voltage                | VOUT      | Driver Off*2          | _      | _    | 17     | V          |

|                               | Ю         | OUTn                  | 5      | _    | 90     |            |

| Output Current                | IOH       | VOH = VCC - 0.4 V     | -0.8   | _    | -2     | mA         |

|                               | IOL       | VOL = 0.2 V           | +0.8   | _    | +2     |            |

| Input Voltage                 | VIH       | VCC = 3.3 V ~ 5.5V    | 0.8VCC | _    | VCC    | V          |

| Input Voltage                 | VIL       | VCC = 3.3 V ~ 5.5V    | 0.0    | _    | 0.2VCC | ] <b>v</b> |

| Input Clock Frequency         | FDCK      | Single Chip Operation | _      | _    | 25     | MHz        |

| Input PWM Frequency           | FGCK      | 3.3V~5.5V             | _      | _    | 25     | IVITIZ     |

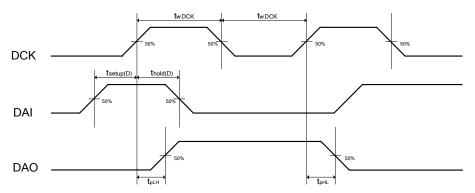

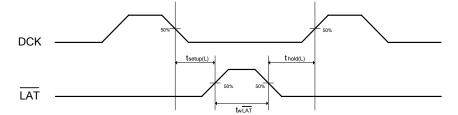

| LAT Pulse Width               | Tw LAT    |                       | 15     | _    |        |            |

| DCK Pulse Width               | Tw DCK    |                       | 15     | _    |        |            |

| Set-up Time for DAI           | tsetup(D) |                       | 10     | _    |        |            |

| Hold Time for DAI             | thold(D)  | VCC = 5.0V            | 10     | _    |        | ns         |

| Set-up Time for LAT           | tsetup(L) |                       | 10     | _    |        |            |

| Hold Time for LAT             | thold(L)  |                       | 10     | _    |        |            |

| Internal Oscillator Frequency | FOSC      |                       | 14.4   | 18   | 21.6   | MHz        |

<sup>\*1</sup> Notice that the power dissipation is limited to its package and ambient temperature.

\*2 The driver output voltage including any overshoot stress has to be compliant with the maximum voltage (17V).

# **Electrical Characteristics** (VCC = 5.0 V, Ta = 25°C unless otherwise noted)

| CHARACTERISTIC                             | SYMBOL                | CONDITION                                                          | MIN.    | TYP.  | MAX.   | UNIT  |

|--------------------------------------------|-----------------------|--------------------------------------------------------------------|---------|-------|--------|-------|

| Input Voltage "H" Level                    | VIH                   | CMOS logic level                                                   | 0.8VCC  |       | VCC    | .,    |

| Input Voltage "L" Level                    | VIL                   | CMOS logic level                                                   | GND     | _     | 0.2VCC | V     |

| Output Leakage Current                     | IOL                   | VOH = 17 V                                                         | _       |       | ±1.0   | uA    |

| Outro 4 ) / =                              | VOL                   | IOL = 1.25 mA                                                      | _       |       | 0.2    | .,    |

| Output Voltage (S-OUT)                     | VOH                   | IOH= 1.2 mA                                                        | VCC-0.4 |       | _      | V     |

| Output Current Skew (Channel-to-Channel)*1 | IOL1                  | VOUT = 1.0 V                                                       | _       | _     | ±3     | %     |

| Output Current Skew (Chip-to-Chip)*2       | IOL2                  | Rrext = 2.2 KΩ                                                     | 25.79   | _     | 29.08  | mA    |

| Output Voltage Regulation                  | % / VOUT              | Rrext = 2.2 KΩ<br>VOUT = 1 V ~ 3 V                                 |         | ±0.1  | ±0.5   | % / V |

| Supply Voltage Regulation                  | % / VCC               | Rrext = 2.2 KΩ                                                     | _       | ±1    | ±4     |       |

| LED Open Detection Threshold               | V(od)                 | all outputs turn on                                                | _       | 0.3   | _      | V     |

|                                            | I <sub>DD</sub> (off) | power on all pins are open unless VCC and GND (fee-running mode)   | _       | 5.39  | 6.5    |       |

|                                            | I <sub>DD(off)</sub>  | power on all pins are open unless VCC and GND (external GCK mode)  |         | 4.57  | _      |       |

| Supply Current*3                           | I <sub>DD(on)</sub>   | input signal is static Rrext = 12.4 $K\Omega$ all outputs turn off | _       | 5.91  | _      | mA    |

|                                            | I <sub>DD(on)</sub>   | input signal is static<br>Rrext = 2.2 KΩ<br>all outputs turn off   | _       | 8.10  | _      |       |

|                                            | I <sub>DD(on)</sub>   | input signal is static  Rrext = $560 \Omega$ all outputs turn off  | _       | 17.11 | _      |       |

\*3 IO excluded.

<sup>\*1</sup> Channel-to-channel skew is defined as the ratio between (any Iout – average Iout) and average Iout, where average Iout = (Imax + Imin) / 2. \*2 Chip-to-Chip skew is defined as the range into which any output current of any IC falls.

# **Electrical Characteristics** (VCC = 3.3 V, Ta = 25°C unless otherwise noted)

| CHARACTERISTIC                             | SYMBOL                | CONDITION                                                          | MIN.    | TYP.  | MAX.       | UNIT  |

|--------------------------------------------|-----------------------|--------------------------------------------------------------------|---------|-------|------------|-------|

| Input Voltage "H" Level                    | VIH                   | CMOS logic level                                                   | 0.8VCC  |       | VCC        |       |

| Input Voltage "L" Level                    | VIL                   | CMOS logic level                                                   | GND     | _     | 0.2VCC     | V     |

| Output Leakage Current                     | IOL                   | VOH = 17 V                                                         | _       |       | ±1.0       | uA    |

| 0.1.17/11(0.01/T)                          | VOL                   | IOL = 1.25 mA                                                      |         |       | 0.2        | .,    |

| Output Voltage (S-OUT)                     | VOH                   | IOH= 1.2 mA                                                        | VCC-0.4 |       |            | - V   |

| Output Current Skew (Channel-to-Channel)*1 | IOL1                  | VOUT = 1.0 V                                                       | _       | _     | ±3         | %     |

| Output Current Skew (Chip-to-Chip)*2       | IOL2                  | Rrext = 2.2 KΩ                                                     | 25.79   | _     | 29.08      | mA    |

| Output Voltage Regulation                  | % / VOUT              | Rrext = 2.2 KΩ<br>VOUT = 1 V ~ 3 V                                 |         | ±0.1  | ±0.5       | % / V |

| Supply Voltage Regulation                  | % / VCC               | Rrext = 2.2 KΩ                                                     | _       | ±1    | <u>±</u> 4 |       |

| LED Open Detection Threshold               | V(od)                 | all outputs turn on                                                | _       | 0.3   | _          | V     |

|                                            | I <sub>DD</sub> (off) | power on all pins are open unless VCC and GND (fee-running mode)   | _       | 3.8   | _          |       |

|                                            | I <sub>DD(off)</sub>  | power on all pins are open unless VCC and GND (external GCK mode)  | _       | 3.39  | _          |       |

| Supply Current*3                           | I <sub>DD(on)</sub>   | input signal is static Rrext = 12.4 $K\Omega$ all outputs turn off | _       | 4.33  | _          | mA    |

|                                            | I <sub>DD(on)</sub>   | input signal is static<br>Rrext = 2.2 KΩ<br>all outputs turn off   | _       | 6.54  | _          |       |

|                                            | I <sub>DD(on)</sub>   | input signal is static  Rrext = $560 \Omega$ all outputs turn off  | _       | 15.10 | _          |       |

\*3 IO excluded.

<sup>\*1</sup> Channel-to-channel skew is defined as the ratio between (any Iout – average Iout) and average Iout, where average Iout = (Imax + Imin) / 2. \*2 Chip-to-Chip skew is defined as the range into which any output current of any IC falls.

# Switching Characteristics (VCC = 5.0V, Ta = 25°C unless otherwise noted)

| CHAR                                 | ACTERISTIC | SYMBOL | CONDITION                 | MIN. | TYP.  | MAX. | UNIT |

|--------------------------------------|------------|--------|---------------------------|------|-------|------|------|

| Propagation Delay                    | GCK-to-OUT |        |                           | _    | 45.74 | _    |      |

| ('L' to 'H')                         | DCK-to-DAO | tpLH   | VIH = VCC                 | _    | 37.16 |      |      |

| Propagation Delay                    | GCK-to-OUT |        |                           |      | 23.76 | _    |      |

| ('H' to 'L')                         | DCK-to-DAO | tpHL   | VIL = GND  Rrext = 2.2 KΩ |      | 27.82 | _    | ns   |

| Output Current Ris                   | se Time    | tor    | VL = 5.0 V                | _    | 18    | _    |      |

| Output Current Fal                   | I Time     | tof    |                           | _    | 6.96  | _    |      |

| Output to output Delay Time Unit     |            | td     | CL = 13 pF                | _    | 33    |      |      |

| Output Current<br>(Propagation Delay |            |        |                           | _    | _     | 4.6  | ms   |

#### **Switching Characteristics** (VCC = 3.3V, Ta = 25°C unless otherwise noted)

| CHAR                                | ACTERISTIC               | SYMBOL | CONDITION      | MIN. | TYP. | MAX. | UNIT |

|-------------------------------------|--------------------------|--------|----------------|------|------|------|------|

| Propagation Delay                   | GCK-to-OUT               |        |                | _    | 48.8 | _    |      |

| ('L' to 'H')                        | DCK-to-DAO               | tpLH   | VIH = VCC      | _    | 21.2 | _    |      |

| Propagation Delay                   | GCK-to-OUT               |        | VIL = GND      |      | 29.6 | _    |      |

| ('H' to 'L')                        | DCK-to-DAO               | tpHL   | Rrext = 2.2 KΩ | _    | 17.6 |      | ns   |

| Output Current Ris                  | se Time                  | tor    | VL = 3.3 V     | _    | 20   | _    |      |

| Output Current Fa                   | Output Current Fall Time |        | CL = 13 pF     | _    | 8.25 | _    |      |

| Output to output Delay Time Unit    |                          | td     | 0L 10 pi       |      | 34   |      |      |

| Output Current<br>(Propagation Dela |                          |        |                | _    |      | 4.6  | ms   |

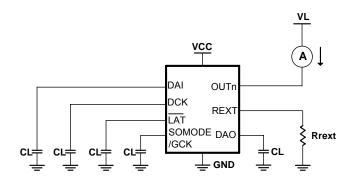

Switching Characteristics Test Circuit

-

<sup>\*1</sup> Reload the new PWM data at the end of the last PWM frame.

#### **Constant-Current Output**

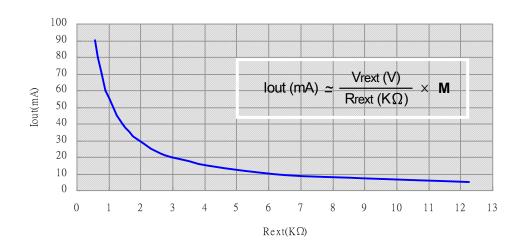

Constant-current value (Iout\*1)of each output channel is set by an external resistor connected between the REXT pin and GND. The current scale ranging can be adjusted from 5mA to 90mA by varying the resistor value. The reference voltage of REXT terminal (Vrext) is approximately 1.23V. The output current value is calculated by the following equation:

| lout(mA) | 5     | 10    | 20    | 30    | 40    | 50    | 60    | 70    | 80    | 90    |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| M        | 50.86 | 48.60 | 48.39 | 47.66 | 46.97 | 46.13 | 44.74 | 43.94 | 43.20 | 42.24 |

#### Output Current as a Functiono Rext value

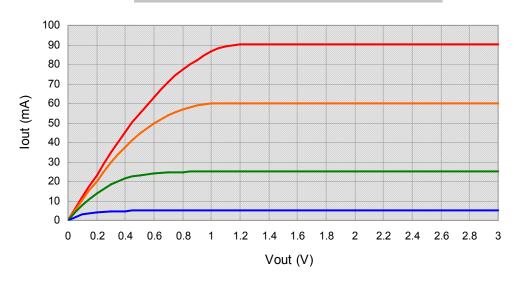

#### Output Current as a Function of Output Voltage

In order to obtain a good performance of constant-current output, a suitable output voltage is necessary. Users can get related information about the minimum output voltage above.

<sup>\*1</sup> Iout is typical current value setting under 100% PWM duty cycle.

#### **Serial Data Interface**

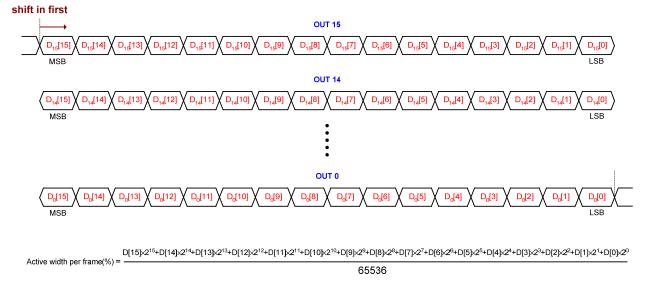

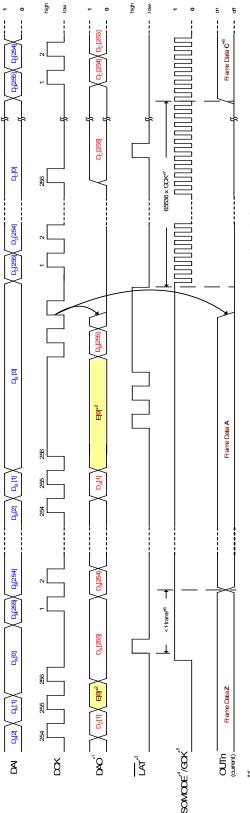

The serial-in data (DAI) will be clocked into  $16 \times 16$  bit shift registers synchronized on the rising edge of the clock (DCK). The data will be transferred into the  $16 \times 16$  bit latch registers when the strobe signal ( $\overline{LAT}$ ) is kept at high level (level trigger); otherwise, the data will be held. The latch pulse should be sent after the falling edge of the last clock within a frame data. The trigger timing of the serial-out data (DAO) will be shifted out on synchronization to the rising edge of the clock if serial out selection (SOMODE) is kept at low level. And if serial out selection (SOMODE) is kept at high level, the serial-out data (DAO) will be shifted out on synchronization to the falling edge of the clock (DCK).

#### **Input Data Format**

# **LED Open Detection**

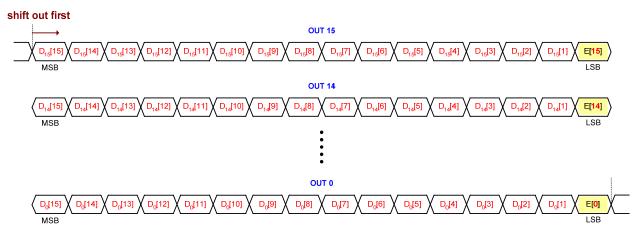

DM632 provides a real time monitor of LED open detection function without extra components or circuit design. It will be identified as a LED open failure when the output is turned on but the output voltage is below 0.3V. The test result of each channel will write to its correspondent shift register which is in LSB position ( $D_{15}[0]$ ,  $D_{14}[0]$ , ....,  $D_{0}[0]$ ) while strobe signal is active. User can refer to timing diagram on page13. Detecting report could be retrieved from serial-out (DAO) data. If the system reads '1' back, that indicates LED is in normal status. But if '0' was retrieved then LED open failure has occurred. In order to make sure LED open detection function is in well operating condition, it is recommended that all the luminance data are wrote to '1' then almost turning on the outputs during detection process.

#### **Serial-out Data Format**

\*E[15], E[14], ..., E[0] are Error Message of LED Open Detection. '1' is normal, and '0' is abnormal.

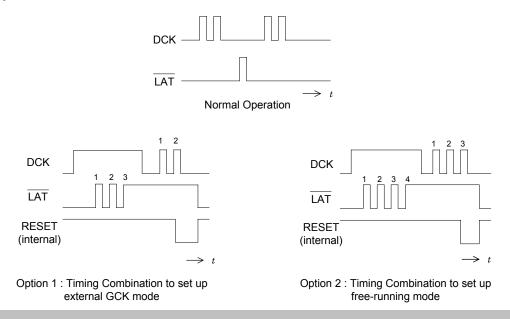

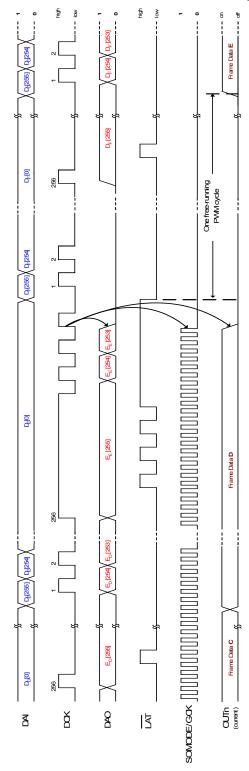

#### **Selection of Internal/External PWM Frequency**

The default operation mode is the **free-running** PWM signal generated by internal oscillator after power-on. Users could switch internal to external PWM frequency source by following timing sequence. There are two alternative options could be selected. The option 1 shows three rising edge of latch pulses ( $\overline{LAT}$ ) when the clock (DCK) kept at high level then two rising edge of clock (DCK) pulses when the latch pulse ( $\overline{LAT}$ ) kept at high level. Then the SOMODE/GCK pin could input external frequency to operate PWM function. The option 2 shows four rising edge of latch pulses( $\overline{LAT}$ ) when clock(DCK) kept at high level then sending three rising edge of clock (DCK) signal, while latch( $\overline{LAT}$ ) signal kept high level at the same time. Meanwhile the GCK external mode can be set back to the free-running mode. Notice that when internal RESET at low level, all the shift registers in DM632 will be cleared (Kept at Low level) and all output current will be off immediately.

## **Timing Diagram**

1. DCK-DAI, DAO (SOMODE = "L" at free-running mode, or external GCK mode)

2. DCK, DAO (SOMODE = "H" at free-running mode)

#### 3. DCK-LAT

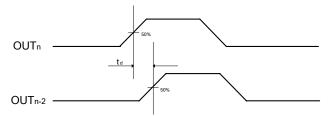

4. Output to Output Delay Time Unit (n=2,3,4,5,6,7, 10, 11, 12, 13, 14, 15)

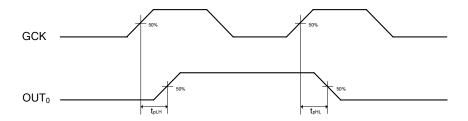

#### 5. GCK-OUT<sub>0</sub>

#### Timing Diagram (free-running mode switch to external GCK mode)

Ţ <sup>1</sup> DAO is shifted out on synchronization to rising / falling edge of DCK according to SOMODE is

$^2$  E[0] is the error message of LED open detection.

$^{*3}$  <u>LAT</u> is level trigger, not edge trigger.

\*4 SOMODE function work in free-running mode.

<sup>5</sup> While switching to external GCK mode, all registers in DM632 will be reset simultaneously.

Starting the new PWM frame after the last PWM period finish completely.

7 While switching to external GCK mode, outputs will be active after 65536 GCK pulse.

<sup>3</sup> When using external frequency for PWM operation, the PWM refresh rate (frame rate) can be calculated by following equation:

Input GCK Frequency (Hz)

Refresh Rate (Hz) = \_\_\_\_\_\_\_

Total PWM resolution ( 2<sup>16</sup> )

For example, if the refresh rate in display system is higher than 60Hz, the input GCK frequency must be higher than 4MHz.

# Timing Diagram (external GCK mode switch to free-running mode)

#### **Output Modulation Technique**

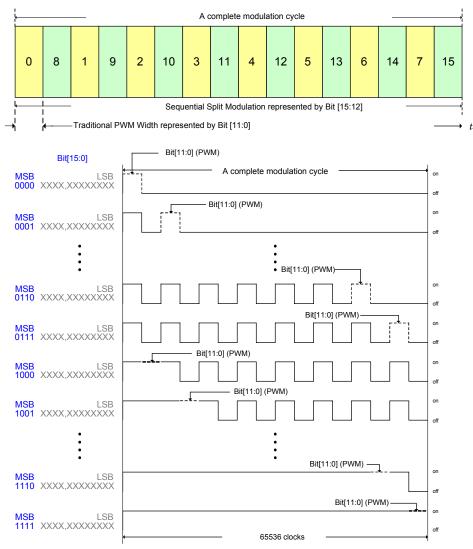

DM632 provides a new LED drive technique of output modulation. It mixes traditional Pulse Width Modulation (PWM) represented by LSB 12 bit with Sequential Split Modulation (SSM) represented by MSB 4 bit. The main benefits of SSM are to drive LED with an equivalent higher refresh rate (up to 380Hzn in DM632 when  $F_{GCK} = 25 MHz$ ) and change bit to next bit smoothly. The relationships between PWM and SSM in time domain can be refer to the diagram (not to scale) below:

# **Ultra High Resolution Current Outputs**

DM632 could provide 16-bit linear PWM control current outputs for each channel. There are two advantages for system design. One is DM632 has sufficient bit resolution (65536 steps), not only LED color information but additional data such as global brightness, dot correction, and gamma correction can be represented by the proper algorithms. The other is to reduce a lot of clock and data rate compared to conventional ON-OFF type LED drivers.

#### **Global Brightness Control**

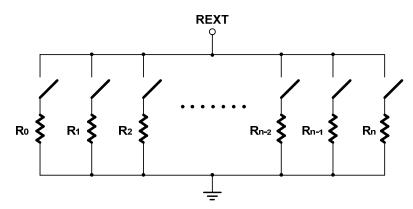

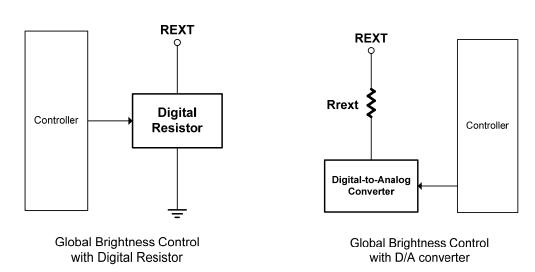

DM632 has no built-in global brightness control feature. In order to obtain a lower resolution of global brightness control effect, two methods could be utilized. Here show different ways to adjust the Rrext value or voltage drop across the external resistor. Please see the reference circuit below:

Global Brightness Control with Resistor Ladder

# **Output to Output Delay**

DM632 has build-in output to output delay with a special arrangement. This arrangement help chip avoid noise cause by large current during channels switching. The arrangement details are shown as following table.

| Channel     | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|-------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| Delay units | 0 | 4 | 1 | 5 | 2 | 6 | 3 | 7 | 3 | 7 | 2  | 6  | 1  | 5  | 0  | 4  |

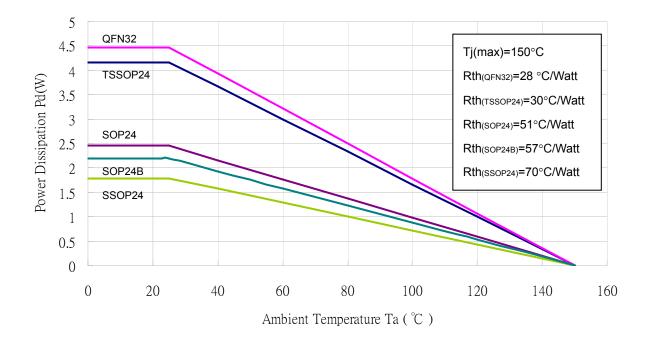

#### **Power Dissipation**

The power dissipation of a semiconductor chip is limited to its package and ambient temperature, in which the device requires the maximum output current calculated for given operating conditions. The maximum allowable power consumption can be calculated by the following equation:

$$Pd(max)(Watt) = \frac{Tj(junction\ temperature)(max)(\ ^{\circ}C) - Ta(ambient\ temperature)(\ ^{\circ}C)}{Rth(junction-to-air\ thermal\ resistance)(\ ^{\circ}C/Watt)}$$

The relationship between power dissipation and operating temperature can be refer to the figure below:

The power consumption of IC can be determined by the following equation and should be less than the maximum allowable power dissipation:

$$Pd(W) = Vcc(V) \times I_{DD}(A) + Vout0 \times Iout0 \times Duty0 + \cdots + Vout15 \times Iout15 \times Duty15 \le Pd(max)(W)$$

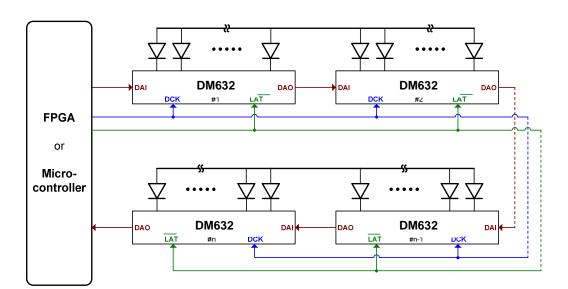

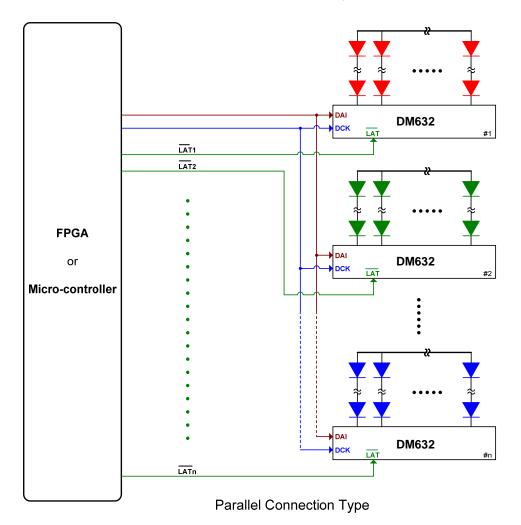

# **Typical Application**

Serial Connection Type

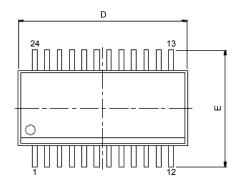

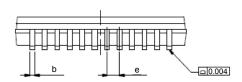

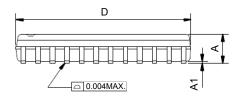

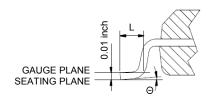

#### DM632-SSOP

|         | DIMENSIO          | NS IN INCH | DIMENSIC  | NS IN MM |  |

|---------|-------------------|------------|-----------|----------|--|

| SYMBOLS | MIN.              | MAX.       | MIN.      | MAX.     |  |

| Α       | 0.053             | 0.069      | 1.346     | 1.753    |  |

| A1      | 0.004             | 0.010      | 0.102     | 0.254    |  |

| A2      | -                 | 0.059      | -         | 1.499    |  |

| b       | 0.008 0.012 0.203 |            | 0.203     | 0.305    |  |

| С       | 0.007             | 0.010      | 0.178     | 0.254    |  |

| D       | 0.337             | 0.344      | 8.560     | 8.738    |  |

| E       | 0.228             | 0.244      | 5.791     | 6.198    |  |

| E1      | 0.150             | 0.157      | 3.810     | 3.988    |  |

| е       | 0.025             | BSC.       | 0.635     | BSC      |  |

| L       | 0.016             | 0.050      | 0.406     | 1.270    |  |

| L1      | 0.041             | BSC        | 1.041 BSC |          |  |

| Θ       | 0°                | 8°         | 0°        | 8°       |  |

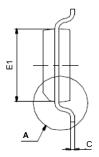

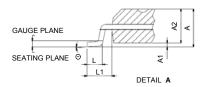

#### DM632-SOPB

|         | DIMENSIO | NS IN INCH | DIMENSIC | ONS IN MM |

|---------|----------|------------|----------|-----------|

| SYMBOLS | MIN.     | MAX.       | MIN.     | MAX.      |

| Α       | -        | 0.075      | -        | 1.900     |

| A1      | 0.002    | 0.008      | 0.050    | 0.200     |

| A2      | 0.051    | 0.067      | 1.300    | 1.700     |

| b       | 0.012    | 0.020      | 0.300    | 0.500     |

| С       | 0.004    | 0.010      | 0.100    | 0.250     |

| D       | 0.504    | 0.520      | 12.800   | 13.200    |

| E       | 0.303    | 0.327      | 7.700    | 8.300     |

| е       | 0.0394   | 4 BSC      | 1.000    | BSC       |

| E1      | 0.228    | 0.244      | 5.800    | 6.200     |

| L       | 0.010    | 0.026      | 0.250    | 0.650     |

| θ       | 0°       | 10°        | 0°       | 10°       |

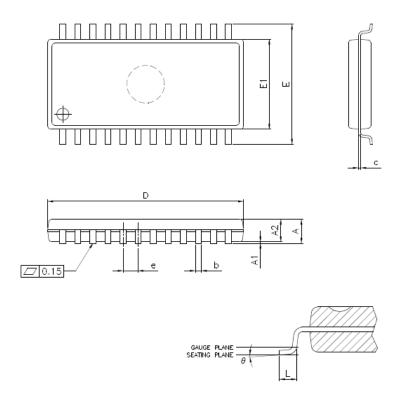

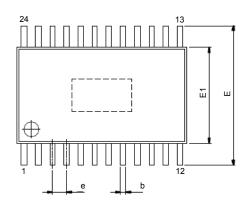

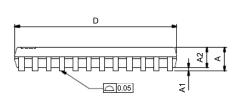

#### DM632-SOP

|         | DIMENSIO | NS IN INCH | DIMENSIC  | NS IN MM |  |

|---------|----------|------------|-----------|----------|--|

| SYMBOLS | MIN.     | MAX.       | MIN.      | MAX.     |  |

| Α       | -        | 0.104      | 1         | 2.642    |  |

| A1      | 0.004    | -          | 0.102     | 1        |  |

| b       | 0.016    | BSC        | 0.406 BSC |          |  |

| D       | 0.612    | 0.624      | 15.545    | 15.850   |  |

| Е       | 0.292    | 0.299      | 7.417     | 7.595    |  |

| е       | 0.050    | BSC        | 1.270 BSC |          |  |

| Н       | 0.405    | 0.419      | 10.287    | 10.643   |  |

| L       | 0.021    | 0.041      | 0.533     | 1.041    |  |

| Θ       | 0°       | 8°         | 0°        | 8°       |  |

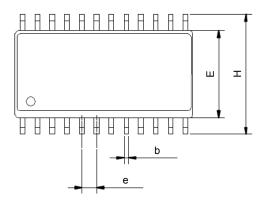

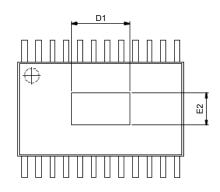

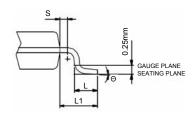

#### DM632-TSSOP (exposed pad)

|         | DIMENSIONS IN INCH |        | DIMENSIONS IN MM |       |

|---------|--------------------|--------|------------------|-------|

| SYMBOLS | MIN.               | MAX.   | MIN.             | MAX.  |

| Α       | -                  | 0.047  | 1                | 1.20  |

| A1      | 0.000              | 0.006  | 0.00             | 0.15  |

| A2      | 0.031              | 0.041  | 0.80             | 1.05  |

| b       | 0.007              | 0.012  | 0.19             | 0.30  |

| D       | 0.303              | 0.311  | 7.70             | 7.90  |

| E1      | 0.169              | 0.177  | 4.30             | 4.50  |

| Е       | 0.252 BSC          |        | 6.400 BSC        |       |

| е       | 0.026 BSC          |        | 0.650 BSC        |       |

| L1      | 0.039 REF          |        | 1.000 REF.       |       |

| L       | 0.018              | 0.030  | 0.45             | 0.75  |

| S       | 0.008              | -      | 0.20             | -     |

| Θ       | 0°                 | 8°     | 0°               | 8°    |

| E2      | 0.0898             | 0.1122 | 2.280            | 2.850 |

| D1      | 0.146              | 1.819  | 3.700            | 4.620 |

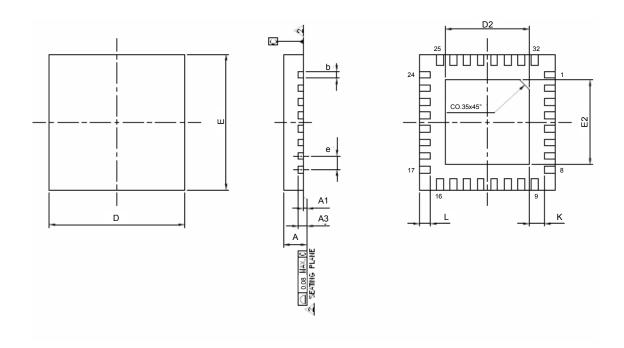

# **Package Outline Dimension**

#### DM632-QFN (exposed pad)

|         | DIMENSIONS IN INCH |       | DIMENSIONS IN MM |       |

|---------|--------------------|-------|------------------|-------|

| SYMBOLS | MIN.               | MAX.  | MIN.             | MAX.  |

| Α       | 0.028              | 0.031 | 0.70             | 0.80  |

| A1      | 0                  | 0.002 | 0                | 0.05  |

| A3      | 0.008 REF.         |       | 0.203 REF.       |       |

| b       | 0.007              | 0.012 | 0.180            | 0.300 |

| D       | 0.193              | 0.201 | 4.900            | 5.100 |

| E       | 0.193              | 0.201 | 4.900            | 5.100 |

| е       | 0.0197 BSC         |       | 0.500 BSC        |       |

| L       | 0.012              | 0.020 | 0.30             | 0.50  |

| K       | 0.0079             | -     | 0.2              | -     |

| D2      | 0.049              | 0.128 | 1.25             | 3.25  |

| E2      | 0.049              | 0.128 | 1.25             | 3.25  |

Note: 1.DIMENSIONING AND TOLERANCING CONFORM TO ASME Y145.5M-1994.

2. REFER TO JEDEC STD. MO-220 WHHD-2 ISSUE A

The products listed herein are designed for ordinary electronic applications, such as electrical appliances, audio-visual equipment, communications devices and so on. Hence, it is advisable that the devices should not be used in medical instruments, surgical implants, aerospace machinery, nuclear power control systems, disaster/crime-prevention equipment and the like. Misusing those products may directly or indirectly endanger human life, or cause injury and property loss.

Silicon Touch Technology, Inc. will not take any responsibilities regarding the misusage of the products mentioned above. Anyone who purchases any products described herein with the above-mentioned intention or with such misused applications should accept full responsibility and indemnify. Silicon Touch Technology, Inc. and its distributors and all their officers and employees shall defend jointly and severally against any and all claims and litigation and all damages, cost and expenses associated with such intention and manipulation.