# **VOICE COIL MOTOR DRIVER FOR CAMERA AUTO FOCUS**

Check for Samples: DRV201

#### **FEATURES**

- Configurable for Linear or PWM Mode VCM Current Generation

- High Efficiency PWM Current Control for VCM

- Advanced Ringing Compensation

- Integrated 10-bit D/A Converter for VCM Current Control

- Protection

- Open and Short-Circuit Detection on VCM Pins

- Undervoltage Lockout (UVLO)

- Thermal Shutdown

- Open and Short Circuit Protection on VCM Output

- Internal Current Limit for VCM Driver

- I<sup>2</sup>C Interface

- Operating Temperature Range: -40°C to 85°C

- 6-Ball WCSP Package With 0.4-mm Pitch

- Max Die Size: 0.8 mm x 1.48 mm

- Package Height: 0.15 mm

### **APPLICATIONS**

- Cell Phone Auto Focus

- Digital Still Camera Auto Focus

- Iris/Exposure Control

- Security Cameras

- Web and PC Cameras

- Actuator Controls

#### DESCRIPTION

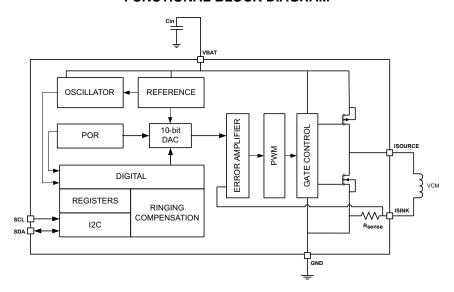

The DRV201 is an advanced voice coil motor driver for camera auto focus. It has an integrated D/A converter for setting the VCM current. VCM current is controlled with a fixed frequency PWM controller or a linear mode driver. Current generation can be selected via I<sup>2</sup>C register. The DRV201 has an integrated sense resistor for current regulation and the current can be controlled through I<sup>2</sup>C.

When changing the current in the VCM, the lens ringing is compensated with an advanced ringing compensation function. Ringing compensation reduces the needed time for auto focus significantly. The device also has VCM short and open protection functions.

### **FUNCTIONAL BLOCK DIAGRAM**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLVSB25 - AUGUST 2011

**STRUMENTS**

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> | ORDERABLE PART NUMBER |

|----------------|------------------------|-----------------------|

| -40°C to 85°C  | YFM                    | DRV201YFMR            |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- (2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

#### **DEVICE INFORMATION**

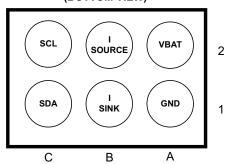

# NanoFree PACKAGE (BOTTOM VIEW)

#### **TERMINAL FUNCTIONS**

| TERMI    | NAL | 1/0 | DESCRIPTION                                                      |  |  |  |

|----------|-----|-----|------------------------------------------------------------------|--|--|--|

| NAME     | NO. | I/O | DESCRIPTION                                                      |  |  |  |

| VBAT     | 2A  |     | Power                                                            |  |  |  |

| GND      | 1A  |     | Ground                                                           |  |  |  |

| I_SOURCE | 2B  |     | Voice coil positive terminal                                     |  |  |  |

| I_SINK   | 1B  |     | Voice coil negative terminal                                     |  |  |  |

| SCL      | 2C  | I   | I <sup>2</sup> C serial interface clock input                    |  |  |  |

| SDA      | 1C  | I/O | 1 <sup>2</sup> C serial interface data input/output (open drain) |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                                       |                            | VALUE      | UNIT |

|------------------|-------------------------------------------------------|----------------------------|------------|------|

|                  | VBAT, ISOURCE, ISOURCE pin voltage range (2)          | -0.3 to 5.5                | V          |      |

|                  | Voltage range at SDA, SCL                             | -0.3 to 3.6                | V          |      |

|                  | Continuous total power dissipation                    | Internally limited         |            |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance <sup>(3)</sup> | 130                        | °C/W       |      |

| T <sub>J</sub>   | Operating junction temperature                        |                            | -40 to 125 | °C   |

| T <sub>A</sub>   | Operating ambient temperature                         |                            | -40 to 85  | °C   |

| T <sub>stg</sub> | Storage temperature                                   |                            | -55 to 150 | °C   |

|                  | ESD rating                                            | (HBM) Human body model     | ±4000      | V    |

|                  |                                                       | (CDM) Charged device model | ±500       | V    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

Over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

|                       | PARAMETER                                                       | TEST CONDITIONS               | MIN | TYP   | MAX | UNIT        |

|-----------------------|-----------------------------------------------------------------|-------------------------------|-----|-------|-----|-------------|

| INPUT VOL             | TAGE                                                            |                               |     |       |     |             |

| $V_{BAT}$             | Input supply voltage                                            |                               | 2.5 | 3.7   | 4.8 | V           |

|                       | Hadamaka na la danak danak alah                                 | V <sub>BAT</sub> rising       |     |       | 2.2 | .,          |

| $V_{UVLO}$            | Undervoltage lockout threshold                                  | V <sub>BAT</sub> falling      | 2   |       |     | V           |

| V <sub>HYS</sub>      | Undervoltage lockout hysteresis                                 |                               | 50  | 100   | 250 | mV          |

| INPUT CUE             | RRENT                                                           |                               |     |       |     |             |

| I <sub>SHUTDOWN</sub> | Input supply current shutdown, includes switch leakage currents | MAX: V <sub>BAT</sub> = 4.4 V |     | 0.15  | 1   | μΑ          |

| I <sub>STANDBY</sub>  | Input supply current standby, includes switch leakage currents  | MAX: V <sub>BAT</sub> = 4.4 V |     | 120   | 200 | μΑ          |

| STARTUP,              | MODE TRANSITIONS, AND SHUTDOW                                   | 'N                            |     |       |     |             |

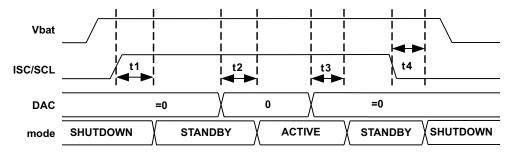

| t <sub>1</sub>        | Shutdown to standby                                             |                               |     |       | 100 | μs          |

| t <sub>2</sub>        | Standby to active                                               |                               |     |       | 100 | μs          |

| t <sub>3</sub>        | Active to standby                                               |                               |     |       | 100 | μs          |

| $t_4$                 | Shutdown time                                                   | Active or standby to shutdown | 0.5 |       | 1   | ms          |

| VCM DRIV              | ER STAGE                                                        |                               |     |       |     |             |

|                       | Resolution                                                      |                               |     | 10    |     | bits        |

| I <sub>RES</sub>      | Relative accuracy                                               |                               | -10 |       | 10  | LSB         |

|                       | Differential nonlinearity                                       |                               | -1  |       | 1   | LOD         |

|                       | Zero code error                                                 |                               |     | 0     |     | mA          |

|                       | Offset error                                                    | At code 32                    |     |       | 3   | mA          |

|                       | Gain error                                                      |                               |     | ±3    |     | % of<br>FSR |

|                       | Gain error drift                                                |                               |     | 0.3   | 0.4 | %/°C        |

|                       | Offset error drift                                              |                               |     | 0.3   | 0.5 | %/°C        |

| I <sub>MAX</sub>      | Maximum output current                                          |                               |     | 102.3 |     | mA          |

| I <sub>LIMIT</sub>    | Average VCM current limit                                       | See (1)                       | 110 | 160   | 240 | mA          |

<sup>(1)</sup> During short circuit condition driver current limit comparator will trip and short is detected and driver goes into STANDBY and short flag is set high in the status register.

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(3)</sup> This thermal data is measured with high-K board (4-layer board).

SLVSB25 - AUGUST 2011 www.ti.com

### **ELECTRICAL CHARACTERISTICS (continued)**

Over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

|                      | PARAMETER                                     | TEST CONDITIONS                     | MIN  | TYP                | MAX  | UNIT |

|----------------------|-----------------------------------------------|-------------------------------------|------|--------------------|------|------|

| I <sub>DETCODE</sub> | Minimum VCM code for OPEN and SHORT detection | See (2)                             | 256  |                    |      | mA   |

| f <sub>SW</sub>      | Switching frequency                           | Selectable through CONTROL register | 0.5  |                    | 4    | MHz  |

| $V_{DRP}$            | Internal dropout                              | See (3)                             |      |                    | 0.4  | V    |

| L <sub>VCM</sub>     | VCM inductance                                |                                     | 30   |                    | 150  | μH   |

| R <sub>VCM</sub>     | VCM resistance                                |                                     | 11   |                    | 22   | Ω    |

| LENS MO              | VEMENT CONTROL                                |                                     |      |                    |      |      |

| t <sub>set1</sub>    | Lens settling time                            | ±10% error band                     |      | 2/f <sub>VCM</sub> |      | ms   |

| t <sub>set2</sub>    | Lens settling time                            | ±10% error band                     |      | 1/f <sub>VCM</sub> |      | ms   |

| ,                    | VCM resonance frequency                       |                                     | 50   |                    | 150  | Hz   |

| f <sub>VCM</sub>     | VCM resonance frequency tolerance             |                                     | -20  |                    | 20   | %    |

| LOGIC I/O            | s (SDA AND SCL)                               |                                     |      |                    |      |      |

|                      | land last and a second                        | V = 3.6 V, SCL                      | -20  |                    | 20   |      |

| I <sub>IN</sub>      | Input leakage current                         | V = 3.6 V, SDA                      | -1   |                    | 1    | μΑ   |

| R <sub>PullUp</sub>  | I <sup>2</sup> C pull-up resistors            | SDA and SCL pins                    |      | 4.7                |      | kΩ   |

| V <sub>IH</sub>      | Input high level                              | See (4)                             | 1.17 |                    | 3.6  | V    |

| V <sub>IL</sub>      | Input low level                               | See (5)                             | 0    |                    | 0.63 | V    |

| t <sub>TIMEOUT</sub> | SCL timeout for shutdown detection            |                                     | 0.5  |                    | 1    | ms   |

| R <sub>PD</sub>      | Pull down resistor at SCL line                |                                     |      | 500                |      | kΩ   |

| f <sub>SCL</sub>     | I <sup>2</sup> C clock frequency              |                                     |      |                    | 400  | kHz  |

|                      | OSCILLATOR                                    |                                     |      |                    |      |      |

| fosc                 | Internal oscillator                           | 20°C ≤ T <sub>A</sub> ≤ 70°C        | -3   |                    | 3    | %    |

|                      | Frequency accuracy                            | -40°C ≤ T <sub>A</sub> ≤ 85°C       | -5   |                    | 5    | %    |

| THERMAL              | SHUTDOWN                                      | <u>'</u>                            |      |                    |      |      |

| T <sub>TRIP</sub>    | Thermal shutdown trip point                   |                                     |      | 140                |      | °C   |

|                      | 2 2                                           |                                     |      |                    |      |      |

When testing VCM open or short this is the recommended minimum VCM code (in dec) to be used.

This is the voltage that is needed for the feedback resistor and high side driver. It should be noted that the maximum VCM resistance is limited by this voltage and supply voltage. E.g. 3-V supply maximum VCM resistance is:  $R_{VCM} = (V_{BAT} - V_{DRP})/I_{VCM} = (3 \text{ V} - 0.4 \text{ V})/I_{VCM} = (3 \text{ V} - 0.4 \text{ V}$  $V)/102.3 \text{ mA} = 25.4 \Omega.$

<sup>(4)</sup> During shutdown to standby transition V<sub>IH</sub> low limit is 1.28 V.

(5) During shutdown to standby transition V<sub>IL</sub> low limit is 0.51 V.

#### FUNCTIONAL DESCRIPTION

The DRV201 is intended for high performance autofocus in camera modules. It is used to control the current in the voice coil motor (VCM). The current in the VCM generates a magnetic field which forces the lens stack connected to a spring to move. The VCM current and thus the lens position can be controlled via the I<sup>2</sup>C interface and an auto focus function can be implemented.

The device connects to a video processor or image sensor through a standard I<sup>2</sup>C interface which supports up to 400-kbit/s data rate. The digital interface supports IO levels from 1.8 V to 3.3 V. All pins have 4-kV HBM ESD rating.

When SCL is low for at least 0.5 ms, the device enters SHUTDOWN mode. If SCL goes from low to high the driver enters STANDBY mode in less than 100 µs and default register values are set as shown in Figure 1. ACTIVE mode is entered when ever the VCM\_CURRENT register is set to something else than zero.

Figure 1. Power Up and Down Sequence

VCM current can be controlled via an I<sup>2</sup>C interface and VCM\_CURRENT registers. Lens stack is connected to a spring which causes a dampened ringing in the lens position when current is changed. This mechanical ringing is compensated internally by generating an optimized ramp when ever the current value in the VCM\_CURRENT register is changed. This enables a fast autofocus algorithm and pleasant user experience.

Current in the VCM can be generated with a linear or PWM control. In linear mode the high side PMOS is configured as a current source and current is set by the VCM\_CURRENT control register. In PWM control the VCM is driven with a half bridge driver. With PWM control the VCM current is increased by connecting the VCM between V<sub>BAT</sub> and GND through the high side PMOS and then released to a 'freewheeling' mode through the sense resistor and low side NMOS. PWM mode switching frequency can be selected from 0.5 MHz up to 4 MHz through a CONTROL register. PWM or linear mode can be selected with the PWM/LIN bit in the MODE register.

SLVSB25 – AUGUST 2011 www.ti.com

#### MODES OF OPERATION

#### **SHUTDOWN**

If the driver detects SCL has a DC level below 0.63 V for duration of at least 0.5 ms, the driver will enter shutdown mode. This is the lowest power mode of operation. The driver will remain in shutdown for as long as SCL pin remain low.

#### **STANDBY**

If SCL goes from low to high the driver enters STANDBY mode and sets the default register values. In this mode registers can be written to through the I<sup>2</sup>C interface. Device will be in STANDBY mode when VCM\_CURRENT register is set to zero. From ACTIVE mode the device will enter STANDBY if the SW\_RST bit of the CONTROL register is set. In this case all registers will be reset to default values.

STANDBY mode is entered from ACTIVE mode if any of the following faults occur: Over temperature protection fault (OTPF), VCM short (VCMS), or VCM open (VCMO). When STANDBY mode is entered due to a fault condition current register is cleared.

#### **ACTIVE**

The device is in ACTIVE mode whenever the VCM\_CURRENT control is set to something else than zero through the I<sup>2</sup>C interface. In ACTIVE mode VCM driver output stage is enabled all the time resulting in higher power consumption. The device remains in active mode until the SW\_RST bit in the CONTROL register is set, SCL is pulled low for duration of 0.5 ms, VCM\_CURRENT control is set to zero, or any of the following faults occur: Over temperature protection fault (OTPF), VCM short (VCMS), or VCM open (VCMO). If active mode is entered after fault the status register is automatically cleared.

#### VCM DRIVER OUTPUT STAGE OPERATION

Current in the VCM can be controlled with a linear or PWM mode output stage. Output stage is enabled in ACTIVE mode which can be controlled through VCM\_CURRENT control register and the output stage mode is selected from MODE register bit PWM/LIN.

In linear mode the output PMOS is configured to a high side current source and current can be controlled from a VCM\_CURRENT registers.

In PWM control the VCM is driven with a half bridge driver. With PWM control the VCM current is increased by connecting the VCM between  $V_{BAT}$  and GND through the high side PMOS and then released to a 'freewheeling' mode through the sense resistor and low side NMOS. Current in the VCM is sensed with a 1- $\Omega$  sense resistor which is connected into an error amplifier input where the other input is controlled by the 10-bit DAC output. PWM mode switching frequency can be selected from 0.5 MHz up to 4 MHz through a CONTROL register. PWM or linear mode can be selected with the PWM/LIN bit in the MODE register.

#### RINGING COMPENSATION

VCM current can be controlled via an I<sup>2</sup>C interface and VCM\_CURRENT registers. Lens stack is connected to a spring which causes a dampened ringing in the lens position when current is changed. This mechanical ringing is compensated internally by generating an optimized ramp when ever the current value in the VCM\_CURRENT register is changed. This enables a fast auto focus algorithm and pleasant user experience.

Ringing compensation is dependent on the VCM resonance frequency and this can be controlled via VCM\_FREQ register from 50 Hz up 152 Hz with 0.4-Hz steps. Ringing compensation is designed in a way that it can tolerate ±20% frequency variation in the VCM resonance frequency so only statistical data from the VCM is needed in production.

#### I<sup>2</sup>C BUS OPERATION

The DRV201 hosts a slave I<sup>2</sup>C interface that supports data rates up to 400 kbit/s and auto-increment addressing and is compliant to I<sup>2</sup>C standard 3.0.

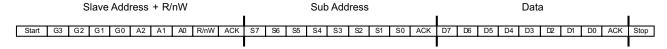

Figure 2. Subaddress in I<sup>2</sup>C Transmission

Start - Start condition

G(3:0) - Group ID: Address fixed at '0001'

A(2:0) - Device Address: Address fixed at '110'

R/nW - Read/not Write select bit

ACK - Acknowledge

S(7:0) – Subaddress: Defined per register map

D(7:0) - Data: Data to be loaded into the device

Stop – Stop condition

The I<sup>2</sup>C Bus is a communications link between a controller and a series of slave terminals. The link is established using a two-wire bus consisting of a serial clock signal (SCL) and a serial data signal (SDA). The serial clock is sourced from the controller in all cases where the serial data line is bi-directional for data communication between the controller and the slave terminals. Each device has an open drain output to transmit data on the serial data line. An external pull-up resistor must be placed on the serial data line to pull the drain output high during data transmission.

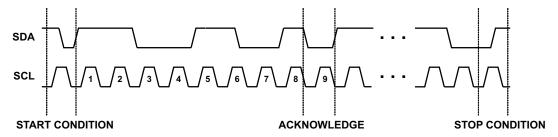

Data transmission is initiated with a start bit from the controller as shown in Figure 3. The start condition is recognized when the SDA line transitions from high to low during the high portion of the SCL signal. Upon reception of a start bit, the device will receive serial data on the SDA input and check for valid address and control information. If the appropriate slave address bits are set for the device, then the device will issue an acknowledge pulse and prepare to receive the register address. Depending on the R/nW bit, the next byte received from the master is written to the addressed register (R/nW = 0) or the device responds with 8-bit data from the register (R/nW = 1). Data transmission is completed by either the reception of a stop condition or the reception of the data word sent to the device. A stop condition is recognized as a low to high transition of the SDA input during the high portion of the SCL signal. All other transitions of the SDA line must occur during the low portion of the SCL signal. An acknowledge is issued after the reception of valid address, sub-address and data words. The  $I^2$ C interfaces will auto-sequence through register addresses, so that multiple data words can be sent for a given  $I^2$ C transmission. Reference Figure 4.

Figure 3. I<sup>2</sup>C Start/Stop/Acknowledge Protocol

Figure 4. I<sup>2</sup>C Data Transmission Protocol

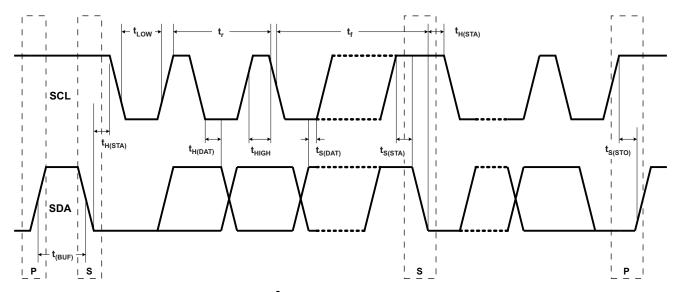

# **DATA TRANSMISSION TIMING**

$V_{BAT} = 3.6 \text{ V } \pm 5\%$ ,  $T_A = 25^{\circ}\text{C}$ ,  $C_L = 100 \text{ pF}$  (unless otherwise noted)

|                                 | PARAMETER                                      | TEST CONDITIONS | MIN          | TYP | MAX  | UNIT |  |

|---------------------------------|------------------------------------------------|-----------------|--------------|-----|------|------|--|

| f <sub>(SCL)</sub>              | Serial clock frequency                         |                 | 100          |     | 400  | KHz  |  |

|                                 | Due Free Time Detugen Sten and Start Condition | SCL = 100 KHz   | 4.7          |     |      |      |  |

| t <sub>BUF</sub>                | Bus Free Time Between Stop and Start Condition | SCL = 400 KHz   | 1.3          |     |      | μs   |  |

|                                 | Toloroble enike width on hus                   | SCL = 100 KHz   |              |     | 50   |      |  |

| t <sub>SP</sub>                 | Tolerable spike width on bus                   | SCL = 400 KHz   |              |     |      | ns   |  |

|                                 | SCL low time                                   | SCL = 100 KHz   | 4.7          |     |      |      |  |

| t <sub>LOW</sub>                | SCL low time                                   | SCL = 400 KHz   | 1.3          |     |      | μs   |  |

|                                 | CCI high time                                  | SCL = 100 KHz   | 4            |     |      | μs   |  |

| tHIGH                           | SCL high time                                  | SCL = 400 KHz   | 600          |     |      | ns   |  |

| $t_{S(DAT)} \qquad SDA \to SCL$ | CDA CCI potrus timo                            | SCL = 100 KHz   | 250          |     |      | 20   |  |

|                                 | SDA → SCL setup time                           | SCL = 400 KHz   | 100          |     |      | ns   |  |

| t <sub>S(STA)</sub> Start con-  | Chart condition actual time                    | SCL = 100 KHz   | 4.7          |     |      | μs   |  |

|                                 | Start condition setup time                     | SCL = 400 KHz   | 600          |     |      | ns   |  |

|                                 | Chan and distance as the state of              | SCL = 100 KHz   | 4            |     |      | μs   |  |

| t <sub>S(STO)</sub>             | Stop condition setup time                      | SCL = 400 KHz   | 600          |     |      | ns   |  |

|                                 | SDA → SCL hold time                            | SCL = 100 KHz   |              |     | 3.45 |      |  |

| t <sub>H(DAT)</sub>             | SDA → SCL floid time                           | SCL = 400 KHz   | 0            |     | 0.9  | μs   |  |

|                                 | Chart aga dition hold time                     | SCL = 100 KHz   | 4            |     |      | μs   |  |

| t <sub>H(STA)</sub>             | Start condition hold time                      | SCL = 400 KHz   | 600          |     |      | ns   |  |

|                                 | Disa time of COL Circus                        | SCL = 100 KHz   |              |     | 1000 | ns   |  |

| t <sub>r(SCL)</sub>             | Rise time of SCL Signal                        | SCL = 400 KHz   | :L = 400 KHz |     |      |      |  |

|                                 | Fall time of COL Cional                        | SCL = 100 KHz   |              |     | 300  | 20   |  |

| t <sub>f(SCL)</sub>             | Fall time of SCL Signal                        | SCL = 400 KHz   |              |     |      | ns   |  |

|                                 | Dies time of CDA Cional                        | SCL = 100 KHz   |              |     | 1000 | 20   |  |

| t <sub>r(SDA)</sub>             | Rise time of SDA Signal                        | SCL = 400 KHz   |              |     | 300  | ns   |  |

|                                 | Dies time of CDA Cional                        | SCL = 100 KHz   |              |     | 300  | 20   |  |

| t <sub>f(SDA)</sub>             | Rise time of SDA Signal                        | SCL = 400 KHz   | 300          | ns  |      |      |  |

SLVSB25 – AUGUST 2011 www.ti.com

### **REGISTER ADDRESS MAP**

| REGISTER | ADDRESS (HEX) | NAME            | DEFAULT<br>VALUE | DESCRIPTION                          |

|----------|---------------|-----------------|------------------|--------------------------------------|

| 1        | 01            | not used        |                  |                                      |

| 2        | 02            | CONTROL         | 0000 0010        | Control register                     |

| 3        | 03            | VCM_CURRENT_MSB | 0000 0000        | Voice coil motor MSB current control |

| 4        | 04            | VCM_CURRENT_LSB | 0000 0000        | Voice coil motor LSB current control |

| 5        | 05            | STATUS          | 0000 0000        | Status register                      |

| 6        | 06            | MODE            | 0000 0000        | Mode register                        |

| 7        | 07            | VCM_FREQ        | 1000 0011        | VCM resonance frequency              |

# **CONTROL REGISTER (CONTROL)**

Address - 0x02h

| DATA BIT    | D7       | D6       | D5       | D4       | D3       | D2       | D1      | D0    |

|-------------|----------|----------|----------|----------|----------|----------|---------|-------|

| FIELD NAME  | not used | EN_RING | RESET |

| READ/WRITE  | R        | R        | R        | R        | R        | R        | R/W     | R/W   |

| RESET VALUE | 0        | 0        | 0        | 0        | 0        | 0        | 1       | 0     |

| FIELD NAME | BIT DEFINITION                                                                                                                                    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Forced software reset (reset all registers to default values) and device goes into STANDBY. RESET bit is automatically cleared when written high. |

| RESET      | 0 – inactive                                                                                                                                      |

|            | 1 – device goes to STANDBY                                                                                                                        |

|            | Enables ringing compensation.                                                                                                                     |

| EN_RING    | 0 – disabled                                                                                                                                      |

|            | 1 – enabled                                                                                                                                       |

# VCM MSB CURRENT CONTROL REGISTER (VCM\_CURRENT\_MSB)

Address - 0x03h

| DATA BIT    | D7       | D6       | D5       | D4       | D3       | D2       | D1               | D0 |

|-------------|----------|----------|----------|----------|----------|----------|------------------|----|

| FIELD NAME  | not used | VCM_CURRENT[9:0] |    |

| READ/WRITE  | R        | R        | R        | R        | R        | R        | R/W              |    |

| RESET VALUE | 0        | 0        | 0        | 0        | 0        | 0        | 0                | 0  |

| FIELD NAME       | BIT DEFINITION           |

|------------------|--------------------------|

|                  | VCM current control      |

|                  | 00 0000 0000b – 0 mA     |

|                  | 00 0000 0001b – 0.1 mA   |

| VCM_CURRENT[9:0] | 00 0000 0010b – 0.2 mA   |

|                  |                          |

|                  | 11 1111 1110b – 102.2 mA |

|                  | 11 1111 1111b – 102.3 mA |

# VCM LSB CURRENT CONTROL REGISTER (VCM\_CURRENT\_LSB)

Address - 0x04h

| DATA BIT    | D7               | D6  | D5 | D4 | D3 | D2 | D1 | D0 |

|-------------|------------------|-----|----|----|----|----|----|----|

| FIELD NAME  | VCM_CURRENT[7:0] |     |    |    |    |    |    |    |

| READ/WRITE  |                  | R/W |    |    |    |    |    |    |

| RESET VALUE | 0                | 0   | 0  | 0  | 0  | 0  | 0  | 0  |

| FIELD NAME       | BIT DEFINITION           |

|------------------|--------------------------|

|                  | VCM current control      |

|                  | 00 0000 0000b – 0 mA     |

|                  | 00 0000 0001b – 0.1 mA   |

| VCM_CURRENT[7:0] | 00 0000 0010b – 0.2 mA   |

|                  |                          |

|                  | 11 1111 1110b – 102.2 mA |

|                  | 11 1111 1111b – 102.3 mA |

# STATUS REGISTER (STATUS)(1)

Address - 0x05h

| DATA BIT    | D7       | D6       | D5       | D4  | D3   | D2   | D1   | D0  |

|-------------|----------|----------|----------|-----|------|------|------|-----|

| FIELD NAME  | not used | not used | not used | TSD | VCMS | VCMO | UVLO | OVC |

| READ/WRITE  | R        | R/WR     | R        | R   | R    | R    | R    | R   |

| RESET VALUE | 0        | 0        | 0        | 0   | 0    | 0    | 0    | 0   |

<sup>(1)</sup> Status bits are cleared when device changes it's state from standby to active. If TSD was tripped the device goes into Standby and will not allow the transition into Active until the device cools down and TSD is cleared.

| FIELD NAME | BIT DEFINITION                  |

|------------|---------------------------------|

| OVC        | Over current detection          |

| UVLO       | Undervoltage Lockout            |

| VCMO       | Voice coil motor open detected  |

| VCMS       | Voice coil motor short detected |

| TSD        | Thermal shutdown detected       |

SLVSB25 – AUGUST 2011 www.ti.com

# **MODE REGISTER (MODE)**

Address – 0x06h

| DATA BIT    | D7       | D6       | D5       | D4      | D3           | D2      | D1            | D0  |

|-------------|----------|----------|----------|---------|--------------|---------|---------------|-----|

| FIELD NAME  | not used | not used | not used | F       | PWM_FREQ[2:0 | PWM/LIN | RING_MOD<br>E |     |

| READ/WRITE  | R        | R        | R        | R/W R/W |              | R/W     | R/W           | R/W |

| RESET VALUE | 0        | 0        | 0        | 0       | 0            | 0       | 0             | 0   |

| FIELD NAME    | BIT DEFINITION                            |  |  |  |  |

|---------------|-------------------------------------------|--|--|--|--|

|               | Ringing compensation settling time        |  |  |  |  |

| RING_MODE     | $0-2x(1/f_{VCM})$                         |  |  |  |  |

|               | $1-1x(1/f_{VCM})$                         |  |  |  |  |

|               | Driver output stage in linear or PWM mode |  |  |  |  |

| PWM/LIN       | 0 – PWM mode                              |  |  |  |  |

|               | 1 – Linear mode                           |  |  |  |  |

|               | Output stage PWM switching frequency      |  |  |  |  |

|               | 000 – 0.5 MHz                             |  |  |  |  |

|               | 001 – 1 MHz                               |  |  |  |  |

|               | 010 – N/A                                 |  |  |  |  |

| PWM_FREQ[2:0] | 011 – 2 MHz                               |  |  |  |  |

|               | 100 – N/A                                 |  |  |  |  |

|               | 101 – N/A                                 |  |  |  |  |

|               | 110 – N/A                                 |  |  |  |  |

|               | 111 – 4 MHz                               |  |  |  |  |

# VCM RESONANCE FREQUENCY REGISTER (VCM\_FREQ)

Address – 0x07h

| DATA BIT    | D7 | D6            | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |  |

|-------------|----|---------------|----|----|----|----|----|----|--|--|--|--|

| FIELD NAME  |    | VCM_FREQ[7:0] |    |    |    |    |    |    |  |  |  |  |

| READ/WRITE  |    | R/W           |    |    |    |    |    |    |  |  |  |  |

| RESET VALUE | 1  | 0             | 0  | 0  | 0  | 0  | 1  | 1  |  |  |  |  |

| FIELD NAME    | BIT DEFINITION                                                                                                                                                                                                   |     |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|               | VCM mechanical ringing frequency for the ringing compensation can be selected with the below formula. The formula gives the VCM_FREQ[7:0] register value in decimal which should be rounded the nearest integer. | to  |

| VCM_FREQ[7:0] | $VCM\_FREQ = 383 - \frac{19200}{F_{res}} \tag{2}$                                                                                                                                                                | (1) |

|               | Default VCM mechanical ringing frequency is 76.4 Hz.                                                                                                                                                             |     |

|               | $VCM \_FREQ = 383 - \frac{19200}{76.4} = 131.69 \Rightarrow 132 \Rightarrow '1000\ 0011'$                                                                                                                        | (2) |

9-Sep-2011

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| DRV201YFMR       | ACTIVE     | DSLGA        | YFM                | 6    | 3000        | Green (RoHS<br>& no Sb/Br) | Call TI              | Level-1-260C-UNLIM           |                             |

| DRV201YFMT       | ACTIVE     | DSLGA        | YFM                | 6    | 250         | Green (RoHS<br>& no Sb/Br) | Call TI              | Level-1-260C-UNLIM           |                             |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PACKAGE MATERIALS INFORMATION

www.ti.com 8-Sep-2011

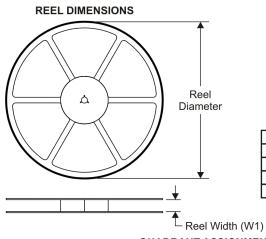

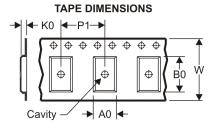

### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

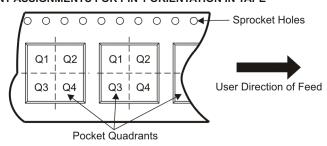

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DRV201YFMR | DSLGA           | YFM                | 6 | 3000 | 180.0                    | 8.4                      | 0.85       | 1.52       | 0.19       | 4.0        | 8.0       | Q1               |

| DRV201YFMT | DSLGA           | YFM                | 6 | 250  | 180.0                    | 8.4                      | 0.85       | 1.52       | 0.19       | 4.0        | 8.0       | Q1               |

www.ti.com 8-Sep-2011

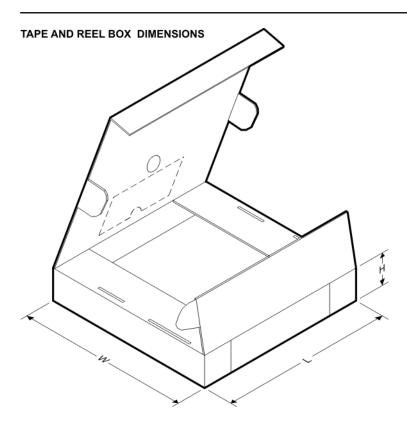

#### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV201YFMR | DSLGA        | YFM             | 6    | 3000 | 210.0       | 185.0      | 35.0        |

| DRV201YFMT | DSLGA        | YFM             | 6    | 250  | 210.0       | 185.0      | 35.0        |

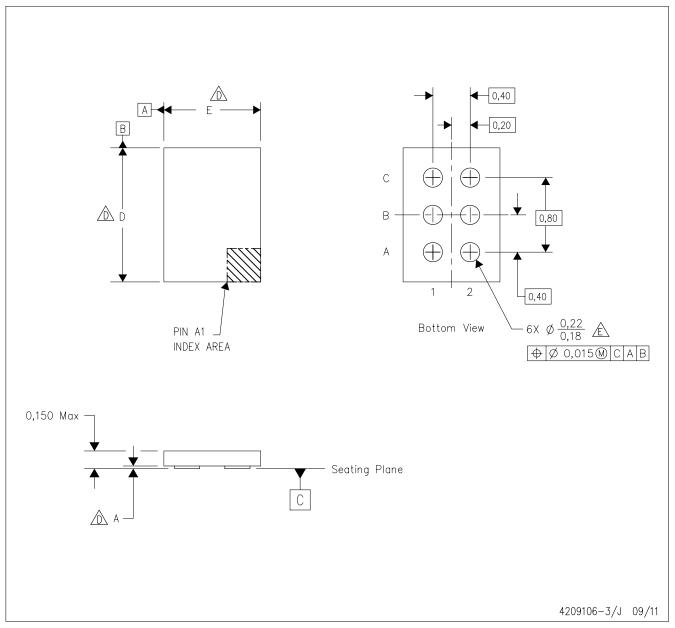

# YFM (R-pSTAR-N6)

PicoStar™

NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. PicoStar™ package configuration.

The package size (Dimension D and E) of a particular device is specified in the device Product Data Sheet version of this drawing, in case it cannot be found in the product data sheet please contact a local TI representative.

Reference Product Data Sheet for array population. 2 x 3 matrix pattern is shown for illustration only.

F. This package is a Pb-free solder land design.

PicoStar is a trademark of Texas Instruments.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

### Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface interface.ti.com Security www.ti.com/security

Logic Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>

TI E2E Community Home Page <u>e2e.ti.com</u>

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated