# Section I. HardCopy II Device Family Data Sheet

This section provides designers with the data sheet specifications HardCopy® II devices. These cpaters contain feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operationg conditions, AC timing parameters, a reference to power consumption, and ordering information for HardCopy II devices.

This section contains the following:

- "Introduction to HardCopy II Devices" on page 1–1

- "Description, Architecture, and Features" on page 2–1

- "Boundary-Scan Support" on page 3–1

- "DC and Switching Specifications and Operating Conditions" on page 4–1

- "Quartus II Support for HardCopy II Devices" on page 5–1

- "Script-Based Design for HardCopy II Devices" on page 6–1

- "Timing Constraints for HardCopy II Devices" on page 7–1

- "Migrating Stratix II Device Resources to HardCopy II Devices" on page 8–1

### **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the complete handbook.

Altera Corporation Section I–1

Section I–2 Altera Corporation

## 1. Introduction to HardCopy II Devices

H51015-2.6

### Introduction

HardCopy® II devices are low-cost, high-performance structured ASICs with pin-outs, densities, and architecture that complement Stratix® II devices. HardCopy II device features, such as phase-locked loops (PLLs), memory, and I/O elements (IOEs), are functionally and electrically equivalent to the Stratix II FPGA features. The combination of Stratix II FPGAs for in-system prototype and design verification, HardCopy II devices for high-volume production, and the Quartus® II software for design, provide a complete, low-risk design solution.

HardCopy II devices improve on the successful and proven methodology of the two previous generations of HardCopy series devices. Altera® HardCopy II devices use the same base arrays across multiple designs for a given device density and are customized using only two metal layers. HardCopy II devices offer up to 90% cost reduction compared to Stratix II FPGA prototypes.

The Quartus II software provides a complete set of tools, common for both designing Stratix II FPGA prototypes and for quickly migrating the design to a HardCopy II companion device. HardCopy II devices are also supported through other front-end design tools from Synopsys, Synplicity, and Mentor Graphics<sup>®</sup>.

## Feature Overview

HardCopy II structured ASICs are manufactured on a 1.2 V, 90 nm all-layer-copper metal fabrication process (up to nine layers of metal). HardCopy II devices offer the following features:

- Fine-grained *HCell* architecture resulting in a low-cost, high-performance, low-power structured ASIC

- Customized using only two metal layers for fast turn-around times and low non-recurring expenses (NRE)

- Fully tested prototypes are available in approximately 10 to 12 weeks from the date of your design submission

- Support for instant-on or instant-on-after-50-ms power-up modes

- Preserves the design functionality of a Stratix II FPGA prototype

- 1,000,000 to 3,600,000 usable gates for both logic and DSP functions

- System performance up to 350 MHz

- Up to 50% power reduction (dynamic and static) for typical designs compared to Stratix II FPGA prototypes

The actual performance and power consumption improvements mentioned in this datasheet are design-dependent.

- Internal Memory

- Up to 8,847,360 RAM bits available (including parity bits)

- True dual-port memory, suitable for use in first-in-first-out (FIFO) buffers

- Phase-Locked Loops (PLLs)

- Up to 16 global clocks with 24 clocking resources per device region

- Clock control block supports dynamic clock network enable/disable and dynamic global clock network source selection

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device which provide identical features as the FPGA counterparts, including spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, advanced multiplication, and phase shifting

- I/O Standards and Intellectual Property (IP)

- Support for numerous single-ended and differential I/O standards such as LVTTL, LVCMOS, PCI, PCI-X, SSTL, HSTL, and LVDS

- High-speed differential I/O support on up to 116 channels with dynamic phase alignment (DPA) circuitry for 1-Gigabit-per-second (Gbps) performance

- Support for high-speed networking and communications bus standards including Parallel RapidIO, SPI-4 Phase 2 (POS-PHY Level 4), HyperTransport™ technology, and SFI-4

- Support for high-speed external memory, including DDR and DDR2 SDRAM, RLDRAM II, QDRII SRAM, and SDR SDRAM

- Support for multiple intellectual property megafunctions from Altera MegaCore<sup>®</sup> functions, and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Packaging

- Pin-compatible with Stratix II FPGA prototypes

- Up to 951 user I/O pins available

- Available in wire bond and flip-chip space-saving FineLine BGA packages (Table 1–3).

The HardCopy II device family consists of five devices. Table 1–1 summarizes the features available in the HardCopy II devices.

| Table 1–1. HardCopy II Device Family Features |            |           |           |           |           |  |

|-----------------------------------------------|------------|-----------|-----------|-----------|-----------|--|

| Feature                                       | HC210W (1) | HC210     | HC220     | HC230     | HC240     |  |

| ASIC equivalent gates (2)                     | 1,000,000  | 1,000,000 | 1,900,000 | 2,900,000 | 3,600,000 |  |

| M4K RAM blocks<br>(4 Kbits plus parity)       | 190        | 190       | 408       | 614       | 768 (3)   |  |

| M-RAM blocks<br>(512 Kbits plus parity)       | 0          | 0         | 2         | 6         | 9         |  |

| Total RAM bits<br>(including parity bits)     | 875,520    | 875,520   | 3,059,712 | 6,368,256 | 8,847,360 |  |

| Enhanced PLLs                                 | 2          | 2         | 2         | 4         | 4         |  |

| Fast PLLs                                     | 2          | 2         | 2         | 4         | 8         |  |

| Maximum user I/O pins (4), (5)                | 308        | 334       | 494       | 698       | 951       |  |

#### Notes to Table 1-1:

- (1) HC210W devices are in a wire bond package. All other HardCopy II devices and Stratix II FPGAs use a flip-chip package. Devices in a wire bond package offer different performance and signal integrity characteristics compared to devices in a flip-chip package.

- (2) This is the number of ASIC equivalent gates available in the HardCopy II base array, shared between both adaptive logic module (ALM) logic and DSP functions from a Stratix II FPGA prototype. Each Stratix II adaptive logic module (ALM) is equal to approximately 30 ASIC equivalent gates. The number of ASIC equivalent gates usable is bounded by the number of ALMs in the companion Stratix II FPGA device.

- (3) Total number of usable M4K blocks is 768, which allows migration compatibility when prototyping with an EP2S180 device. This may be different from the Quartus II software total physical M4K count of the HC240.

- (4) The I/O pin counts include the dedicated CLK input pins, which can be used for clock signals or data inputs.

- (5) The Quartus II I/O pin counts include an additional pin (PLLENA), which is not available as a general-purpose I/O pin. The PLLENA pin can only be used to enable the PLLs.

## Migration and Packaging Overview

HardCopy II devices offer pin-to-pin compatibility to the Stratix II prototype, which makes them drop-in replacements for the FPGAs. Therefore, the same system board and software developed for prototyping and field trials can be retained, enabling the fastest time-to-market for high-volume production. When migrating a specific Stratix II FPGA to a HardCopy II device, there are a number of FPGA prototype choices, as shown in Table 1–2. Depending on the design resource needs, designers can choose an appropriate HardCopy II device.

| Table 1–2. Stratix II FPGA to HardCopy II Migration Paths |                          |                   |          |              |              |              |

|-----------------------------------------------------------|--------------------------|-------------------|----------|--------------|--------------|--------------|

| HardCopy II                                               | Dookono                  | Stratix II Device |          |              |              |              |

| Device                                                    | Package                  | EP2S30            | EP2S60   | EP2S90       | EP2\$130     | EP2S180      |

| HC210W                                                    | 484-pin FineLine BGA (1) | <b>✓</b>          | <b>✓</b> | <b>√</b> (2) |              |              |

| HC210                                                     | 484-pin FineLine BGA     | <b>✓</b>          | ✓        | <b>√</b> (2) |              |              |

| HC220                                                     | 672-pin FineLine BGA     |                   | <b>✓</b> |              |              |              |

| HC220                                                     | 780-pin FineLine BGA     |                   |          | ✓            | <b>√</b> (2) |              |

| HC230                                                     | 1,020-pin FineLine BGA   |                   |          | ✓            | ✓            | <b>√</b> (2) |

| HC240                                                     | 1,020-pin FineLine BGA   |                   |          |              |              | <b>✓</b>     |

| HC240                                                     | 1,508-pin FineLine BGA   |                   |          |              |              | <b>✓</b>     |

#### Notes to Table 1-2:

- The HC210W device uses a wire bond package while the Stratix II FPGA prototype device uses a pin-compatible flip-chip package.

- (2) Depending on design specific resource utilization, an opportunistic migration path may exist between this device pair. Be sure to confirm your design is a potential candidate for such a path by fitting with the Quartus II software and consulting an Altera applications engineer.

HardCopy II devices are available in the packages shown in Table 1–3.

| Table 1–3. HardCopy II Package Options and I/O Pin Counts   Notes (1), (2) |                                |                                |                         |                         |                           |                           |  |

|----------------------------------------------------------------------------|--------------------------------|--------------------------------|-------------------------|-------------------------|---------------------------|---------------------------|--|

| Package                                                                    | 484-Pin<br>FineLine BGA<br>(3) | 484-Pin<br>FineLine BGA<br>(3) | 672-Pin<br>FineLine BGA | 780-Pin<br>FineLine BGA | 1,020-Pin<br>FineLine BGA | 1,508-Pin<br>FineLine BGA |  |

| Туре                                                                       | Wire bond                      | Flip-chip                      | Flip-chip               | Flip-chip               | Flip-chip                 | Flip-chip                 |  |

| Dimension                                                                  |                                |                                |                         |                         |                           |                           |  |

| Pitch (mm)                                                                 | 1.00                           | 1.00                           | 1.00                    | 1.00                    | 1.00                      | 1.00                      |  |

| Area (mm²)                                                                 | 529                            | 529                            | 729                     | 841                     | 1,089                     | 1,600                     |  |

| Length × width (mm × mm)                                                   | 23 × 23                        | 23 × 23                        | 27 × 27                 | 29 × 29                 | 33 × 33                   | 40 × 40                   |  |

| Device                                                                     |                                |                                | Maximum U               | lser I/O Pins           |                           |                           |  |

| HC210W                                                                     | 308                            |                                |                         |                         |                           |                           |  |

| HC210                                                                      |                                | 334                            |                         |                         |                           |                           |  |

| HC220                                                                      |                                |                                | 492                     | 494                     |                           |                           |  |

| HC230                                                                      |                                |                                |                         |                         | 698                       |                           |  |

| HC240                                                                      |                                |                                |                         |                         | 742                       | 951                       |  |

#### *Notes to Table 1–3:*

- (1) The Quartus II I/O pin counts include an additional pin (PLLENA) which is not available as a general-purpose I/O pin. The PLLENA pin can only be used to enable the PLLs.

- (2) The I/O pin counts include the dedicated CLK input pins, which can be used for clock signals or data inputs.

- (3) The EP2S90 FPGA prototype uses a 484-pin hybrid FineLine BGA package. For more information, refer to the Stratix II Device Handbook.

# Document Revision History

Table 1–4 shows the revision history for this chapter.

| Table 1–4. Document Revision History (Part 1 of 2) |                                      |   |  |  |  |  |

|----------------------------------------------------|--------------------------------------|---|--|--|--|--|

| Date and Document<br>Version                       | Changes Made Summary of Changes      |   |  |  |  |  |

| September 2008, v2.6                               | Updated chapter number and metadata. | _ |  |  |  |  |

| June 2007, v2.5                                    | Minor text edits.                    | _ |  |  |  |  |

| Table 1–4. Document Revision History (Part 2 of 2) |                                                                                                                                                     |                                                                                                                                |  |  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date and Document<br>Version                       | Changes Made                                                                                                                                        | Summary of Changes                                                                                                             |  |  |

| December 2006<br>v2.4                              | <ul> <li>Minor updates for the Quartus II software version 6.1.0</li> <li>Merged Table 1-3 and Table 1-4</li> <li>Added revision history</li> </ul> | A minor update to the chapter, due to changes in the Quartus II software version 6.1 release.  Merged Table 1-3 and Table 1-4. |  |  |

| March 2006, v2.3                                   | <ul><li>Updated Table 1-1 and Table 1-3.</li><li>Minor edits and clarifications throughout.</li></ul>                                               |                                                                                                                                |  |  |

| October 2005, v2.2.                                | Updated graphics                                                                                                                                    |                                                                                                                                |  |  |

| July 2005, v2.2.                                   | Updated graphics                                                                                                                                    |                                                                                                                                |  |  |

| May 2005, v2.0                                     | <ul> <li>Updated Table 1–1.</li> <li>Updated migration process time.</li> <li>Updated "Features" section.</li> </ul>                                |                                                                                                                                |  |  |

| January 2005<br>v1.0                               | Added document to the HardCopy Series Handbook.                                                                                                     |                                                                                                                                |  |  |

# 2. Description, Architecture, and Features

H51016-2.5

### Introduction

Altera® HardCopy® II devices feature an architecture that provides high-density, high-performance, and low-power consumption suitable for a variety of applications. HardCopy II devices are low-cost structured ASICs with pin-outs, densities, and architecture that complement Stratix® II FPGAs. HardCopy II devices make optimal use of die area and core resources while offering features that are functionally equivalent to the Stratix II FPGA. The combination of Stratix II FPGAs for in-system prototype and design verification, HardCopy II devices for high-volume production, and the Quartus® II design software, provide a complete, seamless path from prototype to volume production. Table 2–1 provides an overview of the HardCopy II device features.

| Table 2–1. HardCopy II Family Overview (Part 1 of 2) |                                  |                                  |                                                                      |                                    |                                                                          |  |

|------------------------------------------------------|----------------------------------|----------------------------------|----------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|--|

| Feature                                              | HC210W (1)                       | HC210                            | HC220                                                                | HC230                              | HC240                                                                    |  |

| ASIC gates (2)                                       | 1,000,000                        | 1,000,000                        | 1,900,000                                                            | 2,900,000                          | 3,600,000                                                                |  |

| M4K RAM blocks (4k bits plus parity)                 | 190                              | 190                              | 408                                                                  | 614                                | 768 (3)                                                                  |  |

| M-RAM blocks (512k bits plus parity)                 | 0                                | 0                                | 2                                                                    | 6                                  | 9                                                                        |  |

| Total RAM bits (including parity bits)               | 875,520                          | 875,520                          | 3,059,712                                                            | 6,368,256                          | 8,847,360                                                                |  |

| Enhanced PLLs                                        | 2                                | 2                                | 2                                                                    | 4                                  | 4                                                                        |  |

| Fast PLLs                                            | 2                                | 2                                | 2                                                                    | 4                                  | 8                                                                        |  |

| Package (maximum user I/O pins) (4), (5)             | 484-pin<br>FineLine<br>BGA (308) | 484-pin<br>FineLine BGA<br>(334) | 672-pin<br>FineLine BGA<br>(492)<br>780-pin<br>FineLine BGA<br>(494) | 1,020-pin<br>FineLine BGA<br>(698) | 1,020-pin<br>FineLine BGA<br>(742)<br>1,508-pin<br>FineLine BGA<br>(951) |  |

| Table 2–1. HardCopy II Family Overview (Part 2 of 2) |                            |                            |                             |                              |         |  |

|------------------------------------------------------|----------------------------|----------------------------|-----------------------------|------------------------------|---------|--|

| Feature                                              | HC210W (1)                 | HC210                      | HC220                       | HC230                        | HC240   |  |

| FPGA prototype options                               | EP2S30<br>EP2S60<br>EP2S90 | EP2S30<br>EP2S60<br>EP2S90 | EP2S60<br>EP2S90<br>EP2S130 | EP2S90<br>EP2S130<br>EP2S180 | EP2S180 |  |

Notes to Table 2-1:

- HC210W devices use a wire bond package. All other HardCopy II devices and Stratix II FPGAs use a flip-chip

package. Devices in a wire bond package offer different performance and signal integrity characteristics compared

to devices in a flip-chip package.

- (2) This is the number of ASIC gates available in the HardCopy II base array for both logic and DSP functions that can be implemented in a Stratix II FPGA prototype.

- (3) Total number of usable M4K blocks is 768, which allows migration compatibility when prototyping with an EP2S180 device. This may be different from the Quartus II software total physical M4K count of the HC240.

- (4) The I/O pin counts include the dedicated clock input pins, which can be used for clock signals or data inputs.

- (5) The Quartus II I/O pin counts include an additional pin (PLLENA), which is not available as a general-purpose I/O pin. The PLLENA pin can only be used to enable the PLLs.

# Functional Description

The HardCopy II device family provides greater flexibility to design with FPGA prototypes before moving to structured ASICs for production. Before seamlessly migrating to the HardCopy II structured ASIC, designers can prototype and test their design functionality using a Stratix II FPGA. There are multiple options for the prototype FPGA, allowing designers to choose the right HardCopy II device for volume production and maximum cost savings. The Quartus II design software includes features such as the Device Resource Guide, to help select the optimal HardCopy II device based on the design requirements.

For more information on the Device Resource Guide, refer to the *Quartus II Support for HardCopy II Devices* chapter in the *HardCopy Series Handbook*.

HardCopy II devices require minimal involvement from the designer in the device migration process. Additionally, unlike ASICs, the designer is not required to generate test benches, test vectors, or timing and functional simulations since prototyping is performed using an FPGA.

HardCopy II devices consist of base arrays that are common to all designs for a particular device density, with design-specific customization done using two metal layers. The reprogrammable FPGA logic, routing, memory, and FPGA configuration-related logic are stripped from HardCopy II devices. Removing all programmable and configuration resources and replacing them with direct metal connections results in considerable die size reduction and cost savings. A fine-grain architecture consisting of an array of HCells extends the die reduction and cost

savings, which results in low-cost structured ASICs with high-performance and low-power suitable for a wide variety of applications.

The SRAM configuration cells of the Stratix II FPGAs are replaced in HardCopy II devices with metal connections, which define the function of logic, memory, phase-locked loop (PLL), and I/O elements (IOEs) in the device. These resources are interconnected using metallization layers. Once a HardCopy II device is manufactured, the functionality of the device is fixed.

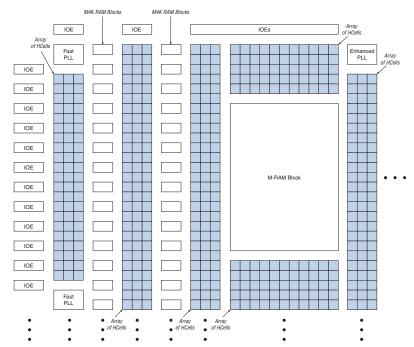

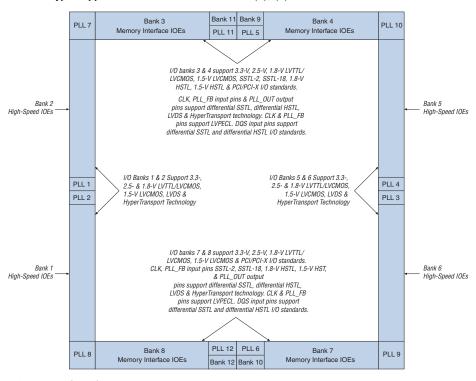

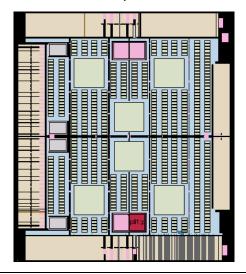

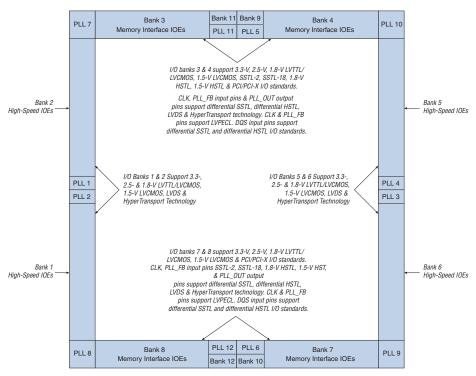

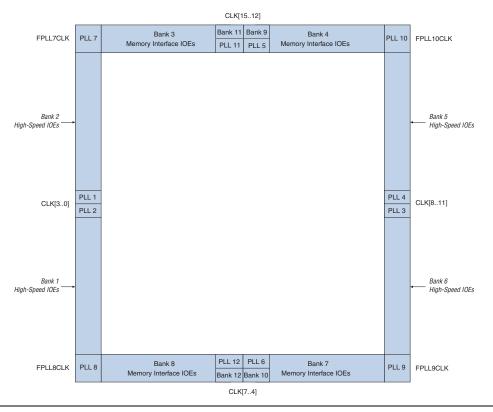

HardCopy II devices are manufactured using the same 90-nm process technology and operate using the same core voltage (1.2 V) as Stratix II FPGAs. Additionally, almost all architectural features in HardCopy II devices are functionally equivalent to features found in the Stratix II FPGA architecture. HardCopy II devices feature HCells, memory blocks, PLLs, and IOEs (Figure 2–1).

Figure 2–1. Example Block Diagram of HC230 Device Note (1)

Note to Figure 2–1:

(1) Figure 2–1 shows a graphical representation of the device floor plan. A detailed floor plan is available in the Quartus II software.

## HardCopy II and Stratix II Similarities and Differences

HardCopy II devices preserve the functionality of Stratix II FPGAs. Implementation of these architectural features in HardCopy II structured ASICs matches Stratix II FPGA implementation, with a few exceptions. Table 2–2 shows a qualitative comparison of HardCopy II device feature implementation versus Stratix II FPGA feature implementation. Other sections within this chapter provide details on similarities and differences of a particular HardCopy II feature.

| Table 2–2. HardCopy II Device vs. Stratix II FPGA Feature Implementation |            |           |  |  |

|--------------------------------------------------------------------------|------------|-----------|--|--|

| Feature                                                                  | Equivalent | Different |  |  |

| Logic blocks                                                             |            | ✓         |  |  |

| DSP blocks                                                               |            | ✓         |  |  |

| Memory                                                                   | ✓          |           |  |  |

| Clock networks                                                           | ✓          |           |  |  |

| PLLs                                                                     | ✓          |           |  |  |

| I/O features                                                             | ✓          |           |  |  |

| Configuration (1)                                                        |            | <b>✓</b>  |  |  |

*Note to Table 2–2:*

(1) HardCopy II structured ASICs do not need to be configured upon power-up.

The major similarities and differences between Stratix II FPGAs and HardCopy II devices are highlighted below:

- HardCopy II may result in a power reduction of up to 50% than an equivalent Stratix II FPGAs operating at the same frequency. Power consumption is design dependent and is a direct result of design performance and resource utilization.

- HardCopy II devices offer up to 100% performance improvement when compared to Stratix II FPGA prototypes. The performance improvement is achieved by efficient use of logic blocks, metal interconnect optimization, die size reduction, and customized signal buffering.

- Logic blocks, known as HCells, are the basic building block of the core logic in HardCopy II devices and replace Stratix II adaptive logic modules (ALMs). HCells implement logic and DSP functions.

- DSP block functions are implemented using HCells, instead of dedicated DSP blocks.

- M4K and M-RAM memory blocks can implement various types of memory (the same as Stratix II FPGAs), with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and first-in first-out (FIFO) buffers.

- Unlike Stratix II FPGAs, the HardCopy II M4K block contents cannot be pre-loaded with a Memory Initialization File (.mif) when used as RAM. When used as ROM, HardCopy II M4K blocks are initialized to the ROM contents.

- When used as RAM, and you select the non-registered output mode, HardCopy II M4K and M-RAM blocks power up with outputs unknown. In Stratix II FPGAs, M4K blocks power up with outputs cleared, while M-RAM blocks power up with outputs unknown. If registered outputs mode is selected, the outputs are cleared on both the M4K and M-RAM blocks in HardCopy II.

- The memory contents are unknown under both instances.

- All HardCopy II clock network features are the same as in Stratix II FPGAs.

- Enhanced PLL and fast PLL implementations in HardCopy II devices are the same as in Stratix II FPGAs.

- All Stratix II I/O features and supported I/O standards are offered in HardCopy II devices.

- The Joint Test Action Group (JTAG) boundary scan order and length in HardCopy II devices is different than that of the Stratix II FPGA. Use a HardCopy II boundary-scan description language (BSDL) file that describes the re-ordered and shortened boundary scan chain.

- Unlike Stratix II devices, HardCopy II devices are customized using two metal layers. Therefore, configuration circuitry is not required. FPGA configuration emulation and other configuration modes, including remote system upgrades and design security using configuration bitstream encryption, are not supported in HardCopy II devices.

- Even though configuration is not required, the CRC\_ERROR pin function is supported by the HardCopy II using Quartus II software version 6.0 and above. There is no need to recompile the Stratix II design to eliminate this feature.

Only supplementary information to highlight HardCopy II similarities and differences compared to the Stratix II FPGA architecture and functionality is provided in this chapter. For more information on similarities and differences of available resources of the HardCopy II, refer to the *Migrating Stratix II Device Resources to HardCopy II Devices* chapter of this Handbook. In addition, the *Stratix II Device Handbook* has detailed explanations of architectural features and functions that are similar to the HardCopy II devices.

### **HCells**

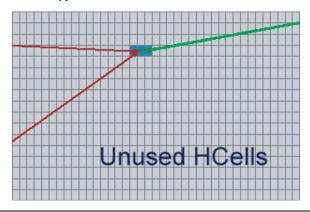

HardCopy II devices are built using an array of fine-grained architecture blocks called HCells. HCells are a collection of logic transistors based on 1.2 V, 90 nm process technology, similar to Stratix II devices. The construction of logic using HCells allows flexible functionality such that when HCells are combined, all viable logic combinations of Stratix II functionality are replicated. These HCells constitute the array of HCells area in Figure 2–1. Only HCells needed to implement the customer design are assembled together, which optimizes HCell utilization. The unused area of the HCell logic fabric is powered down, resulting in significant power savings compared with the Stratix II FPGA prototype.

The Quartus II software uses the library of pre-characterized HCell macros to place Stratix II ALM and DSP configurations into the HardCopy II HCell-based logic fabric. An HCell macro defines how a group of HCells are connected together within the array. HCell macros can construct all combinations of combinational logic, adder, and register functions that can be implemented by a Stratix II ALM. HCells not used for ALM configurations can be used to implement DSP block functions.

Based on design requirements, the Quartus II software will chose the appropriate HCell macros to implement the design functionality. For example, Stratix II ALMs offer flexible look-up table (LUT) blocks, registers, arithmetic blocks, and LAB-wide control signals. In HardCopy II devices, if your design requires these architectural elements, the Quartus II synthesis tool will map the design to the appropriate HCells, resulting in improved design performance compared to the Stratix II FPGA prototype.

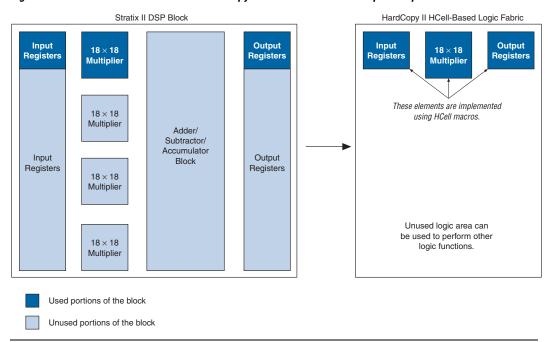

Stratix II FPGAs have dedicated DSP blocks to implement various DSP functions. Stratix II DSP blocks consist of a multiplier block, an adder/subtractor/accumulator block, a summation block, input and output interfaces, and input and output registers. In HardCopy II devices, HCell macros implement Stratix II DSP block functionality with area efficiency and performance on par with the dedicated DSP blocks in Stratix II FPGAs.

There are eight HCell macros which implement the eight supported modes of operation for the Stratix II DSP block:

- 9 × 9 multiplier

- $9 \times 9$  two-multiplier adder ( $9 \times 9$  complex multiply)

- 9 × 9 four-multiplier adder

- 18 × 18 multiplier

- $18 \times 18$  two-multiplier adder ( $18 \times 18$  complex multiply)

- 18 × 18 four-multiplier adder

- 52-bit (18 × 18) multiplier-accumulator

- 36 × 36 multiplier

Only HCells that are required to implement the design's DSP functions are enabled. HCells not needed for DSP functions can be used for ALM configurations, which results in efficient logic usage. In addition to area management, the placement of these HCell macros allows for optimized routing and performance.

An example of efficient logic area usage can be seen when comparing the  $18 \times 18$  multiplier implementation in Stratix II FPGAs using the dedicated DSP block versus the implementation in HardCopy II devices using HCells. If the Stratix II DSP function only calls for one  $18 \times 18$  multiplier, the other three  $18 \times 18$  multipliers and the DSP block's adder output block are not used (Figure 2–2). In HardCopy II devices, the HCell-based logic fabric that is not used for DSP functions can be used to implement other combinational logic, adder, and register functions.

Figure 2-2. Stratix II DSP Block versus HardCopy II HCell 18 x 18-Bit Multiplier Implementation

HardCopy II devices support all Stratix II DSP configurations (9  $\times$  9, 18  $\times$  18, and 36  $\times$  36 multipliers) and all Stratix II DSP block features, such as dynamic sign controls, dynamic addition/subtraction, saturation, rounding, and dynamic input shift registers, except for dynamic mode switching.

Dynamic mode switching allows the designer to set up each Stratix II DSP block to dynamically switch between the following three modes:

- Up to four 18-bit independent multipliers

- Up to two 8-bit multiplier-accumulators

- One 36-bit multiplier

Each half of a Stratix II DSP block has separate mode control signals. Since DSP block functions are implemented in HardCopy II devices using HCells, HardCopy II devices do not support dynamic mode switching. If this feature is used, the Quartus II software flags the DSP implementation and does not allow you to migrate the design. The fitter reports that all HardCopy II devices are not compatible with the design. To migrate your Stratix II design to a HardCopy II companion device, disable dynamic switching in the DSP blocks.

For more information on the Stratix II DSP operational modes, refer to the *Stratix II Device Handbook*.

# Embedded Memory

HardCopy II memory blocks can implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. HardCopy II devices support the same memory functions and features as Stratix II FPGAs.

Functionally, the memory in both devices are identical. However, the number of available memory blocks differs based on density (Table 2–3).

| Table 2–3. HardCopy II Embedded Memory Resources |         |         |           |           |           |  |

|--------------------------------------------------|---------|---------|-----------|-----------|-----------|--|

| Feature HC210W HC210 HC220 HC230 HC240           |         |         |           |           |           |  |

| M4K RAM blocks (4 Kbits)                         | 190     | 190     | 408       | 614       | 768       |  |

| M-RAM blocks (512 Kbits)                         | 0       | 0       | 2         | 6         | 9         |  |

| Total RAM bits (bits)                            | 875,520 | 875,520 | 3,059,712 | 6,368,256 | 8,847,360 |  |

Since device functionality is fixed in HardCopy II devices, M4K block contents cannot be preloaded or initialized with a MIF when they are configured as RAM. When the M4K blocks are used as ROM, they will initialize to the design's ROM contents.

When using the non-registered outputs mode for the HardCopy II M4K memory block, the outputs power up uninitialized. When using the registered outputs mode for the HardCopy II M4K memory blocks, the

outputs are cleared on power up. The designer needs to take these into consideration when designing logic that might evaluate the initial power-up values of the memory block.

HardCopy II embedded memory consists of M4K and M-RAM memory blocks and have a one-to-one mapping from Stratix II M4K and M-RAM resources. Table 2–4 shows the size and features of the different RAM blocks.

For more information on the Stratix II memory block features, refer to the *Stratix II Device Handbook*.

## PLLs and Clock Networks

Both HardCopy II enhanced and fast PLLs are feature rich, supporting advanced capabilities such as clock switchover, reconfigurable phase shift, PLL reconfiguration, and reconfigurable bandwidth. PLLs are used for general-purpose clock management, supporting multiplication, division, phase shifting, and programmable duty cycle. In addition, enhanced PLLs support external clock feedback mode, spread-spectrum clocking, and counter cascading. Fast PLLs offer high speed outputs to manage the high-speed differential I/O interfaces.

All Stratix II PLL features are supported by HardCopy II PLLs.

Similar to Stratix II FPGAs, HardCopy II devices also support a power-down mode where unused clock networks can be disabled. HardCopy II and Stratix II clock control blocks support dynamic selection of the input clock from up to four possible sources, giving the designer the flexibility to choose from multiple (up to four) clock sources.

| Table 2-4. HardCopy II Embedded Memory Features (Part 1 of 2) Notes (1), (2), (3) |                                                                                                  |                                                                                                                  |  |  |  |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| Feature                                                                           | M4K Blocks                                                                                       | M-RAM Blocks                                                                                                     |  |  |  |

| Maximum performance (1), (4)                                                      | 350 MHz                                                                                          | 350 MHz                                                                                                          |  |  |  |

| Total RAM bits (including parity bits)                                            | 4,608                                                                                            | 589,824                                                                                                          |  |  |  |

| Configurations                                                                    | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |  |  |  |

| Parity bits                                                                       | ✓                                                                                                | ✓                                                                                                                |  |  |  |

| Byte enable                                                                       | ✓                                                                                                | ✓                                                                                                                |  |  |  |

| Pack mode                                                                         | <b>✓</b>                                                                                         | ✓                                                                                                                |  |  |  |

| Address clock enable                                                              | <b>✓</b>                                                                                         | ✓                                                                                                                |  |  |  |

| Single-port memory                                                                | ✓                                                                                                | ✓                                                                                                                |  |  |  |

| Simple dual-port memory                                                           | ✓                                                                                                | ✓                                                                                                                |  |  |  |

| True dual-port memory                                                             | ✓                                                                                                | ✓                                                                                                                |  |  |  |

| Embedded shift register                                                           | ✓                                                                                                |                                                                                                                  |  |  |  |

| ROM                                                                               | ✓                                                                                                |                                                                                                                  |  |  |  |

| FIFO buffer                                                                       | ✓                                                                                                | ✓                                                                                                                |  |  |  |

| Simple dual-port mixed width support                                              | ✓                                                                                                | ✓                                                                                                                |  |  |  |

| True dual-port mixed width support                                                | ✓                                                                                                | ✓                                                                                                                |  |  |  |

| Memory initialization file (.mif)                                                 | Not supported, except in ROM mode                                                                | Not supported                                                                                                    |  |  |  |

| Mixed-clock mode                                                                  | ✓                                                                                                | ✓                                                                                                                |  |  |  |

| Power-up condition (2)                                                            | Outputs unknown                                                                                  | Outputs unknown                                                                                                  |  |  |  |

| Register clears (3)                                                               | Output registers only                                                                            | Output registers only                                                                                            |  |  |  |

| Same-port read-during-write                                                       | New data available at positive clock edge                                                        | New data available at positive clock edge                                                                        |  |  |  |

| Mixed-port read-during-write                                                      | Outputs set to unknown or old data                                                               | Unknown output                                                                                                   |  |  |  |

| Table 2–4. HardCopy II Embedded Memory Features (Part 2 of 2) Notes (1), (2), (3) |            |              |  |  |

|-----------------------------------------------------------------------------------|------------|--------------|--|--|

| Feature                                                                           | M4K Blocks | M-RAM Blocks |  |  |

Note to Table 2-4:

- (1) Maximum performance information is preliminary until device characterization.

- (2) The memory cells power up randomly, so reads before writes are not valid. Make sure you write to the memory location before you read it.

- (3) Even though the output register is cleared, the memory cells power up randomly. So reads before write are not valid. Make sure you write to the memory location first before reading it.

- (4) Violating the setup or hold time requirements on the address registers could corrupt the memory contents. This applies to both read and write operations.

#### **Enhanced and Fast PLLs**

The number of PLLs available differs based on density (Table 2–5).

| Table 2–5. HardCopy II PLLs |        |       |       |       |       |

|-----------------------------|--------|-------|-------|-------|-------|

| Feature                     | HC210W | HC210 | HC220 | HC230 | HC240 |

| Enhanced PLLs               | 2      | 2     | 2     | 4     | 4     |

| Fast PLLs                   | 2      | 2     | 2     | 4     | 8     |

The target HardCopy II device may not support the same number of enhanced PLLs as the prototyping Stratix II FPGA. However, since HardCopy II enhanced PLLs and fast PLLs offer a similar feature set (Table 2–7 on page 2–13), a fast PLL could be used in place of an enhanced PLL. The type of PLL used in the design should be chosen using the Quartus II software to accommodate the resources available in the HardCopy II device.

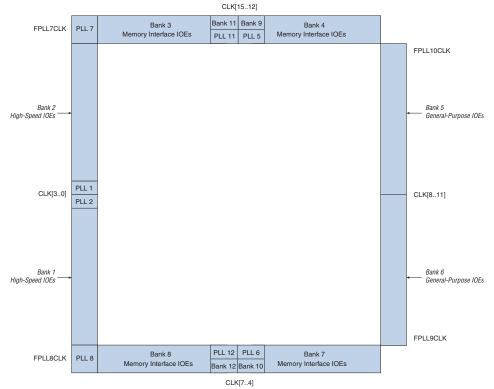

Table 2–6 shows which PLLs are available in each device density. Figure 2–3 shows the location of each PLL. During the prototyping stage using the FPGA, you must select the appropriate number of enhanced and fast PLLs that will be used in your HardCopy II device. Use Table 2–6 to ensure that the FPGA prototyping design uses the same PLL resources available in the HardCopy II device.

| Table 2–6. HardCopy II PLLs Available (Part 1 of 2) Note (1) |          |                         |   |   |   |   |   |    |          |          |    |    |

|--------------------------------------------------------------|----------|-------------------------|---|---|---|---|---|----|----------|----------|----|----|

| Dovino                                                       |          | Fast PLLs Enhanced PLLs |   |   |   |   |   |    |          |          |    |    |

| Device                                                       | 1        | 2                       | 3 | 4 | 7 | 8 | 9 | 10 | 5        | 6        | 11 | 12 |

| HC210W                                                       | <b>✓</b> | <b>✓</b>                |   |   |   |   |   |    | <b>✓</b> | <b>✓</b> |    |    |

| HC210                                                        | <b>✓</b> | <b>✓</b>                |   |   |   |   |   |    | <b>✓</b> | <b>✓</b> |    |    |

| Table 2–6. | Table 2–6. HardCopy II PLLs Available (Part 2 of 2) Note (1) |                         |          |          |          |          |          |          |          |          |          |          |

|------------|--------------------------------------------------------------|-------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Device     |                                                              | Fast PLLs Enhanced PLLs |          |          |          |          |          |          |          |          |          |          |

| Device     | 1                                                            | 2                       | 3        | 4        | 7        | 8        | 9        | 10       | 5        | 6        | 11       | 12       |

| HC220      | <b>✓</b>                                                     | <b>✓</b>                |          |          |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |

| HC230      | <b>✓</b>                                                     | <b>✓</b>                |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| HC240      | <b>✓</b>                                                     | <b>✓</b>                | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |

*Note to Table 2–6:*

(1) PLL performance in the HC210W device may differ from the Stratix II FPGA prototype.

CLK[3..0] 1 2 PLLSCLK 8

*Notes to Figure 2–3:*

- (1) The PLLs may be located in the periphery or in the core of the device.

- (2) This is the die-level top view of the device and is only a graphical representation of the PLL locations.

CLK[7..4]

PLL functionality in HardCopy II devices remains the same as in Stratix II FPGA PLLs. Therefore, the HardCopy II PLLs support PLL reconfiguration (the PLL can be dynamically configured in user mode).

HardCopy II enhanced and fast PLLs support a one-to-one mapping from Stratix II PLL resources. Table 2–7 shows the features of the different PLLs. For more information on the Stratix II PLL features, refer to the Stratix II Device Handbook.

| Table 2–7. HardCopy II PLL Features                |                                             |                                       |  |  |  |  |  |

|----------------------------------------------------|---------------------------------------------|---------------------------------------|--|--|--|--|--|

| Feature                                            | Enhanced PLL                                | Fast PLL                              |  |  |  |  |  |

| Clock multiplication and division                  | $m/(n \times post-scale counter)$ (1)       | $m/(n \times post-scale counter)$ (2) |  |  |  |  |  |

| Phase shift                                        | Down to 125-ps increments (3)               | Down to 125-ps increments (3)         |  |  |  |  |  |

| Clock switchover                                   | ✓                                           | <b>√</b> (4)                          |  |  |  |  |  |

| PLL reconfiguration                                | ✓                                           | ✓                                     |  |  |  |  |  |

| Reconfigurable bandwidth                           | ✓                                           | ✓                                     |  |  |  |  |  |

| Spread-spectrum clocking                           | ✓                                           |                                       |  |  |  |  |  |

| Programmable duty cycle                            | ✓                                           | ✓                                     |  |  |  |  |  |

| Number of clock outputs per PLL (5)                | 6                                           | 4                                     |  |  |  |  |  |

| Number of dedicated external clock outputs per PLL | Three differential or six singled-<br>ended | (6)                                   |  |  |  |  |  |

| Number of feedback clock inputs per PLL            | 1 (7)                                       |                                       |  |  |  |  |  |

Notes to Table 2-7:

- (1) For enhanced PLLs, *m* and *n* range from 1 to 512 and post-scale counters range from 1 to 512 with 50% duty cycle. For non-50% duty-cycle clock outputs, post-scale counters range from 1 to 256.

- (2) For fast PLLs, *n* can range from 1 to 4. The post-scale and *m* counters range from 1 to 32. For non-50% duty-cycle clock outputs, post-scale counters range from 1 to 16.

- (3) The smallest phase shift is determined by the voltage controlled oscillator (VCO) period divided by eight. The supported phase shift range is from 125 to 250 ps. HardCopy II devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and divide parameters. For non-50% duty cycle clock outputs post-scale counters range from 1 to 256.

- (4) HardCopy II fast PLLs only support manual clock switchover.

- (5) The clock outputs can be driven to internal clock networks or to a pin.

- (6) The PLL clock outputs of the fast PLLs can drive to any I/O pin to be used as an external clock output. For high-speed differential I/O pins, the device uses a data channel to generate the transmitter output clock (txclkout).

- (7) If the design uses external feedback input pins, you will lose one (or two, if f<sub>BIN</sub> is differential) dedicated external clock output pin.

#### **Clock Networks**

There are 16 clock pins (CLK[15..0]) in HardCopy II devices that can drive either the global- or regional-clock networks. The CLK pins can drive clock ports or data inputs.

HardCopy II devices provide 16 dedicated global-clock networks and 32 regional-clock networks; the same as in Stratix II FPGAs. These clocks are organized to provide 24 unique clock sources per device quadrant with low skew and delay. This clocking scheme provides up to 48 unique clock domains within the entire HardCopy II device. Table 2–8 lists the clock resources and features available in HardCopy II devices.

| Table 2–8. Clock Network Resources and Features Available in HardCopy II Devices |                                                                                         |  |  |  |  |

|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| Resources and Features                                                           | Availability                                                                            |  |  |  |  |

| Number of global clock networks                                                  | 16                                                                                      |  |  |  |  |

| Number of regional clock networks                                                | 32                                                                                      |  |  |  |  |

| Global clock input sources                                                       | Clock input pins, PLL outputs, logic array                                              |  |  |  |  |

| Regional clock input sources                                                     | Clock input pins, PLL outputs, logic array                                              |  |  |  |  |

| Number of unique clock sources in a quadrant                                     | 24 (16 global clocks and 8 regional clocks)                                             |  |  |  |  |

| Number of unique clock sources in the entire device                              | 48 (16 global clocks and 32 regional clocks)                                            |  |  |  |  |

| Power-down mode                                                                  | Global- and regional-clock networks, dual-regional-clock region                         |  |  |  |  |

| Clocking regions for high fan-out applications                                   | Quadrant region, dual-regional, entire device via global-<br>or regional-clock networks |  |  |  |  |

HardCopy II devices also support the same features as the Stratix II clock control block, which is available for each global- and regional-clock network. The control block has two functions:

- Clock source selection (dynamic selection for global clocks): You user can either dynamically select between two PLL outputs, between two clock pins (CLKp or CLKn), or a combination of the clock pins or PLL outputs.

- Clock power-down (dynamic clock enable or disable):

In HardCopy II devices, you can dynamically turn the clock off or on in user-mode.

# I/O Structure and Features

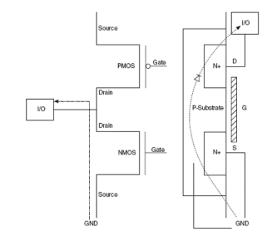

The structure and features of the HardCopy II IOE remains the same as in Stratix II. Any feature implemented in Stratix II IOEs can be migrated to Hardcopy II IOEs.

The IOE feature set in HardCopy II devices can be classified in one of three categories:

- General purpose IOEs—The most commonly used I/O type in designs.

- Memory Interface IOEs—Includes features to interface with common external memory standards.

- High-speed IOEs—Supports high-speed data transmission and reception.

All I/O pins in Stratix II FPGAs support general-purpose I/O standards, which includes the LVTTL and LVCMOS I/O standards. In Stratix II FPGAs, the PCI clamping diode and memory interfaces are supported on the top and bottom I/O pins, while high-speed interfaces are supported on the left and right side I/O pins of the device.

The new general purpose IOEs in HardCopy II devices are a cost saving and area efficient advantage. The complex memory interface and the high-speed IOE circuitry is removed to save die area while still offering the more commonly-used features. The memory interface IOE supports all the features available in the general purpose IOE. The high-speed IOE also supports all the same features and I/O standards as the general purpose IOE, except for the PCI clamping diode (supported on the bottom general purpose IOEs in HC210 and HC220 devices).

In order to increase the I/O area efficiency of HardCopy II devices, the features available on any given IOE depends on the location.

Table 2–9 shows which I/O standards are supported by the different IOE types.

| Table 2–9. HardCopy II Supported I/O Standards (Part 1 of 3) |                       |                      |          |                   |              |                    |  |

|--------------------------------------------------------------|-----------------------|----------------------|----------|-------------------|--------------|--------------------|--|

| I/O Standard                                                 | Tuno                  | V <sub>CCIO</sub> Le | evel (V) | Memory            | General      | High-Speed<br>IOEs |  |

| I/O Standard                                                 | Туре                  | Input                | Output   | Interface<br>IOEs | Purpose IOEs |                    |  |

| 3.3-V LVTTL/<br>LVCMOS                                       | Single-ended          | 3.3/2.5              | 3.3      | ✓                 | ~            | ~                  |  |

| 2.5-V LVTTL/<br>LVCMOS                                       | Single-ended          | 3.3/2.5              | 2.5      | ✓                 | ~            | ~                  |  |

| 1.8-V LVTTL/<br>LVCMOS                                       | Single-ended          | 1.8/1.5              | 1.8      | ✓                 | ~            | ~                  |  |

| 1.5-V LVCMOS                                                 | Single-ended          | 1.8/1.5              | 1.5      | ✓                 | ✓            | ✓                  |  |

| SSTL-2 class I                                               | Voltage<br>referenced | 2.5                  | 2.5      | ✓                 |              |                    |  |

| Table 2–9. HardCopy II Supported I/O Standards (Part 2 of 3) |                            |                      |          |                   |              |            |  |

|--------------------------------------------------------------|----------------------------|----------------------|----------|-------------------|--------------|------------|--|

|                                                              | _                          | V <sub>CCIO</sub> Le | evel (V) | Memory            | General      | High-Speed |  |

| I/O Standard                                                 | Туре                       | Input                | Output   | Interface<br>IOEs | Purpose IOEs | IOEs       |  |

| SSTL-2 class II                                              | Voltage referenced         | 2.5                  | 2.5      | <b>✓</b>          |              |            |  |

| SSTL-18 class I                                              | Voltage<br>referenced      | 1.8                  | 1.8      | ✓                 |              |            |  |

| SSTL-18 class II                                             | Voltage referenced         | 1.8                  | 1.8      | <b>✓</b>          |              |            |  |

| 1.8-V HSTL class I                                           | Voltage referenced         | 1.8                  | 1.8      | ✓                 |              |            |  |

| 1.8-V HSTL class II                                          | Voltage referenced         | 1.8                  | 1.8      | ✓                 |              |            |  |

| 1.5-V HSTL Class I                                           | Voltage<br>referenced      | 1.5                  | 1.5      | ✓                 |              |            |  |

| 1.5-V HSTL Class II                                          | Voltage<br>referenced      | 1.5                  | 1.5      | <b>✓</b>          |              |            |  |

| PCI/PCI-X                                                    | Single-ended               | 3.3                  | 3.3      | <b>√</b> (2)      | <b>√</b> (2) |            |  |

| Differential SSTL-2<br>class I and II input                  | Pseudo<br>differential (1) | 3.3/2.5/<br>1.8/1.5  |          | (3)               |              |            |  |

| Differential SSTL-2 class I and II output                    | Pseudo<br>differential (1) |                      | 2.5      | (3)               |              |            |  |

| Differential SSTL-18 class I and II input                    | Pseudo<br>differential (1) | 3.3/2.5/<br>1.8/1.5  |          | (3)               |              |            |  |

| Differential SSTL-18 class I and II output                   | Pseudo<br>differential (1) |                      | 1.8      | (3)               |              |            |  |

| 1.8-V differential<br>HSTL class I and II<br>input           | Pseudo<br>differential (1) | 3.3/2.5/<br>1.8/1.5  |          | (3)               |              |            |  |

| 1.8-V differential<br>HSTL class I and II<br>output          | Pseudo<br>Differential (1) |                      | 1.8      | (3)               |              |            |  |

| 1.5-V differential<br>HSTL class I and II<br>input           | Pseudo<br>differential (1) | 3.3/2.5/<br>1.8/1.5  |          | (3)               |              |            |  |

| 1.5-V differential<br>HSTL class I and II<br>output          | Pseudo<br>Differential (1) |                      | 1.5      | (3)               |              |            |  |

| LVDS                                                         | Differential               | 2.5                  | 2.5      | (5)               | (4), (6)     | <b>✓</b>   |  |

| HyperTransport™<br>technology                                | Differential               | 2.5                  | 2.5      | (5)               | (4), (6)     | <b>✓</b>   |  |

| Table 2–9. HardCopy II Supported I/O Standards (Part 3 of 3) |              |                      |          |                   |              |            |  |  |

|--------------------------------------------------------------|--------------|----------------------|----------|-------------------|--------------|------------|--|--|

| 1/0 0111                                                     | Tuno         | V <sub>CCIO</sub> Le | evel (V) | Memory            | General      | High-Speed |  |  |

| I/O Standard                                                 | Туре         | Input                | Output   | Interface<br>IOEs | Purpose IOEs | IOEs       |  |  |

| LVPECL                                                       | Differential | 3.3/2.5/<br>1.8/1.5  | (8)      | (8)               | (8)          |            |  |  |

Notes to Table 2-9:

- (1) Pseudo-differential HSTL and SSTL inputs only use the positive-polarity input in the speed path. The negative input is not connected internally. Pseudo-differential HSTL and SSTL outputs use two single-ended outputs with the second output programmed as inverted. This is similar to a Stratix II device implementation.

- (2) The PCI clamping diode is only supported on the I/O pins on the top and bottom sides of the device.

- (3) This I/O standard is only supported on the DQS, CLK and PLL FB input pins or on the PLL OUT output pins.

- (4) This I/O standard is only supported on the bottom CLK and PLL\_FB input pins or on the bottom PLL\_OUT output pins.

- (5) This I/O standard is only supported on the CLK and PLL FB input pins or on the PLL OUT output pins.

- (6) Also supported on CLK9 and CLK11 pins.

- (7) This I/O standard is only supported on CLK and PLL FB input pins.

- (8) LVPECL input I/O standard is supported on the top and bottom CLK and PLL\_FB input pins. LVPECL output I/O standard is supported on the top and bottom PLL\_OUT output pins. LVPECL support is similar to Stratix II devices.

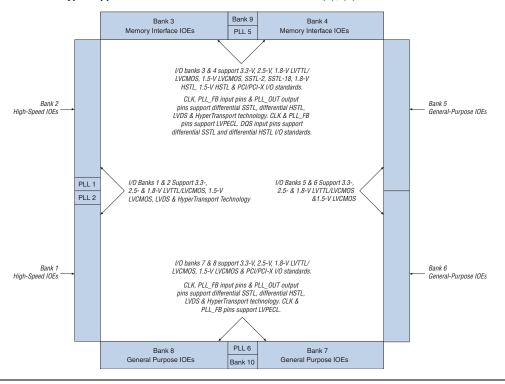

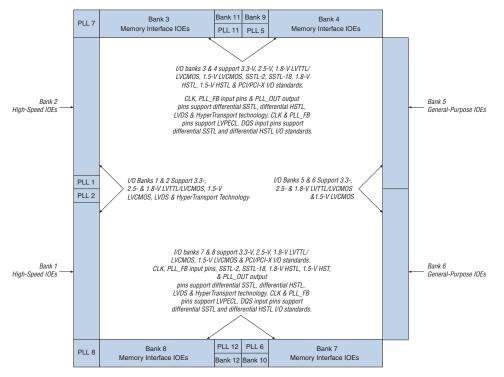

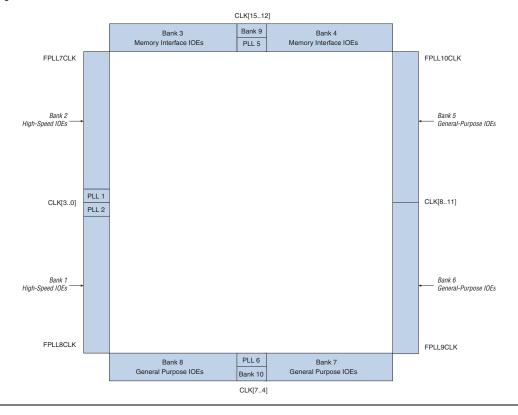

The three types of IOEs are located in different areas of the device and are described in the following sections. HardCopy II devices have eight I/O banks, just as in Stratix II FPGAs. Figures 2–4 through 2–6 show which I/O type each bank supports.

Figure 2–4. I/O Type Support in HC210 and HC220 Devices Notes (1), (2)

Figure 2–5. I/O Type Support in HC230 Devices Notes (1), (2)

Figure 2–6. I/O Type Support in HC240 Devices Notes (1), (2)

*Notes to Figures 2–4 through 2–6:*

- (1) In addition to supporting external memory interfaces, memory interface IOEs have the same features as general purpose IOEs. In addition to supporting high-speed I/O interfaces, high-speed IOEs have the same features as general purpose IOEs, except for the PCI clamping diode and LVPECL clock input support.

- (2) This is a top view of the silicon die which corresponds to a reverse view for flip-chip packages. It is a graphical representation only.

When planning I/O placement for designs targeting HardCopy II devices, care should be taken to ensure the same I/O standards are supported in the same HardCopy II I/O banks as in the Stratix II I/O banks.

### **General Purpose IOE**

The general purpose IOEs in HC210 and HC220 devices are located on the right side and at the bottom of the device. The general purpose IOEs in HC230 devices are located on the right side of the device. (Directions are based on a top view of the silicon die.) HC240 devices do not have general purpose IOEs. The general purpose IOE functionality is supported in the memory interface IOEs for these devices. The high-speed IOEs also

provide the same features as the general purpose IOEs except for the PCI clamping diode. In Stratix II FPGAs, all IOEs support the general purpose IOE features except the PCI diode, which is only supported on the top and bottom I/O pins.

The general purpose IOE has many features, including:

- Dedicated single-ended I/O buffers

- 3.3-V, 64-bit, 66 MHz PCI compliance

- 3.3-V, 64-bit, 133 MHz PCI-X 1.0 compliance

- JTAG boundary-scan test (BST) support

- On-chip driver series termination (non-calibrated)

- Output drive strength control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Open-drain outputs

- PCI clamping diode (supported on the bottom I/O pins only)

- Double data rate (DDR) registers

General purpose IOEs support the following I/O standards:

- 3.3-V LVTTL/LVCMOS

- 2.5-V LVTTL/LVCMOS

- 1.8-V LVTTL/LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI

- 3.3-V PCI-X mode 1

The general purpose CLK and PLL\_FB input pins and the PLL\_OUT output pins support the following I/O standards:

- LVDS

- HyperTransport technology

- LVPECL (on input clocks and PLL OUT only)

The programmable drive strengths available vary depending on the I/O standard being used and are listed in Table 2–10.

| Table 2–10. Programmable Drive Strength Support for General-Purpose IOEs (Part 1 of 2) |                                          |  |  |  |  |  |

|----------------------------------------------------------------------------------------|------------------------------------------|--|--|--|--|--|

| I/O Standard                                                                           | Programmable Drive Strength Options (mA) |  |  |  |  |  |

| 3.3-V LVTTL                                                                            | 4, 8, 12                                 |  |  |  |  |  |

| 3.3-V LVCMOS                                                                           | 4, 8                                     |  |  |  |  |  |

| 2.5-V LVTTL/LVCMOS                                                                     | 4, 8, 12                                 |  |  |  |  |  |

| Table 2–10. Programmable Drive Strength Support for General-Purpose IOEs (Part 2 of 2) |                                          |  |  |  |  |

|----------------------------------------------------------------------------------------|------------------------------------------|--|--|--|--|

| I/O Standard                                                                           | Programmable Drive Strength Options (mA) |  |  |  |  |

| 1.8 V LVTTL/LVCMOS                                                                     | 2, 4, 6, 8                               |  |  |  |  |

| 1.5 V LVCMOS                                                                           | 2, 4                                     |  |  |  |  |

General purpose IOEs support non-calibrated on-chip series termination. 50- and 25- $\Omega$  on-chip series termination is available for 3.3-V or 2.5-V I/O standards. 50- $\Omega$  on-chip series termination is available for 1.8- and 1.5-V I/O standards (pending characterization).

#### **Memory Interface IOE**

Memory interface IOEs in HC210 and HC220 devices are located on the top of the device. Memory interface IOEs in HC230 and HC240 devices are located on the top and the bottom of the device. In Stratix II FPGAs, the top and bottom IOEs support the memory interface IOE features.

The memory interface IOE has many features, including:

- Dedicated single-ended I/O buffers

- 3.3-V, 64-bit, 66 MHz PCI compliance

- 3.3-V, 64-bit, 133 MHz PCI-X 1.0 compliance

- JTAG BST support

- On-chip driver series termination

- V<sub>REF</sub> pins

- Output drive strength control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Open-drain outputs

- PCI clamping diode

- DQ and DQS I/O pins

- Double data rate (DDR) registers

The following I/O standards are supported when using the memory interface IOEs and can be used to interface to external memory, including DDR and DDR2 SDRAM, and QDRII, RLDRAM II, and SDR SRAM:

- 3.3-V LVTTL/LVCMOS

- 2.5-V LVTTL/LVCMOS

- 1.8-V LVTTL/LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI

- 3.3-V PCI-X mode 1

- SSTL-2 class I and II

- SSTL-18 class I and II

- 1.8-V HSTL class I and II

- 1.5-V HSTL class I and II

The memory interface DQS, CLK, and PLL\_FB input pins and the PLL\_OUT output pins support the following I/O standards:

- LVTTL/LVCMOS

- SSTL-2 class I and II

- SSTL-18 class I and II

- 1.8-V HSTL class I and II

- 1.5-V HSTL class I and II

- Differential SSTL-2 class I and II

- Differential SSTL-18 class I and II

- 1.8-V differential HSTL class I and II

- 1.5-V differential HSTL class I and II

- LVDS (not supported on DQS pins)

- HyperTransport technology (not supported on DQS pins)

- LVPECL on input clocks and PLL\_OUT only (not supported on DQS pins)

Pseudo-differential HSTL and SSTL inputs are supported on clock and DQS pins, while outputs are supported on dedicated PLL\_OUT and DQS pins. Pseudo-differential HSTL and SSTL I/O standards use two single-ended outputs with the second output programmed as inverted. Pseudo-differential HSTL and SSTL inputs treat differential inputs as two single-ended HSTL and SSTL inputs and only decode one of them. This I/O support is the same as in Stratix II FPGAs.

The functionality of all DQS circuitry in HardCopy II devices is the same as in Stratix II FPGAs. Table 2–11 shows the number of DQS/DQ groups supported in each HardCopy II device density and package.

| Table 2-1 | Table 2–11. DQS and DQ Bus Mode Support (Part 1 of 2) |                        |                           |                          |                             |  |  |  |

|-----------|-------------------------------------------------------|------------------------|---------------------------|--------------------------|-----------------------------|--|--|--|

| Device    | Package                                               | Number of ×4<br>Groups | Number of ×8/×9<br>Groups | Number of ×16/×18 Groups | Number of<br>×32/×36 Groups |  |  |  |

| HC210W    | 484-pin FineLine BGA<br>(Wire Bond)                   | 4                      | 2                         | 0                        | 0                           |  |  |  |

| HC210     | 484-pin FineLine BGA                                  | 4                      | 2                         | 0                        | 0                           |  |  |  |

| HC220     | 672-pin FineLine BGA                                  | 9                      | 4                         | 2                        | 0                           |  |  |  |

|           | 780-pin FineLine BGA                                  | 9                      | 4                         | 2                        | 0                           |  |  |  |

| HC230     | 1,020-pin FineLine BGA                                | 36                     | 18                        | 8                        | 4                           |  |  |  |

| Table 2–11. DQS and DQ Bus Mode Support (Part 2 of 2) |                        |                        |                           |                          |                             |  |  |

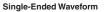

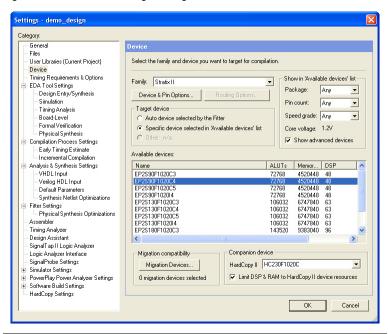

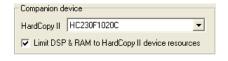

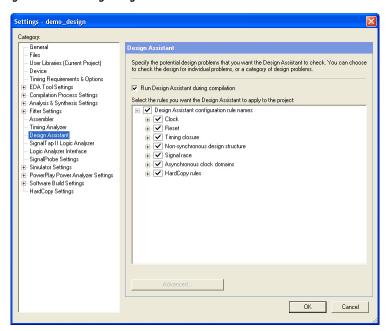

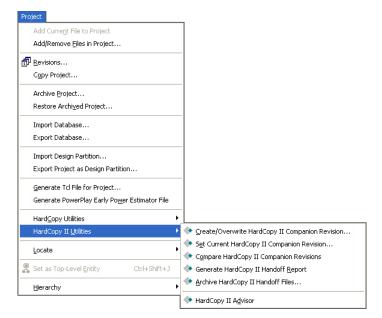

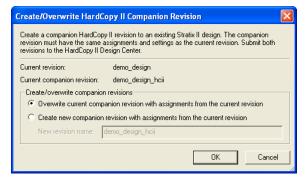

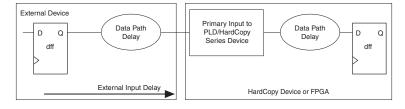

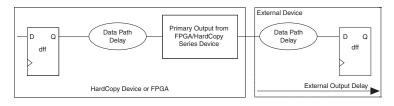

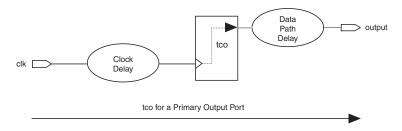

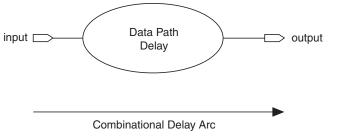

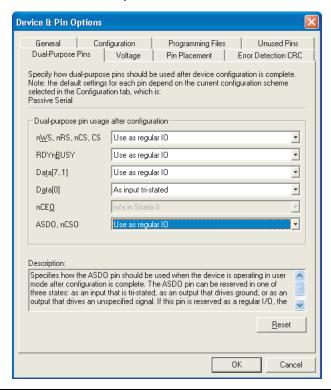

|-------------------------------------------------------|------------------------|------------------------|---------------------------|--------------------------|-----------------------------|--|--|