Memory Page NMOS ROMs IM7332 IM7364 2-18 2-21 CMOS EPROMs IM6653/4 2-11

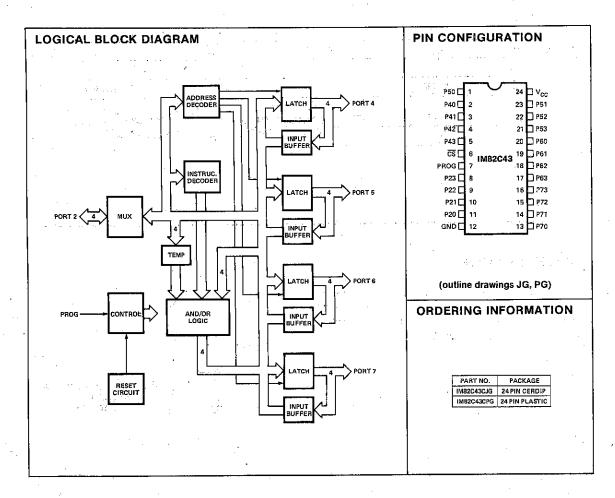

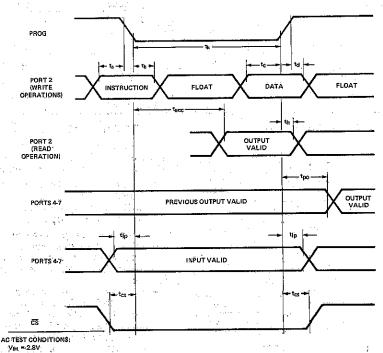

Peripherals IM6402/3 82C43 2-24

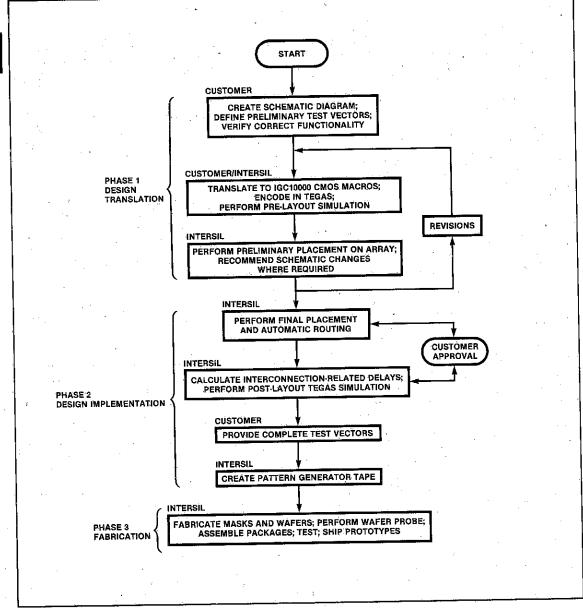

Gate Arrays IGC10000

2-28

#### DIGITAL

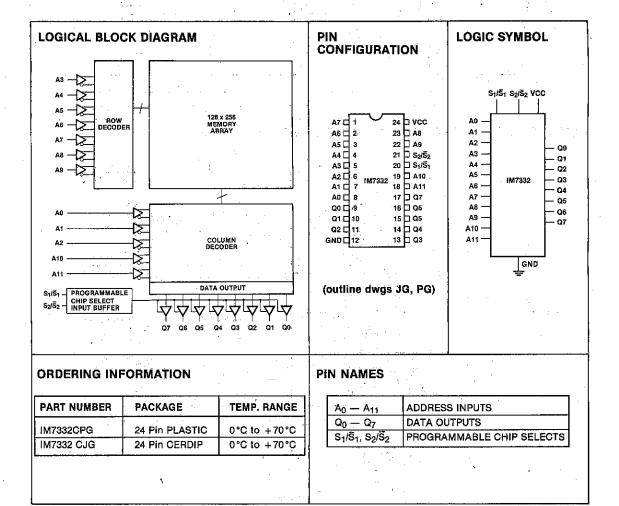

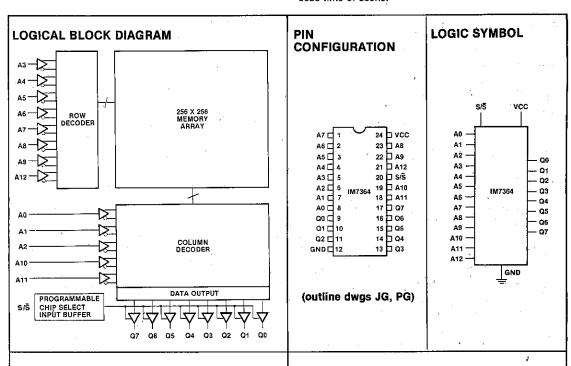

| ROMs               |                      |             |          |          |             |

|--------------------|----------------------|-------------|----------|----------|-------------|

| Organization       | Max Access Time (ns) | IDD Max(mA) | No. Pins | Package* | Temp Range* |

| 4096 x 8<br>1M7332 | 300                  | 80          | 24       | J,P      | С           |

| 8192 x 8<br>1M7364 | 350                  | 150         | 24       | J,P      | С           |

## **EPROMs**

| Organiza                      | alion | Max Access<br>Time (ns) | <b>V</b> oc<br>(V) | loc Max (mA)<br>Operating | Ico Max ("A)<br>Standby | No. Pins | Package* | Temp Range                  |

|-------------------------------|-------|-------------------------|--------------------|---------------------------|-------------------------|----------|----------|-----------------------------|

| 1024 x 4<br>IM6653<br>IM6653A |       | 550<br>300              | 5<br>10            | 6<br>12                   | 140<br>140              | 24<br>24 | J .      | <b>I,M</b><br>1, <b>M</b> , |

| 512 x 8<br>IM6654<br>IM6654A  |       | 550<br>300              | 5<br>10            | 6<br>12                   | 140<br>140              | 24<br>24 | J        | I,M<br>I,M                  |

## PERIPHERAL

#### IM8048 Paripheral

IM82C43 - CMOS 1/O Exponder

\*Package and Temperature Key

F—Flatpack

J—Ceramic Dual In-Line

P—Plastic Dual in-Line

D-Ceramic Side Brazed (Not Recommended for High Volume)

## **UARTS**

| Part Number | * Max.<br>Clock<br>Frequency | XTAL<br>Frequency | V Supply | I <sub>CC</sub> Max. |

|-------------|------------------------------|-------------------|----------|----------------------|

| IM6402      | 1,0 MHz                      |                   | 5.0      | 1,2 mA               |

| IM6402A     | 4.0 MHz                      | _                 | 4-11     | 9.0 mA               |

| IM6402-1    | 2.0 MHz                      | ·                 | 5.0      | 1.9 mA               |

| IM6403      | 2.46 MHz                     | 2.46 MHz          | 5.0      | 3.7 mA               |

| IM6403A     | 6.0 MHz                      | 6.0 MHz           | 4-11     | 13.0 mA              |

| IM6403-1    | 3.58 MHz                     | 3.58 MHz          | 5.0      | 5.5 mA               |

## **GATE ARRAYS**

| Part Number          | Delay  | înput Nand<br>Gate Equivalent | I/O<br>Cells | V <sub>CC</sub> |

|----------------------|--------|-------------------------------|--------------|-----------------|

| 10010109             | 6 ns · | 408                           | 34           | 3-9V            |

| IGC10408             | 6 ns   | 756                           | 44           | 3-9V            |

| IGC10756<br>IGC11500 | 6 ns   | 1500                          | 62           | 3-9V            |

| IGC12001             | 6 пѕ   | 2001                          | 70           | 3-9V            |

# IM6402/IM6403 Universal Asynchronous Receiver Transmitter (UART)

#### **FÉATURES**

"See Table 1

- Low Power Less Than 10mW Typ, at 2MHz

- Operation Up to 4MHz Clock (IM6402A)

- Programmable Word Length, Stop Bits and Parity

- Automatic Data Formatting and Status Generation

- Compatible with Industry Standard UART's (IM6402)

- On-Chip Oscillator with External Crystal (IM6403)

- Operating Voltage IM6402-1/03-1: 5V IM6402A/03A: 4-11V IM6402/03: 5V

#### PIN CONFIGURATION (outline dwg DL, PL) 39 DEPE 38 DCLS1 37 DCLS2 36 DSBS 35 DPI GND B RBR8 0 5 TABLE 1. RBR6 [ 7 34 CAL 33 D.TBR8 PIN IM6402 IM6403 w/XTAL IM6403 w/EXT CLOCK RBR3 C 10 RBR3 C 10 RBR3 C 11 RBR1 C 12 -N/C 32 TBR7 Divide Control. Divide.Control 17 BBC External Clock Input XTAL 30 C TBR5 29 C TBR4 28 C TBR3 27 C TBR2 19 Tri-Stat Always Active Always Active 22 Tri-State Always Active Always Active PE 13 40 TRC GND XTAL 26 TBR1 25 TRO OE 🗆 15 SPORT 16 24 TRE 0RR | 18 RRI 20

#### **GENERAL DESCRIPTION**

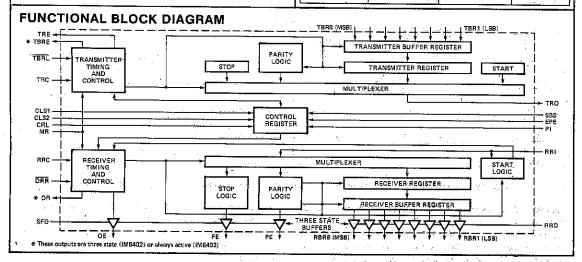

The IM6402 and IM6403 are CMOS/LSI UART's for interfacing computers or microprocessors to asynchronous serial data channels. The receiver converts serial start, data, parity and stop bits to parallel data verifying proper code transmission, parity, and stop bits. The transmitter converts parallel data into serial form and automatically adds start, parity, and stop bits.

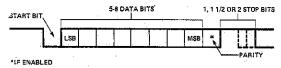

The data word length can be 5, 6, 7 or 8 bits. Parity may be odd or even, and parity checking and generation can be inhibited. The stop bits may be one or two (or one and one-half when transmitting 5 bit code). Serial data format is shown in Figure 6.

The IM6402 and IM6403 can be used in a wide range of applications including modems, printers, peripherals and remote data acquisition systems. CMOS/LSI technology permits clock frequencies up to 4,0MHz (250K Baud), an improvement of 10 to 1 over previous PMOS UART designs. Power requirements, by comparison, are reduced from 670mW to 10mW. Status logic increases flexibility and simplifies the user interface.

The M6402 differs from the IM6403 in the use of five device pins as indicated in Table 1 and Figure 1.

#### ORDERING INFORMATION ORDER CODE 4M6402-1/03-1 IMB402A/03A IMBA02/03 PLASTIC PKG IM6402-1/03-1IPL IM6402/03-AIPL IM6402/03-IPL CERAMIC PKG IM6402-1/03-1IDL 1M6402/03-AIDL IM6402/03IDL MILITARY TEMP IM6402-1/03-1MDL IM6402/03.4 MDJ MILITARY TEMP IM6402/03-AMDL/ IM6402-1/03-1 WITH 883B

# IM6402/IM6403 IM6402/IM6403

#### **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature               | ,                           |

|-------------------------------------|-----------------------------|

| IM6402/03                           | -40°C to +85°C              |

| Storage Temperature                 | -65°C to 150°C              |

| Operating Voltage                   | 4.0V to 7.0V                |

| Supply Voltage                      | +8.0V                       |

| Voltage On Any Input or Output Pin0 | 3V to V <sub>CC</sub> +0.3V |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

#### D.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 5.0 \pm 10\%$ ,  $T_A = -40$ °C to +85°C

|     | SYMBOL | PARAMETER                           | CONDITIONS                                                                   | MIN                  | TYP | MÁX  | UNITS |

|-----|--------|-------------------------------------|------------------------------------------------------------------------------|----------------------|-----|------|-------|

| 1   | ViH    | Input Voltage High                  |                                                                              | V <sub>CC</sub> -2.0 |     |      | V     |

| 2   | VIL    | Input Voltage Low                   |                                                                              |                      |     | 0.8  | V     |

| 3   | Iμ     | Input Leakage[1]                    | GND <vin<vcc< td=""><td>-5.0</td><td></td><td>5.0</td><td>μΑ</td></vin<vcc<> | -5.0                 |     | 5.0  | μΑ    |

| 4   | VoH    | Output Voltage High                 | l <sub>OH</sub> = -0.2mA                                                     | 2.4                  |     |      | V     |

| . 5 | VoL    | Output Voltage Low                  | I <sub>OL</sub> =1.6mA                                                       |                      |     | 0,45 | V     |

| 6   | OLK    | Output Leakage                      | GND <v<sub>OUT<v<sub>CC</v<sub></v<sub>                                      | -5.0                 |     | 5.0  | μA    |

| 7   | lcc    | Power Supply Current Standby        | VIN=GND or VCC                                                               |                      | 1.0 | 800  | μΑ    |

| .8  | Icc    | Power Supply Current IM6402 Dynamic | f <sub>0</sub> = 500 KHz                                                     |                      |     | 1,2  | mA_   |

| . 9 | 1cc    | Power Supply Current IM6403 Dynamic | f <sub>crystal</sub> = 2.46MHz                                               |                      |     | 3.7  | mΑ    |

| 10* | CIN    | Input Capacitance[1]                |                                                                              | 1                    | 7.0 | 8.0  | þЕ    |

| 11  | CO     | Output Capacitance[1]               | **                                                                           |                      | 8.0 | 10.0 | рF    |

NOTE 1: Except IM6403 XTAL input pins (i.e. pins 17 and 40).

NOTE 2: VCC = 5V, TA = 25°C.

#### A.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 5.0V \pm 10\%$ ,  $C_L = 50pF$ ,  $T_A = -40$ °C to +85°C

|              | SYMBOL               | PARAMETER                   | CONDITIONS          | MIN  | TYP | MAX  | STINU |

|--------------|----------------------|-----------------------------|---------------------|------|-----|------|-------|

| 1            | ₹ <sub>c</sub>       | Clock Frequency IM6402      | 7                   | D.C. |     | 1.0  | MHz   |

| 2            | f <sub>crystal</sub> | Crystal Frequency IM6403    | •                   |      |     | 2.46 | . MHz |

| 3            | tow                  | Pulse Widths CRL, DRR, TBRL | •                   | 225  | 50  |      | ńs    |

| 4            | tmr                  | Pulse Width MR              | See Timing Diagrams | 600  | 200 |      | ns    |

| 5            | t <sub>ds</sub>      | Input Data Setup Time       | (Figures 2,3,4)     | 75   | 20  |      | ns    |

| 6            | tdh                  | Input Data Höld Time        |                     | 90   | 40  |      | ns    |

| <del>7</del> | ten                  | Output Enable Time          |                     |      | 80  | 190  | ns ·  |

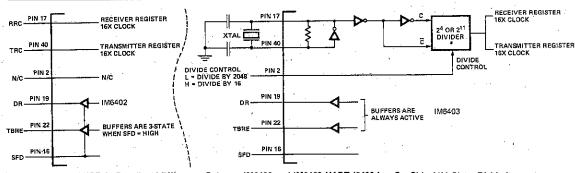

FIGURE 1. Functional Difference Between IM6402 and IM6403 UART (6403 has On-Chip 4/11 Stage Divider)

The IM6403 differs from the IM6402 on three Inputs (RRC, TRC, pin 2) as shown in Figure 1. Two outputs (TBRE, DR) are not three-state as on the IM6402, but are always active. The on-chip divider and oscillator allow an inexpensive crystal to be used as a timing source rather than additional circuitry such

as baud rate generators. For example, a color TV crystal at 3.579545MHz results in a baud rate of 109.2Hz for an easy teletype interface (Figure 10). A 9600 baud interface may be implemented using a 2.4576MHz crystal with the divider set to divide by 16.

2

## IM6402/IM6403 IM6402A/IM6403A

#### **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature               | 5.7                           |

|-------------------------------------|-------------------------------|

| Industrial IM6402AI/03AI            |                               |

| Military IM6402AM/03AM              | -55°C to +125°C               |

| Storage Temperature                 | -65°C to 150°C                |

| Operating Voltage                   | 4.0V to 11.0V                 |

| Supply Voltage                      | +12.0V                        |

| Voltage On Any Input or Output Pin( | 0.3V to V <sub>CC</sub> +0.3V |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

#### D.C. CHARACTERISTICS

TEST CONDITIONS: V<sub>CC</sub> = 4.0V to 11.0V, T<sub>A</sub> = Industrial or Military

|    | SYMBOL          | PARAMETER                            | CONDITIONS                              | MIN                   | TYP <sup>2</sup> | MAX                 | UNITS |

|----|-----------------|--------------------------------------|-----------------------------------------|-----------------------|------------------|---------------------|-------|

| 1  | V <sub>IH</sub> | Input Voltage High                   |                                         | 70% V <sub>CC</sub>   | 1                |                     | V     |

| 2  | V <sub>IL</sub> | Input Voltage Low                    |                                         |                       |                  | 20% V <sub>CC</sub> | V     |

| 3  | İμ              | Input Leakage[1]                     | GND≤V <sub>IN</sub> ≤V <sub>CC</sub>    | -1.0                  | 4                | 1.0                 | μА    |

| 4  | Voн             | Output Voltage High                  | I <sub>OH</sub> = 0mA                   | V <sub>CC</sub> -0.01 |                  |                     | V     |

| 5  | VoL             | Output Voltage Low                   | I <sub>OL</sub> = 0mA                   |                       |                  | GND+0.01            | ν     |

| 6  | lolk            | Output Leakage                       | GND <v<sub>OUT<v<sub>CC</v<sub></v<sub> | -1.0                  |                  | 1.0                 | μA    |

| 7  | Icc             | Power Supply Current Standby         | V <sub>IN</sub> =GND or V <sub>CC</sub> |                       | 5.0              | 500                 | μΑ    |

| 8  | Icc             | Power Supply Current IM6402A Dynamic | f <sub>c</sub> =4MHz                    |                       |                  | 9.0                 | mA    |

| 9  | lcc             | Power Supply Current IM6403A Dynamic | f <sub>crystal</sub> = 3.58MHz          |                       | ,                | 13.0                | mA    |

| 10 | c <sub>IN</sub> | Input Capacitance[1]                 |                                         |                       | 7.0              | 8.0                 | pF    |

| 11 | ¢ <sub>O</sub>  | Output Capacitance[1]                |                                         | -                     | 8.0              | 10.0                | рF    |

NOTE 1: Except IM6403 XTAL input pins (i.e. pins 17 and 40).

NOTE 2: V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

#### A.C. CHARACTERISTICS

**TEST CONDITIONS:**  $V_{CC} = 10.0V \pm 5\%$ ,  $C_L = 50pF$ ,  $T_A = Industrial or Military$

|    | SYMBOL          | PARAMETER                   | CONDITIONS          | MIN  | TYP <sup>2</sup> | MAX     | UNITS |

|----|-----------------|-----------------------------|---------------------|------|------------------|---------|-------|

| 1  | fc              | Clock Frequency IM6402A     |                     | D.C. |                  | 4.0     | MHz   |

| 2  | fcrystál        | Crystal Frequency IM6403A   |                     |      |                  | 6.0     | MHz   |

| 3  | tpw             | Pulse Widths CRL, DRR, TBRL |                     | 100  | 40               | 7       | ns .  |

| 4  | tmr             | Pulse Width MR              | See Timing Diagrams | 400  | 200              |         | ns    |

| .5 | t <sub>ds</sub> | Input Data Setup Time       | (Figures 2,3,4)     | . 40 | 0                | 1 - 1 - | ns    |

| 6  | <sup>t</sup> dh | Input Data Hold Time        |                     | 30   | 30               |         | пз    |

| 7  | t <sub>en</sub> | Output Enable Time          | ]                   |      | 40               | 70      | ns    |

#### TIMING DIAGRAMS

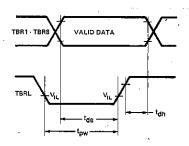

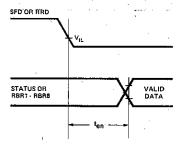

FIGURE 2. Data input Cycle

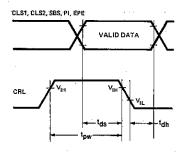

FIGURE 3. Control Register Load Cycle

FIGURE 4. Status Flag Enable Time or Data Output Enable Time

# IM6402/IM6403

#### IM6402-1/IM6403-1

#### **ABSOLUTE MAXIMUM RATINGS**

Operating Temperature

-40°C to +85°C

Industrial IM6402-1I/03-1I

-40°C to +85°C

Military IM6402-1M/03-1M

-55°C to +125°C

Storage Temperature

-65°C to +150°C

Operating Voltage

4.0V to 7.0V

Supply Voltage

+8.0V

Voltage On Any Input or Output Pin

-0.3V to Vcc +0.3V

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent device failure. These are stress ratings only and functional operation of the devices at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may cause device failures.

# 2

#### D.C. CHARACTERISTICS

**TEST CONDITIONS:**  $V_{CC} = 5.0 \pm 10\%$ ,  $T_A = Industrial or Military$

|      | SYMBOL          | PARAMETER                           | CONDITIONS                              | MIN                  | TYP2 | MAX  | UNITS |

|------|-----------------|-------------------------------------|-----------------------------------------|----------------------|------|------|-------|

| -1   | V <sub>1H</sub> | Input Voltage High                  | •                                       | V <sub>CC</sub> -2.0 |      |      | ٧     |

| 2    | VIL             | Input Voltage Low                   |                                         |                      |      | 0.8  | ٧     |

| 3    | JiL             | Input Leakage[1]                    | GND SVINSVCC                            | -1,0                 |      | 1.0  | μА    |

| 4    | ∨он .           | Output Voltage High                 | I <sub>OH</sub> =-0.2mA                 | 2.4                  |      |      | V     |

| 5    | VOL             | Output Voltage Low                  | I <sub>OL</sub> = 2.0mA                 |                      |      | 0.45 | V     |

| 6    | TOLK            | Output Leakage                      | GND <v<sub>QUT<v<sub>CC</v<sub></v<sub> | -1.0                 |      | 1.0  | μА    |

| 7    | ¹cc             | Power Supply Current Standby        | V <sub>IN</sub> =GND or V <sub>CC</sub> |                      | 1.0  | 100  | μА    |

| 8    | Icc             | Power Supply Current IM6402 Dynamic | f <sub>c</sub> = 2MHz                   |                      |      | 1.9  | · mA  |

| 9    | Icc             | Power Supply Current IM6403 Dynamic | f <sub>crystal</sub> = 3.58MHz          |                      |      | -5.5 | mΑ    |

| 10 " | CIN             | Input Capacitance[1]                |                                         |                      | 7.0  | 8.0  | рF    |

| 71   | c <sub>o</sub>  | Output Capacitance[1]               | T                                       |                      | 8,0  | 10.0 | рF    |

NOTE 1: Except IM6403 XTAL input pins (i.e. pins 17 and 40).

**NOTE 2:**  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

#### A.C. CHARACTERISTICS

TEST CONDITIONS:  $V_{CC} = 5.0V \pm 10\%$ ,  $C_L = 50pF$ ,  $T_A = Industrial or Military$

|   | SYMBOL          | PARAMETER                   | CONDITIONS          | MIN  | түр2 | MAX  | UNITS |

|---|-----------------|-----------------------------|---------------------|------|------|------|-------|

| 1 | fc              | Clock Frequency IM6402      | 1.                  | D.C. |      | 2.0  | MHz   |

| 2 | forystal        | Crystal Frequency IM6403    |                     |      |      | 3.58 | MHz   |

| 3 | t <sub>pw</sub> | Pulse Widths CRL, DRR, TBRL |                     | 150  | 50   | -    | ns    |

| 4 | tmr             | Pulse Width MR              | See Timing Diagrams | 400  | 200  | ,    | ns    |

| 5 | t <sub>ds</sub> | Input Data Setup Time       | (Figures 2,3,4)     | 50   | 20   |      | ns    |

| 6 | t <sub>dh</sub> | Input Data Hold Time        |                     | 60   | 40   |      | ns    |

| 7 | t <sub>en</sub> | Output Enable Time          |                     |      | 80   | 160  | n\$   |

## IM6402/IM6403

\*DIFFERS BETWEEN IM6402 AND IM6403:

FIGURE 5. Pin Configuration

## **IM6403 FUNCTIONAL PIN DEFINITION**

| PIN | SYMBOL                       | DESCRIPTION                                                                                                                                                                                                                          |

|-----|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | v <sub>cc</sub>              | Positive Power Supply                                                                                                                                                                                                                |

| 2   | IM6402-N/C<br>IM6403-Control | No Connection<br>Divide Control<br>High: 2 <sup>4</sup> (16) Divider<br>Low: 2 <sup>11</sup> (2048) Divider                                                                                                                          |

| 3   | GND                          | Ground                                                                                                                                                                                                                               |

| 4   | RRD                          | A high level on RECEIVER REGISTER DISABLE forces the receiver holding register outputs RBR1-RBR8 to a high impedance state.                                                                                                          |

| 5   | RBR8                         | The contents of the RECEIVER BUFFER REGISTER appear on these three-state outputs. Word formats less than 8 characters are right justified to RBR1.                                                                                   |

| 6   | RBR7                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 7   | RBR6                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 8   | RBR5                         | See Pin 5"— RBR8                                                                                                                                                                                                                     |

| - 9 | RBR4                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 10  | RBR3                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 11  | RBR2                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 12  | RBR1                         | See Pin 5 — RBR8                                                                                                                                                                                                                     |

| 13  | PE .                         | A high-level on PARITY ERROR indicates that the received parity does not match parity programmed by control bits. The output is active until parity matches on a succeeding character. When parity is inhibited, this output is low. |

# IM6403 FUNCTIONAL PIN DEFINITION (Continued)

| PIN | SYMBOL                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                 |

|-----|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | FE                                         | A high level on FRAMING ERROR indi-<br>cates the first stop bit was invalid. FE will<br>stay active until the next valid character's<br>stop bit is received.                                                                                                                                                                                               |

| 15  | ΘE                                         | A high level on OVERRUN ERROR indicates the data received flag was not cleared before the last character was transferred to the receiver buffer register. The Error is reset at the next character's stop bit if DRR has been performed (i.e., DRR; active low).                                                                                            |

| 16  | SFD                                        | A high level on STATUS FLAGS DISABLE forces the outputs PE, FE, OE, DR*TBRE* to a high impedance state. See Block Diagram and Figure 4.  *IM6402 only.                                                                                                                                                                                                      |

| 17  | IM6402-RRC<br>IM6403-XTAL<br>or EXT CLK IN | The RECEIVER REGISTER CLOCK is 16X the receiver data rate.                                                                                                                                                                                                                                                                                                  |

| 1/8 | DRR                                        | A low level on DATA RECEIVED RESET clears the data received output (DR), to a low level.                                                                                                                                                                                                                                                                    |

| 19  | DR                                         | A high level on DATA RECEIVED indicates a character has been received and transferred to the receiver buffer register.                                                                                                                                                                                                                                      |

| 20  | RRI -                                      | Serial data on RECEIVER REGISTER INPUT is clocked into the receiver register.                                                                                                                                                                                                                                                                               |

| 21  | MR                                         | A high level on MASTER RESET (MR) clears PE, FE, OE, DR, TRE and sets TBRE, TRO high. Less than: 18 clocks after MR goes low, TRE returns high. MR does not clear the receiver buffer register, and is required after power-up.                                                                                                                             |

| 22  | · TBRE                                     | A high level on TRANSMITTER BUFFER REGISTER EMPTY indicates the transmitter buffer register has transferred its data to the transmitter register and is ready for new data.                                                                                                                                                                                 |

| 23  | TBRL                                       | A low level on TRANSMITTER BUFFER REGISTER LOAD transfers data from inputs TBR1-TBR8 into the transmitter buffer register. A low to high transition on TBRL requests data transfer to the transmitter register. If the transmitter register is busy, transfer is automatically delayed so that the two characters are transmitted end to end. See Figure 2. |

| 24  | TRE                                        | A high level on TRANSMITTER REGISTER EMPTY indicates completed transmission of a character including stop bits.                                                                                                                                                                                                                                             |

| 25  | TRO                                        | Character data, start data and stop bits appear serially at the TRANSMITTER REGISTER OUTPUT.                                                                                                                                                                                                                                                                |

#

# IM6403 FUNCTIONAL PIN DEFINITION (Continued)

#### PIN SYMBOL **DESCRIPTION** 26 TBR1 Character data is loaded into the TRANS-MITTER BUFFER REGISTER via inputs TBR1-TBR8. For character formats less than 8-bits, the TBR8, 7, and 6 inputs are ignored corresponding to the programmed word length. 27 TBR2 See Pin 26 - TBR1 28 TBR3 See Pin 26 - TBR1 29 TBR4 See Pin 26 - TBR1 30 TBR5 See Pin 26 - TBR1 31 TBR6 See Pin 26 - TBR1 32 TBR7 See Pin 26 - TBR1 33 TBR8 See Pin 26 - TBR1 34 CRL A high level on CONTROL REGISTER LOAD loads the control register. See Figure 3.

# IM6403 FUNCTIONAL PIN DEFINITION (Continued)

| PIN | SYMBOL                              | DESCRIPTION                                                                                                                                                         |

|-----|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35  | PI*                                 | A high level on PARITY INHIBIT inhibits parity generation, parity checking and forces PE output low.                                                                |

| 36  | SBS*                                | A high level on STOP BIT SELECT selects 1.5 stop bits for a 5 character format and 2 stop bits for other lengths.                                                   |

| 37  | CLS2*                               | These inputs program the CHARACTER LENGTH SELECTED. (CLS1 low CLS2 low 5-bits) (CLS1 high CLS2 low 6-bits) (CLS1 low CLS2 high 7-bits) (CLS1 high CLS2 high 8-bits) |

| 38  | CLS1*                               | See Pin 37 — CLS2                                                                                                                                                   |

| 39  | EPE*                                | When PI is low, a high level on EVEN PARITY ENABLE generates and checks even parity. A low level selects odd parity.                                                |

| 40  | IM6402-TRC<br>IM6403-XTAL<br>or GND | The TRANSMITTER REGISTER CLOCK is 16X the transmit data rate.                                                                                                       |

<sup>\*</sup>See Table 2 (Control Word Function)

#### **TABLE 2. Control Word Function**

|      | CO   | NTROL WO |            |     | DATA BITS | PARITY BIT | STOP BIT(S) |

|------|------|----------|------------|-----|-----------|------------|-------------|

| CLS2 | CLS1 | PI       | EPE        | SBS | DAIADIIS  |            | STOP BIT(S) |

| L    | L    | L        | L          | L   | 5         | ODD        | 1 1         |

| L    | L    | · L      | L ·        | H   | 5         | ODD        | 1.5         |

| L.   | L    | L        | H          | L   | 5         | EVEN       | 1           |

| L    | L    | , L      | н          | Н   | 5         | EVEN       | 1.5         |

| L.   | L ·  | Н        | ×          | L   | 5         | DISABLED   | 1           |

| L.   | L    | н        | ×          | н   | 5         | DISABLED   | 1.5         |

| L    | н    | L        | L          | L   | 6         | ODD        | 1           |

| L    | Н    | L        | L          | Н   | 6         | ODD        | 2           |

| ∱ L  | . н  | L        | · н        | L   | 6         | EVEN       | 1 .         |

| L    | Н    | L        | н          | H   | 6         | EVEN -     | 2           |

| L    | н    | н        | ×          | L   | 6         | DISABLED   | 1           |

| L    | н    | Н        | ×          | H   | 6         | DISABLED   | 2           |

| • н  | L    | · L      | L .        | L   | 7         | ODD        | 1           |

| Н    | L    | L        | L          | н   | 7 ,       | ODD -      | 2           |

| H    | L    | . Ł      | н          | L   | 7         | EVEN       | 1           |

| H    | L.   | Ł        | Н          | H   | 7         | EVEN       | 2           |

| H    | L    | Н        | ×          | L.  | 7         | DISABLED   | 1           |

| Н .  | L    | H        | х          | Н   | 7         | DISABLED   | 2           |

| Н    | н    | L.       | L          | L . | 8         | ODD        | 1 1         |

| Н    | н    | L        | L          | н   | 8         | ODD ·      | 2 ·         |

| H +  | н    | Ĺ        | Н          | L   | 8         | EVEN       | 1 .         |

| Ĥ    | Н    | L        | н          | - H | 8         | EVEN       | 2           |

| H ,  | . н  | н        | <b>x</b> . | L - | 8         | DISABLED   | 1 .         |

| Н    | Н .  | H        | X          | Н   | 8         | DISABLED   | 2           |

X = Don't Care

#### IM6402/IM6403

#### TRANSMITTER OPERATION

The transmitter section accepts parallel data, formats it and transmits it in serial form (Figure 6) on the TROutput terminal.

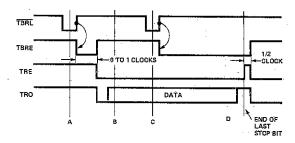

FIGURE 6. Serial Data Format

Transmitter timing is shown in Figure 7. (A) Data is loaded into the transmitter buffer register from the inputs TBR1 through TBR8 by a logic low on the TBRLoad input. Valid data must be present at least t<sub>DS</sub> prior to and t<sub>DH</sub> following the rising edge of TBRL. If words less than 8 bits are used, only the least significant bits are used. The character is right justified into the least significant bit, TBR1. (B) The rising edge of TBRL clears TBREmpty. O to 1 clock cycles later, data is transferred to the transmitter register, TREmpty is cleared and transmission starts. TBREmpty is reset to a logic high. Output data is clocked by TRClock, which is 16 times the data rate CA second pulse on TBRLoad loads data into the transmitter buffer register. Data transfer to the transmitter register is delayed until transmission of the current character is complete. Data is automatically transferred to the transmitter register and transmission of that character begins.

FIGURE 7. Transmitter Timing (Not to Scale)

#### RECEIVER OPERATION

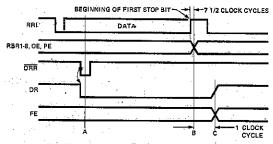

Data is received in serial form at the RI input. When no data is being received, RI input must remain high. The data is clocked by the RRClock, which is 16 times the data rate. Receiver timing is shown in Figure 8.

A low level on DRReset clears the DReady line. During the first stop bit, data is transferred from the receiver register to the RBRegister. If the word is less than 8 bits, the unused most significant bits will be a logic low. The output character is right justified to the least significant bit RBR1. A logic high on OError indicates an overrun which occurs when DReady has not been cleared before the present character was transferred to the RBRegister. A logic high on PError indicates a parity error. 1/2 clock cycle later, DReady is set to a logic high and FError is evaluated. A logic high on FError indicates an invalid stop bit was received. The receiver will not begin searching for the next start bit until a stop bit is received.

FIGURE 8. Receiver Timing (Not to Scale)

#### START BIT DETECTION

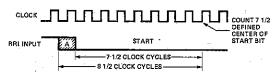

The receiver uses a 16X clock for timing (see Figure 9.) The start bit 3 could have occurred as much as one clock cycle before it was detected, as indicated by the shaded portion. The center of the start bit is defined as clock count  $7\frac{1}{2}$ . If the receiver clock is a symmetrical square wave, the center of the start bit will be located within  $\pm 1/2$  clock cycle,  $\pm 1/32$  bit or  $\pm 3.125\%$ . The receiver begins searching for the next start bit at the center of the first stor-bit.

FIGURE 9. Start Bit Timing

#### TYPICAL APPLICATION

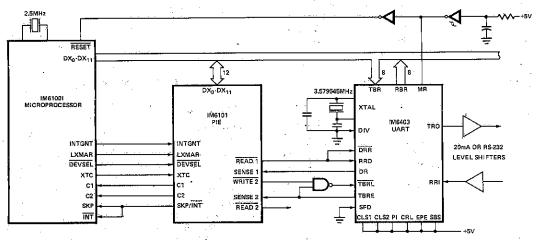

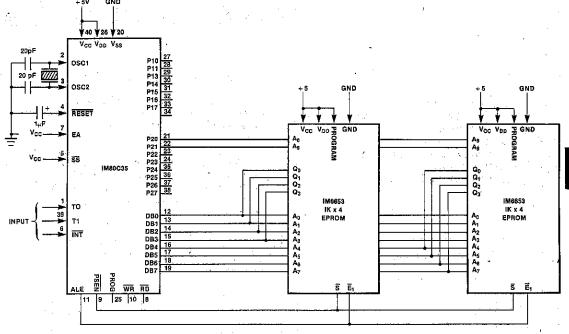

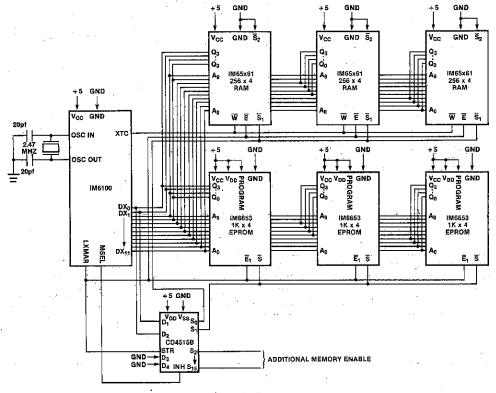

Microprocessor systems, which are inherently parallel in nature, often require an asynchronous serial interface. This function can be performed easily with the IM6402/03 UART. Figure 10 shows how the IM6403 can be interfaced to an IM6100 microcomputer system with the aid of an IM6101 Programmable Interface Element (PIE). The PIE interprets Input/Output transfer (IOT) instructions from the processor and generates read and write pulses to the UART. The SENSE lines on the PIE are also employed to allow the processor to detect UART status. In particular, the processor must know when the Receive Buffer Register has accumulated a character (DR active), and when the Transmit Buffer Register can accept another character to be transmitted.

In this example the characters to be received or transmitted will be eight bits long (CLS 1 and 2: both HIGH) and transmitted with no parity (PI:HIGH) and two stop bits (SBS:HIGH). Since these control bits will not be changed during operation, Control Register Load (CRL) can be tied high. Remember, since the IM6402/03 is a CMOS device, all unused inputs should be committed.

The baud rate at which the transmitter and receiver will operate is determined by the external crystal and DIVIDE CONTROL pin on the IM6403. The internal divider can be set to reduce the crystal frequency by either 16 (PIN 2:HIGH) or 2048. (PIN 2:LOW) times. The frequency out of the internal divider should be 16 times the desired baud rate. To generate 110 baud, this example will use a 3.579545MHz color TV crystal

2

and DIVIDE CONTROL set low. The IM6402 may use different receive (RRC) and transmit (TRC) clock rates, but requires an external clock generator.

To ensure consistent and correct operation, the IM6402/03 must be reset after power-up. The Master Reset (MR) pin is active high, and can be driven reliably from a Schmitt trigger inverter and R-C delay. In this example, the IM6100 is reset through still another inverter. The Schmitt trigger between the processor and R-C network is needed to assure that a slow rising capacitor voltage does not re-trigger RESET. A long reset pulse after power-up (~100ms) is required by the processor to assure that the on-board crystal oscillator has sufficient time to start.

The IM6402 supports the processor's bi-directional data bus quite easily by tying the TBR and RBR buses together. A read command from the processor will enable the RECEIVER BUFFER REGISTER onto the bus by using the RECEIVER REGISTER DISABLE (RRD) pin. A write command from the processor clocks data from the bus into the TRANSMITTER BUFFER REGISTER using TBRL. Figure 10 shows a NAND gate driving TBRL from the WRITE2 pin on the PIE. This gate is used to generate a rising edge to TBRL at the point where data is

stable on the bus, and to hold TBRL high until the UART actually transfers the data to it's internal buffer. If TBRL were allowed to return low before TBRE went high, the intended output data would be overwritten, since the TBR is a transparent latch.

Although not shown in this example, the error flags (PE, FE, OE) could be read by the processor, using the other READ line from the PIE. Since an IM6403 is used, TBRE and DR are not affected by the STATUS FLAGS DISABLE pin, thus, the three error flags can be tied to the data bus and gated by connecting SFD to READ<sub>2</sub>.

If parity is not inhibited, a parity error will cause the PE pin to go high until the next valid character is received.

A framing error is generated when an expected stop bit is not received. FE will stay high after the error until the next complete character's stop bit is received.

The overrun error flag is set if a received character is transferred to the RECEIVER BUFFER REGISTER when the previous character has not been read. The OE pin will stay high until the next received stop bit after a DRR is performed.

FIGURE 10. 110 Baud Serial Interface for IM6100 System

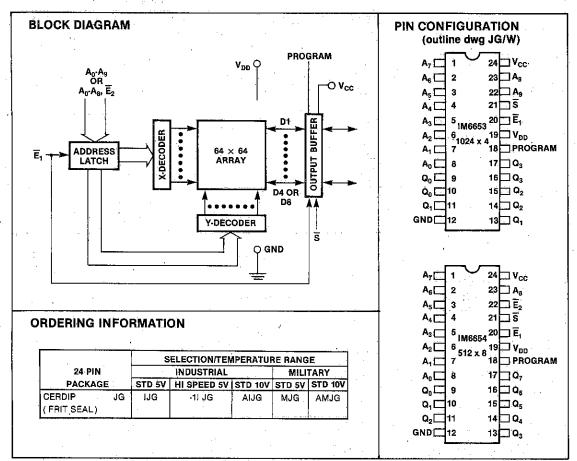

# IM6653/IM6654 4096 Bit CMOS UV Erasable PROM

#### **FEATURES**

- Organization IM6653: 1024 x 4 IM6654: 512 x 8

- Low Power 770µW Maximum Standby

- High Speed

- 300ns 10V Access Time for IM6653/54 AI

450ns 5V Access Time for IM6653/54-1I

- Single + 5V supply operation

- UV erasable

- Synchronous operation for low power dissipation

- Three-state outputs and chip select for easy system expansion

- Full -55°C to +125°C MIL range devices— IM6653/54 M, IM6653A/64A M

#### **GENERAL DESCRIPTION**

The Intersil IM6653 and IM6654 are fully decoded 4096 bit CMOS electrically programmable ROMs (EPROMs) fabricated with Intersil's advanced CMOS processing technology. In all static states these devices exhibit the microwatt power dissipation typical of CMOS. Inputs and three-state outputs are TTL compatible and allow for direct interface with common system bus structures. On-chip address registers and chip select functions simplify system interfacing requirements.

The IM6653 and IM6654 are specifically designed for program development applications where rapid turn-around for program changes is required. The devices may be erased by exposing their transparent lids to ultra-violet light, and then re-programmed.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltages                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------|

| Supply Voltages  V <sub>DD</sub> +8.0V                                                                                   |

| VCC = VDD + 8.0V                                                                                                         |

| Input or Output Voltage Supplied                                                                                         |

| Storage Temperature Range 65°C to + 150°C                                                                                |

| Operating Range                                                                                                          |

| Temperature                                                                                                              |

| Industrial                                                                                                               |

| Military55°C to +125°C                                                                                                   |

| Voltage                                                                                                                  |

| 6653/54 I, - II                                                                                                          |

| 6653/54 M                                                                                                                |

| NOTE: Stresses above those listed under Absolute Maximum Ratings may cause permanent                                     |

| damage to the device. These are stress ratings only, and functional operation of the device at                           |

| these or any other conditions above those indicated in the operational sections of the specifica-                        |

| tions is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. |

#### DC CHARACTERISTICS

**TEST CONDITIONS:**  $V_{CC} = V_{DD} = 5V \pm 10\%$ ,  $T_A = Operating Temperature Range$

|                            |                    |                                     | IM6653                 | /54I, -1I,M |              |

|----------------------------|--------------------|-------------------------------------|------------------------|-------------|--------------|

| PARAMETER                  | SYMBOL             | CONDITIONS                          | MIN                    | MAX         | UNITS        |

| Logical "1" Input Voltage  | V <sub>IH</sub>    | Ē <sub>1</sub> ,S                   | V <sub>DD</sub> - 2.0  |             |              |

|                            | V <sub>IH</sub>    | Address Pins                        | 2.7                    |             | v            |

| Logical "0" Input Voltage  | V <sub>IL</sub>    |                                     |                        | 0.8         |              |

| Input Leakage              | J <sub>I</sub>     | $GND \le V_{IN} \le V_{DD}$         | - 1.0                  | 1.0         | μA           |

| Logical "1" Output Voltage | V <sub>OH</sub> 2  | I <sub>OUT</sub> = 0                | V <sub>CC</sub> - 0.01 | *           |              |

| Logical "1" Output Voltage | V <sub>OH1</sub>   | $I_{OH} = -0.2 mA$                  | 2.4                    |             | 1            |

| Logical "0" Output Voltage | V <sub>OL2</sub>   | l <sub>OUT</sub> = 0                |                        | GND + 0.01  | V            |

| Logical "0" Output Voltage | · V <sub>OL1</sub> | i <sub>OL</sub> = 2.0mA             |                        | 0.45        | 1            |

| Output Leakage             | louk               | GND≤V <sub>O</sub> ≤V <sub>CC</sub> | - 1.0                  | 1.0         |              |

| Standby Supply Current     | lpose              | $V_{IN} = V_{DD}$                   | -                      | 100         | μΑ           |

|                            | lcc :              | $V_{IN} = V_{DD}$                   |                        | 40          | 1            |

| Operating Supply Current   | · lodob            | f=1 MHz                             |                        | 6           | mA           |

| Input Capacitance          | Cı                 | Note 1                              |                        | 7.0         |              |

| Output Capacitance         | Co                 | Note 1                              |                        | 10.0        | - p <b>F</b> |

Note 1: These parameters guaranteed but not 100% tested.

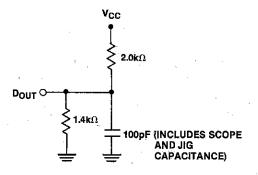

#### **AC CHARACTERISTICS**

**TEST CONDITIONS:**  $V_{CC} = V_{DD} = 5V \pm 10\%$ ,  $C_L = 50 pf$ ,  $T_A = Operating Temperature Range$

|                                       |                                   | IM6653/54-11 |     | IM6653/54 1  |      | IIM6653/54 M |     |       |

|---------------------------------------|-----------------------------------|--------------|-----|--------------|------|--------------|-----|-------|

| PARAMETER                             | SYMBOL                            | MIN          | MAX | MIN          | MAX  | MIN          | MAX | UNITS |

| Access Time From E                    | TE₁LQV                            |              | 450 |              | -550 |              | 600 |       |

| Output Enable Time                    | TSLQV                             |              | 110 | 1            | 140  |              | 150 | 1     |

| Output Disable Time                   | TE <sub>1</sub> HQZ               |              | 110 | <del> </del> | 140  |              | 150 | 1     |

| E <sub>1</sub> Pulse Width (Positive) | TE <sub>1</sub> HE <sub>1</sub> L | 130          | ·   | 150          |      | 150          |     | 1     |

| E <sub>1</sub> Pulse Width (Negative) | TE1LE1H                           | 450          |     | 550          |      | 60,0         |     | ns    |

| Address Setup Time                    | TAVE <sub>1</sub> L               | 0            |     | 0            | -    | 0            |     |       |

| Address Hold Time                     | TE <sub>1</sub> LAX               | 80           | 3   | 100          |      | 100          |     |       |

| Chip Enable Setup Time (6654)         | TE <sub>2</sub> VE <sub>1</sub> L | 0            |     | 0            | 1    | 0            |     |       |

| Chip Enable Hold Time (6654)          | TE <sub>1</sub> LE <sub>2</sub> X | 80           |     | 100          |      | 100          | 7   |       |

# 2

| Supply Voltages                  | the contract of the contract o |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>                  | + 11.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{CC} = V_{DD}$                | +11.0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Input or Output Voltage Supplied | GND - 0.3V to V <sub>DD</sub> + 0.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Storage Temperature Range        | 65°C to + 150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Operating Range                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Temperature                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Industrial                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Military                         | 55°C to +125°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Voltage                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

NOTE: Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC CHARACTERISTICS

**TEST CONDITIONS:**  $V_{CC} = V_{DD} = 4.5V$  to 10.5V,  $T_A = Operational$  Temperature Range

|                            |                   |                                      | IM665                  | 3/54AI, AM |          |

|----------------------------|-------------------|--------------------------------------|------------------------|------------|----------|

| PARAMETER                  | SYMBOL            | CONDITIONS                           | MIN                    | MAX        | UNITS    |

| Logical "1" Input Voltage  | V <sub>IH</sub>   | Ē₁,Ŝ                                 | V <sub>DD</sub> - 2.0  |            | ·        |

|                            | V <sub>IH</sub>   | Address Pins                         | V <sub>DD</sub> - 2.0  |            | V        |

| Logical "0" Input Voltage  | V <sub>IL</sub>   |                                      | T                      | 0.8        |          |

| Input Leakage              | l <sub>1</sub>    | GND≤V <sub>IN</sub> ≤V <sub>DD</sub> | -1.0                   | 1.0        | μΑ       |

| Logical "1" Output Voltage | V <sub>OH</sub> : | I <sub>OUT</sub> = 0                 | V <sub>CC</sub> - 0.01 |            | <u> </u> |

| Logical "0" Output Voltage | VoL               | I <sub>OUT</sub> = 0                 |                        | GND + 0.01 | V        |

| Output Leakage             | l <sub>oLK</sub>  | GND≤V <sub>0</sub> ≤V <sub>CC</sub>  | 1.0                    | 1.0        |          |

| Standby Supply Current     | I <sub>DDSB</sub> | $V_{IN} = V_{DD}$                    |                        | 100        | μÀ       |

|                            | lcc               | $V_{IN} = V_{DD}$                    |                        | 40         |          |

| Operating Supply Current   | IDDOP             | f=1 MHz                              |                        | 12         | mA       |

| Input Capacitance          | C <sub>I</sub>    | Note 1                               |                        | 7.0        |          |

| Output Capacitance         | Co                | Note 1                               |                        | 10.0       | рF       |

Note 1: These parameters guaranteed but not 100% tested.

#### **AC CHARACTERISTICS**

**TEST CONDITIONS:**  $V_{CC} = V_{DD} = 10V \pm 5\%$ ,  $C_L = 50pf$ ,  $T_A = Operating Temperature Range$

|                                       |                                   | IM66 | 53/54 Al     | IM66 |                                                  |              |

|---------------------------------------|-----------------------------------|------|--------------|------|--------------------------------------------------|--------------|

| PARAMETER                             | SYMBOL                            | MIN  | MAX          | MIN  | MAX                                              | UNITS        |

| Access Time From E <sub>1</sub>       | TE <sub>1</sub> LQV               |      | 300          |      | 350                                              |              |

| Output Enable Time                    | TSLQV                             |      | 60           | -    | 70                                               |              |

| Output Disable Time                   | TE <sub>1</sub> HQZ               |      | 60           |      | 70                                               | †            |

| E <sub>1</sub> Pulse Width (Positive) | TE <sub>1</sub> HE <sub>1</sub> L | 125  | T            | 125  |                                                  | ┪ ・          |

| E₁ Pulse Width (Negative)             | TE <sub>1</sub> LE <sub>1</sub> H | 300  |              | 350  | <del>                                     </del> | ns ns        |

| Address Setup Time                    | TAVE <sub>1</sub> L               | 0    | <del>-</del> | 0    | <del> </del>                                     | 1            |

| Address Hold Time                     | TE <sub>1</sub> LAX               | 60   |              | 60   |                                                  | <del> </del> |

| Chip Enable Setup Time (6654)         | TE <sub>2</sub> VE <sub>1</sub> L | 0    | <u> </u>     | 0    | <del> </del>                                     | -            |

| Chip Enable Hold Time (6654)          | TE <sub>1</sub> LE <sub>2</sub> X | 60   |              | 60   |                                                  | 1            |

#### PIN ASSIGNMENTS

| PIN        | SYMBOL                                         | ACTIVE<br>LEVEL | DESCRIPTION                                                           |

|------------|------------------------------------------------|-----------------|-----------------------------------------------------------------------|

| 1-8,23     | A <sub>0</sub> -A <sub>7</sub> ,A <sub>8</sub> |                 | Address Lines                                                         |

| 9-11,13-17 | $Q_0$ - $Q_7$                                  | 1               | Data Out lines, 6654                                                  |

| •          | $Q_0$ - $Q_3$                                  | -               | Data Out lines, 6653                                                  |

| 12         | GND                                            | _               |                                                                       |

| 18         | Program                                        |                 | Programming pulse input                                               |

| 19         | V <sub>DD</sub>                                | _               | Chip V+ supply, normally tied to V <sub>CC</sub>                      |

| 20         | Ē, /                                           | L               | Strobe line, latches both address lines and, for 6654, Chip enable E2 |

| 21         | <u> </u>                                       | L               | Chip select line, must be low for valid data out                      |

| 22         | Ag                                             |                 | Additional address line for 6653                                      |

|            | $\overline{\overline{E}}_{2}$                  | Ĺ               | Chip enable line, latched by Chip enable E <sub>1</sub> on 6654       |

| 24         | V <sub>CC</sub>                                |                 | Output buffer + V Supply                                              |

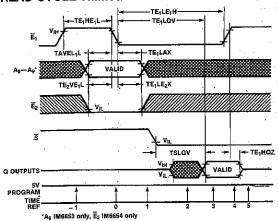

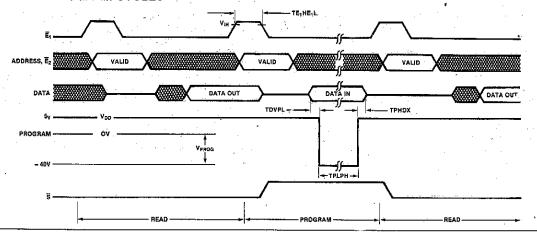

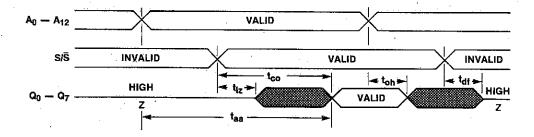

#### **READ CYCLE TIMING**

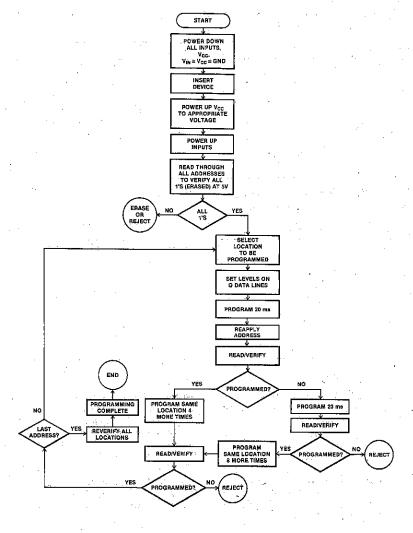

#### **READ MODE OPERATION**

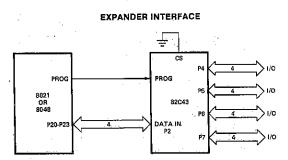

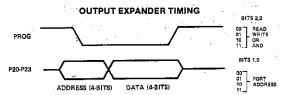

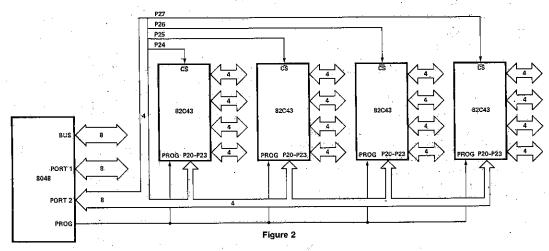

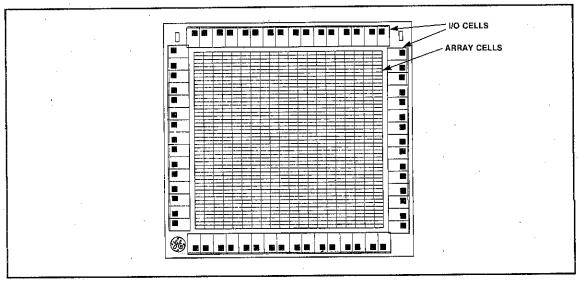

In a typical READ operation address lines and chip enable  $\overline{E}_2$ \*are latched by the falling edge of chip enable  $\overline{E}_1$  (T = 0). Valid data appears at the outputs one access time (TELQV) later, provided level-sensitive chip select line 5 is low  $(\Gamma = 3)$ . Data remains valid until either  $\overline{E}_1$  or  $\overline{S}$  returns to a high level (T = 4). Outputs are then forced to a high-Z state.