# National Semiconductor LMV1024/LMV1026 (Stereo)

OBSOLETE July 20, 2009

### PDM Output with Pre-Amplifier for Electret Microphones

### **General Description**

National's LMV1024 and LMV1026 stereo amplifiers are solutions for the new generation of voice enrichment capabilities. National has integrated sigma delta modulation and analog cores to improve the voice quality and the performance and to support designer's choices.

Each 20 kHz preamplifier drives a Pulse Density Modulated (PDM) signal at an over sampled 60 bit stream, offering versatility. These solutions provide immediate conversion to high performance audio spectrum, thus completing a high quality audio system. The LMV1024 and LMV1026 operate from 1.6V to 3V.

National's new adjustable clock frequency technology is designed for stereo, performance and ease of use. The stereo function is either a rising or falling edge clock command. The high drive, robust PDM signal directly from an ECM (Electret Condenser Microphone), upgrades existing lower quality, low-level signal constraints.

These advanced mixed signal preamplifiers cleanly, accurately and creatively eliminate older, poorer quality systems. which restricted performance and versatility. The 4-wire PDM signaling reduces RF noise and simplifies layout. Using National's PDM solutions is the choice for higher quality mono or stereo and multi-array applications.

National's 518uA circuits deliver stereo portability with audio quality bandwidth. These solutions enable rapid system evaluation and enhance consumer satisfaction. National provides the LMV1024 and LMV1026 in 6-bump micro SMD packages with 1 kg adhesion properties.

### **Features**

(Typical  $V_{DD} = 1.8V$ , CLOCK = 1.2 MHz,  $f_{INPUT} = 1$  kHz,  $V_{INPLIT} = 18 \text{ mV}_{PP}$ , unless otherwise specified)

- Enhanced high-performance, full PDM output from the element

- Stereo chipset and array routing

- 59 dB SNR A-weighted

- Digital A-weighted noise floor -89 dBFS

- Supply current 518 µA

- 400 kHz to 2.4 MHz Clock frequency Total harmonic distortion 0.03%

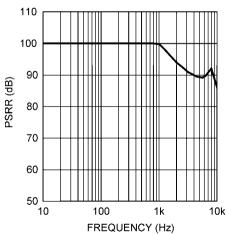

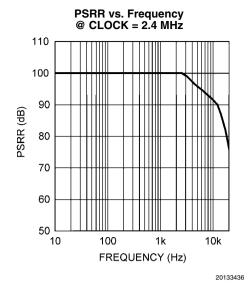

- Power supply rejection ratio 100 dB

- Adhesion technology >1 kg

- Highly integrated stereo or mono signaling

- Maximized system performance

- Reduced components and layout

- RF (buzz noise) managed with 4 wire signaling

- Thinnest 0.35 mm micro SMD packaging

### **Applications**

- Digital output audio subsystems and stereo arrays

- Electret condenser microphones with all digital output

- Portable communications and small form factor

- Digital audio computing or voice security

- Automotive or array systems

- Headphone and Headset accessories

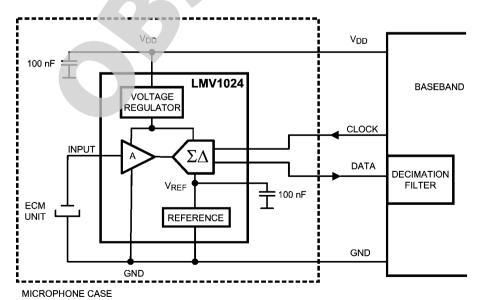

### **Typical Application**

20133475

For a stereo application, see STEREO OPERATION in the Application Section.

### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance (Note 2)

**Human Body Model** 2500V Machine Model 250V Supply Voltage

$V_{DD}$  - GND 3.3V Storage Temperature Range -65°C to 150°C Junction Temperature (Note 6)

Mounting Temperature

Infrared or Convection (20 sec.)

150°C max

235°C

### **Operating Ratings** (Note 1)

Supply Voltage 1.6V to 3.0V Input Clock Frequency 400 kHz to 2.4 MHz **Duty Cycle** 40% to 60% Operating Temperature Range -40°C to 85°C

### 1.8V Electrical Characteristics (Note 3)

Unless otherwise specified, all limits are guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{DD} = 1.8V$ ,  $V_{IN} = 18 \text{ mV}_{PP}$ ,  $f_{CLK} = 1.2 \text{ MHz}$ , Duty Cycle = 50% and 100 nF capacitor between  $V_{REF}$  and GND. **Boldface** limits apply at the temperature extremes.

| Symbol                  | Parameter                                                                                           | Conditions                                                                                                     | Min<br>(Note 4) | Typ<br>(Note 5) | Max<br>(Note 4) | Units            |

|-------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|------------------|

| SNR                     | Signal to Noise Ratio                                                                               | f <sub>IN</sub> = 1 kHz, A-Weighted                                                                            |                 | 59              |                 | dB               |

| e <sub>N</sub>          | Digital Noise Floor (Integrated)                                                                    | f = 20 Hz to 10 kHz, A-Weighted, 4.7 pF<br>Capacitor Connected from Input to<br>GND to Simulate ECM, No Signal |                 | -89             |                 | dBFS(A)          |

| THD                     | Total Harmonic Distortion                                                                           | $f_{IN} = 1 \text{ kHz}, V_{IN} = 18 \text{ mV}_{PP}$                                                          |                 | 0.03            |                 | %                |

| I <sub>DD</sub>         | Supply Current                                                                                      | V <sub>IN</sub> = GND, CLK = ON, High Impedance<br>Load (Note 7)                                               |                 | 518             |                 | μΑ               |

| V                       | CLOCK Input Logic Low Level                                                                         | V <sub>IN</sub> = GND, CLK = OFF                                                                               |                 | 503             | 600<br>0.3      | V                |

| V <sub>IL</sub>         | CLOCK Input Logic High Level                                                                        |                                                                                                                | 1.5             |                 | 0.5             | V                |

| $\frac{V_{IH}}{V_{OL}}$ | DATA Output Logic Low Level                                                                         |                                                                                                                | 1.5             |                 | 0.1             | V                |

| V <sub>OH</sub>         | DATA Output Logic High Level                                                                        |                                                                                                                | 1.7             |                 | 0.1             | V                |

| V <sub>IN</sub>         | Max Input Signal                                                                                    | f <sub>IN</sub> = 1 kHz, THD < 1%                                                                              | 1.7             | 243             |                 | mV <sub>PP</sub> |

| V <sub>OUT</sub>        | Max Output Signal                                                                                   | f <sub>IN</sub> = 1 kHz, THD < 1%                                                                              |                 | -6.8            |                 | dBFS             |

| PSRR                    | Power Supply Rejection Ratio                                                                        | V <sub>IN</sub> = GND, Test Signal on V <sub>DD</sub> = 217<br>Hz, 100 mV <sub>PP</sub>                        |                 | 100             |                 | dB               |

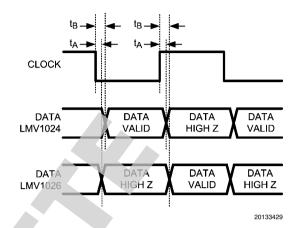

| t <sub>A</sub>          | Time from CLOCK Transition to DATA Becoming High Impedance (See also <i>Figure 10</i> , Application | LMV1024: On Rising Edge of the CLOCK LMV1026: On Falling Edge of the                                           |                 | 65              |                 | ns               |

|                         | Section)                                                                                            | CLOCK                                                                                                          |                 |                 |                 |                  |

| t <sub>B</sub>          | Time from CLOCK Transition to DATA Becoming Valid (See also                                         | LMV1024: On Falling Edge of the CLOCK                                                                          | 90              |                 |                 | 200              |

|                         | Figure 10, Application Section)                                                                     | LMV1026: On Rising Edge of the CLOCK                                                                           |                 |                 |                 | ns               |

| C <sub>IN</sub>         | Input Capacitance                                                                                   |                                                                                                                |                 | 2               |                 | pF               |

| R <sub>IN</sub>         | Input Impedance                                                                                     |                                                                                                                |                 | 1000            |                 | MΩ               |

### 2.7V Electrical Characteristics (Note 3)

Unless otherwise specified, all limits are guaranteed for  $T_J = 25$ °C,  $V_{DD} = 2.7V$ ,  $V_{IN} = 18$  mV<sub>PP</sub>,  $f_{CLK} = 1.2$  MHz, Duty Cycle = 50% and 100 nF capacitor between  $V_{REF}$  and GND. **Boldface** limits apply at the temperature extremes.

| Symbol            | Parameter                                                                                                    | Conditions                                                                                                     | Min<br>(Note 4) | Typ             | Max<br>(Note 4) | Units            |

|-------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|------------------|

|                   | l                                                                                                            |                                                                                                                | (Note 4)        | (Note 5)        | (Note 4)        |                  |

| SNR               | Signal to Noise Ratio                                                                                        | f <sub>IN</sub> = 1 kHz, A-Weighted                                                                            |                 | 59              |                 | dB               |

| e <sub>n</sub>    | Digital Noise Floor (Integrated)                                                                             | f = 20 Hz to 10 kHz, A-Weighted, 4.7 pF<br>Capacitor Connected from Input to<br>GND to Simulate ECM, No Signal |                 | <del>-</del> 89 |                 | dBFS(A)          |

| THD               | Total Harmonic Distortion                                                                                    | $f_{IN} = 1 \text{ kHz}, V_{IN} = 18 \text{ mV}_{PP}$                                                          |                 | 0.03            |                 | %                |

| I <sub>DD</sub>   | Supply Current                                                                                               | V <sub>IN</sub> = GND, CLK = ON, High Impedance<br>Load (Note 7)                                               |                 | 535             |                 | μA               |

|                   |                                                                                                              | V <sub>IN</sub> = GND, CLK = OFF                                                                               |                 | 519             | 650             |                  |

| V <sub>LOW</sub>  | CLOCK Logic Low Level                                                                                        |                                                                                                                |                 |                 | 0.3             | V                |

| V <sub>HIGH</sub> | CLOCK Logic High Level                                                                                       |                                                                                                                | 2.4             |                 |                 | V                |

| V <sub>OL</sub>   | DATA Output Logic Low Level                                                                                  |                                                                                                                |                 |                 | 0.1             | V                |

| V <sub>OH</sub>   | DATA Output Logic High Level                                                                                 |                                                                                                                | 2.6             |                 |                 | V                |

| V <sub>IN</sub>   | Max Input Signal                                                                                             | f <sub>IN</sub> = 1 kHz, THD < 1%                                                                              |                 | 249             |                 | mV <sub>PP</sub> |

| V <sub>OUT</sub>  | Max Output Signal                                                                                            | f <sub>IN</sub> = 1 kHz, THD < 1%                                                                              |                 | -6.6            |                 | dBFS             |

| PSRR              | Power Supply Rejection Ratio                                                                                 | $V_{IN}$ = GND, Test Signal on $V_{DD}$ = 217<br>Hz, 100 m $V_{PP}$                                            |                 | 100             |                 | dB               |

| t <sub>A</sub>    | Time from CLOCK Transition to DATA Becoming High Impedance (See also <i>Figure 10</i> , Application Section) | LMV1024: On Rising Edge of the<br>CLOCK<br>LMV1026: On Failing Edge of the<br>CLOCK                            |                 | 65              |                 | ns               |

| t <sub>B</sub>    | Time from CLOCK Transition to DATA Becoming Valid (See also Figure 10, Application Section)                  | LMV1024: On Falling Edge of the<br>CLOCK<br>LMV1026: On Rising Edge of the<br>CLOCK                            |                 | 90              |                 | ns               |

| C <sub>IN</sub>   | Input Capacitance                                                                                            |                                                                                                                |                 | 2               |                 | pF               |

| R <sub>IN</sub>   | Input Impedance                                                                                              |                                                                                                                |                 | 1000            |                 | MΩ               |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

Note 2: The Human Body Model (HBM) is 1.5 k $\Omega$  in series with 100 pF. The Machine Model is  $0\Omega$  in series with 200 pF.

Note 3: Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No guarantee of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

Note 4: All limits are guaranteed by design or statistical analysis.

Note 5: Typical values represent the most likely parametric norm.

Note 6: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$  and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly into a PC board.

Note 7: The Supply Current depends on the applied Clock Frequency and the load on the DATA output.

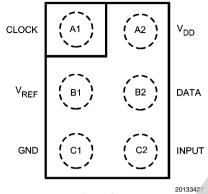

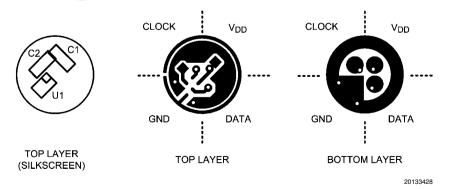

# **Connection Diagram**

### Large Dome 6-Bump Ultra Thin micro SMD

**Top View**

## **Pin Descriptions**

|              | Pin | Name             | Description                                                                                              |  |  |

|--------------|-----|------------------|----------------------------------------------------------------------------------------------------------|--|--|

| Power Supply | A2  | V <sub>DD</sub>  | Positive supply voltage                                                                                  |  |  |

|              | C1  | GND              | Ground                                                                                                   |  |  |

| Input        | C2  | Input            | The microphone is connected to this input pin.                                                           |  |  |

| Reference    | B1  | V <sub>REF</sub> | A capacitor of 100 nF is connected between V <sub>REF</sub> and ground. This capacitor is used to filter |  |  |

|              |     |                  | the internal converter reference voltage.                                                                |  |  |

| Clock Input  | A1  | Clock            | The user adjustable clock frequency ranges from 400 kHz to 2.4 MHz.                                      |  |  |

| Data Output  | B2  | Data             | Over sampled bitstream output. Data is valid if clock is LOW (LMV1024). The data of the                  |  |  |

|              |     |                  | LMV1026 data is valid when clock is HIGH. When the data is not valid the data output is                  |  |  |

|              |     |                  | Hi-Z. For exact specifications see application section.                                                  |  |  |

# **Ordering Information**

| Package                     | Part Number  | Package Marking         | Transport Media         | NSC Drawing |  |

|-----------------------------|--------------|-------------------------|-------------------------|-------------|--|

|                             | LMV1024UR    | ΙE                      | 250 Units Tape and Reel |             |  |

| 6-Bump Ultra Thin micro SMD | LMV1024URX   | I E                     | 3k Units Tape and Reel  | URA06GGA    |  |

| lead free only              | LMV1026UR IF | 250 Units Tape and Reel | UHAUBGGA                |             |  |

|                             |              | ''-                     | 3k Units Tape and Reel  |             |  |

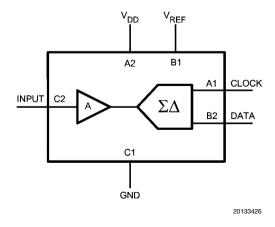

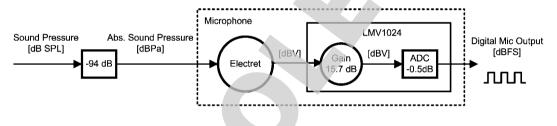

## **Block Diagram**

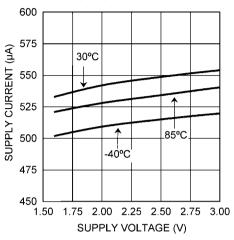

# **Typical Performance Characteristics** Unless otherwise specified, measurements are performed on an LMV1024 with $V_{DD} = 1.8V$ , Clock Duty Cycle = 50% and a 100 nF capacitor is placed between $V_{REF}$ and GND, $T_{J} = 25^{\circ}C$ .

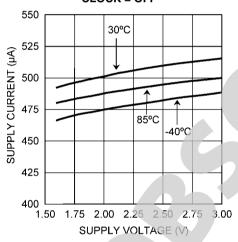

#### Supply Current vs. Supply Voltage @ CLOCK = 1.2 MHz

20133446

### Supply Current vs. Supply Voltage CLOCK = OFF

20133431

20133448

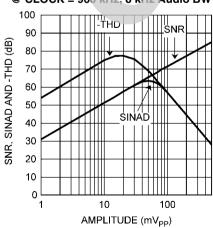

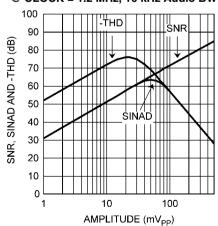

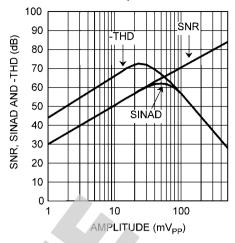

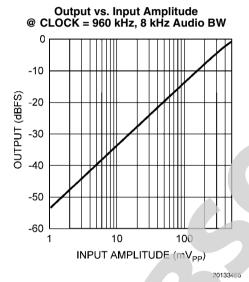

### SNR, SINAD and -THD vs. Input Amplitude @ CLOCK = 960 kHz, 8 kHz Audio BW

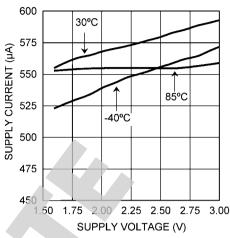

#### Supply Current vs. Supply Voltage @ CLOCK = 2.4 MHz

20133430

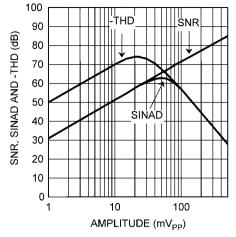

### SNR, SINAD and -THD vs. Input Amplitude @ CLOCK = 408 kHz, 3.4 kHz Audio BW

20133447

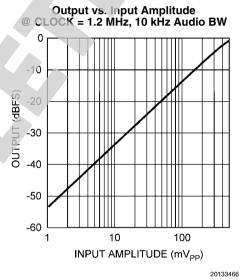

### SNR, SINAD and -THD vs. Input Amplitude @ CLOCK = 1.2 MHz, 10 kHz Audio BW

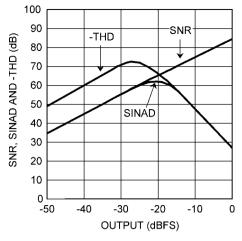

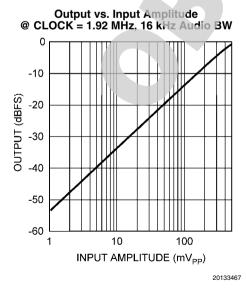

### SNR, SINAD and -THD vs. Input Amplitude @ CLOCK = 1.92 MHz, 16 kHz Audio BW

20133450

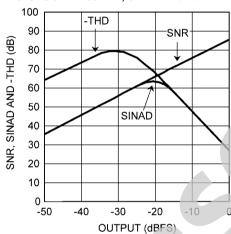

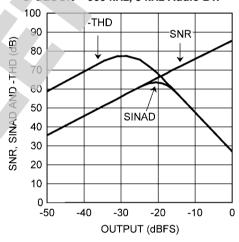

### SNR, SINAD and -THD vs. Output @ CLOCK = 408 kHz, 3.4 kHz Audio BW

20133451

### SNR, SINAD and -THD vs. Output @ CLOCK = 1.2 MHz, 10 kHz Audio BW

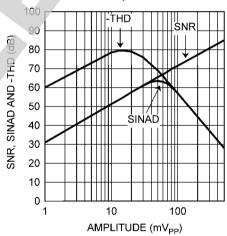

SNR, SINAD and -THD vs. Input Amplitude @ CLOCK = 2.4 MHz, 20 kHz Audio BW

20133432

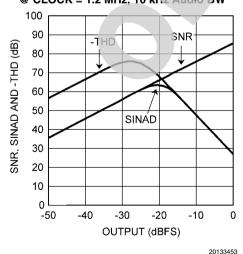

### SNR, SINAD and -THD vs. Output @ CLOCK = 960 kHz, 8 kHz Audio BW

20133452

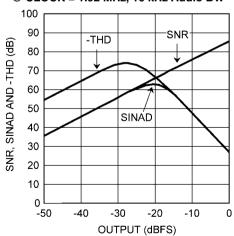

### SNR, SINAD and -THD vs. Output @ CLOCK = 1.92 MHz, 16 kHz Audio BW

20133454

### SNR, SINAD and -THD vs. Output @ CLOCK = 2.4 MHz, 20 kHz Audio BW

20133433

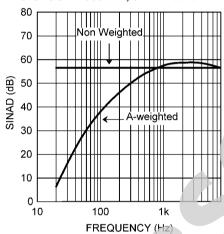

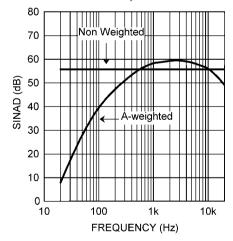

### SINAD vs. Frequency @ CLOCK = 960 kHz, 8 kHz Audio BW

20133456

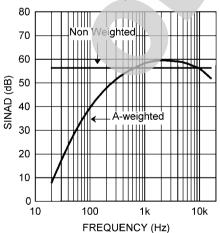

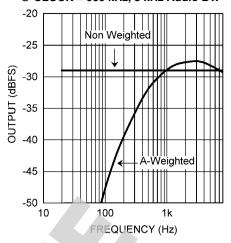

## SINAD vs. Frequency @ CLOCK = 1.92 MHz, 16 kHz Audio BW

20133458

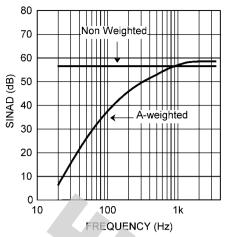

## SINAD vs. Frequency @ CLOCK = 408 kHz, 3.4 kHz Audio BW

20133455

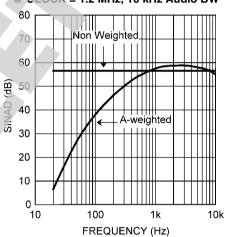

# SINAD vs. Frequency © CLOCK = 1.2 MHz, 10 kHz Audio BW

20133457

## SINAD vs. Frequency @ CLOCK = 2.4 MHz, 20 kHz Audio BW

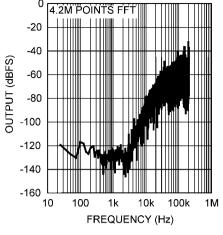

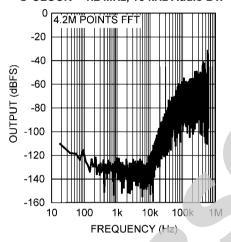

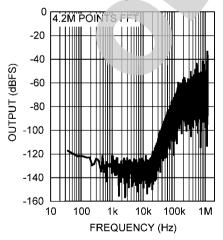

### Noise vs. Frequency @ CLOCK = 408 kHz, 3.4 kHz Audio BW

20133459

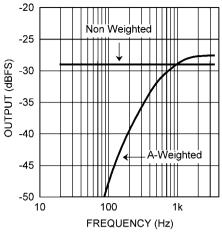

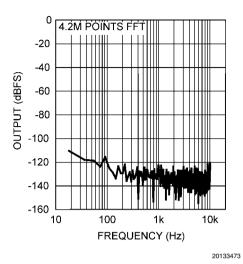

# Noise vs. Frequency @ CLOCK = 1.2 MHz, 10 kHz Audio BW

2013346

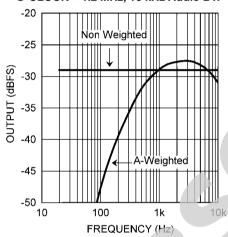

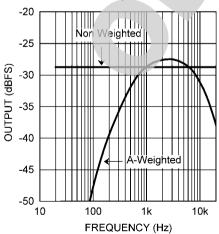

# Noise vs. Frequency @ CLOCK = 2.4 MHz, 20 kHz Audio BW

20133444

### Noise vs. Frequency @ CLOCK = 960 kHz, 8 kHz Audio BW

20133460

# Noise vs. Frequency © CLOCK = 1.92 MHz, 16 kHz Audio BW

20133462

#### PSRR vs. Frequency @ CLOCK = 1.2 MHz

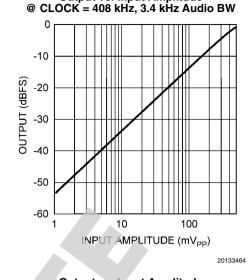

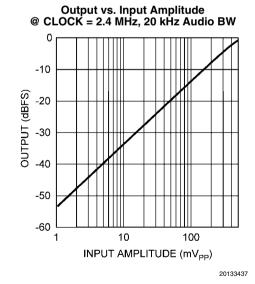

**Output vs. Input Amplitude**

### Output vs. Frequency @ CLOCK = 408 kHz, 3.4 kHz Audio BW

20133468

## Output vs. Frequency @ CLOCK = 1.2 MHz, 10 kHz Audio BW

20133470

### Output vs. Frequency @ CLOCK = 2.4 MHz, 20 kHz Audio BW

20133438

### Output vs. Frequency @ CLOCK = 960 kHz, 8 kHz Audio BW

20133469

# Output vs. Frequency © CLOCK = 1.92 MHz, 16 kHz Audio BW

### **Application Section**

The LMV1024/LMV1026 consist of a pre-amplifier and sigma delta converter for placement inside an electret condenser microphone (ECM). The output of the LMV1024/LMV1026 is a robust digital serial bit stream eliminating the sensitive low-level analog signals of conventional JFET microphones. This application section describes, among others, a typical application, a sensitivity comparison between different ECM types, stereo operation and layout recommendations on the ECM PCBs.

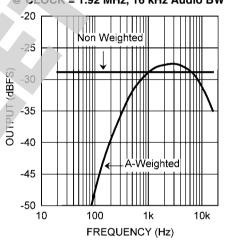

### TYPICAL APPLICATION

Figure 1 depicts a typical application, where the LMV1024 or LMV1026 is built inside the ECM canister. This ECM can be directly connected to a DSP in a digital audio system, like a baseband chip in a cell phone. Connecting is easy because of the digital LMV1024/LMV1026 interface. A digital filter in the DSP or Baseband decimates the audio signal.

**FIGURE 1. Typical Application**

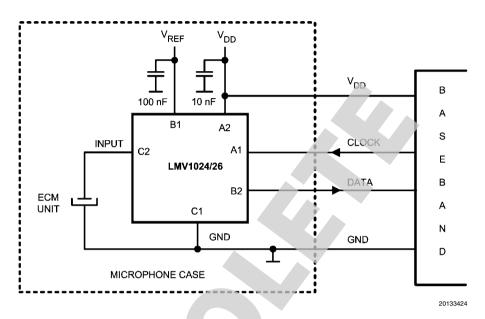

#### **BUILT-IN PRE-AMPLIFIER / ADC**

The LMV1024/LMV1026 are offered in a space saving small 6-bump micro SMD package in order to fit inside small ECM canisters. The LMV1024 or LMV1026 IC is placed on the PCB. This PCB forms the bottom of the microphone, which is placed in the cell phone.

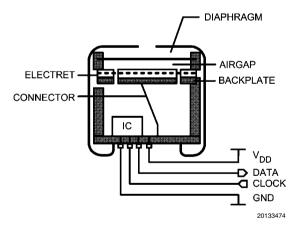

FIGURE 2. Built-in Pre-Amplifier / ADC

Figure 3 depicts a cross section of a microphone with the IC inside the ECM canister. The PCB of the microphone has 4 pads that connects  $V_{DD}$ , Ground, DATA and the CLOCK.

FIGURE 3. Cross section of a Microphone

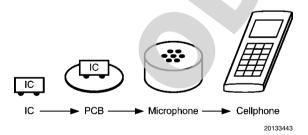

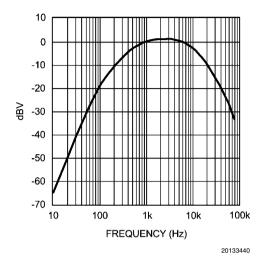

#### **A-WEIGHTED FILTER**

The human ear has a frequency range from about 20 Hz to 20 kHz. Within this range the sensitivity of the human ear is not equal for each frequency. In order to approach a natural hearing response, weighting filters are introduced. One of these filters is the A-weighted filter. The A-weighted filter is commonly used in signal-to-noise ratio measurements, where sound is compared to device noise. The filter improves the correlation of the measured data to the signal-to-noise ratio perceived by the human ear.

FIGURE 4. A-weighted Filter

### **SENSITIVITY**

Sensitivity is a measure for the transfer from the applied acoustic signal to the output of the microphone. Conventional JFET microphones and microphones with built-in gain have a sensitivity that is expressed in dB(V/Pa), where 0dB = 1V/Pa. A certain pressure on the electret of the microphone gives a certain voltage at the output of the microphone. Since the LMV1024 microphone has a digital output, the sensitivity will be stated in dB(Full Scale/Pascal) or dB(FS/Pa) as opposed

to conventional microphones. This section compares the various microphone types and their sensitivity. Examples are given to calculate the resulting output for a given sound pressure.

### **Sound Pressure Level**

The volume of sound applied to a microphone is usually stated as a sound pressure in dB SPL. This unity of dB SPL refers to the threshold of hearing of the human ear. The sound pressure in decibels is defined by:

$SPL = 20 \log (P_{M}/P_{O})$

Where,SPL is the Sound Pressure in dB SPLP $_{\rm M}$  is the measured absolute sound pressure in PaP $_{\rm O}$  is the threshold of hearing (20  $\mu$ Pa)

In order to calculate the resulting output voltage of the electret element for a given sound pressure in dB SPL, the absolute sound pressure  $P_M$  must be known. This is the absolute sound pressure in decibels referred to 1 Pa instead of 20 µPa.

The absolute sound pressure  $P_M$  in dBPa is given by:  $P_M$  = SPL (dB SPL) +  $P_O$  (dBPa) $P_M$  = SPL + 20\*log 20  $\mu$ Pa $P_M$  = SPL - 94 dB

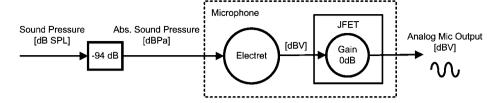

### **JFET Microphone**

Translation from the absolute sound pressure level to a voltage can be done when the electrets sensitivity is known. A typical electret element has a sensitivity of –44 dB(V/Pa). This is also the typical sensitivity number for the JFET microphone, since a JFET usually has a gain of about 1x (0 dB). A block diagram of a microphone with a JFET is given in *Figure 5*.

Example: Busy traffic has a Sound Pressure of 70 dB SPL. Microphone Output = SPL + C + S

Where, SPL is the Sound Pressure in dB SPLC is the dB SPL to dBPa conversion (-94 dB)S is the Sensitivity in dB(V/Pa) Microphone Output = 70 - 94 - 44 = -68 dBVThis is equivalent to 1.13 mV<sub>PP</sub>.

The analog output signal is so low that it can easily be distorted by interference from outside the microphone. Additional gain is desirable to make the signal less sensitive to interference.

### Microphone with JFET

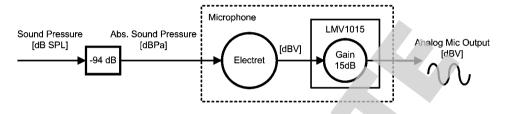

### Microphone with LMV1015 Preamplifier

### Digital Microphone with LMV1024 Preamplifier / ADC

20133445

FIGURE 5. Microphone Sensitivity

### **Microphone with Additional Gain**

When gain is added to the electret element, the analog signal becomes larger and therefore more robust. This can be accomplished by using a pre-amplifier with a higher gain then the JFET. The sensitivity of the microphone consists of the sensitivity of the electret plus the gain of the pre-amplifier. When choosing National Semiconductor's LMV1015-15 for instance, a gain of 15 dB is added by the pre-amplifier. This results in a sensitivity of –29 dB(V/Pa) with a typical electret element of –44 dB(V/Pa). National Semiconductor has a wide range of pre-amplifiers with different gain factors, which can be used to replace the JFET inside the microphone canister. Please visit www.national.com for more information on the LMV1015 and LMV1032 pre-amplifier series. A block diagram with the LMV1015 pre-amplifier inside an ECM is given in Figure 5.

When taking the same example of busy traffic (70 dB SPL), the output voltage of the microphone with the LMV1015 is:

Microphone Output = SP + C + S

Where,SP is the Sound Pressure in dB SPLC is the dB SPL to dBPa conversion (-94 dB)S is the Sensitivity in dB(V/Pa) Microphone output = 70 - 94 - 29 = -53 dBV. This is equivalent to 6.33 mV<sub>PP</sub>.

The pre-amplifier with additional gain reduces the impact of noise on the wiring / traces from the microphone to the base-

band chip significantly. To minimize interference ultimately, an Analog-to-Digital converter is integrated in both the LMV1024/LMV1026, realizing a digital interface between the microphone and the baseband.

#### **Digital Microphone**

By integrating the Analog-to-Digital converter (ADC) in the LMV1024/LMV1026 all analog signals are kept within the "shielded" microphone canister. The output is a digital interface that is robust and insensitive to interference and noise from outside the canister. The output is expressed in dBFS and therefore the sensitivity is also stated in dB(FS/Pa) instead of dB(V/Pa). To calculate the digital output (Data) in dBFS the following equation can be written for the LMV1024/LMV1026:

Digital Output = 10 LOG

$$\left[\frac{P_{INPUT}}{P_{REF}}\right]$$

+ A (1)

Where,

$P_{REF}$  is the reference power, which is defined as the maximum allowed input power (Full Scale).  $P_{INPUT}$  is the applied power on the input pin and "A" is the gain of the pre-amplifier in decibels.

Written into voltages, the equation is:

Digital Output = 20 LOG

$$\left[\frac{V_{\text{INPUT}}}{V_{\text{REF}}}\right]$$

+ A (2)

Or in decibels:Digital Output (dBFS) = Input (dBV) - Reference (dB) + A

Where,Input = 20 Log  $V_{INPUT}$  ( $V_{RMS}$ )Ref = 20 Log  $V_{REF}$  ( $V_{RMS}$ )A is the Gain (dB)

For the LMV1024/LMV1026 the reference voltage  $V_{REF}$  is 1.5 $V_{P}$  (1.06  $V_{RMS}$ ) and the Gain A is 15.7 dB. These parameters are fixed inside the device. Knowing this, *Equation 2* can be simplified:

Digital Output (dBFS) =  $V_{INPUT}$  (dBV) - 0.5 + 15.7Digital Output (dBFS) =  $V_{INPUT}$  (dBV) + 15.2

The sensitivity of the digital microphone is the sensitivity of a conventional microphone plus the input to output transfer of the LMV1024. The sensitivity of a typical digital microphone is therefore: -44 + 15.2 = -28.8 dB(FS/Pa).

Digital Output = SP + C + S

Where,SP is the Sound Pressure in dB SPLC is the dB SPL to dBPa conversion (–94 dB)S is the Sensitivity in dB(V/Pa) Taking the example of busy traffic (70 dB SPL) again results in the following digital output (dBFS):

Digital Output (dBFS) = SP - C + SDigital Output (dBFS) = 70 - 94 - 28.8 = -52.8 dBFS

### **ANALOG-TO-DIGITAL CONVERTER**

The ADC used in the LMV1024/LMV1026 is an one bit sigma delta converter with a Pulse Density Modulated output signal (PDM). The output of this ADC can be either High (one) or Low (zero). Assume that the LMV1024/LMV1026 input is at the minimum level. In that case the DATA output will produce almost only "zeros". When the input increases, the amount of "ones" increases too. At mid-point, where the input is 0V, the number of "zeros" will equal the number of "ones". At the time that the input approaches the maximum level, the DATA output produces a majority of "ones". Figure 6 shows the resulting DATA output as function of the input.

FIGURE 6. DATA Output versus Input Amplitude

An important characteristic of the sigma delta converter is that the noise is shifted out of the band to frequencies above the band of interest. The band that can be used (Audio Bandwidth) relates directly the applied clock frequency. *Table 1* shows the relation between the Clock Frequency and a couple of common Audio Bandwidths.

TABLE 1. Audio Bandwidth vs. Clock Frequency

Audio Bandwidth

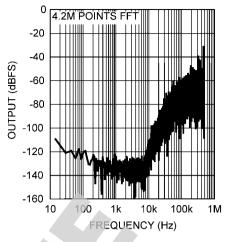

The high corner of the band of interest (knee) is determined by the clock frequency divided by 2 times the OSR. The factor of two comes from the Nyquist theorem. The over sampling ratio (OSR) of this particular ADC is chosen at 60. This sets the high corner of the band at the clock frequency divided by 120. For instance when a bandwidth of 10 kHz is desired, the clock frequency needs to be 1.2 MHz or higher. *Figure 7* depicts the noise shaping effect in a frequency spectrum plot, where a 1 kHz signal is applied.

FIGURE 7. Frequency Spectrum

|         |             | •                    |

|---------|-------------|----------------------|

| 3.4 kHz | 0           |                      |

| 8 kHz   | 0           | 4.2M POINTS FFT      |

| 10 kHz  | -20         |                      |

| 16 kHz  | -40         |                      |

| 20 kHz  | ဂ်          |                      |

|         | -60         |                      |

|         | 5 -80       |                      |

|         | -80<br>-100 |                      |

|         |             |                      |

|         | -120        |                      |

|         | -140        |                      |

|         | -160        |                      |

|         | 1           | 0 100 1k 10k 100k 1M |

|         |             | FREQUENCY (Hz)       |

|         |             | 20133461             |

|         |             |                      |

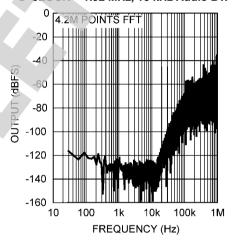

To eliminate the noise above the band of interest a low pass decimation filter is implemented in the baseband chip or DSP. The resulting frequency spectrum contains only the frequency components left within the band of interest. *Figure 8* depicts the frequency spectrum after filtering.

FIGURE 8. Frequency Spectrum after Filtering

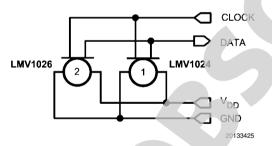

### STEREO OPERATION

The LMV1024 and the LMV1026 are designed to operate together in a stereo solution with two microphones. One microphone will have a LMV1024 built-in and the other will have a LMV1026 built-in. These two microphones share the same interface lines to minimize wiring (*Figure 9*).

FIGURE 9. Stereo Application

Both microphones produce valid data in only one half of a clock cycle to allow the two microphones to operate on the

same I/O lines (Data and Clock). To avoid overlap between the drivers of the microphones, one microphone always goes into a high impedance state before the second microphone starts driving the data-line. The LMV1024 is positive edge triggered while the LMV1026 is negative edge triggered. The timing between the two microphones is shown in *Figure 10*. For exact timing values, please see the Electrical Characteristics table.

FIGURE 10. Timing

### LAYOUT CONSIDERATIONS

To obtain the best possible performance from the microphone, special care needs to be taken for the design of the PCB. Especially the V<sub>IN</sub> trace is very sensitive as it is connected to the high impedance electret element. It is essential to isolate and shield the  $V_{\rm IN}$  trace as much as possible from the digital signal traces (DATA and CLOCK). This needs to be done to avoid any switching noise coupling directly into the input of the IC. An example of a PCB layout is given in Figure 11. The microphone PCB has two capacitors. One capacitor (100 nF) is connected to the reference pin of the LMV1024/ LMV1026. The other capacitor (10 nF) is used as decoupling for high frequencies on the supply. No capacitors should be placed on the data output of the LMV1024/LMV1026 since it will only load the output driver and would degrade the performance. This is opposite to the regular analog phantom biased microphones, where capacitors are needed to improve RFI.

FIGURE 11. PCB Layout

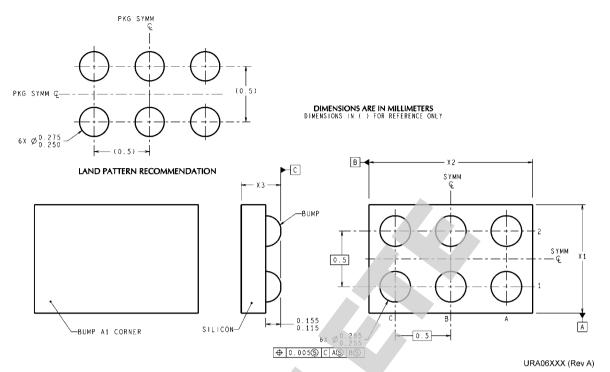

### Physical Dimensions inches (millimeters) unless otherwise noted

NOTE: UNLESS OTHERWISE SPECIFIED.

- 1. FOR SOLDER BUMP COMPOSITION, SEE "SOLDER INFORMATION" IN THE PACKAGING SECTION OF THE NATIONAL SEMICONDUCTOR WEB PAGE (www.national.com).

- 2. RECOMMEND NON-SOLDER MASK DEFINED LANDING PAD.

- 3. PIN A1 IS ESTABLISHED BY LOWER LEFT CORNER WITH RESPECT TO TEXT ORIENTATION.

- 4. XXX IN DRAWING NUMBER REPRESENTS PACKAGE SIZE VARIATION WHERE X1 IS PACKAGE WIDTH, X2 IS PACKAGE LENGTH AND X3 IS PACKAGE HEIGHT.

- 5. NO JEDEC REGISTRATION AS OF MARCH 2003

6-Bump Ultra Thin micro SMD NS Package Number URA06GGA  $X_1 = 1.128$  mm,  $X_2 = 1.628$  mm,  $X_3 = 0.35$  mm

### Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage Reference              | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions                       | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS, PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS. NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor **Americas Technical** Support Center Email: support@nsc.com ww.national.com Tel: 1-800-272-9959

National Semiconductor Europe **Technical Support Center** Email: europe.support@nsc.com

National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan **Technical Support Center** Email: ipn.feedback@nsc.com