# 38D5 Group

# SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

REJ03B0158-0304 Rev.3.04 May 20, 2008

### **DESCRIPTION**

The 38D5 Group is the 8-bit microcomputer based on the 740 Family core technology.

The 38D5 Group is pin-compatible with the 38C5 Group.

The 38D5 Group has an LCD drive control circuit, an A/D converter, a serial interface, and a ROM correction function as additional functions.

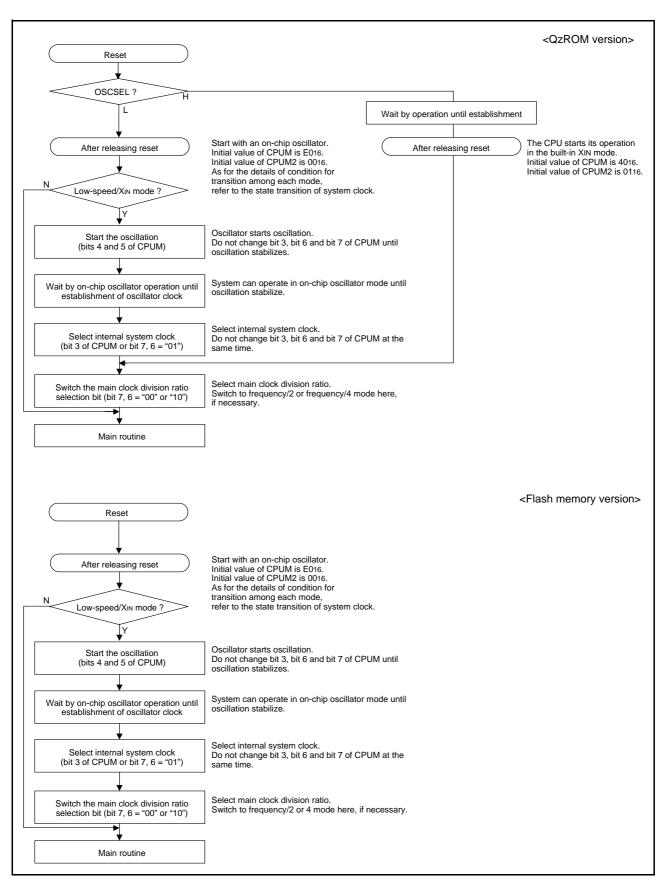

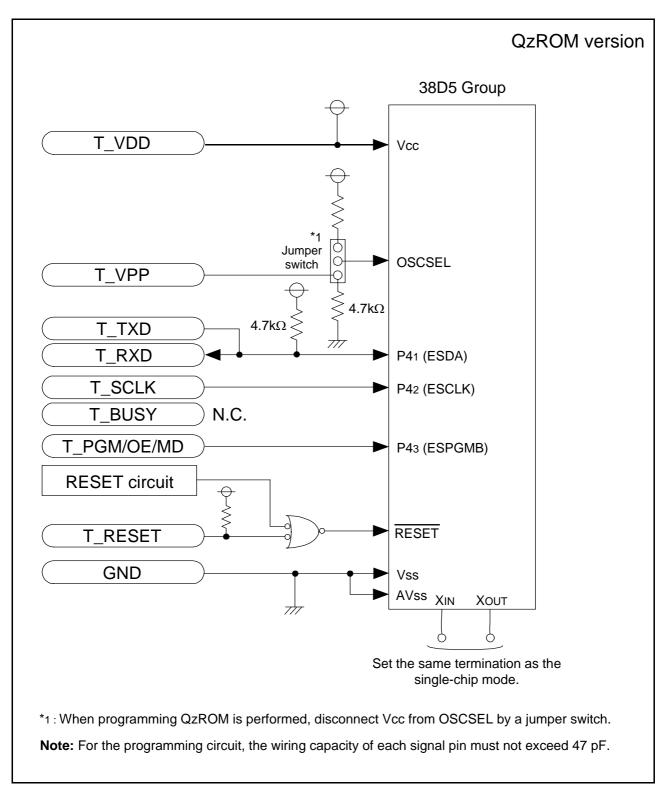

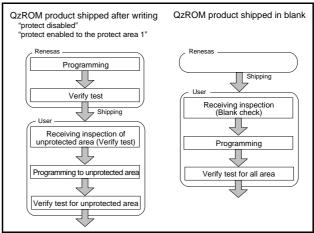

The QzROM version and the flash memory version are available. The flash memory version does not have a selection function for the oscillation start mode. Only the on-chip oscillator starts oscillating.

The various microcomputers include variations of memory size, and packaging. For details, refer to the section on part numbering.

### **FEATURES**

| • Basic machine-language instructions                                    |

|--------------------------------------------------------------------------|

| • The minimum instruction execution time 0.32 µs                         |

| (at 12.5 MHz oscillation frequency)                                      |

| • Memory size (QzROM version)                                            |

| ROM                                                                      |

| RAM                                                                      |

| • Memory size (Flash memory version)                                     |

| ROM                                                                      |

| RAM                                                                      |

| • Programmable input/output ports 59 (common to SEG: 36)                 |

| • Interrupts                                                             |

| (Key input interrupt included)                                           |

| • Timers                                                                 |

| Serial interface                                                         |

| Serial I/O18-bit × 1 (UART or Clock-synchronized)                        |

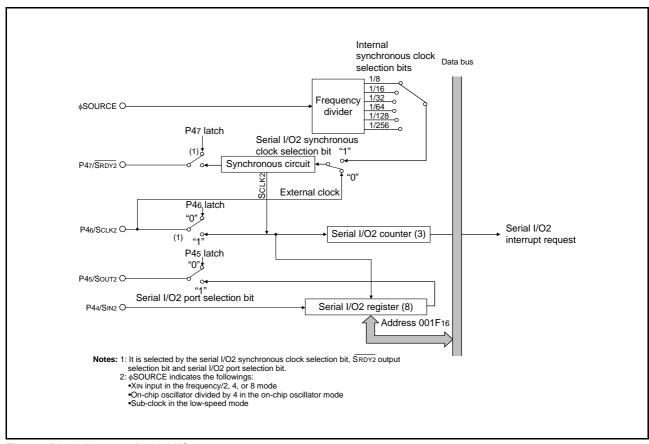

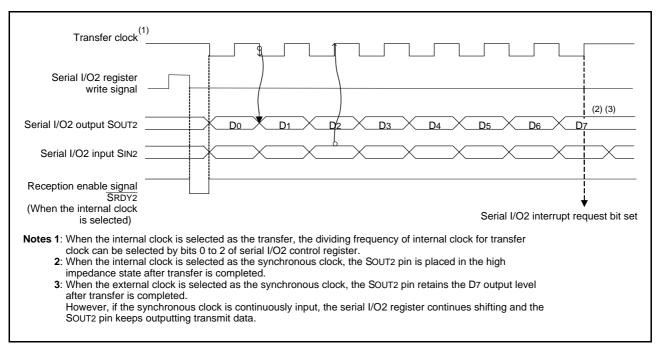

| Serial I/O2 8-bit × 1 (Clock-synchronized)                               |

| • PWM $10$ -bit $\times$ 2, $16$ -bit $\times$ 1 (common to IGBT output) |

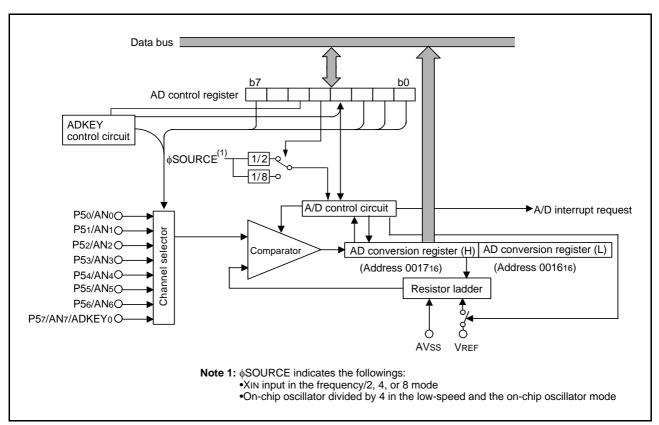

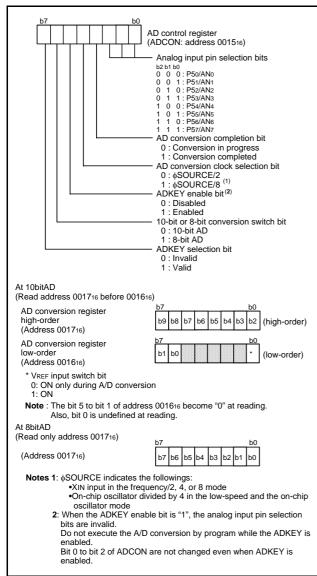

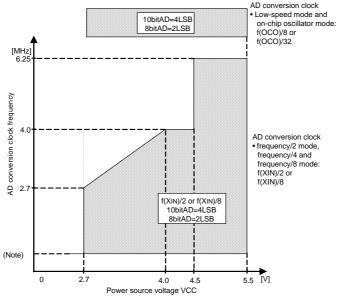

| • A/D converter $10$ -bit $\times$ 8 channels                            |

| (A/D converter can be operated in low-speed mode.)                       |

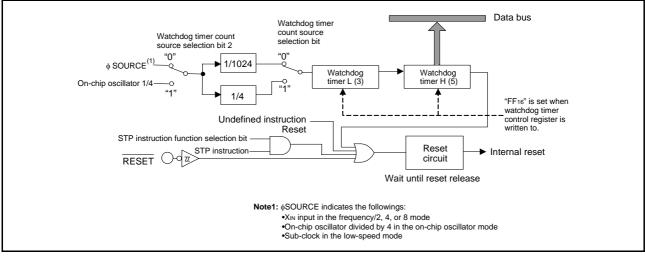

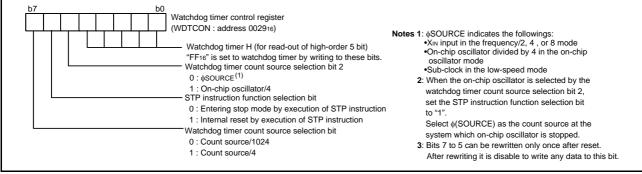

| • Watchdog timer                                                         |

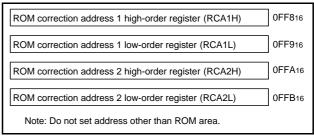

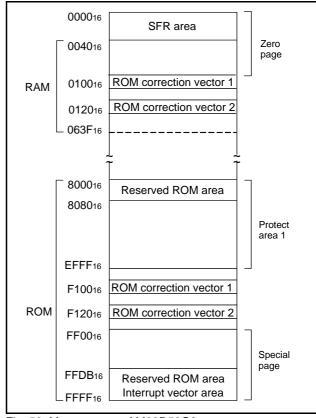

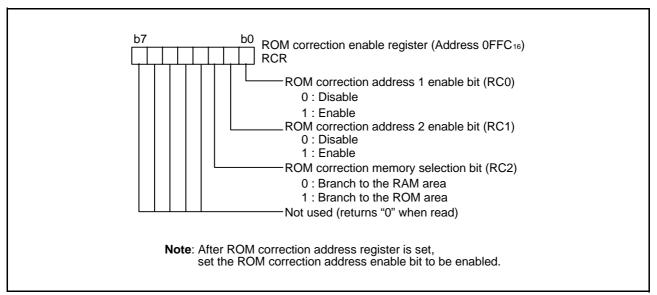

| • ROM correction function 32 bytes × 2 vectors                           |

| • LED direct drive port                                                  |

| (average current: 15 mA, peak current: 30 mA, total current: 90 mA)      |

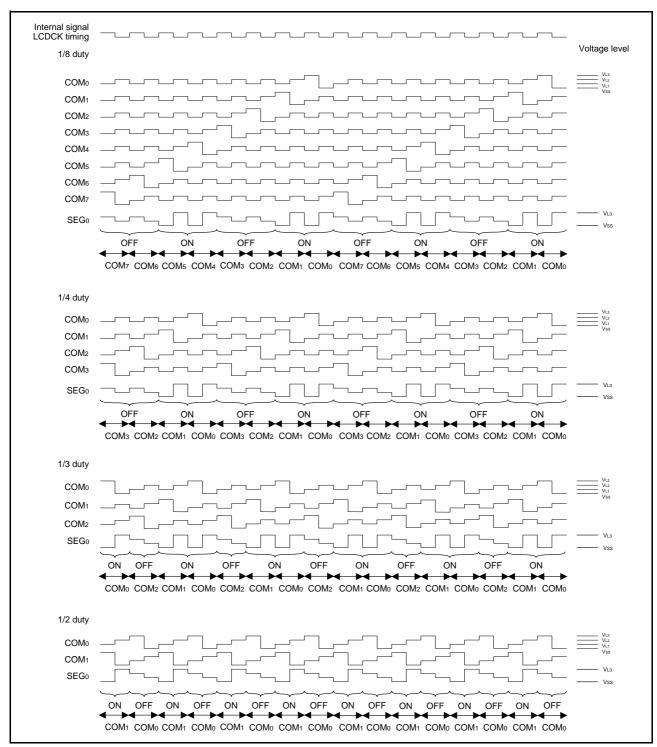

| LCD drive control circuit                                                |

| Bias                                                                     |

| Duty Static, 2, 3, 4, 8                                                  |

| Common output                                                            |

| Segment output                                                           |

| • Main clock generating circuit                                          |

| (connect to external ceramic resonator or on-chip oscillator)            |

| • Sub-clock generating circuit                                           |

| (connect to external quartz-crystal oscillator)                          |

|                                                                          |

| D (O DOM : )                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

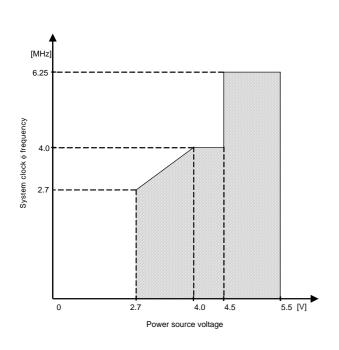

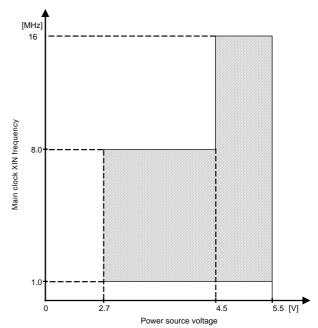

| Power source voltage (QzROM version)  The for source voltage (Az ROM version)  The formula (Az ROM version)  The formula (Az ROM version)  The formula (Az ROM version) |

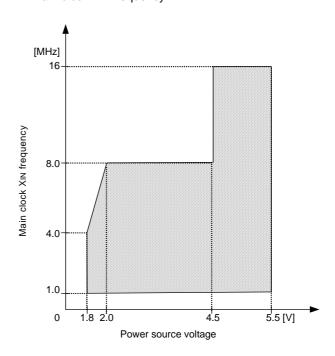

| [In frequency/2 mode]                                                                                                                                                   |

| $f(XIN) \le 12.5 \text{ MHz}$ 4.5 to 5.5 V                                                                                                                              |

| $f(X_{IN}) \le 8 \text{ MHz}$ 4.0 to 5.5 V                                                                                                                              |

| $f(XIN) \le 4 \text{ MHz.}$ 2.0 to 5.5 V                                                                                                                                |

| $f(XIN) \le 2 \text{ MHz.}$ 1.8 to 5.5 V                                                                                                                                |

| [In frequency/4 mode]                                                                                                                                                   |

| $f(XIN) \le 16 \text{ MHz}$                                                                                                                                             |

| $f(XIN) \le 8 \text{ MHz}$ 2.0 to 5.5 V                                                                                                                                 |

| $f(XIN) \le 4 \text{ MHz}$ 1.8 to 5.5 V                                                                                                                                 |

| [In frequency/8 mode]                                                                                                                                                   |

| $f(XIN) \le 16 \text{ MHz}$                                                                                                                                             |

| $f(XIN) \le 8 \text{ MHz.}$ 2.0 to 5.5 V                                                                                                                                |

| $f(X_{IN}) \le 4 \text{ MHz}$ 1.8 to 5.5 V                                                                                                                              |

| [In low-speed mode]                                                                                                                                                     |

| Note. 12.5 MHz $<$ f(XiN) $\le$ 16 MHz is not available in the fre                                                                                                      |

| quency/2 mode.                                                                                                                                                          |

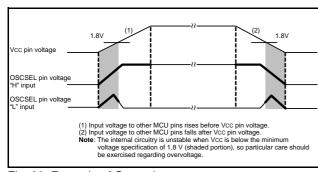

| • Power source voltage (Flash memory version)                                                                                                                           |

| [In frequency/2 mode]                                                                                                                                                   |

| $f(XIN) \le 12.5 \text{ MHz.}$ 4.5 to 5.5 V                                                                                                                             |

| $f(XIN) \le 8 \text{ MHz.}$ 4.0 to 5.5 V                                                                                                                                |

| $f(XIN) \le 4 \text{ MHz.}$ 2.7 to 5.5 V                                                                                                                                |

| [In frequency/4 mode]                                                                                                                                                   |

| $f(XIN) \le 16 \text{ MHz}$ 4.5 to 5.5 V                                                                                                                                |

| $f(XIN) \le 8 \text{ MHz}$ 2.7 to 5.5 V                                                                                                                                 |

| [In frequency/8 mode]                                                                                                                                                   |

| $f(XIN) \le 16 \text{ MHz}$                                                                                                                                             |

| $f(XIN) \le 8 \text{ MHz.}$ 2.7 to 5.5 V                                                                                                                                |

| [In low-speed mode]                                                                                                                                                     |

| Note. 12.5 MHz $<$ f(XiN) $\le$ 16 MHz is not available in the fre                                                                                                      |

| quency/2 mode.                                                                                                                                                          |

| <ul> <li>Power dissipation (QzROM version)</li> </ul>                                                                                                                   |

| • In frequency/2 mode Typ. 32 mW                                                                                                                                        |

| $(Vcc = 5 V, f(Xin) = 12.5 MHz, Ta = 25^{\circ}C)$                                                                                                                      |

| • In low-speed mode Typ. 18 $\mu W$                                                                                                                                     |

| $(VCC = 2.5 \text{ V}, f(XIN) = \text{stop}, f(XCIN) = 32 \text{ kHz}, Ta = 25^{\circ}C)$                                                                               |

| • Power dissipation (Flash memory version)                                                                                                                              |

| • In frequency/2 mode Typ. 20 mW                                                                                                                                        |

| $(V_{CC} = 5 \text{ V}, f(X_{IN}) = 12.5 \text{ MHz}, Ta = 25^{\circ}\text{C})$                                                                                         |

| • In low-speed mode Typ. 1.1 mW                                                                                                                                         |

| $(VCC = 2.7 \text{ V}, f(XiN) = \text{stop}, f(XciN) = 32 \text{ kHz}, Ta = 25^{\circ}\text{C})$                                                                        |

| • Operating temperature range                                                                                                                                           |

| operating temperature range                                                                                                                                             |

| Flash Memory Mode                                                                                                                                                       |

| • Program/Erase voltage Vcc = 2.7 to 5.5 V                                                                                                                              |

| Program method Programming in unit of byte                                                                                                                              |

| • Erase method                                                                                                                                                          |

| - Erase method Block crasing                                                                                                                                            |

### **APPLICATION**

Household products, Consumer electronics, etc.

• Program/Erase control by software command

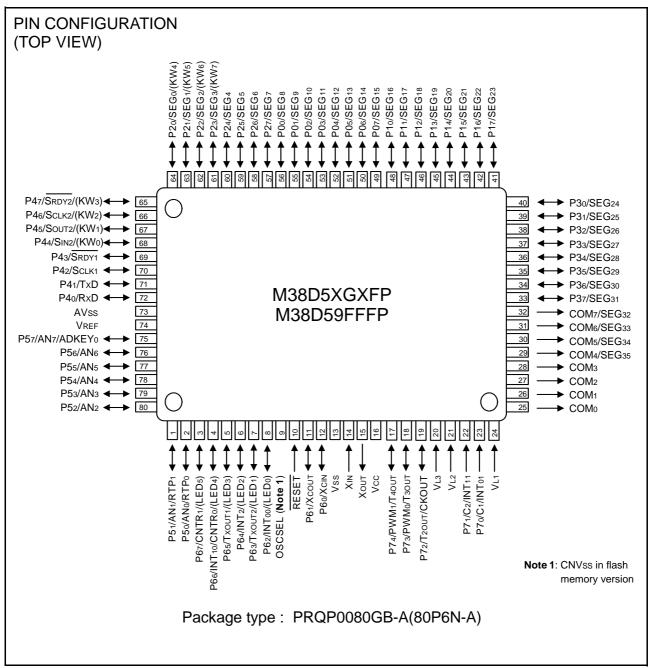

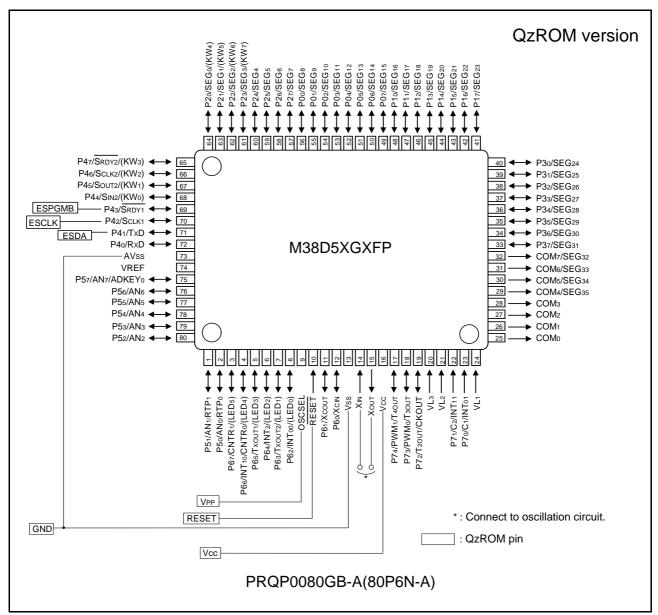

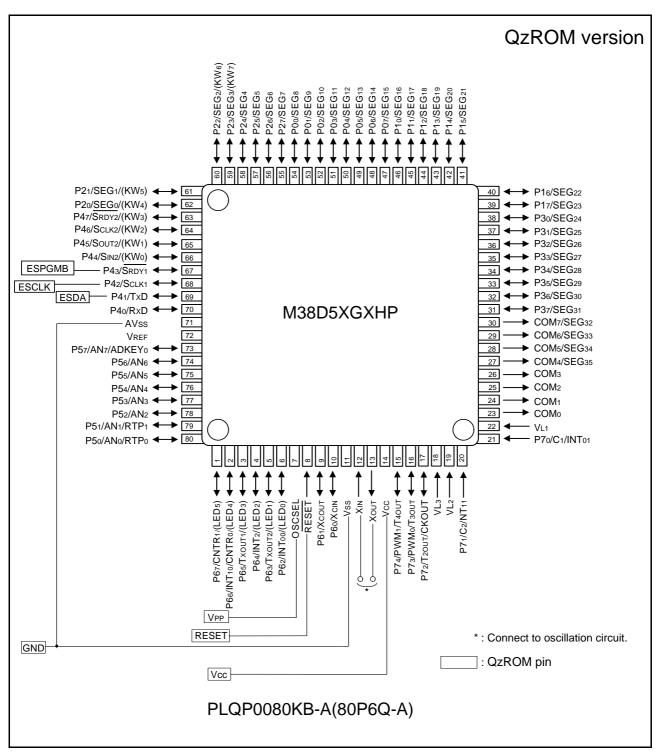

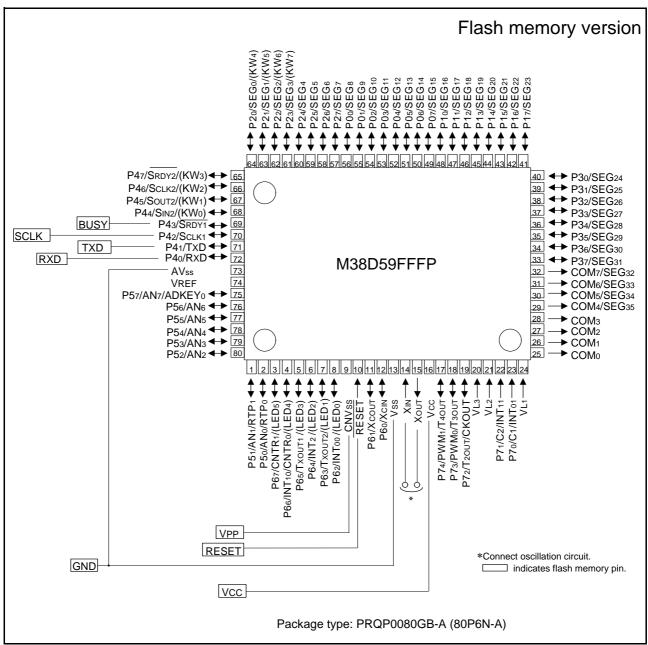

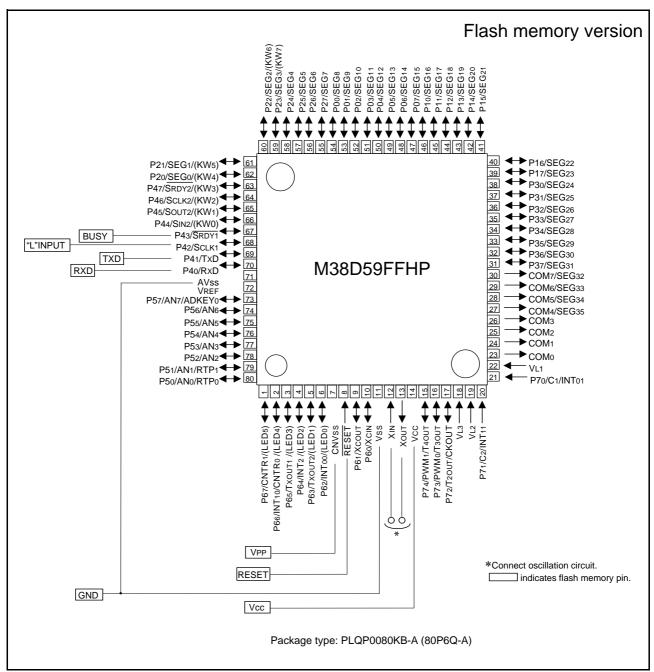

Fig. 1 Pin configuration (QFP Package)

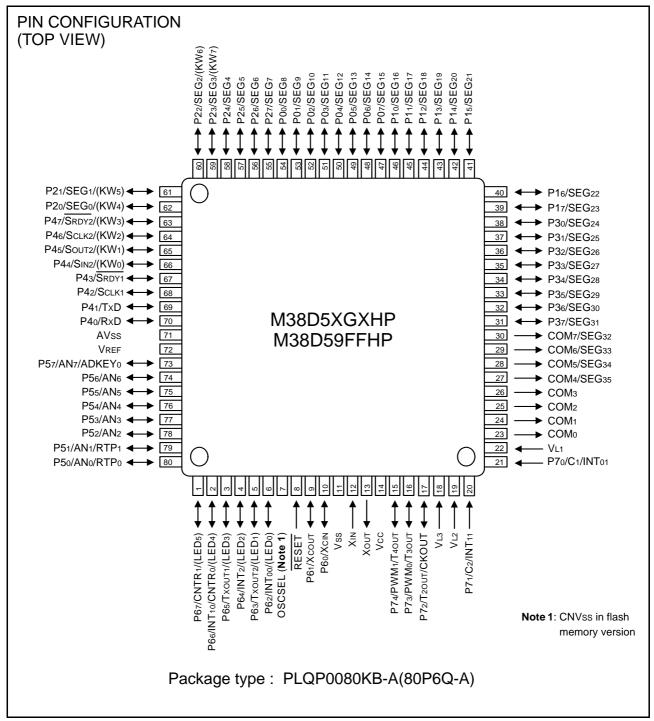

Fig. 2 Pin configuration (LQFP package)

Table 1 Performance overview (1)

|                          | Parameter                               |                    | Function                                                               |  |  |  |

|--------------------------|-----------------------------------------|--------------------|------------------------------------------------------------------------|--|--|--|

| Number of basic instru   | Number of basic instructions            |                    | 71                                                                     |  |  |  |

| Instruction execution ti | me                                      |                    | 0.32 μs (Minimum instruction, Oscillation frequency 12.5 MHz)          |  |  |  |

| Oscillation frequency    |                                         |                    | 16 MHz (Maximum) <sup>(1)</sup>                                        |  |  |  |

| Memory sizes             | ROM                                     |                    | 32 K to 60 K bytes                                                     |  |  |  |

| (QzROM version)          | RAM                                     |                    | 1536 to 2048 bytes                                                     |  |  |  |

| Memory sizes             |                                         |                    | 60 K bytes                                                             |  |  |  |

| (Flash memory version)   |                                         |                    | 2048 bytes                                                             |  |  |  |

| Input port               | P70, P71                                |                    | 2-bit × 1                                                              |  |  |  |

| I/O port                 | P0-P6, P7 <sub>2</sub> -P7 <sub>4</sub> |                    | 8-bit × 7, 3-bit × 1 (36 pins sharing SEG)                             |  |  |  |

| Interrupt                |                                         |                    | 17 sources, 16 vectors (includes key input interrupt)                  |  |  |  |

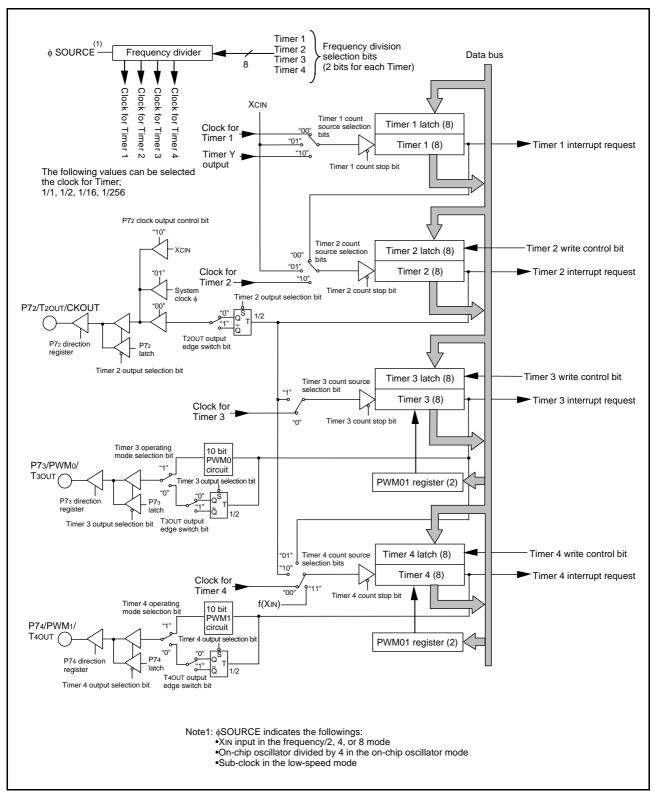

| Timer                    |                                         |                    | 8-bit × 4, 16-bit × 2                                                  |  |  |  |

| Serial I/O1              |                                         |                    | 8-bit × 1 (UART or Clock-synchronized)                                 |  |  |  |

| Serial I/O2              |                                         |                    | 8-bit × 1 (Clock-synchronized)                                         |  |  |  |

| PWM                      |                                         |                    | 10-bit × 2, 16-bit × 1 (common to IGBT output)                         |  |  |  |

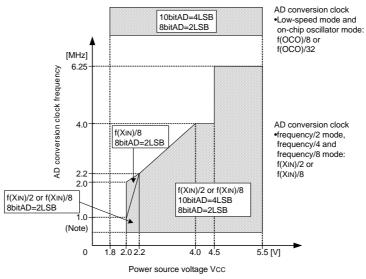

| A/D converter            |                                         |                    | 10-bit × 8 (operated in low-speed mode)                                |  |  |  |

| Watchdog timer           |                                         |                    | 8-bit × 1                                                              |  |  |  |

| ROM correction function  | ROM correction function                 |                    | 32 bytes × 2 vectors                                                   |  |  |  |

| LED direct drive port    |                                         |                    | 6 (average current: 15 mA, peak current: 30 mA, total current: 90 mA   |  |  |  |

| LCD drive control        |                                         |                    | 1/2, 1/3                                                               |  |  |  |

| circuit                  | Duty                                    |                    | Static, 2, 3, 4, 8                                                     |  |  |  |

|                          | Common output                           |                    | 4/8                                                                    |  |  |  |

|                          | Segment output                          |                    | 32/36                                                                  |  |  |  |

| Main clock generating    | circuits                                |                    | Built-in (connect to external ceramic resonator or on-chip oscillator) |  |  |  |

| Sub-clock generating of  | rcuits                                  |                    | Built-in (connect to external quartz-crystal oscillator)               |  |  |  |

|                          | In frequency/2 mode                     | f(XIN) ≤ 12.5 MHz  | 4.5 to 5.5 V                                                           |  |  |  |

| (QzROM version)          | (1)                                     | f(XIN) ≤ 8 MHz     | 4.0 to 5.5 V                                                           |  |  |  |

|                          |                                         | f(XIN) ≤ 4 MHz     | 2.0 to 5.5 V                                                           |  |  |  |

|                          |                                         | f(XIN) ≤ 2 MHz     | 1.8 to 5.5 V                                                           |  |  |  |

|                          | In frequency/4 mode                     | f(XIN) ≤ 16 MHz    | 4.5 to 5.5 V                                                           |  |  |  |

|                          |                                         | f(XIN) ≤ 8 MHz     | 2.0 to 5.5 V                                                           |  |  |  |

|                          |                                         | $f(XIN) \le 4 MHz$ | 1.8 to 5.5 V                                                           |  |  |  |

|                          | In frequency/8 mode                     | f(XIN) ≤ 16 MHz    | 4.5 to 5.5 V                                                           |  |  |  |

|                          |                                         | f(XIN) ≤ 8 MHz     | 2.0 to 5.5 V                                                           |  |  |  |

|                          |                                         | f(XIN) ≤ 4 MHz     | 1.8 to 5.5 V                                                           |  |  |  |

|                          | In low-speed mode                       |                    | 1.8 to 5.5 V                                                           |  |  |  |

| Power source voltage     | In frequency/2 mode                     | f(XIN) ≤ 12.5 MHz  | 4.5 to 5.5 V                                                           |  |  |  |

| (Flash memory version)   | (1)                                     | f(XIN) ≤ 8 MHz     | 4.0 to 5.5 V                                                           |  |  |  |

|                          |                                         | f(XIN) ≤ 4 MHz     | 2.7 to 5.5 V                                                           |  |  |  |

|                          | In frequency/4 mode                     | f(XIN) ≤ 16 MHz    | 4.5 to 5.5 V                                                           |  |  |  |

|                          |                                         | f(XIN) ≤ 8 MHz     | 2.7 to 5.5 V                                                           |  |  |  |

|                          | In frequency/8 mode                     | f(XIN) ≤ 16 MHz    | 4.5 to 5.5 V                                                           |  |  |  |

|                          |                                         | f(XIN) ≤ 8 MHz     | 2.7 to 5.5 V                                                           |  |  |  |

|                          | In low-speed mode                       |                    | 2.7 to 5.5 V                                                           |  |  |  |

NOTE:

1. 12.5 MHz < f(XIN) ≤ 16 MHz is not available in the frequency/2 mode.

Table 2 Performance overview (2)

| Parameter                    |                                | Function                                                                                                         |  |  |  |

|------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| Power dissipation            | In frequency/2 mode            | Std. 32 mW (Vcc = 5 V, f(XIN) = 12.5 MHz, Ta = 25°C)                                                             |  |  |  |

| (QzROM version)              | In low-speed mode              | Std. 18 $\mu$ W (Vcc = 2.5 V, f(XIN) = stop, f(XCIN) = 32 kHz, Ta = 25°C)                                        |  |  |  |

| Power dissipation            | In frequency/2 mode            | Std. 20 mW (Vcc = 5 V, f(XIN) = 12.5 MHz, Ta = 25°C)                                                             |  |  |  |

| (Flash memory version)       | In low-speed mode              | Std. 1.1 mW ( $Vcc = 2.7 \text{ V}$ , $f(XIN) = \text{stop}$ , $f(XCIN) = 32 \text{ kHz}$ , $Ta = 25^{\circ}C$ ) |  |  |  |

| Input/Output characteristics | Input/Output withstand voltage | Vcc                                                                                                              |  |  |  |

|                              | Output current                 | 10 mA                                                                                                            |  |  |  |

| Operating temperature range  |                                | -20 to 85°C                                                                                                      |  |  |  |

| Device structure             |                                | CMOS silicon gate                                                                                                |  |  |  |

| Package                      |                                | 80-pin plastic molded LQFP/QFP                                                                                   |  |  |  |

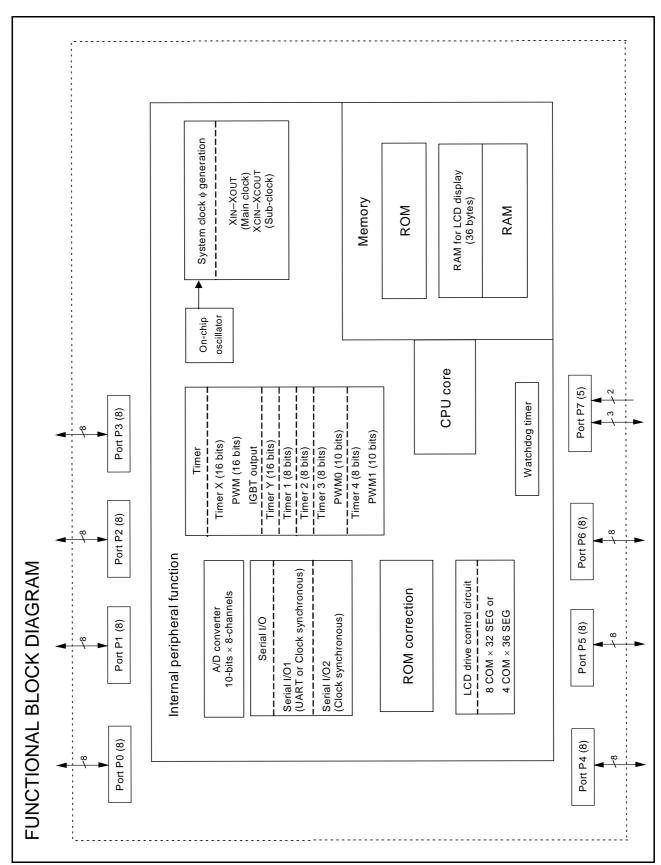

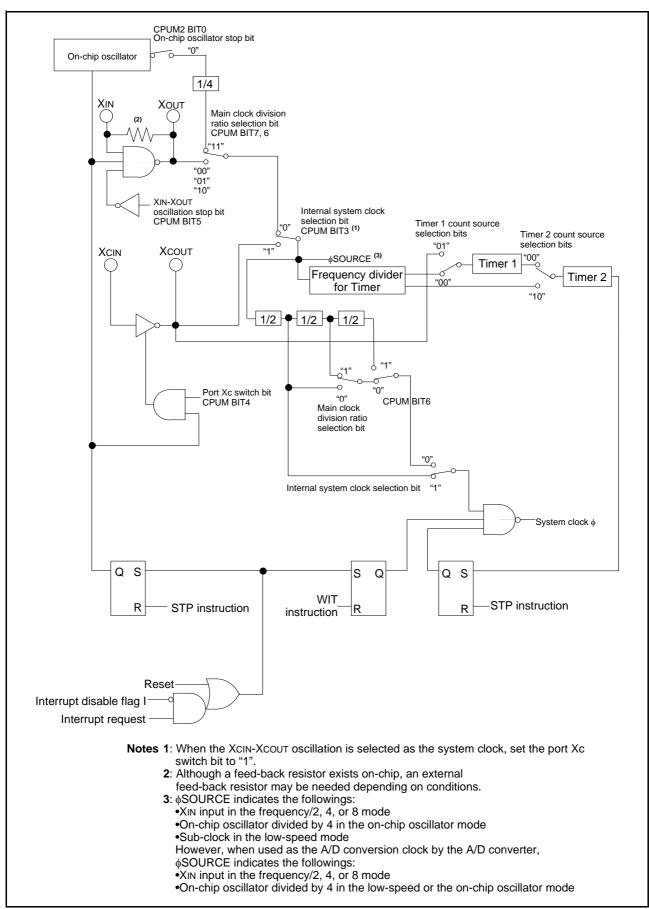

Fig. 3 Functional block diagram

# PIN DESCRIPTION

Table 3 Pin description (1)

| Pin                                                                                                                     | Name             | Function                                                                                                                                                                                                                                                                       |                                                    |                                   |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------|--|--|--|--|--|

|                                                                                                                         |                  |                                                                                                                                                                                                                                                                                |                                                    | pt a port function                |  |  |  |  |  |

| Vcc, Vss                                                                                                                | Power source     | Apply power source voltage to Vcc, and 0 V to Vss                                                                                                                                                                                                                              | S                                                  |                                   |  |  |  |  |  |

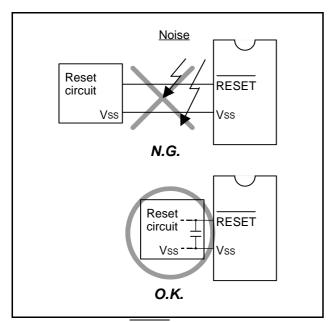

| RESET                                                                                                                   | Reset input      | Reset input pin for active "L".                                                                                                                                                                                                                                                |                                                    |                                   |  |  |  |  |  |

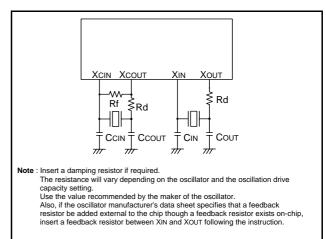

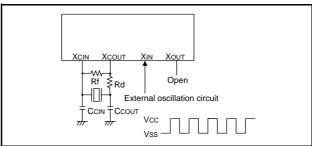

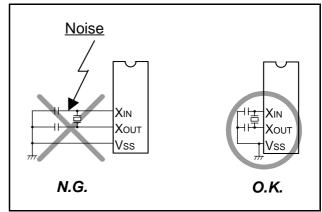

| XIN                                                                                                                     | Clock input      | Input and output pins for the main clock generating                                                                                                                                                                                                                            |                                                    |                                   |  |  |  |  |  |

| Хоит                                                                                                                    | Clock output     | Connect a ceramic resonator or a quartz-crystal oscillator between the XIN and XOUT pins set the oscillation frequency. When an external clock is used, connect the clock source to XIN, and leave XOUT pin open.  Feedback resistor is built in between XIN pin and XOUT pin. |                                                    |                                   |  |  |  |  |  |

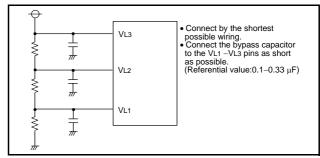

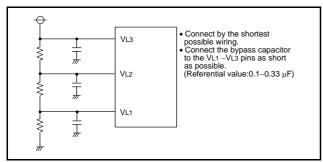

| VL1, VL2, VL3                                                                                                           | LCD power source | <ul> <li>Input 0 ≤ VL1 ≤ VL2 ≤ VL3 voltage.</li> <li>Input 0 − VL3 voltage to LCD.</li> </ul>                                                                                                                                                                                  |                                                    |                                   |  |  |  |  |  |

| COM <sub>0</sub> –                                                                                                      | Common output    | LCD common output pins.                                                                                                                                                                                                                                                        |                                                    |                                   |  |  |  |  |  |

| СОМ3                                                                                                                    |                  | <ul> <li>COM<sub>2</sub> and COM<sub>3</sub> are not used at 1/2 duty ratio.</li> <li>COM<sub>3</sub> is not used at 1/3 duty ratio.</li> </ul>                                                                                                                                |                                                    |                                   |  |  |  |  |  |

| COM4/SEG35-                                                                                                             | Common output    | LCD common/segment output pins.                                                                                                                                                                                                                                                |                                                    |                                   |  |  |  |  |  |

| COM7/SEG32                                                                                                              | Segment output   |                                                                                                                                                                                                                                                                                |                                                    |                                   |  |  |  |  |  |

| P00/SEG8-<br>P07/SEG15                                                                                                  | I/O port P0      | <ul> <li>8-bit I/O port.</li> <li>CMOS compatible input level.</li> <li>CMOS 3-state output structure.</li> <li>I/O direction register allows each pin to be individually programmed as either input or output.</li> <li>Pull-up control is enabled in a bit unit.</li> </ul>  |                                                    |                                   |  |  |  |  |  |

| P10/SEG16-<br>P17/SEG23                                                                                                 | I/O port P1      | 8-bit I/O port.     CMOS compatible input level.     CMOS 3-state output structure.     I/O direction register allows each pin to be programmed as either input or output.     Pull-up control is enabled in 4-bit unit.                                                       |                                                    |                                   |  |  |  |  |  |

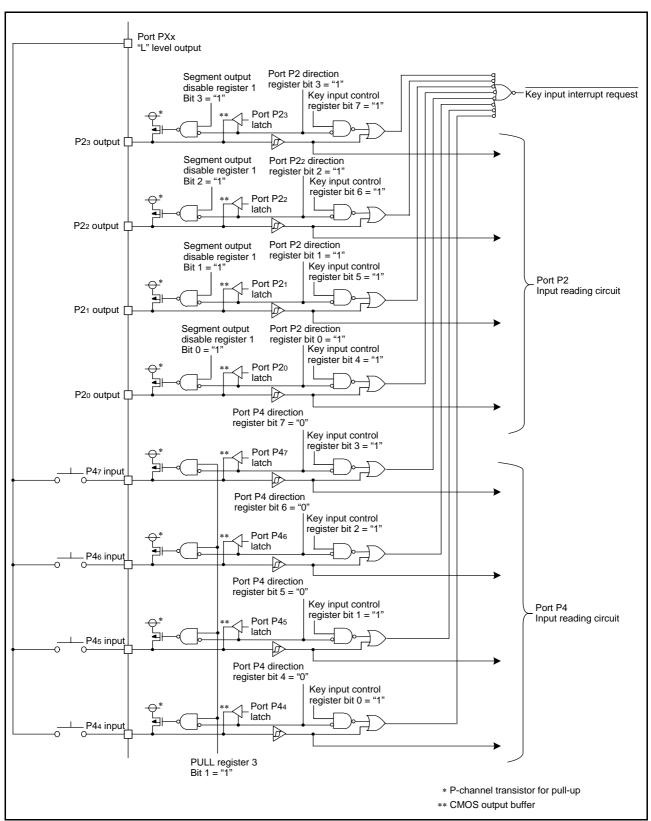

| P20/SEG0/(KW4)—<br>P23/SEG3/(KW7)<br>P24/SEG4—<br>P27/SEG7                                                              | I/O port P2      | 8-bit I/O port.     CMOS compatible input level.     CMOS 3-state output structure.     I/O direction register allows each pin to be individually programmed as either input or output.     Pull-up control is enabled in a bit unit.                                          |                                                    | Key input interrupt<br>input pins |  |  |  |  |  |

| P30/SEG24-<br>P37/SEG31                                                                                                 | I/O port P3      | 8-bit I/O port.     CMOS compatible input level.     CMOS 3-state output structure.     I/O direction register allows each pin to be individually programmed as either input or output.     Pull-up control is enabled in 4-bit unit.                                          |                                                    |                                   |  |  |  |  |  |

| P40/RxD<br>P41/TxD<br>P42/Sclk1<br>P43/SRDY1<br>P44/SIN2/(KW0)<br>P45/SOUT2/(KW1)<br>P46/Sclk2/(KW2)<br>P47/SRDY2/(KW3) | I/O port P4      | 8-bit I/O port.     CMOS compatible input level.     CMOS 3-state output structure.     I/O direction register allows each pin to be individually programmed as either input or output.     Pull-up control is enabled in 4-bit unit.                                          | Serial I/O1 function     Serial I/O2 function pins | Key input interrupt input pins    |  |  |  |  |  |

Table 4 Pin description (2)

| D'                                                  | Niema                           | Forefore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |                                                                           |

|-----------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------|

| Pin                                                 | Name                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Function excep                                                      | ot a port function                                                        |

| P50/AN0/RTP0<br>P51/AN1/RTP1<br>P52/AN2-<br>P56/AN6 | I/O port P5                     | 8-bit I/O port.     CMOS compatible input level.     CMOS 3-state output structure.     I/O direction register allows each pin to be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | AD converter<br>input pins                                          | Real time port<br>function pins                                           |

| P57/AN7/ADKEY0                                      |                                 | individually programmed as either input or output.  • Pull-up control is enabled in a bit unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     | ADKEY input pin                                                           |

| P60/XCIN<br>P61/XCOUT<br>P62/INT00/(LED0)           | I/O port P6                     | 8-bit I/O port.     CMOS compatible input level.     CMOS 3-state output structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Sub clock generati<br>(oscillator connecti     External interrupt g | ed)                                                                       |

| P63/Txout2/(LED1)                                   |                                 | I/O direction register allows each pin to be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Timer X output pin                                                  |                                                                           |

| P64/INT2/(LED2)                                     |                                 | individually programmed as either input or output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | External interrupt p                                                |                                                                           |

| P65/Txout1/(LED3)                                   |                                 | <ul> <li>Pull-up control is enabled in a bit unit.</li> <li>P62 to P67 (6 bits) are enabled to output large</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Timer X output pin                                                  |                                                                           |

| P66/INT10/CNTR0/<br>(LED4)<br>P67/CNTR1/(LED5)      |                                 | current for LED drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Timer X, Timer Y output pins                                        | External interrupt pins                                                   |

| P70/C1/INT01<br>P71/C2/INT11                        | Input port P7                   | 2-bit input port.     CMOS input level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | External interrupt<br>pins                                          | External<br>capacitor connect<br>pins for a voltage<br>multiplier of LCD. |

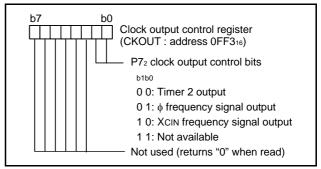

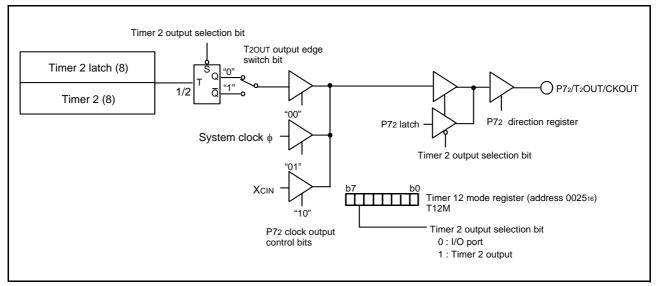

| P72/T2OUT/CKOUT                                     | I/O port P7                     | • 3-bit I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Clock output pin                                                    | Timer 2 output pin                                                        |

| P73/PWM0/T30UT<br>P74/PWM1/T40UT                    |                                 | <ul> <li>CMOS compatible input level.</li> <li>CMOS 3-state output structure.</li> <li>I/O direction register allows each pin to be individually programmed as either input or output.</li> <li>Pull-up control is enabled in 3-bit unit.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PWM output pins                                                     | Timer 3 output pin Timer 4 output pin                                     |

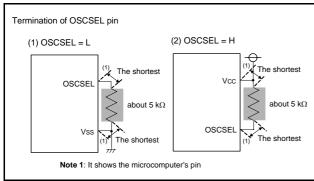

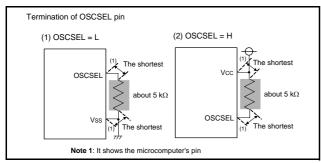

| OSCSEL<br>(Only QzROM<br>version)                   | Oscillation start selection pin | Whether oscillation starts by an oscillator between oscillator is selected.     VPP power source input pin in the QzROM writing it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ·                                                                   | s or an on-chip                                                           |

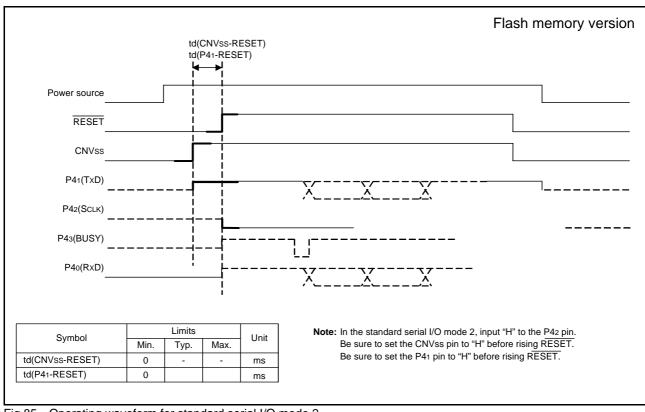

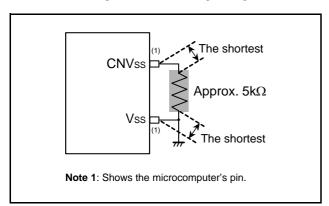

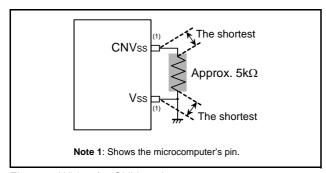

| CNVss<br>(Only flash memory<br>version)             | CNVss                           | Pin for controlling the operating mode of the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Connect to Vss.                                                     |                                                                           |

| VREF                                                | Analog reference voltage        | Reference voltage input pin for A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                     |                                                                           |

| AVss                                                | Analog power source             | Analog power source input pin for A/D converter. C | Connect to Vss.                                                     |                                                                           |

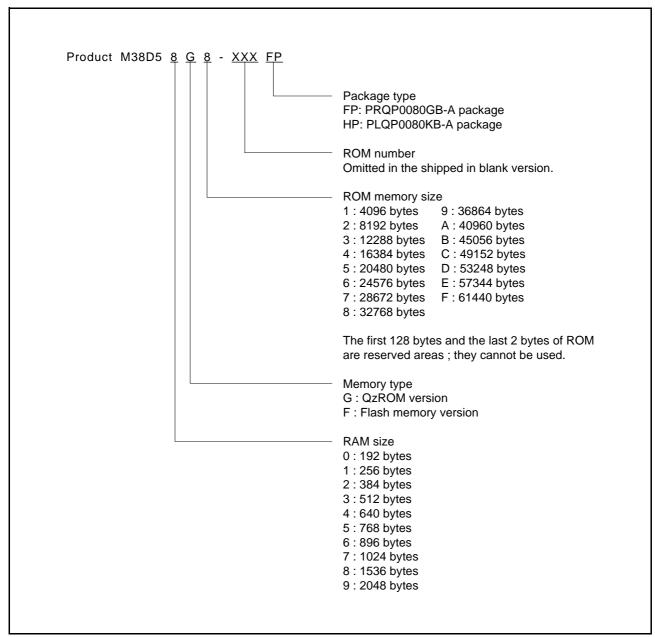

# **PART NUMBERING**

Fig. 4 Part numbering

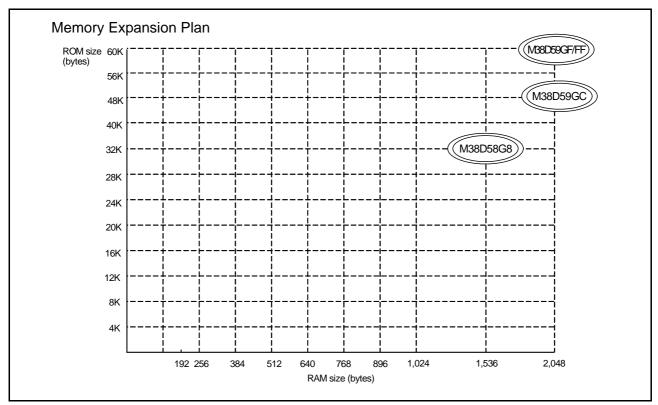

# **GROUP EXPANSION**

Renesas plans to expand the 38D5 Group as follows.

# **Memory Size**

- <QzROM version>

- <Flash memory version>

- ROM size ...... 60 K bytes

# **Packages**

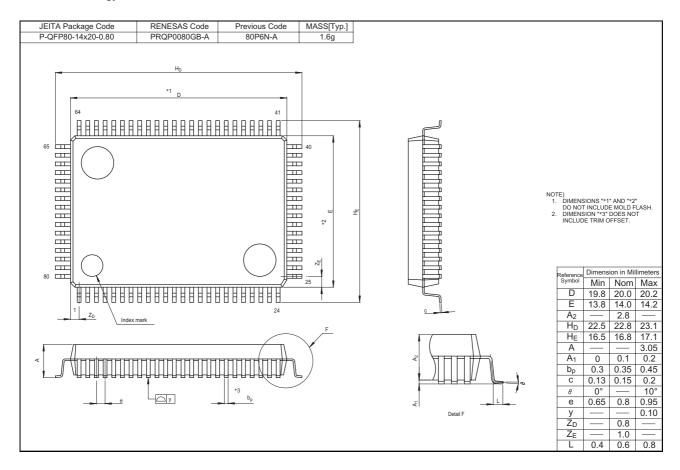

- PRQP0080GB-A ......0.8 mm-pitch plastic molded QFP

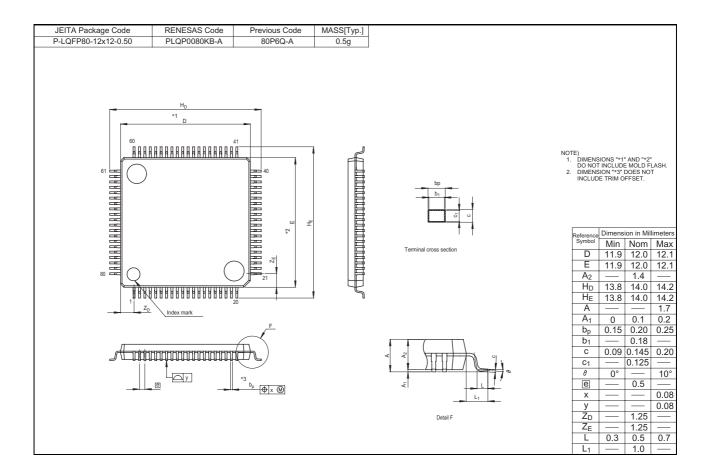

- PLQP0080KB-A ......0.5 mm-pitch plastic molded LQFP

Fig. 5 Memory expansion plan

Currently supported products are listed below.

Table 5 Support products

As of Apr. 2008

| Part No.       | ROM size (bytes)<br>ROM size for User in ( ) | RAM size<br>(bytes) | Package      | Remarks               |

|----------------|----------------------------------------------|---------------------|--------------|-----------------------|

| M38D58G8-XXXFP | 32768 (32638)                                | 1536                | PRQP0080GB-A | QzROM version         |

| M38D58G8-XXXHP |                                              |                     | PLQP0080KB-A |                       |

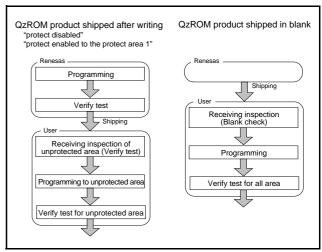

| M38D58G8FP     | 32768 (32638)                                | 1536                | PRQP0080GB-A | QzROM version (blank) |

| M38D58G8HP     |                                              |                     | PLQP0080KB-A |                       |

| M38D59GC-XXXFP | 49152 (49022)                                | 2048                | PRQP0080GB-A | QzROM version         |

| M38D59GC-XXXHP |                                              |                     | PLQP0080KB-A |                       |

| M38D59GCFP     | 49152 (49022)                                | 2048                | PRQP0080GB-A | QzROM version (blank) |

| M38D59GCHP     |                                              |                     | PLQP0080KB-A |                       |

| M38D59GF-XXXFP | 61440 (61310)                                | 2048                | PRQP0080GB-A | QzROM version         |

| M38D59GF-XXXHP |                                              |                     | PLQP0080KB-A |                       |

| M38D59GFFP     | 61440 (61310)                                | 2048                | PRQP0080GB-A | QzROM version (blank) |

| M38D59GFHP     |                                              |                     | PLQP0080KB-A | 7                     |

| M38D59FFFP     | 61440 (61310)                                | 2048                | PRQP0080GB-A | Flash memory version  |

| M38D59FFHP     |                                              |                     | PLQP0080KB-A |                       |

Table 6 Differences between QzROM and flash memory versions

|                                                                          | QzROM                                    | l version          | Flash memory version                                                      |

|--------------------------------------------------------------------------|------------------------------------------|--------------------|---------------------------------------------------------------------------|

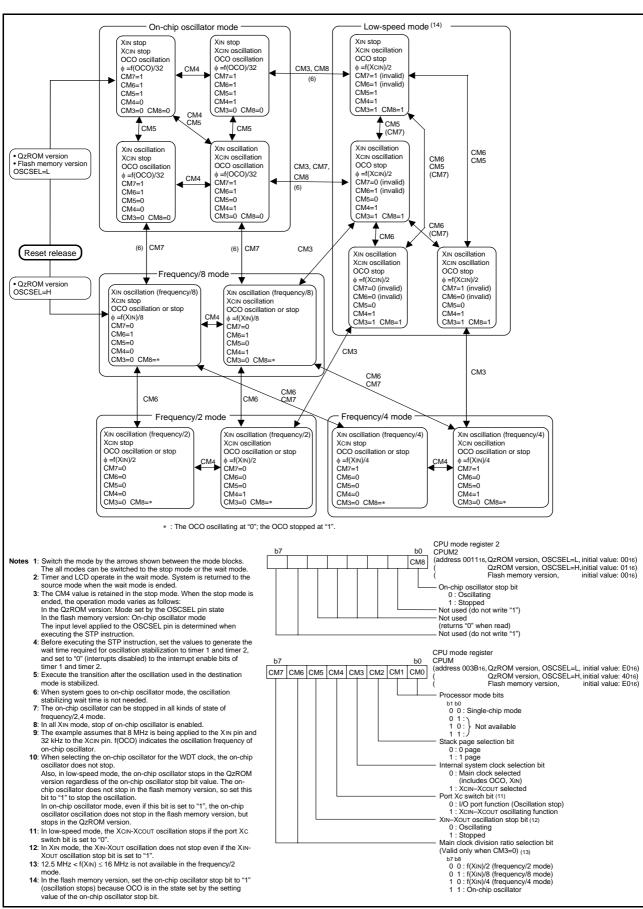

| Oscillation circuit at reset and at returning from stop mode             | Main clock XIN or on-ch<br>by OSCSEL pin | On-chip oscillator |                                                                           |

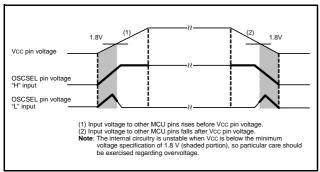

| Termination of OSCEL/CNVss pin                                           | OSCSEL = "H"                             | OSCSEL = "L"       | CNVss = "L"                                                               |

| Main clock oscillation at reset and at returning from stop mode          | Oscillation on                           | Stop               | Stop                                                                      |

| On-chip oscillator oscillation at reset and at returning from stop mode  | Stop                                     | Oscillation on     | Oscillation on                                                            |

| System clock φ oscillation at reset and at returning<br>I from stop mode | f(XIN)/8                                 | f(OCO)/32          | f(OCO)/32                                                                 |

| Mounting of main clock oscillation circuit                               | Required                                 | Optional           | Optional                                                                  |

| On-chip oscillator oscillation in low speed-mode                         | Stop                                     |                    | Stop by setting the on-chip oscillator stop bit because i is not stopped. |

| Writing "1" to on-chip oscillator stop bit in on-chip oscillator mode    | On-chip oscillator is stopped            |                    | On-chip oscillator is not stopped                                         |

| Reset input "L" pulse width                                              | 2 μs or more                             |                    | 2 ms or more                                                              |

| Absolute maximum rating: OSCSEL/CNVss pin                                | -0.3 to 8.0                              |                    | -0.3 to Vcc + 0.3                                                         |

| Minimum operating power source voltage                                   | 1.8 V                                    |                    | 2.7 V                                                                     |

| A/D converter minimum operating power source voltage                     | 2.0                                      | 2.7 V              |                                                                           |

### NOTE:

# Notes on Differences between QzROM and Flash Memory Versions

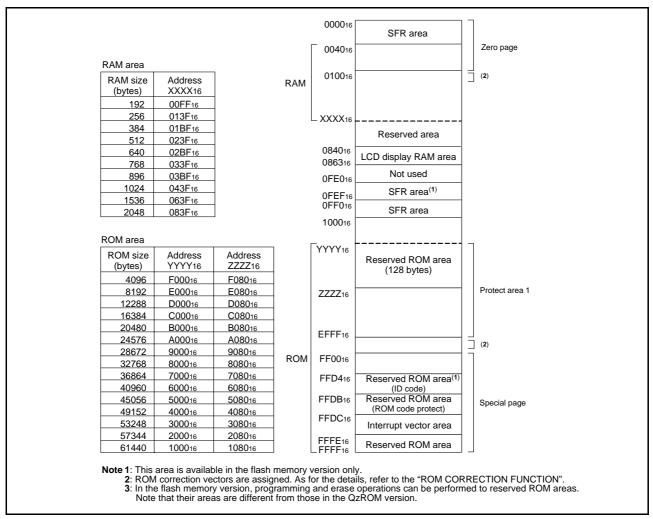

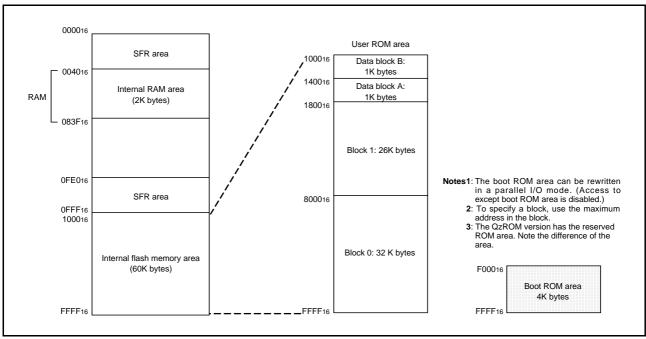

- (1) The memory map, the writing modes and programming circuits vary because of the differences in their internal memories.

- (2) The oscillation parameters of XIN-XOUT and XCIN-XCOUT may vary.

- (3) The QzROM version and the flash memory version MCUs differ in their manufacturing processes, built-in ROM, and layout patterns. Because of these differences, characteristic values, operation margins, A/D conversion accuracy, noise immunity, and noise radiation may vary within the specified range of electrical characteristics.

- (4) When switching from the flash memory version to the QzROM version, implement system evaluations equivalent to those implemented in the flash memory version.

- (5) The both operations except the electrical characteristics are same at the emulator (emulator MCU board: M38D59T-RLFS).

<sup>1.</sup> For detailed specifications, confirm the descriptions in the Datasheet.

### **FUNCTIONAL DESCRIPTION**

### **Central Processing Unit (CPU)**

The 38D5 Group uses the standard 740 Family instruction set. Refer to the 740 Family Software Manual for details on the instruction set.

Machine-resident 740 Family instructions are as follows:

The FST and SLW instructions cannot be used.

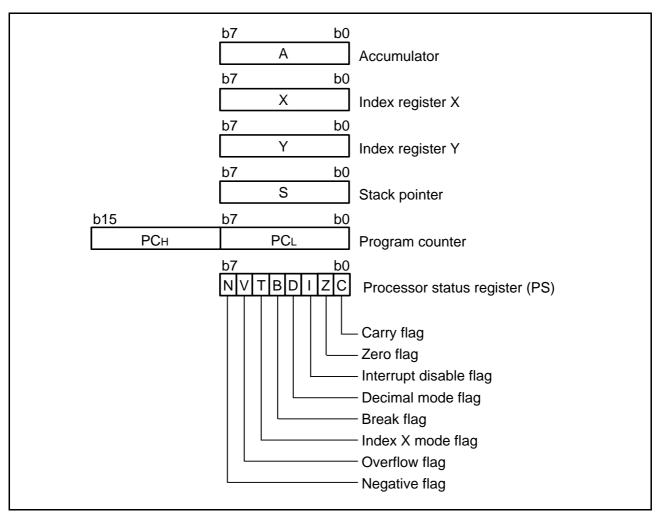

The STP, WIT, MUL, and DIV instructions can be used. The central processing unit (CPU) has six registers. Figure 6 shows the 740 Family CPU register structure.

### [Accumulator (A)]

The accumulator is an 8-bit register. Data operations such as arithmetic data transfer, etc., are executed mainly through the accumulator.

### [Index Register X (X)]

The index register X is an 8-bit register. In the index addressing modes, the value of the OPERAND is added to the contents of register X and specifies the real address.

## [Index Register Y (Y)]

The index register Y is an 8-bit register. In partial instruction, the value of the OPERAND is added to the contents of register Y and specifies the real address.

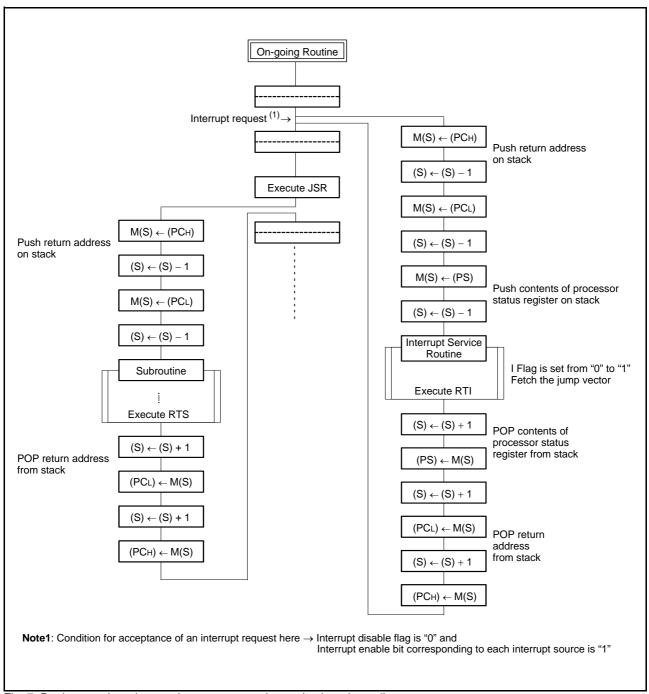

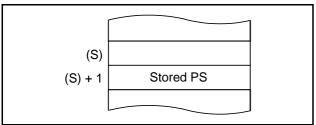

## [Stack Pointer (S)]

The stack pointer is an 8-bit register used during subroutine calls and interrupts. This register indicates start address of stored area (stack) for storing registers during subroutine calls and

The low-order 8 bits of the stack address are determined by the contents of the stack pointer. The high-order 8 bits of the stack address are determined by the stack page selection bit. If the stack page selection bit is "0", the high-order 8 bits becomes "0016". If the stack page selection bit is "1", the high-order 8 bits becomes "0116".

The operations of pushing register contents onto the stack and popping them from the stack are shown in Figure 7.

Table 7 shows the push and pop instructions of accumulator or processor status register.

Store registers other than those described in Figure 7 with program when the user needs them during interrupts or subroutine calls.

## [Program Counter (PC)]

The program counter is a 16-bit counter consisting of two 8-bit registers PCH and PCL. It is used to indicate the address of the next instruction to be executed.

Fig. 6 740 Family CPU register structure

Fig. 7 Register push and pop at interrupt generation and subroutine call

Table 7 Push and pop instructions of accumulator or processor status register

|                           | Push instruction to stack | Pop instruction from stack |

|---------------------------|---------------------------|----------------------------|

| Accumulator               | PHA                       | PLA                        |

| Processor status register | PHP                       | PLP                        |

### [Processor Status Register (PS)]

The processor status register is an 8-bit register consisting of 5 flags which indicate the status of the processor after an arithmetic operation and 3 flags which decide MCU operation. Branch operations can be performed by testing the Carry (C) flag, Zero (Z) flag, Overflow (V) flag, or the Negative (N) flag. In decimal mode, the Z, V, N flags are not valid.

# • Bit 0: Carry flag (C)

The C flag contains a carry or borrow generated by the arithmetic logic unit (ALU) immediately after an arithmetic operation. It can also be changed by a shift or rotate instruction.

• Bit 1: Zero flag (Z)

The Z flag is set to "1" if the result of an immediate arithmetic operation or a data transfer is "0", and set to "0" if the result is anything other than "0".

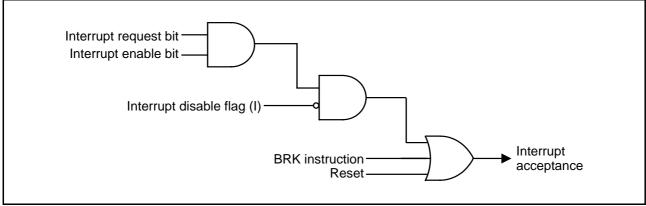

• Bit 2: Interrupt disable flag (I)

The I flag disables all interrupts except for the interrupt generated by the BRK instruction.

Interrupts are disabled when the I flag is "1".

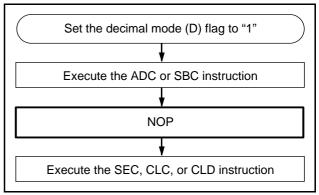

• Bit 3: Decimal mode flag (D)

The D flag determines whether additions and subtractions are executed in binary or decimal. Binary arithmetic is executed when this flag is "0"; decimal arithmetic is executed when it is