# PM6641

# Monolithic VR for chipset and DDR2/3 supply for ultra-mobile PC (UMPC) applications

# Features

- 0.8 V ±1 % internal voltage reference

- 2.7 V to 5.5 V input voltage range

- Fast response, constant frequency, current mode control

- Three independent, adjustable, out-of-phase SMPS for DDR2/3 (VDDQ) and chipset supply

- Low noise DDR2/3 reference (VTTREF)

- ±2 Apk LDO for DDR2/3 termination (VTT) with foldback

- S0-S5 states compliant DDR2/3 section

- Active soft-end for all outputs

- Selectable tracking discharge for VDDQ

- Separate power-good signals

- Pulse skipping at light load

- Programmable current limit and soft-start for all outputs

- Latched OVP, UVP protection

- Thermal protection

# Applications

- DDR2/3 memory and chipset supply

- UMPC and portable equipment

- Handheld and PDAs

# Description

The PM6641 is a monolithic voltage regulator module specifically designed to supply DDR2/3 memory and chipset in ultra-mobile PC and real estate constrained portable systems.

It integrates three independent, adjustable, constant frequency buck converters, a  $\pm 2$  Apk Low Drop-Out (LDO) linear regulator and a  $\pm 15$  mA low noise buffered reference.

Each regulator provides basic UV and OV Protections, programmable Soft-Start and Current Limit and active Soft-End.

Pulse-Skipping technique is performed to increase efficiency at very light load.

#### Table 1. Device summary

| Part number | Package Packaging           |             |

|-------------|-----------------------------|-------------|

| PM6641      | VFQFPN-48 7x7 (exposed pad) | Tray        |

| PM6641TR    | VFQFPN-48 7x7 (exposed pad  | Tape & reel |

January 2008

# Contents

| 1 | Туріса | al application circuit                      |

|---|--------|---------------------------------------------|

| 2 | Pin se | ettings                                     |

|   | 2.1    | Connections                                 |

|   | 2.2    | Pin description                             |

| 3 | Electr | ical data                                   |

|   | 3.1    | Maximum rating                              |

|   | 3.2    | Thermal data                                |

|   | 3.3    | Recommended operating conditions 8          |

| 4 | Electr | ical characteristics9                       |

| 5 | Туріса | al operating characteristics14              |

| 6 | Block  | diagram                                     |

| 7 | Devic  | e description                               |

|   | 7.1    | Memory supply                               |

|   |        | 7.1.1 VDDQ switching regulator              |

|   |        | 7.1.2 VTT LDO and VTTREF buffered reference |

|   |        | 7.1.3 VTT and VTTREF Soft Start             |

|   |        | 7.1.4 S3 and S5 power management pins       |

|   | 7.2    | Chipset supply 22                           |

|   | 7.3    | SW regulators control loop 24               |

|   | 7.4    | SW regulators pulse skipping and PWM mode   |

|   | 7.5    | Output voltage divider 27                   |

|   | 7.6    | Outputs Soft-Start                          |

|   | 7.7    | Outputs Soft-End                            |

|   | 7.8    | Switching frequency selection               |

|   | 7.9    | Phase management                            |

|   | 7.10   | Peak current limit                          |

|   | 7.11   | Fault management                            |

|    |      | 7.11.1     | Output over voltage                      |    |

|----|------|------------|------------------------------------------|----|

|    |      | 7.11.2     | Output under voltage                     |    |

|    |      | 7.11.3     | Thermal shutdown                         |    |

|    |      | 7.11.4     | Input under voltage lock-out             |    |

| 8  | Com  | ponents    | selection                                |    |

|    | 8.1  | Inducto    | r selection                              |    |

|    | 8.2  | Input ca   | apacitor selection                       |    |

|    | 8.3  | Output     | capacitor selection                      |    |

|    | 8.4  | SW reg     | ulator compensation components selection |    |

|    | 8.5  | Layout     | guidelines                               | 40 |

| 9  | Арр  | lication e | examples                                 | 41 |

|    | 9.1  | UMPC       | DDR2 and chipset power supply            | 41 |

| 10 | Pack | kage med   | chanical data                            | 44 |

| 11 | Revi | sion his   | tory                                     | 46 |

57

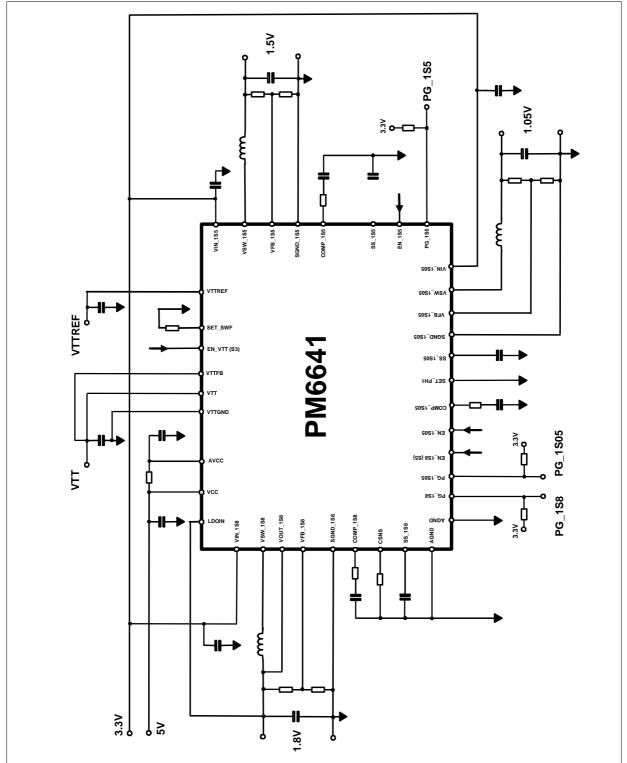

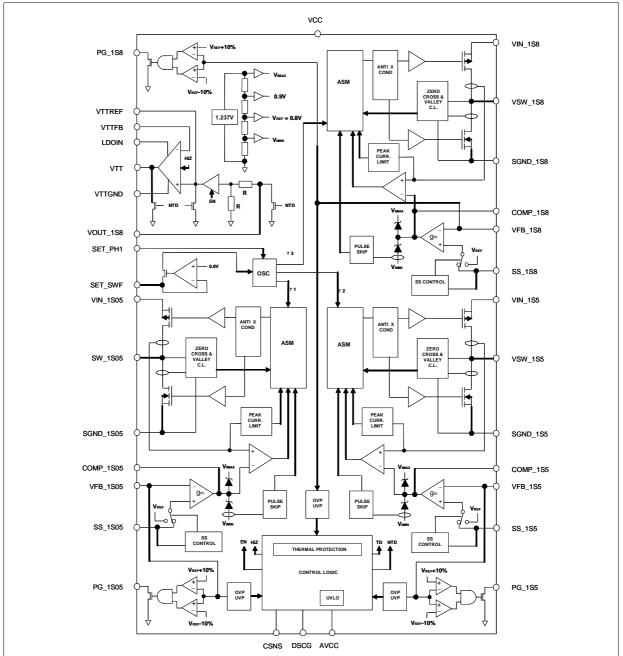

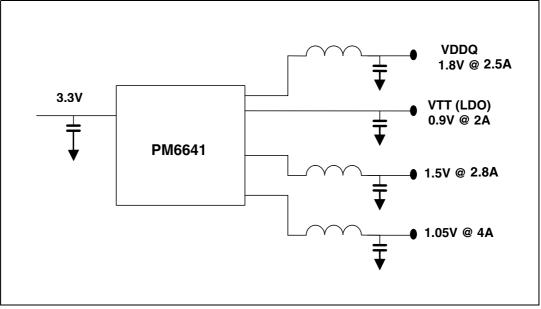

# **1** Typical application circuit

## Figure 1. Application circuit

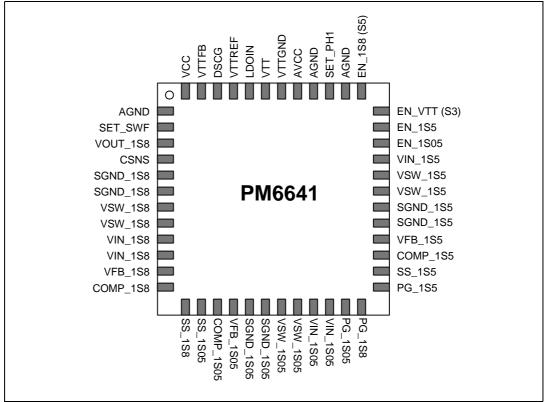

# 2 Pin settings

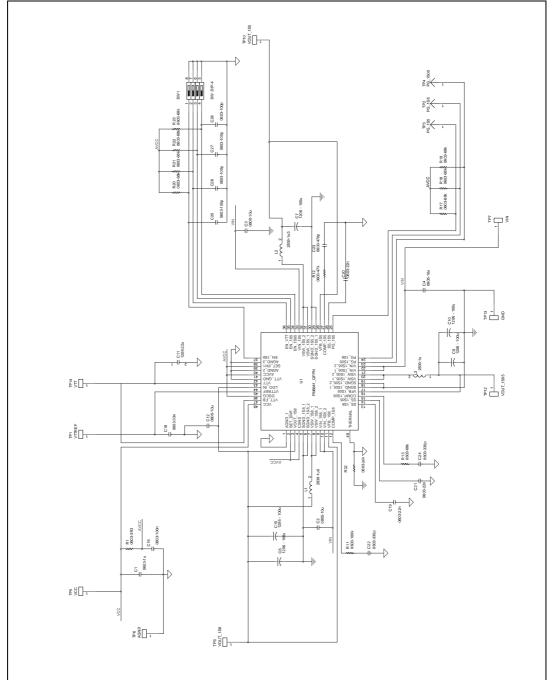

## 2.1 Connections

Figure 2. Pin connection (through top view)

# 2.2 Pin description

### Table 2. Pin functions

| N° | Pin       | Function                                                                                                                                                                                                       |

|----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | AGND      | Analog and signal ground.                                                                                                                                                                                      |

| 2  | SET_SWF   | Switching Frequency Setting Input.<br>See <i>Chapter 7.8: Switching frequency selection on page 29</i>                                                                                                         |

| 3  | VOUT_1S8  | VDDQ/2 Divider Input and Discharge path for 1.8 V rail.                                                                                                                                                        |

| 4  | CSNS      | Current Limit Setting Input for All rails.<br>See <i>Chapter 7.10: Peak current limit on page 31</i>                                                                                                           |

| 5  | SGND_1S8  | Switcher power ground for 1.8 V rail.                                                                                                                                                                          |

| 6  | SGND_1S8  | Switcher power ground for 1.8 V rail.                                                                                                                                                                          |

| 7  | VSW_1S8   | Switch node for 1.8 V rail.                                                                                                                                                                                    |

| 8  | VSW_1S8   | Switch node for 1.8 V rail.                                                                                                                                                                                    |

| 9  | VIN_1S8   | Power supply input for 1.8 V rail.                                                                                                                                                                             |

| 10 | VIN_1S8   | Power supply input for 1.8 V rail.                                                                                                                                                                             |

| 11 | VFB_1S8   | Feedback Input for 1.8 V rail.<br>See <i>Chapter 7.5: Output voltage divider on page 27</i>                                                                                                                    |

| 12 | COMP_1S8  | Loop Compensation Output for 1.8 V rail. See <i>Chapter 7.3: SW regulators</i> control loop on page 24 and <i>Chapter 8.4: SW regulator compensation</i> components selection on page 38 sections for details. |

| 13 | SS_1S8    | Positive Terminal of the external Soft-Start Capacitor for 1.8 V rail.<br>See <i>Chapter 7.6: Outputs Soft-Start on page 28</i> section for details.                                                           |

| 14 | SS_1S05   | Positive Terminal of the external Soft-Start Capacitor for 1.05 V rail.<br>See <i>Chapter 7.6: Outputs Soft-Start on page 28</i> section for details.                                                          |

| 15 | COMP_1S05 | Loop Compensation Output for 1.05 V rail. See <i>Chapter 7.3: SW regulators</i> control loop on page 24 and <i>Chapter 8.4: SW regulator compensation</i> components selection on page 38 for details.         |

| 16 | VFB_1S05  | Feedback Input for 1.05 V rail.<br>See <i>Chapter 7.5: Output voltage divider on page 27</i> section for details                                                                                               |

| 17 | SGND_1S05 | Switcher power ground for 1.05 V rail.                                                                                                                                                                         |

| 18 | SGND_1S05 | Switcher power ground for 1.05 V rail.                                                                                                                                                                         |

| 19 | VSW_1S05  | Switch node for 1.05 V rail.                                                                                                                                                                                   |

| 20 | VSW_1S05  | Switch node for 1.05 V rail.                                                                                                                                                                                   |

| 21 | VIN_1S05  | Power supply input for 1.05 V rail.                                                                                                                                                                            |

| 22 | VIN_1S05  | Power supply input for 1.05 V rail.                                                                                                                                                                            |

| 23 | PG_1S05   | Power-Good Signal for 1.05 V rail. Open Drain. See <i>Chapter 7.2: Chipset</i> supply on page 22 section for details.                                                                                          |

| 24 | PG_1S8    | Power-Good Signal for 1.8 V rail. Open Drain. See <i>Chapter 7.1.1: VDDQ switching regulator on page 20</i> section for details.                                                                               |

| 25 | PG_1S5    | Power-Good Signal for 1.5 V rail. Open Drain. See <i>Chapter 7.2: Chipset supply on page 22</i> section for details.                                                                                           |

| N° | Pin      | Function                                                                                                                                                                                                   |

|----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26 | SS_1S5   | Positive terminal of the external Soft-Start Capacitor for 1.5 V rail.<br>See <i>Chapter 7.6: Outputs Soft-Start on page 28</i> section for details.                                                       |

| 27 | COMP_1S5 | Loop Compensation Output for 1.5 V rail. <i>Chapter 7.3: SW regulators control loop on page 24</i> and <i>Chapter 8.4: SW regulator compensation components selection on page 38</i> sections for details. |

| 28 | VFB_1S5  | Feedback Input for 1.5 V rail.<br>See <i>Chapter 7.5: Output voltage divider on page 27</i> section for details                                                                                            |

| 29 | SGND_1S5 | Switcher power ground for 1.5 V rail.                                                                                                                                                                      |

| 30 | SGND_1S5 | Switcher power ground for 1.5 V rail.                                                                                                                                                                      |

| 31 | VSW_1S5  | Switch node for 1.5 V rail.                                                                                                                                                                                |

| 32 | VSW_1S5  | Switch node for 1.5 V rail.                                                                                                                                                                                |

| 33 | VIN_1S5  | Power supply input for 1.5 V rail.                                                                                                                                                                         |

| 34 | EN_1S05  | Enable input for 1.05 V rail.                                                                                                                                                                              |

| 35 | EN_1S5   | Enable input for 1.5 V rail.                                                                                                                                                                               |

| 36 | EN_VTT   | Enable Input for VTT rail. High in S0 System States. See <i>Chapter 7.1.4: S3</i> and <i>S5 power management pins on page 22</i> section for details.                                                      |

| 37 | EN_1S8   | Enable Input for 1.8 V (VDDQ) rail. High in S0-S3 System States.<br>See <i>Chapter 7.1.4: S3 and S5 power management pins on page 22</i> section for details.                                              |

| 38 | AGND     | Analog and Signal Ground.                                                                                                                                                                                  |

| 39 | SET_PH1  | Switching Regulator Phase Control.<br>See <i>Chapter 7.9: Phase management on page 30</i> section for details.                                                                                             |

| 40 | AGND     | Analog and Signal Ground.                                                                                                                                                                                  |

| 41 | AVCC     | Analog Circuitry Supply. Connect to +5 V by a simple RC filter.                                                                                                                                            |

| 42 | VTTGND   | LDO Linear Regulator Power Ground.                                                                                                                                                                         |

| 43 | VTT      | LDO Linear Regulator Output. DDR2-3 Termination Voltage. See<br>Chapter 7.1: Memory supply on page 20 and Chapter 7.1.2: VTT LDO and<br>VTTREF buffered reference on page 21 sections for details.         |

| 44 | LDOIN    | LDO Linear Regulator Input. Typically connected to the 1.8 V rail.                                                                                                                                         |

| 45 | VTTREF   | Reference Voltage Buffer Output. See <i>Chapter 7.1: Memory supply on page 20</i> and <i>Chapter 7.1.2: VTT LDO and VTTREF buffered reference on page 21</i> sections for details.                         |

| 46 | DSCG     | Tracking/Non-tracking Discharge Selection for DDR2-3 Section. See <i>Chapter 7.7: Outputs Soft-End on page 29</i> section for details.                                                                     |

| 47 | VTTFB    | Feedback Input for VTT Linear Regulator Output.                                                                                                                                                            |

| 48 | VCC      | +5 V Switching Circuitry Supply. Bypass to AGND by a 100 nF capacitor.                                                                                                                                     |

### Table 2. Pin functions (continued)

# 3 Electrical data

# 3.1 Maximum rating

### Table 3. Absolute maximum ratings <sup>(1)</sup>

| Symbol            | Parame                                                                            | ter                                                                                                                                            | Value                           | Unit |

|-------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|

| V <sub>VIN</sub>  | VIN_x to SGND_x                                                                   | N N                                                                                                                                            |                                 |      |

| V <sub>VCC</sub>  | VCC to AGND or SGND_x                                                             | V <sub>IN</sub> = V <sub>AVCC</sub><br>V <sub>VCC</sub> = V <sub>AVCC</sub><br>, COMP_x, VFB_x, SS_x,<br>IT_1S8 to AGND<br>GND<br>FB to VTTGND | -0.3 to 6                       |      |

| V <sub>AVCC</sub> | AVCC to AGND or SGND_x                                                            |                                                                                                                                                |                                 |      |

|                   | AGND to SGND_x                                                                    |                                                                                                                                                | -0.3 to 0.3                     |      |

|                   | VTTGND to SGND_x                                                                  |                                                                                                                                                | -0.3 10 0.3                     |      |

| V <sub>VSW</sub>  | VSW_x to SGND_x                                                                   |                                                                                                                                                | -0.3 to 6                       | V    |

|                   | VSW_x to AGND                                                                     |                                                                                                                                                | -0.3 10 0                       |      |

|                   | CSNS, PG_x, EN_x, DSCG, COMP_x, VFB_x, SS_x<br>SET_SWF, SET_PH1, VOUT_1S8 to AGND |                                                                                                                                                |                                 |      |

|                   | VTT, VTTREF, VTTFB to AGN                                                         | ND                                                                                                                                             | -0.3 to V <sub>AVCC</sub> + 0.3 |      |

|                   | LDOIN, VTT, VTTREF, VTTFB to VTTGND                                               |                                                                                                                                                |                                 |      |

| P <sub>TOT</sub>  | Power dissipation @ $T_A = 25$                                                    | O°                                                                                                                                             | 4                               | W    |

1. Free air operating conditions unless otherwise specified. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

# 3.2 Thermal data

### Table 4. Thermal data

| Symbol            | Parameter                              | Value      | Unit |

|-------------------|----------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance junction to ambient | 42         | °C/W |

| T <sub>STG</sub>  | Storage temperature range              | -50 to 150 | °C   |

| T <sub>A</sub>    | Operating ambient temperature range    | -40 to 85  | °C   |

| TJ                | Junction operating temperature range   | -40 to 125 | °C   |

## 3.3 Recommended operating conditions

### Table 5. Recommended operating conditions

|  | Symbol            | Parameter                 |     | Values |                   |      |  |

|--|-------------------|---------------------------|-----|--------|-------------------|------|--|

|  |                   |                           |     | Тур    | Max               | Unit |  |

|  | V <sub>AVCC</sub> | AVCC voltage range        | 4.5 |        | 5.5               |      |  |

|  | V <sub>VCC</sub>  | VCC IC supply voltage     | 4.5 |        | $V_{\text{AVCC}}$ | V    |  |

|  | V <sub>IN</sub>   | VIN_x input voltage range | 2.7 |        | $V_{\text{VCC}}$  |      |  |

# 4 Electrical characteristics

$T_A$  = 0 °C to 85 °C, AVCC = 5 V, VCC = 5 V , VIN\_x = 3.3 V and LDOIN connected to 1.8 V output if not otherwise specified, *Note:*

**Table 6. Electrical characteristics**

| Symbol               | Parameter                                              | Test condition                                                    | Values  |           |           | Unit  |

|----------------------|--------------------------------------------------------|-------------------------------------------------------------------|---------|-----------|-----------|-------|

| Symbol               | Parameter                                              | Test condition                                                    | Min     | Тур       | Max       |       |

| Supply sect          | tion all rails                                         |                                                                   |         |           |           |       |

| I <sub>CC</sub>      | AVCC+VCC operating current                             | $V_{VCC}$ = +5 V , all switching regulators active without load   |         |           | 3         | mA    |

| I <sub>SHDN</sub>    | Total shutdown current into<br>VIN_x + AVCC + VCC pins | $V_{IN} = V_{AVCC} = V_{VCC} = +5 V$ ,<br>all EN_x low            |         |           | 10        | μA    |

|                      | AVCC under voltage lockout upper threshold             |                                                                   | 4.0     | 4.1       | 4.35      | v     |

| UVLO <sub>th</sub>   | AVCC under voltage lockout lower threshold             |                                                                   | 3.6     | 3.9       | 4.0       |       |

|                      | UVLO hysteresis                                        |                                                                   | 100     |           |           | mV    |

| Error amplif         | fier, FB AND SS – all rails                            |                                                                   |         |           |           |       |

| V <sub>REF</sub>     | Error amplifier reference voltage                      | $V_{AVCC} = V_{VCC} = 5 V$                                        | 792     | 800       | 808       | mV    |

| I <sub>FB</sub>      | FB input bias current                                  | VFB_X = 0.8 V                                                     |         |           | 25        | nA    |

| I <sub>SS</sub>      | Soft-start current                                     | Vss_x = 0.4 V                                                     |         | 10        |           | μA    |

| Oscillator fr        | requency                                               |                                                                   | 1       | 1         |           | _     |

|                      |                                                        | $R_{SETSWF} = 140 \text{ k}\Omega$                                |         | 500       |           | kHz   |

| f <sub>SW</sub>      | Switching frequency                                    | SET_SWF to VCC                                                    | 675     | 750       | 825       |       |

|                      |                                                        | $R_{SETSWF} = 70 \text{ k}\Omega$                                 |         | 1000      |           |       |

| Comp all ra          | ils                                                    |                                                                   |         |           |           |       |

| 9 <sub>m</sub>       | COMP_x Transconductance                                |                                                                   |         | 300       |           | μS    |

| UVP/OVP pi           | rotectionS and PGOOD signal (S                         | MPS only) all rails                                               |         |           |           | -     |

| OVP <sub>th</sub>    | Overvoltage threshold                                  |                                                                   | 116     | 120       | 124       |       |

| UVP <sub>th</sub>    | Undervoltage threshold                                 |                                                                   | 56      | 60        | 64        | 0/    |

| PC                   | Power-good upper threshold                             |                                                                   | 106     | 110       | 115       | %     |

| PG <sub>th</sub>     | Power-good lower threshold                             |                                                                   | 86      | 90        | 94        | ]     |

| I <sub>PG,LEAK</sub> | PG_x Outputs Leakeage<br>Current                       | PG_x tied to +5 V                                                 |         |           | 1         | uA    |

| V <sub>PG,LOW</sub>  | PG_x Outputs Low Level                                 | $V_{FB_X} = 0.6 \text{ V or } 1\text{V}, I_{PG_X} = 2 \text{ mA}$ |         |           | 250       | mV    |

| Note:                | All parameters at operating te                         | mperature extremes are guarante                                   | ed by a | lesian ar | nd statis | tical |

*Note:* All parameters at operating temperature extremes are guaranteed by design and statistical analysis (not production tested).

**Electrical characteristics**

| Symbol              | Parameter                                             | Test condition                                   |                             |     | Values |     | Unit         |

|---------------------|-------------------------------------------------------|--------------------------------------------------|-----------------------------|-----|--------|-----|--------------|

| Symbol              | Parameter                                             | lest condition                                   |                             | Min | Тур    | Max | Uni          |

| Thermal sh          | utdown                                                |                                                  |                             |     |        |     |              |

| -                   | Thermal shutdown threshold                            |                                                  |                             |     | 150    |     |              |

| T <sub>SHDN</sub>   | Thermal shutdown hysteresis                           |                                                  |                             |     | 15     |     | °C           |

| Switching n         | ode – chipset 1.5 V rail                              |                                                  | R                           |     |        | L   |              |

| t <sub>Onmin</sub>  | Minimum On-Time                                       |                                                  |                             |     | 200    |     | ns           |

| RDSon,HS            | High side PMOS Ron                                    |                                                  |                             |     | 150    | 220 |              |

| RDSon,LS            | Low side NMOS Ron                                     |                                                  |                             |     | 100    | 160 | - mΩ         |

|                     |                                                       | V <sub>AVCC</sub> = V <sub>VCC</sub> = +5 V,     | V <sub>IN</sub> =<br>+5 V   |     |        | -   |              |

| I <sub>INLEAK</sub> | VIN_1S5 leakage current                               | all EN_1S5 low                                   | V <sub>IN</sub> =<br>+3.3 V |     |        | 1   | μA           |

|                     | Peak current limit                                    | $R_{CSNS} = 50 \text{ k}\Omega$                  |                             |     | 3.9    |     | Α            |

| Soft end see        | ction – chipset 1.5 V rail                            | 1                                                | 1 1                         |     | I      | I   |              |

|                     | Discharge resistance                                  |                                                  |                             |     | 25     |     | Ω            |

|                     | LS Turn-on VFB_1SX<br>Threshold with internal divider | VFB_S1X to OUT_X                                 |                             |     | 0.29   |     | v            |

|                     | LS Turn-on VFB_1SX<br>Threshold with external divider | VFB_S1X to external dvide                        | ər                          |     | 0.16   |     | - V          |

| Power mana          | agement section – chipset 1.5 V                       | rail                                             |                             |     |        |     |              |

|                     | EN_1S5 Turn-Off level                                 |                                                  |                             | 0.8 |        |     | v            |

|                     | EN_1S5 Turn-On level                                  | $V_{AVCC} = 5 V$                                 |                             |     |        | 2   | v            |

| Switching n         | ode – chipset 1.05 V rail                             |                                                  |                             |     |        |     |              |

| t <sub>Onmin</sub>  | Minimum On-Time                                       |                                                  |                             |     | 180    |     | ns           |

| RDSon,HS            | High side PMOS Ron                                    |                                                  |                             |     | 100    | 160 |              |

| RDSon,LS            | Low side NMOS Ron                                     |                                                  |                             |     | 70     | 110 | mΩ           |

| I <sub>INLEAK</sub> | VIN_1S05 leakage current                              | V <sub>AVCC</sub> = V <sub>VCC</sub> = +5 V, all | V <sub>IN</sub> =<br>+5 V   |     |        | 1   | - μ <b>A</b> |

|                     |                                                       | EN_1S05 low                                      | V <sub>IN</sub> =<br>+3.3 V |     |        | 1   | μΑ           |

|                     | Peak current limit                                    | $R_{CSNS} = 50 \text{ k}\Omega$                  | ·                           |     | 5.1    |     | Α            |

| Symbol              | Baramatar                                                                                                      | Test condition                                |                             | Values |       |     | Unit |

|---------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------|--------|-------|-----|------|

| Symbol              | Parameter                                                                                                      | Test condition                                |                             | Min    | Тур   | Max | Unit |

| Soft end sec        | ction – chipset 1.05 V rail                                                                                    |                                               |                             |        |       |     |      |

|                     | Discharge resistance                                                                                           |                                               |                             |        | 25    |     | Ω    |

|                     | LS Turn-on VFB_1SX<br>Threshold with internal divider                                                          | VFB_S1X to OUT_X                              |                             | 0.2    |       | v   |      |

|                     | LS Turn-on VFB_1SX<br>Threshold with external divider                                                          | VFB_S1X to external divider                   |                             |        | 0.16  |     |      |

| Power mana          | gement section – chipset 1.05                                                                                  | V rail                                        | I                           |        | 1     |     |      |

|                     | EN_1S05 Turn-Off level                                                                                         | У <del>Б</del> . М                            |                             | 0.8    |       |     | V    |

|                     | EN_1S05 Turn-On level                                                                                          | $V_{AVCC} = +5 V$                             |                             |        |       | 2   | V    |

| Switching n         | ode – DDR2/3 rails                                                                                             |                                               |                             |        |       |     |      |

| t <sub>Onmin</sub>  | Minimum On-Time                                                                                                |                                               |                             |        | 200   |     | ns   |

| RDSon,HS            | High side PMOS Ron                                                                                             |                                               |                             |        | 90    | 130 |      |

| RDSon,LS            | Low side NMOS Ron                                                                                              |                                               |                             |        | 80    | 120 | - mΩ |

| I                   | VIN_1S8 leakage current                                                                                        | $V_{AVCC} = V_{VCC} = 5 V,$<br>all EN_1S8 low | V <sub>IN</sub> =<br>+5 V   |        |       | 1   |      |

| I <sub>INLEAK</sub> |                                                                                                                |                                               | V <sub>IN</sub> =<br>+3.3 V |        |       | 1   | – μΑ |

|                     | Peak current limit                                                                                             | $R_{CSNS} = 50 \text{ k}\Omega$               |                             |        | 6.1   |     | А    |

| Soft end sec        | ction – DDR2/3 rails                                                                                           | 1                                             |                             |        |       |     |      |

|                     | VDDQ discharge resistance in non-tracking discharge mode                                                       |                                               |                             |        | 25    |     | Ω    |

|                     | VTTREF discharge resistance<br>in non-tracking discharge mode                                                  |                                               |                             |        | 200   |     | Ω    |

|                     | VTTFB discharge resistance in<br>non-tracking discharge mode                                                   |                                               |                             |        | 40    |     | Ω    |

|                     | V <sub>FB_1SX</sub> Threshold for final<br>tracking/Non-tracking discharge<br>transition with internal divider | VFB_S1X to OUT_X                              |                             |        | 0.340 |     | v    |

|                     | V <sub>FB_1SX</sub> Threshold for final<br>tracking/Non-tracking discharge<br>transition with external divider | VFB_S1X to external div                       | ider                        |        | 0.160 |     | v    |

| Table 6. Electrical characteristics | (continued) |

|-------------------------------------|-------------|

|-------------------------------------|-------------|

| Symbol                   | Parameter                                                           | Test soundition                                                               | Values |      |     | Unit |  |

|--------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------|--------|------|-----|------|--|

| Symbol                   | Parameter                                                           | Test condition                                                                | Min    | Тур  | Max |      |  |

| Power mana               | gement section – DDR2/3 rails                                       |                                                                               |        |      |     |      |  |

|                          | DSCG Turn-Off Level                                                 | V <sub>AVCC</sub> = +5 V                                                      |        |      | 1.5 |      |  |

|                          | DSCG Turn-On Level                                                  | VAVCC = +5 V                                                                  | 3.5    |      |     |      |  |

|                          | EN_1S8 (S5), EN_VTT (S3)<br>Turn-Off Level                          | V <sub>AVCC</sub> = +5 V                                                      | 0.8    |      |     | V    |  |

|                          | EN_1S8 (S5), EN_VTT (S3)<br>Turn-On Level                           | AVCC - +3 V                                                                   |        |      | 2   |      |  |

| V <sub>TT</sub> LDO sec  | tion – DDR2/3 rails                                                 |                                                                               |        |      |     |      |  |

|                          | Power-good upper threshold                                          |                                                                               | 106    | 110  | 114 | %    |  |

| PG_VTT_TH                | Power-good lower threshold                                          |                                                                               | 86     | 90   | 94  | %    |  |

| I <sub>LDOIN,ON</sub>    | LDO input bias current in full-<br>ON State                         | EN_1S8 = EN_VTT = +5 V,<br>No Load on VTT                                     |        | 1    | 10  |      |  |

| I <sub>LDOIN,STR</sub>   | LDO input bias current in<br>suspend-To-RAM State                   | EN_1S8 = +5 V, EN_VTT = 0 V,<br>No Load on VTT                                |        |      | 10  | μA   |  |

| I <sub>LDOIN,STD</sub>   | LDO input bias current in<br>suspend-To-Disk State                  | EN_1S8 = EN_VTT = 0 V,<br>No Load on VTT                                      |        |      | 3   |      |  |

| I <sub>VTTFB, BIAS</sub> | VTTFB bias current                                                  | $EN_{1S8} = EN_{VTT} = +5 V,$<br>$V_{VTTFB} = V_{VOUT_{1S8}}/2$               |        |      | 1   |      |  |

| I <sub>VTTFB, LEAK</sub> | VTTFB leakage current                                               | $      EN_1S8 = +5 V, EN_VTT = 0 V,                                 $         |        |      | 1   | μΑ   |  |

| I <sub>VTT,LEAK</sub>    | VTT leakage current                                                 | EN_1S8 = +5 V, EN_VTT = 0 V,<br>V <sub>VTT</sub> = V <sub>VOUT_1S8</sub> /2   | -10    |      | 10  |      |  |

|                          | LDO linear regulator output voltage (DDR2)                          | EN_1S8 = EN_VTT = +5 V,<br>I <sub>VTT</sub> 0 A, V <sub>LDOIN</sub> = 1.8 V   |        | 0.9  |     |      |  |

| V <sub>VTT</sub>         | LDO linear regulator output voltage (DDR3)                          | EN_1S8 = EN_VTT = +5 V,<br>I <sub>VTT</sub> = 0 A, V <sub>LDOIN</sub> = 1.5 V |        | 0.75 |     |      |  |

|                          |                                                                     | EN_1S8 = EN_VTT = +5 V,<br>-1 mA < I <sub>VTT</sub> < 1 mA                    | -20    |      | 20  |      |  |

|                          | LDO Output accuracy respect to<br>VTTREF, V <sub>LDOIN</sub> =1.8 V | EN_1S8 = EN_VTT = +5 V,<br>-1 A < I <sub>VTT</sub> < 1 A                      | -25    |      | 25  | mV   |  |

|                          |                                                                     | EN_1S8 = EN_VTT = +5 V,<br>-2 A < I <sub>VTT</sub> < 2 A                      | -35    |      | 35  | ]    |  |

| Symbol              | Parameter                                                                 | Test condition                                                          |      | Values |     | Unit |  |

|---------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------|------|--------|-----|------|--|

| Symbol              | Farameter Test condition                                                  |                                                                         | Min  | Тур    | Max | Unit |  |

|                     | LDO source current limit                                                  | V <sub>VTT</sub> < 1.10*( V <sub>VOUT_1S8</sub> /2)                     | 2    | 2.3    | 3   |      |  |

|                     |                                                                           | V <sub>VTT</sub> > 1.10*( V <sub>VOUT_1S8</sub> /2)                     | 1    | 1.25   | 1.5 | А    |  |

| I <sub>VTT,CL</sub> | LDO sink current limit                                                    | V <sub>VTT</sub> > 0.90*( V <sub>VOUT_1S8</sub> /2)                     | -3   | -2.3   | -2  |      |  |

|                     |                                                                           | $V_{VTT} < 0.90^{*}(V_{VOUT_{1}S8}/2)$ -                                | -1.5 | -1.25  | -1  |      |  |

| VTTREF sec          | tion – DDR2/3 rails                                                       |                                                                         |      |        |     |      |  |

|                     | VTTREF output voltage                                                     | $I_{VTTREF} = 0A, V_{VOUT_{1S8}} = 1.8 V$                               |      | 0.9    |     | V    |  |

| V <sub>VTTREF</sub> | VTTREF output voltage<br>accuracy relative to<br>V <sub>VOUT_1S8</sub> /2 | -15 mA < I <sub>VTTREF</sub> < +15 mA,<br>V <sub>VOUT_1S8</sub> = 1.8 V | -2   |        | 2   | %    |  |

| IVTTREF             | VTTREF short circuit source<br>current                                    | V <sub>VOUT_1S8</sub> =1.8 V, V <sub>VTTREF</sub> = 0 V                 |      | 40     |     | mA   |  |

|                     | VTTREF short circuit sink current                                         | V <sub>VOUT_1S8</sub> =1.8 V, V <sub>VTTREF</sub> = 1.8 V               |      | -40    |     | mA   |  |

## Table 6. Electrical characteristics (continued)

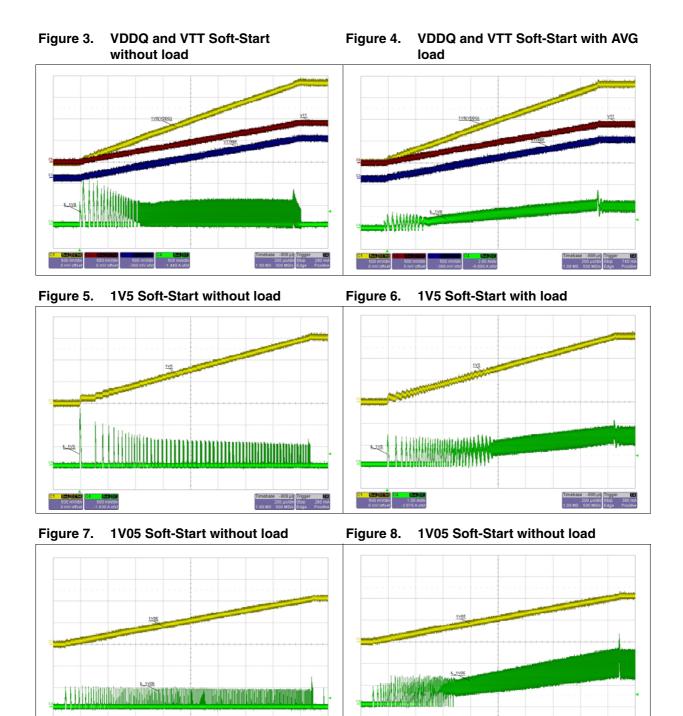

# 5 Typical operating characteristics

14/47

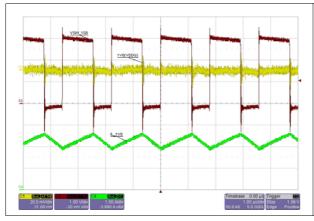

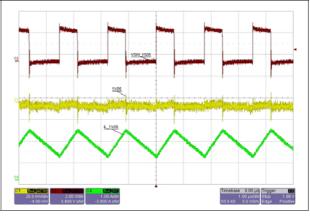

# Figure 9. VDDQ output ripple and phase @ AVG current

Figure 11. 1V5 output ripple and phase @ AVG current

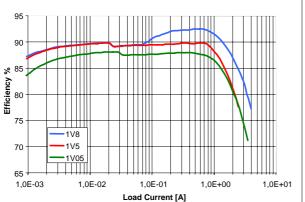

Figure 13. SW reg. efficiency @  $V_{IN} = 3.3 V$ , F<sub>SW</sub> = 600 kHz

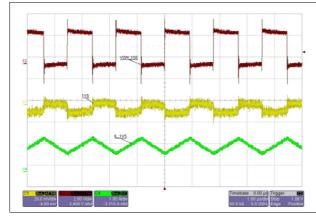

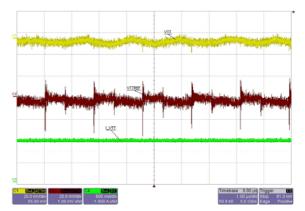

Figure 10. VTT, VTTREF output ripple @ AVG current

Figure 12. 1V05 output ripple and phase @ AVG current

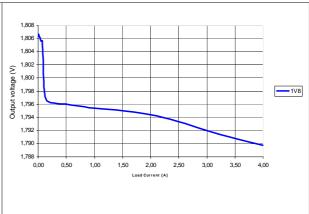

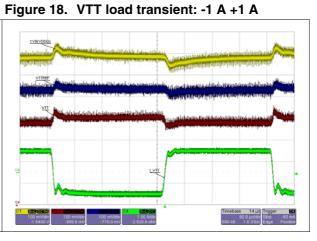

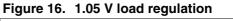

Figure 14. VDDQ (1.8 V) load regulation

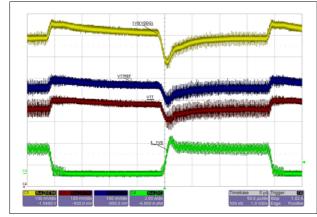

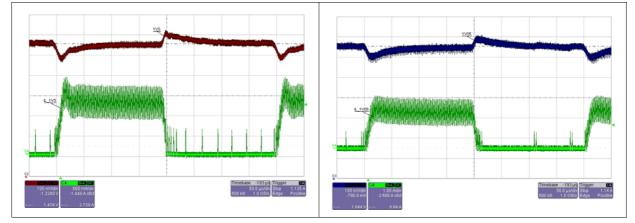

Figure 20. 1V05 load transient: 0-AVG

Figure 24. Soft-OV (1V05)

Figure 26. Output UV (1V5)

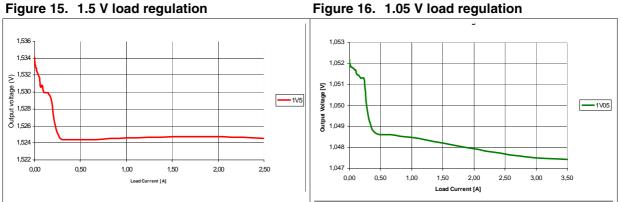

Note: All the above measures and screen captures are based on PM6641EVAL evaluation board. Refer to PM6641 Evaluation Kit for details.

57

# 6 Block diagram

Figure 27. Functional and block diagram

### Table 7. Legend

| TD  | Tracking discharge enable      |

|-----|--------------------------------|

| NTD | Non-tracking discharge enable  |

| EN  | VTTREF buffer enable           |

| HiZ | LDO high impedance mode enable |

# 7 Device description

The PM6641 is an integrated Voltage Regulator Module designed to supply DDR2/3 memory and Chipset I/O in real estate constrained portable equipment and ultra-mobile PCs. The device consists of three buck regulators (two for Chipset Supply and one for main DDR Supply), a Low Drop-Out (LDO) Linear Regulator capable of  $\pm 2$  Apk (DDR Termination Voltage) and a low noise buffered reference (DDR Input Buffer Reference). It has been developed for single-series Li-Ion battery stack powered equipment, allowing an input power supply from 2.7 V up to 5.5 V.

The PM6641 provides a compact solution by integrating DDR and Chipset voltage regulators on a single IC with internal power MOSFETs and requiring a minimum number of external components. All its buck regulators are based on a Current-Mode control scheme with integrated features to guarantee stability and fast load transient response. Each regulator output voltage can be adjusted or a pre-fixed output voltage can be chosen, if external components are unwanted. Each switching regulator has independent programmable soft-start, to reduce inrush current, and output soft-end, to avoid inductor and MOSFETs high peak current.

Other buck regulators features include output Over-Voltage and Under-Voltage Protections, programmable current limit and output Power-Good signals. High efficiency is achieved over a wide range of load conditions by using a Pulse-Skipping technique at light load.

The PM6641 can detect the AVCC pin under-voltage through the Under-Voltage Lock-Out (UVLO) block and it is able to limit its internal temperature through its auto-recovery Thermal Shutdown.

The switching frequency of the buck controllers can be set in the range 500 kHz-1 MHz with an external resistor or can be set equal to 750 kHz without external components use. All buck regulators work at the same switching frequency with selectable Phase Shift.

The regulators can support both electrolytic and ceramic output capacitors because no minimum output voltage ripple is required for stability purposes.

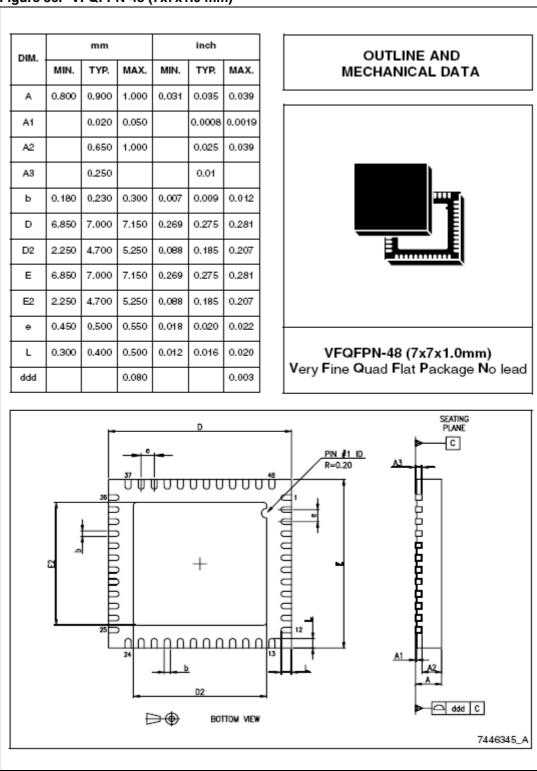

The PM6641 is provided in a QFN7x7mm 48-pin lead-free package.

57

## 7.1 Memory supply

The DDR2/3 section of PM6641 is based on the VDDQ rail, the VTT termination rail and the VTTREF reference voltage buffer.

The VDDQ rail is provided by a step-down switching regulator whose output voltage, by default, is set to 1.8 V, in order to be compliant with DDR2 JEDEC specs. The output voltage can also be adjusted using an external resistor divider. This rail performs latched Output Under-Voltage and Over-Voltage and auto-recovery Current Limit, without requiring external sensing resistor.

The VTT termination rail is supplied by a Low Drop-Out (LDO) Linear Regulator, able to sink and source up to 2 A peak current. This regulator follows the half of the VDDQ rail and is a replica of the VTTREF reference voltage buffer. When LDOIN is directly supplied by VDDQ, i.e. the PM6641 1S8 rail, VTT and VDDQ can perform the so called Tracking Discharge, in compliance with the JEDEC specs, as described in the following section. If higher efficiency is required, VTT can be supplied by a lower voltage rail. An output capacitor of at least 20  $\mu$ F is the only external component required.

The VTTREF reference voltage buffer is always in tracking with the half of VDDQ and is able to sink and source up to 15mA with an accuracy of  $\pm 2$  % relative to VDDQ half. A 10 nF up to 100nF bypass capacitor for stability purposes is required.

### 7.1.1 VDDQ switching regulator

The VDDQ rail is provided by a constant frequency current-mode buck regulator, whose frequency is set by inserting an external resistor between SET\_SWF pin and AGND (see *Chapter 7.8: Switching frequency selection on page 29* section for details). The output voltage can easily be set to 1.8 V by connecting the feedback pin VFB\_1S8 directly to the output rail, avoiding the use of external components. However, if a different output voltage is desired, the VFB\_1S8 pin must be connected to the central tap of a resistor divider. The output voltage can be adjusted from 0.8V up to the input voltage value, decreased by a drop due to the high-side MOSFET on resistance.

(see Chapter 7.5: Output voltage divider on page 27 section for details).

The control loop needs to be compensated by inserting a resistor-capacitor series connected between the COMP\_1S8 pin and ground; if electrolytic capacitor with relevant equivalent series resistance (ESR) are used, an additional capacitor between the COMP\_1S8 pin and ground can be useful (see *Chapter 7.3: SW regulators control loop on page 24* section for details). The classical slope compensation is internally implemented and no external components are required.

The internal High-Side PMOS and Low-Side NMOS allow the regulator to source an average current of 2.8 A and a peak current of 5 A. The peak current limit protection is performed by sensing the internal high side MOSFET current and can be decreased by inserting an external resistor between CSNS pin and AGND (see *Chapter 7.10: Peak current limit on page 31* section for details).

This 1S8 rail is able to protect the load from Over-Voltage and Under-Voltage protection, which avoid the output to be higher than 120 % or lower than 60 % of the nominal value (see *Chapter 7.11.1: Output over voltage on page 33* and *Chapter 7.11.2: Output under voltage on page 33* section for details).

When the EN\_1S8 pin goes high the VDDQ rail is turned on and the output voltage soft-start is performed by slowly charging the rail output capacitor; this behavior is achieved because

the loop voltage reference is increased linearly from zero up to 0.8V in a long time (up to a couple of milliseconds) (see *Chapter 7.6: Outputs Soft-Start on page 28* for details).

When the EN\_1S8 pin goes low, the VDDQ rail output capacitor is discharged through internal discharge MOSFET and, at the end of the capacitor discharge, the low side power MOSFET is eventually closed (see *Chapter 7.7: Outputs Soft-End on page 29* for details).

The Power Good Signal (PG\_1S8 pin) is an open drain output, shorting the output to GND in the following conditions:

- When the 1.8 V rail output voltage is outside +/- 10 % range from nominal value

- When a protection (UV, OV, thermal) has been triggered

- When the regulator is in soft-start.

When VDDQ and VTT rails are enabled, PG\_1S8 is left floating and, as a consequence, pulled-up by the external pull-up resistor, if both the rails are inside +/- 10 % range of nominal value. The PG\_1S8 pin can sink current up to 4mA when it's asserted low.

### 7.1.2 VTT LDO and VTTREF buffered reference

The PM6641 provides the required DDR2/3 reference voltage on VTTREF pin. The internal buffer tracks half the voltage on VOUT\_1S8 pin and has a sink and source capability up to 15mA with an accuracy of  $\pm 2$  % referred to the VDDQ half.

Higher currents rapidly deteriorate the output accuracy. A 10 nF to 100 nF (33 nF typical) bypass capacitor to SGND is required for stability.

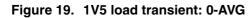

The VTT Low-Drop-Out linear regulator has been designed to sink and source up to 2 A peak current and 1 A continuously. The VTT voltage tracks VTTREF within ±35 mV. A remote voltage sensing pin (VTTFB) is provided to recovery voltage drops due to parasitic resistance. In DDR2/3 applications, the linear regulator input LDOIN is typically connected to VDDQ output; connecting LDOIN pin to a lower voltage (if available in the system) reduces the power dissipation of the LDO, but a minimum drop-out voltage must be guaranteed, depending on the maximum current expected.

A minimum output capacitance of 20 uF (2x10 uF or single 22 uF ceramic capacitors) is enough to assure stability and fast load transient response.

According to DDR2/3 JEDEC specifications, when the system enters the Suspend-To-RAM state (S5 high and S3 low) the LDO output is left in high-impedance while VTTREF and VDDQ are still alive. When the Suspend-To-Disk state (S3 and S5 tied to ground) is entered, all outputs are actively discharged by a tracking or a non-tracking discharge as selected through the DSCG pin (see *Chapter 7.7: Outputs Soft-End on page 29* for details).

### 7.1.3 VTT and VTTREF Soft Start

Soft-Start on VTT and VTTREF outputs is achieved by current clamping. The LDO linear regulator is provided of a current fold-back protection: when the output voltage exits the internal  $\pm 10$  % VTT-Good window, the output current is clamped at  $\pm 1$  A. Re-entering VTT-Good window releases the current limit clamping. The fold-back mechanism naturally implements a two steps soft-start charging the output capacitors with a 1 A constant current.

Something similar occurs at VTTREF pin, where the output capacitor is smoothly charged at a fixed 40 mA (typ) current limit.

### 7.1.4 S3 and S5 power management pins

According to DDR2/3 memories supply requirements, the PM6641 can manage all S0 to S5 system states just connecting EN\_VTT – EN\_1S8 pins to their respective sleep-mode signals in the notebook's motherboard: connect EN\_1S8 to S5 and EN\_VTT to S3.

Keeping EN\_VTT and EN\_1S8 high, the S0 (Full-On) state is decoded and the outputs are alive.

In S3 state (EN\_1S8=1, EN\_VTT =0), the PM6641 maintains VDDQ and VTTREF outputs active and VTT output in high-impedance as needed.

In S4/S5 states (EN\_1S8= EN\_VTT =0) all outputs are turned off and, according to DSCG pin voltage, the proper Soft-End is performed (see *Chapter 7.7: Outputs Soft-End on page 29* section for details).

The following table resumes the DDR power supply states.

| S3 (EN_VTT) | S5 (EN_1S8) | System state               | VDDQ            | VTTREF          | VTT             |

|-------------|-------------|----------------------------|-----------------|-----------------|-----------------|

| 1           | 1           | S0<br>(Full-On)            | On              | On              | On              |

| 0           | 1           | S3<br>(Suspend-To-RAM)     | On              | On              | Hi-Z            |

| 0           | 0           | S4/S5<br>(Suspend-To-Disk) | Off (Discharge) | Off (Discharge) | Off (Discharge) |

Table 8. S3 and S5 sleep-states decoding

# 7.2 Chipset supply

The chipset power supply section is based on two constant frequency current-mode buck regulators with a pre-fixed output voltage of 1.5 V and 1.05 V.

These two independent rails have programmable switching frequency, set by inserting an external resistor between SET\_SWF pin and AGND. The PM6641 allows also to manage the switching regulators phases for 1.5V, 1.05V and 1.8V (VDDQ) rails in order to limit the RMS input current (see *Chapter 7.8: Switching frequency selection on page 29* and *Chapter 7.9: Phase management on page 30* section for details).

The output voltages can easily be set to the pre-fixed value by connecting the feedback pins VFB\_1S5 and VFB\_1S05 directly to the respective output rail, avoiding the use of external components. However, if a different output voltage is desired, the feedback pins can be independently connected to the central tap of a resistor divider.

The output voltage can be adjusted from 0.8V up to the input voltage value, decreased by a drop due to the high-side MOSFET on resistance.

(see Chapter 7.5: Output voltage divider on page 27 section for details).

Both regulators are current-mode step-down switching regulators whose control loop needs to be compensated by inserting a resistor-capacitor series connected between the compensation pin (COMP\_1S5 and COMP\_1S05) and ground; if electrolytic capacitor with relevant equivalent series resistance (ESR) are used, an additional capacitor between this compensation pin and ground can be useful (see *Chapter 7.3: SW regulators control loop on page 24* section for details). The classical slope compensation, which allows the peak current mode loop to avoid sub-harmonic instability with duty cycle greater than 50%, is internally implemented and no further external components are required.

The chipset supply is able to source the following average and peak currents, , assuming 1 A peak-to-peak inductor current ripple:

| Table 9. | Chipset | supply | currents |

|----------|---------|--------|----------|

|----------|---------|--------|----------|

| Chipset supply rail [V] | Average current [A] | Peak current [A] |

|-------------------------|---------------------|------------------|

| 1.5                     | 1.5                 | 3.0              |

| 1.05                    | 2.1                 | 4.0              |

The peak current and the inductor ripple must be carefully evaluated in order to choose the right current limit protection; this feature is performed by sensing the internal high side MOSFET current and can be decreased by inserting an external resistor between CSNS pin and AGND (see *Chapter 7.10: Peak current limit on page 31* for details).

Both rails are able to protect the load from Over-Voltage and Under-Voltage protection, which avoid the output to be higher than 120% or lower than 60% of the nominal value (see *Chapter 7.11.1: Output over voltage on page 33* and *Chapter 7.11.2: Output under voltage on page 33* section for details).

When the EN\_1S5 or EN\_1S05 pin goes high the respective rail is turned on and the output voltage soft-start is performed by slowly charging the rail output capacitor; this behavior is achieved because the loop voltage reference is increased linearly from zero up to 0.8V (see *Chapter 7.6: Outputs Soft-Start on page 28* section for details). When the EN\_1S5 or EN\_1S05 pin goes low, the respective rail output capacitor is discharged through internal discharge MOSFET and, at the end of the capacitor discharge, the low side power MOSFET is finally closed (see *Chapter 7.7: Outputs Soft-End on page 29* section for details).

Each rail has a dedicated pin to assert if its output voltage is not in the power good window, i.e. if the output voltage drops 10% below or rises 10% above the nominal regulated value. These Power Good Signals (PG\_1S5 and PG\_1S05 pins) are open drain outputs, tied to GND in the following conditions:

- When the rail output voltage is outside +/- 10 % range from nominal value

- When a protection (UV, OV, thermal) has been triggered

- When the regulator is in soft-start.

The PG\_1S5 and PG\_1S05 pins can sink current up to 4 mA when it's asserted low.

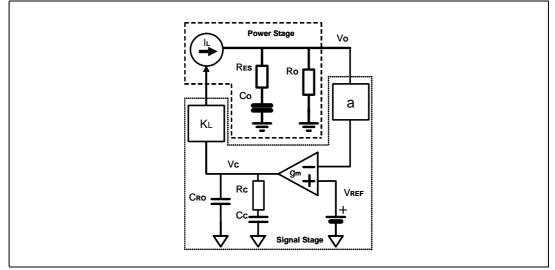

# 7.3 SW regulators control loop

The PM6641 switching regulators are buck converters employing a constant frequency, peak current mode PWM control loop, as shown in the following figure:

### Figure 28. SW Regulator Control Loop

In the current mode constant frequency loop the Power Stage is represented by a controlled current generator feeding the power stage output capacitor and load. The equivalent transfer function is:

### **Equation 1**

$$H(s) = \frac{V_{O}(s)}{I_{L}(s)} = \frac{(sC_{O}R_{ES} + 1)}{sC_{O}(R_{ES} + R_{O}) + 1}R_{O}$$

with Co and Res being the output capacitance and its equivalent series resistance and Ro representing the output load.

In order to obtain the typical integrative loop transfer function the signal stage must compensate for the power stage pole (due to the output capacitor and the load) and zero (above the loop bandwidth if ceramic output capacitors are selected). The signal stage transfer function is:

#### **Equation 2**

$$G(s) = g_m K_L \alpha \frac{s C_C R_C + 1}{s C_C \left(s C_{R_0} R_C + \frac{C_{R_0}}{C_C} + 1\right)}$$

Where  $g_M$  is the power stage transconductance,  $K_L$  is a design parameter and  $\alpha$  is the gain due to the output resistor divider (0.8V / Vout). The external compensation network ( $R_c$ ,  $C_c$  and  $C_{RO}$ ) introduces:

One zero, to compensate the power stage pole:

$$C_{C}R_{C} = C_{O}(R_{O} + R_{ES})$$

- One pole in order to delete the static output voltage error;

- One pole, if necessary, in order to compensate the high frequency zero due to the output capacitor ESR:

$$C_{RO}R_{C} = C_{O}R_{ES}$$

The control loop gain is obtained by multiplying G(s) by H(s):

#### **Equation 3**

$$G_{LOOP}(s) = g_m K_L \alpha \frac{(sC_CR_C + 1)}{sC_C \left(sC_{Ro}R_C + \frac{C_{Ro}}{C_C} + 1\right)} \cdot \frac{(sC_OR_{ES} + 1)}{sC_O(R_{ES} + R_O) + 1} R_O$$

This model provides good results if the control loop cut-off frequency  $\rm f_{\rm CO}$  is lower than about fsw/10.

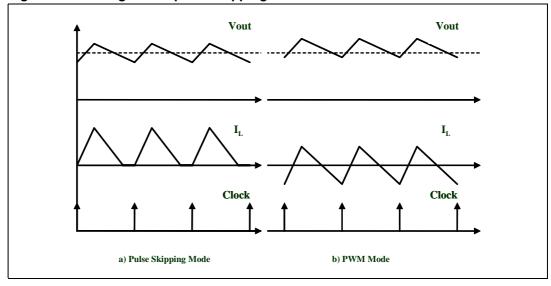

## 7.4 SW regulators pulse skipping and PWM mode

In order to enhance the light load efficiency each switching regulator enters the Pulse Skipping algorithm when the output current sourced is too low. The threshold load current which allows the regulator to enter the pulse skipping mode can be estimated with the following formula: (Vi-Vo)/(2Lfsw)\*Vo/Vi

#### **Equation 4**

$Iomin \approx \frac{(V_I - V_O)}{(2Lf_{SW})} \cdot \frac{V_O}{V_I}$

When the load current is lower than I<sub>Omin</sub> value, the switching regulator begins to skip some cycle, decreasing the effective switching frequency and, as a consequence, reducing the switching losses. This mode of operation is guaranteed by the presence of the zero crossing current comparator, the internal block which senses the inductor current and avoids this current to becoming negative, in the normal operating condition.

The inductor current is allowed to become negative when the output voltage rises above the +10% power good threshold. In this condition of output soft over voltage the zero crossing current comparator is deactivated and the pulse skipping algorithm is replaced by the typical PWM one; as a consequence each switching regulator can sink up to some hundreds milliamps to decrease the output voltage to the nominal value.

#### Figure 29. SW regulators pulse skipping and PWM mode

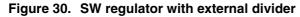

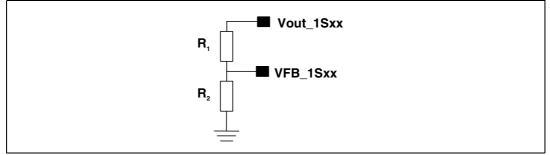

## 7.5 Output voltage divider

PM6641 switching regulators are adjustable voltage converters.

If the feedback pin (VFB\_1S8, VFB\_1S5, VFB\_1S05 respectively belonging to VDDQ (1.8 V), 1.5 V, 1.05 V rail) is directly tied to the rail output capacitor the internal divider with pre-fixed output voltage value is activated and the nominal output voltages are selected.

If the feedback pin is connected to the output voltage divider central tap (as depicted in *Figure 30*)

the PM6641 switching regulator automatically recognizes the external divider and the output voltage is regulated to the following value:

### **Equation 5**

$$Vout\_1Sxx = \left(\frac{R_1}{R_2} + 1\right) \cdot 0.8V$$

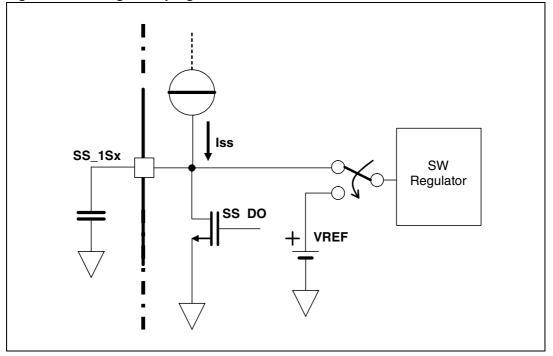

## 7.6 Outputs Soft-Start

The soft start function of each switching regulator is achieved by ramping up the SS pin voltage with a constant slew rate dV/dt.

When the switching section is enabled (EN high), the SS pin constant current charges the capacitor connected between SS and ground pins.

The SS voltage is used as reference of the switching regulator and the output voltage of the converter follows the ramp of the SS voltage. When the SS pin voltage is higher than 0.8 V, the error amplifier will use the internal 0.8 V  $\pm$ 1 % reference to regulate the output voltage.

Figure 31. SW regulator programmable Soft-Start

The dV/dt slope is set by charging the external capacitor with a 10  $\mu$ A current. The capacitance values will be of the order of magnitude of 10 nF for a 1 msec soft-start duration, as pointed out by the following formula:

### **Equation 6**

$$C = \frac{I \cdot \Delta t}{\Delta V} = \frac{10 \mu A \cdot 1ms}{0.8 V} = 12.5 nF$$

During the soft-start the output under voltage management is not enabled, whereas the output over voltage, the current limit and the thermal overheat are always monitored.

When the first switching regulator is turned on the output soft-start begins after an additional delay of about 180  $\mu s,$  due to PM6641 initializing and fuses reading.

# 7.7 Outputs Soft-End

When the switching regulator enable pin (EN\_1S8 for the VDDQ section, EN\_1S5 and EN\_1S05 for chipset sections) goes down or when UV or thermal protections are detected, the switching regulator output capacitor is actively discharged through a dedicated discharge MOSFET of about 25  $\Omega$  typical resistance.

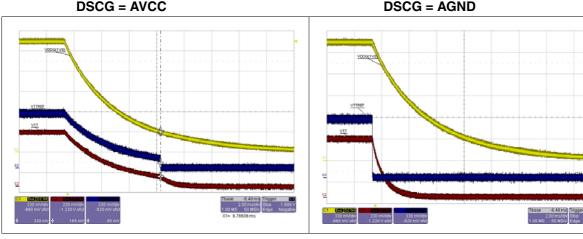

The PM6641 DDR supply allows choosing between two different output discharge behaviors, involving the VDDQ (1S8) switching rail, VTT LDO termination and VTTREF reference buffered voltage: the tracking discharge and the non-tracking discharge. This selection is set by tying the Discharge pin (DSCG) to AVCC (tracking discharge enabled) or to AGND (tracking discharge disabled).

When the 1.8 V rail is turned off (EN\_1S8 goes low) and non-tracking discharge is active (DSCG is low), or when UV or thermal protections are detected, the VDDQ and VTT rails and the VTTREF buffer are discharged by internal discharge MOSFETs, through the VSW\_1S8, VTTFB and VTTREF pins respectively. VTT termination output capacitor is discharged through 25  $\Omega$  dedicated MOSFET whereas VTTREF output capacitor is discharged through 200  $\Omega$  dedicated MOSFET.

When the 1.8 V rail is turned off (EN\_1S8 goes low) and tracking discharge is selected (DSCG is high), tracking discharge takes place:

- The 1.8 V rail regulator is discharged by internal MOSFET

- The 0.9 V VTT LDO and VTTREF work in tracking with the half of 1.8 V rail

When the VTT LDO and VTTREF reach a voltage threshold of about 200-300 mV, the device switches to non-tracking discharge mode and the internal discharge MOSFETs are turned on.

# 7.8 Switching frequency selection

SET\_SWF (pin 2) allows to vary the internal oscillator switching frequency, in the range of 500 kHz  $\Leftrightarrow$  1 MHz, by connecting this pin to AGND through a resistor between 70 k $\Omega \Leftrightarrow$  140k  $\Omega$ .

The following table summarizes the output resistor – switching frequency correspondence:

| R <sub>SET_SWF</sub> (kΩ) | Approx. switching frequency (kHz) |  |

|---------------------------|-----------------------------------|--|

| 140                       | 500                               |  |

| 100                       | 670                               |  |

| 70                        | 1000                              |  |

Table 10. Typical values for switching frequency selection

When SET\_SWF is tied to AVCC the internal reference is chosen and each regulator performs a typical 750 kHz switching frequency.

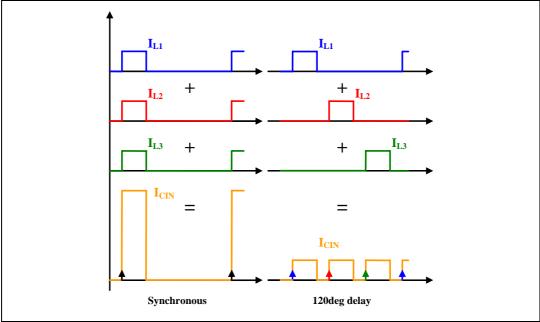

## 7.9 Phase management

When all the three switching regulators high side MOSFETs are turned on simultaneously the input root mean square (RMS) current could rise up to very high values, increasing the system losses and inducing external components overheating. It's possible to reduce the input overall RMS current by inserting one ceramic capacitor as close as possible to each switching regulator power supply input, reducing the impulsive input current path. However this synchronous mode of operation is jitter-free and noise immune.

Another possible way to reduce the input RMS current is based on the phase shifting technique, which decreases the total input current by delaying the regulators turn on pulse. With three regulators turned on, the 120d eg phase shifting allows to reduce the overall input current up to 1.73 times as depicted in the following configuration, in which three independent regulators with Vout/Vin lower than 0.333 and identical output current (I) are managed with synchronous or 120 deg phase shifted turning on.

Figure 32. SW regulator phase management

Each regulator RMS input current is easily computed:

### **Equation 7**

$$I_{L1,L2,L3} = \sqrt{\frac{1}{T_{SW}} \int_{T_{SW}} I_{L1,L2,L3}^2 dt} = \sqrt{\frac{1}{T_{SW}} I^2 T_{ON}}$$

defining T<sub>SW</sub> the switching period, equal to  $f_{SW}$  and T<sub>ON</sub> the high side MOSFET on time.

The synchronous mode of operation provides the following total input current:

#### **Equation 8**

$$I_{\text{CIN,SYNC}} = \sqrt{\frac{1}{T_{\text{SW}}} \int_{T_{\text{SW}}} (I_{\text{L1}} + I_{\text{L2}} + I_{\text{L3}})^2 dt} = \sqrt{\frac{1}{T_{\text{SW}}} (3I)^2 T_{\text{ON}}}$$

whereas by shifting the three regulator turn on pulses of 120 deg the resulting total input current is given by

#### **Equation 9**

$$I_{\text{CIN,DELAY}} = \sqrt{\frac{1}{T_{\text{SW}}} \int_{T_{\text{SW}}} (I_{\text{L1}} + I_{\text{L2}} + I_{\text{L3}})^2 dt} = \sqrt{\frac{1}{T_{\text{SW}}} (I_{\text{CIN,DELAY}} - I_{\text{CIN,DELAY}})^2 dt}$$

that is  $\sqrt{3} \approx 1.73$  times smaller than the one computed before.

The PM6641 SET\_PH1 pin, if tied to AVCC, enables the synchronous switching regulators high side MOSFET turn on, whereas if tied to ground enables the 120 deg phase shifting.

## 7.10 Peak current limit

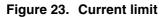

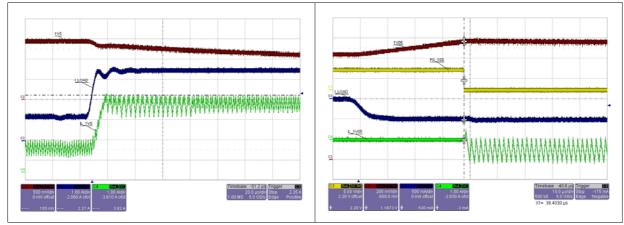

The peak current limit performed by the PM6641 switching regulators allows to monitor, cycle by cycle, the inductor current; this feature prevents IC wire bonding overheating and failure.

If the current sensed on the monolithic high side MOSFET reaches the programmed current limit the regulator starts behaving like a current generator, more than a voltage regulator. Consequently, if the output load still increases the rail output capacitor discharges itself and the regulator works as current generator until the Output Under Voltage occurs and the regulator is latched off (see *Chapter 7.11.2: Output under voltage on page 33* section for details).

The pin 4 (CSNS) allows to select the right value for the peak current limit by inserting an external resistor (R<sub>CSNS</sub>) between this pin and ground. CSNS forces a constant voltage on RCSNS resistor or, when tied to AVCC, enables the internal reference (equal to a 50 k $\Omega$  external resistor). A simple equation shows how to compute the right value for R<sub>CSNS</sub> in order to decrease the peak current limit:

#### **Equation 10**

$$\mathsf{R}_{\mathsf{CSNS}} = \alpha \cdot \frac{\mathsf{V}_{\mathsf{REF}}}{\mathsf{I}_{\mathsf{CL}}}$$

The following table resumes values for all the switching regulators.

| SW regulator | α        |

|--------------|----------|

| 1.8V         | 333x10e3 |

| 1.5V         | 222x10e3 |

| 1.05V        | 278x10e3 |

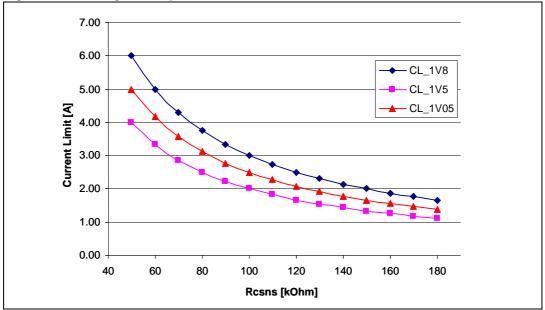

The following graph is a plot of the switching regulators peak current limit, increasing the  $R_{CSNS}$  resistor:

#### Figure 33. SW regulators peak current limit

From the previous plot and table it's clear that the three regulators peak current limits are scaled; by changing the  $R_{CSNS}$  external resistor the three peak current limits all change.

## 7.11 Fault management

PM6641 has been conceived to constantly monitor the rails output voltage. In order to protect itself from failure and the load from damage, the device is able to:

- Limit the power MOSFETs current

- Detect output over voltage

- Detect output under voltage

- Monitor the device temperature

- Detect input power supply under voltage

The current limit is an auto-recovery protection, monitoring cycle by cycle the regulators high side MOSFET current (see *Chapter 7.10: Peak current limit on page 31* section for details).

The output Over Voltage and Under Voltage and the input Under Voltage are latched protections, whereas the thermal shutdown is auto-recovery; all these features are described in the following sections.

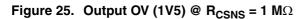

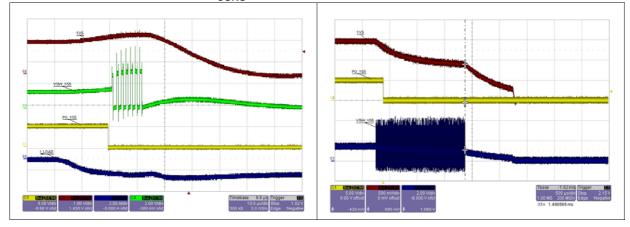

### 7.11.1 Output over voltage

If the output voltage of a switching regulator (memory supply rail VDDQ (1.8 V), chipset supply rails 1.5 V or 1.05 V) becomes greater than 120 % of its nominal value, an over voltage (OV) protection for that rail is triggered. As a consequence the regulator stops switching, the internal low-side power MOSFET of that rail is turned on and the high-side MOSFET is turned off. The OV protection effect is the very quick discharge of the rail output capacitor.

The OV condition is latched, and it can be reset only by toggling the enable pin of that rail or by turning off and on the IC power supply (AVCC pin).

An OV condition for one of the outputs of the PM6641 has no effect on the operation of the other outputs (e.g., if the OV protection is triggered for the VDDQ regulator, the 1.5 V and 1.05 V regulators continue to work normally).

### 7.11.2 Output under voltage

If the output voltage of a switching regulator (memory supply rail VDDQ (1.8 V), chipset supply rails 1.5 V or 1.05 V) becomes lower than 60 % of its nominal value (e.g. because the rail was shorted to ground or the output load is increased dramatically), an under voltage (UV) protection for that rail is triggered.

An UV condition causes the soft-end of the rail, which implies the regulator turn off and the rail discharge MOSFET turn on (see *Chapter 7.7: Outputs Soft-End on page 29* section for details); the UV condition is latched, and it can be reset only by toggling the enable pin of that rail or by turning off and on the PM6641 power supply (AVCC pin).

As for OV protection, each switching regulator can perform under voltage protection without affecting other regulators.

The over-current feature is implemented in the PM6641 by limiting the output current of each rail (see *Chapter 7.10: Peak current limit on page 31* section for details) and triggering a latched UV protection if the output voltage falls because of a load requesting more current than the limit.

### 7.11.3 Thermal shutdown

If the device temperature exceeds 150 °C, a thermal protection is triggered. As a consequence, the Output Soft End takes place for all the outputs of the PM6641 (VDDQ rail (1.8 V), VTT, VTTREF, 1.5 V, 1.05 V) by closing the output discharge MOSFET (see *Chapter 7.7: Outputs Soft-End on page 29* section for details).

The thermal protection condition is not latched: the device leaves this condition and reactivates itself automatically when its temperature falls below 135  $^{\circ}$ C (i.e. there is a 15  $^{\circ}$ C of hysteresis).

### 7.11.4 Input under voltage lock-out

The PM6641 AVCC pin is the device power supply input. This pin must be fed with 5 V,  $\pm 10$  % in order to allow the device to work properly. If this rail falls under 3.9 V typical threshold, the input under voltage is detected and the device performs the Under Voltage Lock-Out (UVLO) protection. When this event occurs, each regulator stops switching and the following actions are performed:

- The memory supply rails (VDDQ, VTT and VTTREF) are discharged by closing the output discharge MOSFET (see *Chapter 7.7: Outputs Soft-End on page 29* section for details);

- Chipset power supply output rails (1V5 and 1V05 rails) are discharged through the low side power MOSFETs;

- The device is turned OFF.

The PM6641 is turned on again when the AVCC pin voltage reaches the UVLO on threshold (about 4.1 V).

# 8 Components selection