02/13/07

# 900MHz TTL/CMOS Potato Chip

| FEATURES:                                                                                                                                                                                                                   | <b>DESCRIPTION:</b>                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| . Patented technology . Operating frequency up to 900MHz with 2pf load . Operating frequency up to 700MHz with 5pf load . Operating frequency up to 350MHz with 15pf load . Operating frequency up to 180MHz with 50pf load | Potato Semiconductor's PO74G38074A is designed for world top performance using submicron CMOS technology to achieve 900MHz TTL output frequency with less than 50ps output pin to pin skew. |

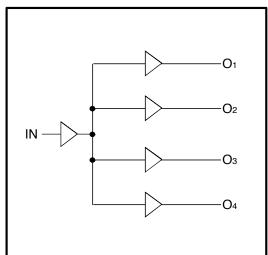

| . Very low output pin to pin skew < 50ps<br>. VCC = 1.65V to 3.6V                                                                                                                                                           | PO74G38074A is a 3.3V CMOS 1 input to 4 outputs Buffered driver to achieve 900MHz output frequency.                                                                                         |

| . Propagation delay < 1.5ns max with 15pf load<br>. Low input capacitance: 3pf typical                                                                                                                                      | Typical applications are clock and signal distribution.                                                                                                                                     |

| . 1:4 fanout . Available in 8 pin SOIC package                                                                                                                                                                              | Inputs can be driven from either 3.3V or 5V devices. This feature allows the use of these devices as translators in a mixed 3.3V/5V system environment.                                     |

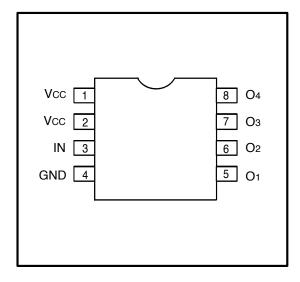

# **Pin Configuration**

# Logic Block Diagram

# **Pin Description**

| Pin Name | Description |

|----------|-------------|

| IN       | Input       |

| Ox       | Outputs     |

www.potatosemi.com 3.3V 1:4 C

900MHz TTL/CMOS Potato Chip

02/13/07

# Maximum Ratings

| Description           | Max             | Unit |

|-----------------------|-----------------|------|

| Storage Temperature   | -65 to 150      | °C   |

| Operation Temperature | -40 to 85       | °C   |

| Operation Voltage     | -0.5 to +4.6    | V    |

| Input Voltage         | -0.5 to +5.5    | V    |

| Output Voltage        | -0.5 to Vcc+0.5 | V    |

#### Note:

stresses greater than listed under Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability specification is not implied.

#### **DC** Electrical Characteristics

| Symbol | Description         | Test Conditions                         | Min  | Тур  | Max  | Unit |

|--------|---------------------|-----------------------------------------|------|------|------|------|

| Vон    | Output High voltage | Vcc=3V Vin=VIH or VIL, IOH= -12mA       | 2.4  | 3    | -    | V    |

| Vol    | Output Low voltage  | Vcc=3V Vin=VIH or VIL, IOH=12mA         | -    | 0.3  | 0.5  | V    |

| Vih    | Input High voltage  | Guaranteed Logic HIGH Level (Input Pin) | 2    | -    | Vcc  | V    |

| Vil    | Input Low voltage   | Guaranteed Logic LOW Level (Input Pin)  | -0.5 | -    | 0.8  | V    |

| Ітн    | Input High current  | Vcc = 3.6V and $Vin = 5.5V$             | -    | -    | 1    | uA   |

| In     | Input Low current   | Vcc = 3.6V and $Vin = 0V$               | -    | -    | -1   | uA   |

| Vik    | Clamp diode voltage | Vcc = Min. And IIN = -18mA              | -    | -0.7 | -1.2 | V    |

#### Notes:

- 1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at Vcc = 3.3V, 25 °C ambient.

- 3. This parameter is guaranteed but not tested.

- 4. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.

- 5. VoH = Vcc 0.6V at rated current

www.potatosemi.com

### 900MHz TTL/CMOS Potato Chip

**Power Supply Characteristics**

| Symbol | l Description Test Conditions (1) |                         | Min | Тур | Max | Unit |

|--------|-----------------------------------|-------------------------|-----|-----|-----|------|

| IccQ   | Quiescent Power Supply Current    | Vcc=Max, Vin=Vcc or GND | -   | 0.1 | 30  | uA   |

#### **Notes:**

- 1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at Vcc = 3.3V, 25°C ambient.

- 3. This parameter is guaranteed but not tested.

- 4. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.

### Capacitance

| Parameters (1) | Description        | Test Conditions | Тур | Max | Unit |

|----------------|--------------------|-----------------|-----|-----|------|

| Cin            | Input Capacitance  | Vin = 0V        | 3   | 4   | pF   |

| Cout           | Output Capacitance | Vout = 0V       | -   | 6   | pF   |

#### **Notes:**

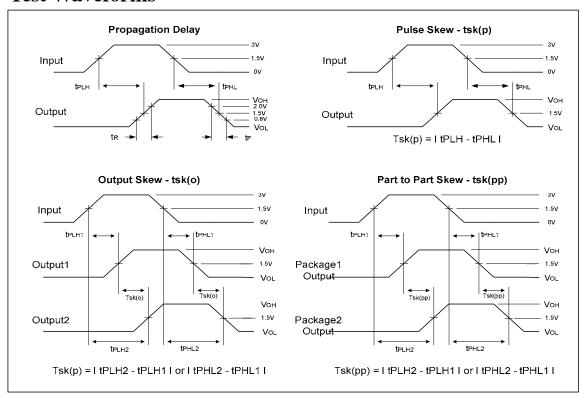

### **Switching Characteristics**

| Symbol       | Description               | Test Conditions (1) | Max | Unit |

|--------------|---------------------------|---------------------|-----|------|

| <b>t</b> PLH | Propagation Delay A to Bn | CL = 15pF           | 1.5 | ns   |

| <b>t</b> PHL | Propagation Delay A to Bn | CL = 15pF           | 1.5 | ns   |

| tr/tf        | Rise/Fall Time            | 0.8V - 2.0V         | 0.8 | ns   |

| tsk(o)  | Output Pin to Pin Skew (Same Package) | CL = 15pF, 125MHz | 50  | ps  |

|---------|---------------------------------------|-------------------|-----|-----|

| tsk(pp) | Output Skew (Different Package)       | CL = 15pF, 125MHz | 0.3 | ns  |

| fmax    | Input Frequency                       | CL = 50pF         | 180 | MHz |

| fmax    | Input Frequency                       | CL =15pF          | 350 | MHz |

| fmax    | Input Frequency                       | CL = 5pF          | 700 | MHz |

| fmax    | Input Frequency                       | CL = 2pF          | 900 | MHz |

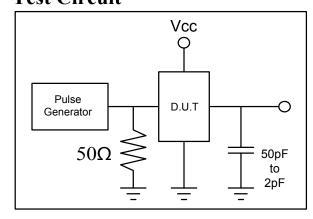

#### **Notes:**

- 1. See test circuits and waveforms.

- 2. tpLH, tpHL, tsk(p), and tsk(o) are production tested. All other parameters guaranteed but not production tested.

- 3. Airflow of 1m/s is recommended for frequencies above 133MHz

<sup>1</sup> This parameter is determined by device characterization but not production tested.

02/13/0

### 900MHz TTL/CMOS Potato Chip

### **Test Waveforms**

### **Test Circuit**

# 900MHz TTL/CMOS Potato Chip

02/13/07

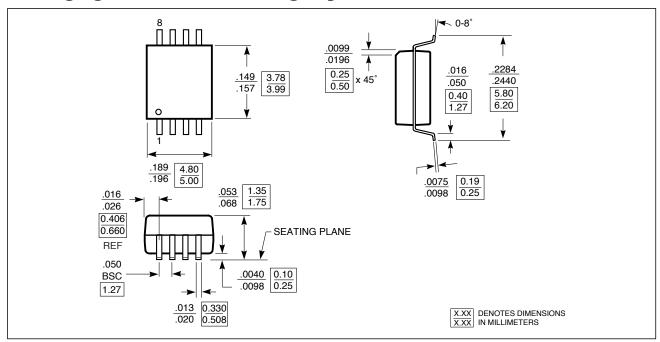

## **Packaging Mechanical Drawing: 8 pin SOIC**

## **Ordering Information**

| Ordering Code | Package    |               | Top-Marking     | $T_{\mathbf{A}}$ |               |

|---------------|------------|---------------|-----------------|------------------|---------------|

| PO74G38074ASU | 8-pin SOIC | Tube          | Pb-free & Green | PO74G38074AS     | -40°C to 85°C |

| PO74G38074ASR | 8-pin SOIC | Tape and reel | Pb-free & Green | PO74G38074AS     | -40°C to 85°C |