# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# Mitsubishi 32-bit RISC Single-chip Microcomputers M32R Family M32R/ECU Series

# http://www.infomicom.maec.co.jp/indexe.htm

Before using this material, please visit the above website to confirm that this is the most current document available.

#### Keep safety first in your circuit designs!

Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement

of any third-party's rights, originating in the use of any product data, diagrams, charts,

programs, algorithms, or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Mitsubishi Electric Corporation by various means, including the Mitsubishi Semiconductor home page (http://www.mitsubishichips.com).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use

in a device or system that is used under circumstances in which human life is potentially at

stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any

specific purposes, such as apparatus or systems for transportation, vehicular, medical,

aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/ or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

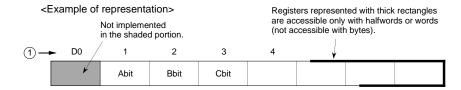

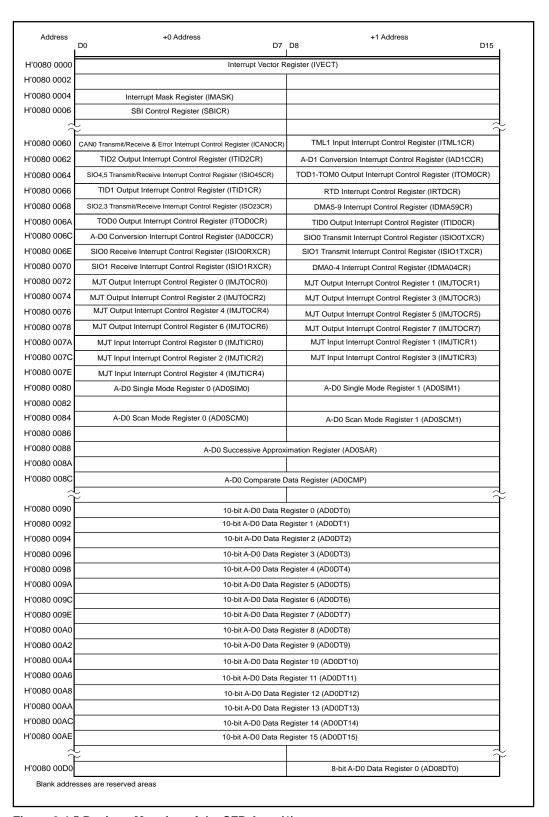

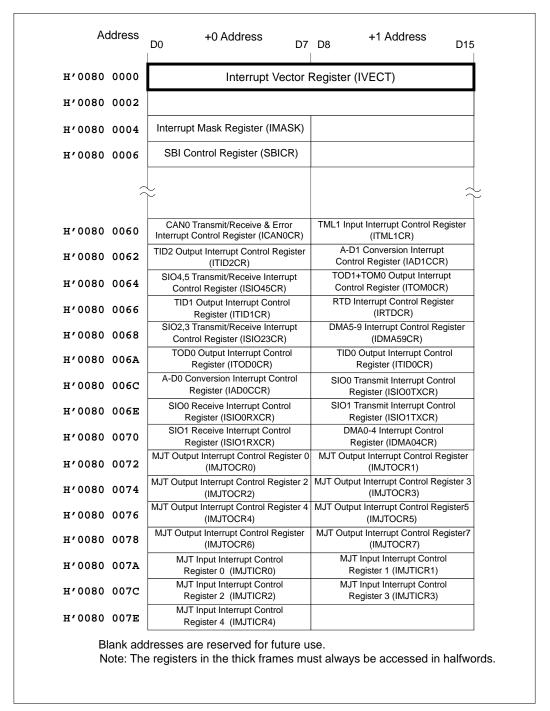

#### How to read internal I/O register tables

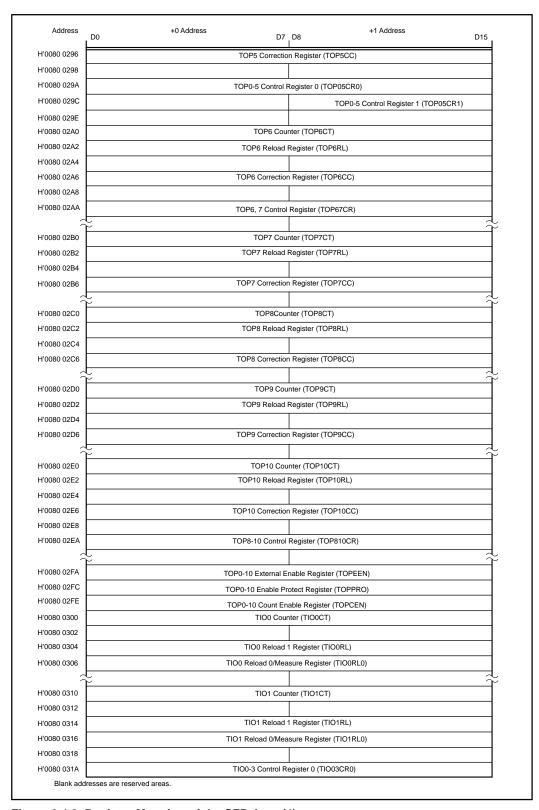

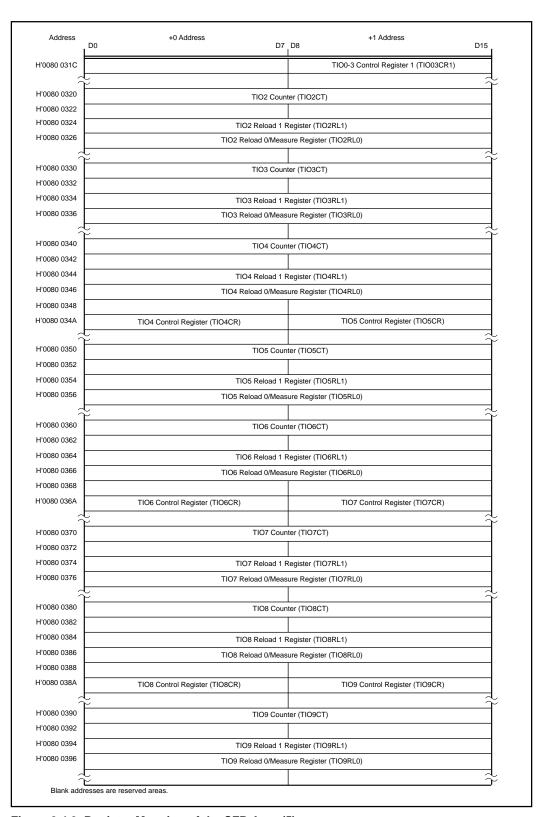

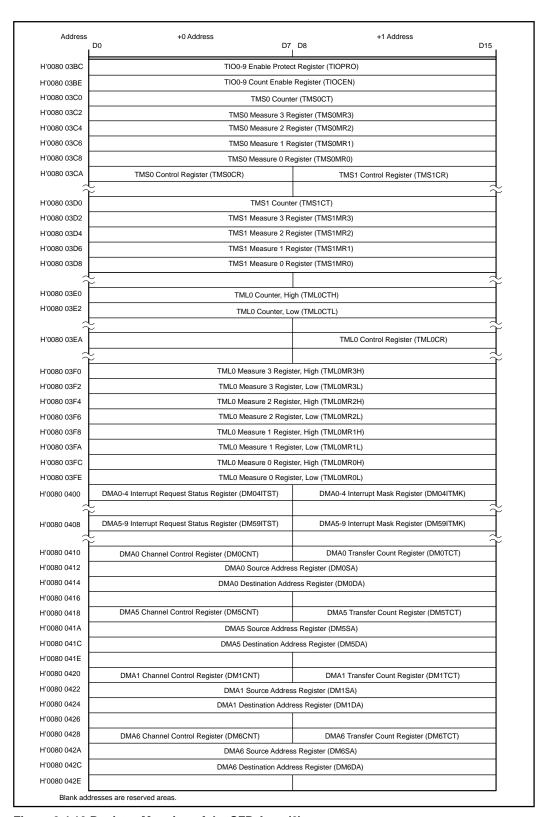

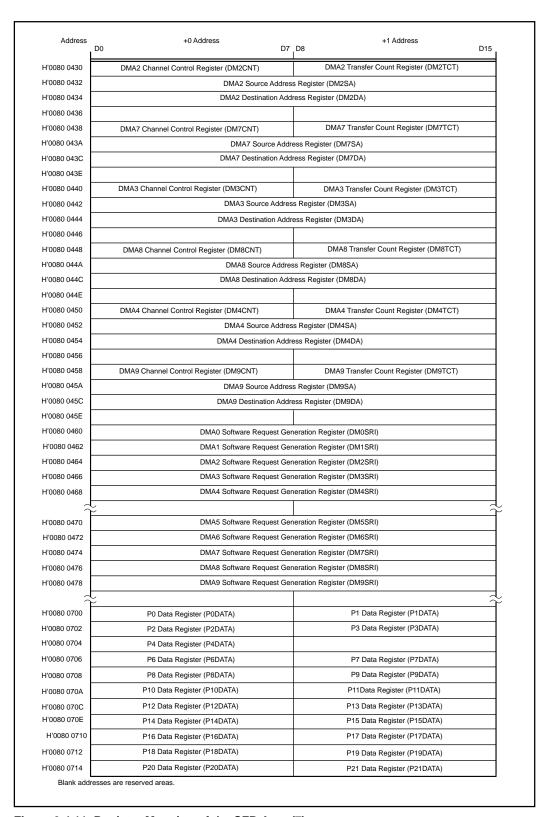

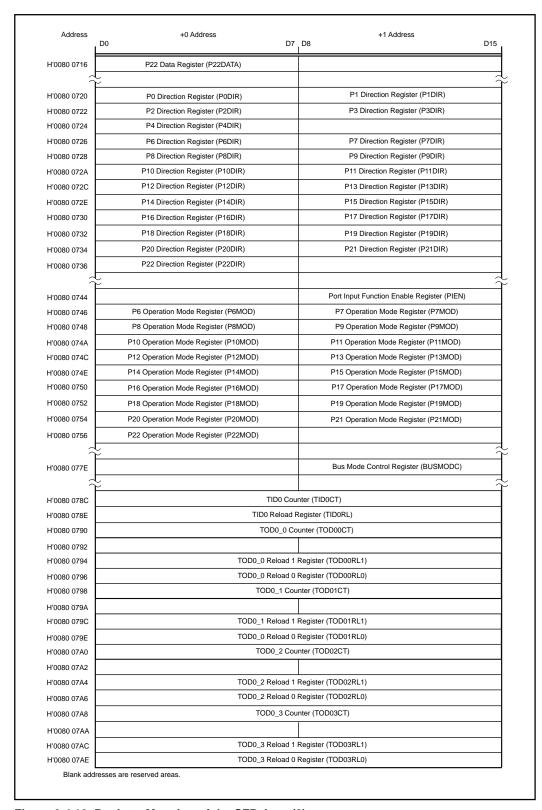

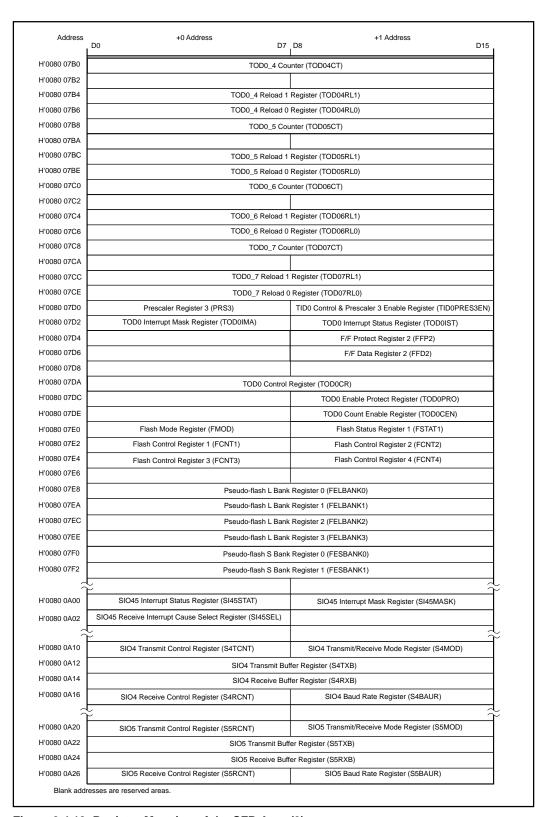

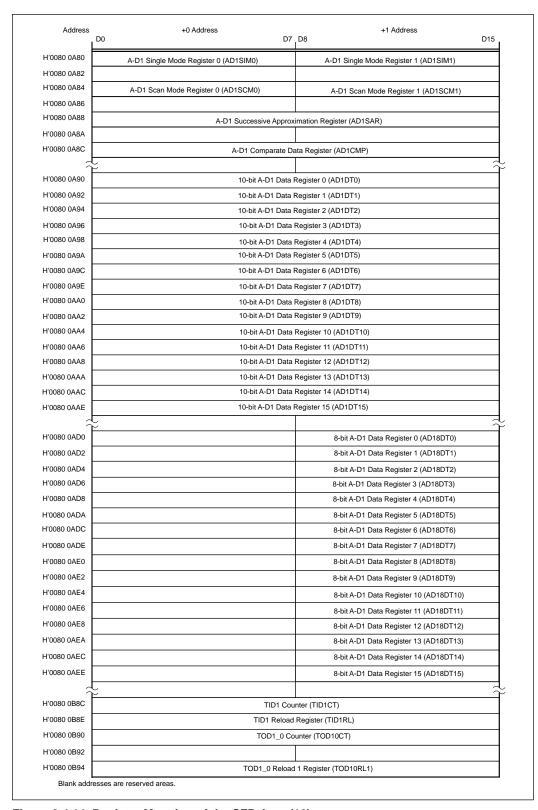

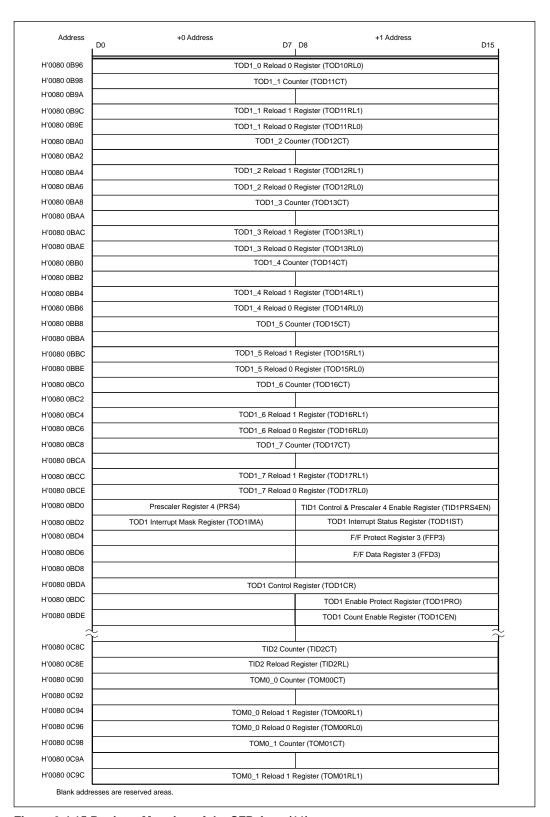

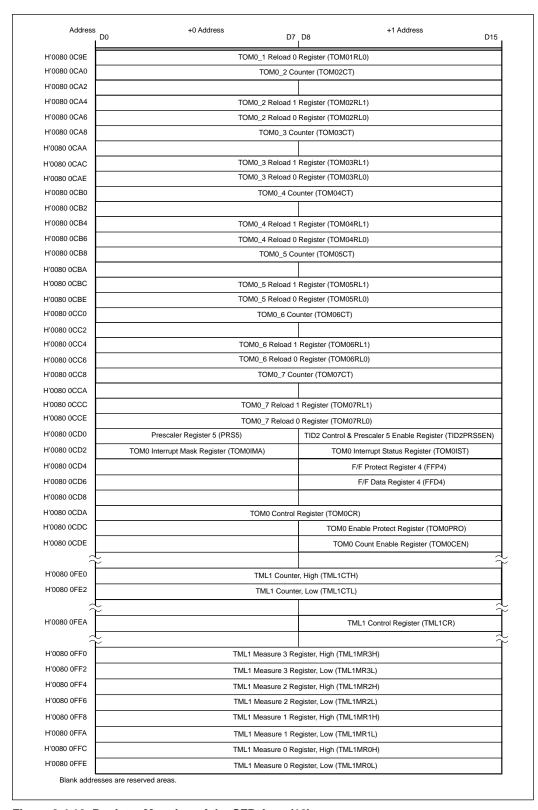

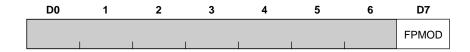

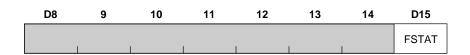

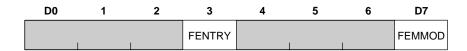

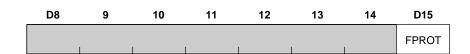

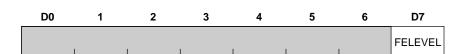

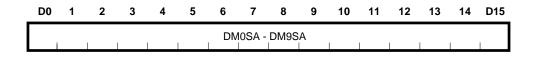

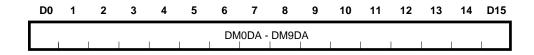

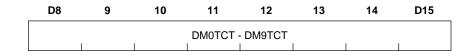

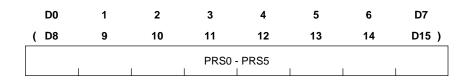

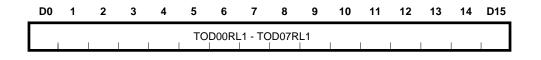

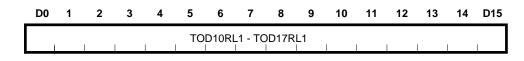

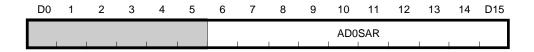

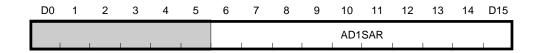

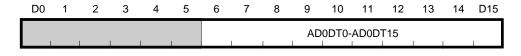

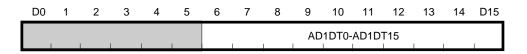

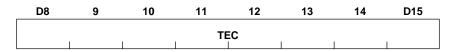

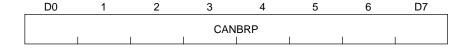

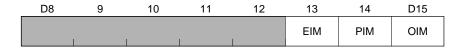

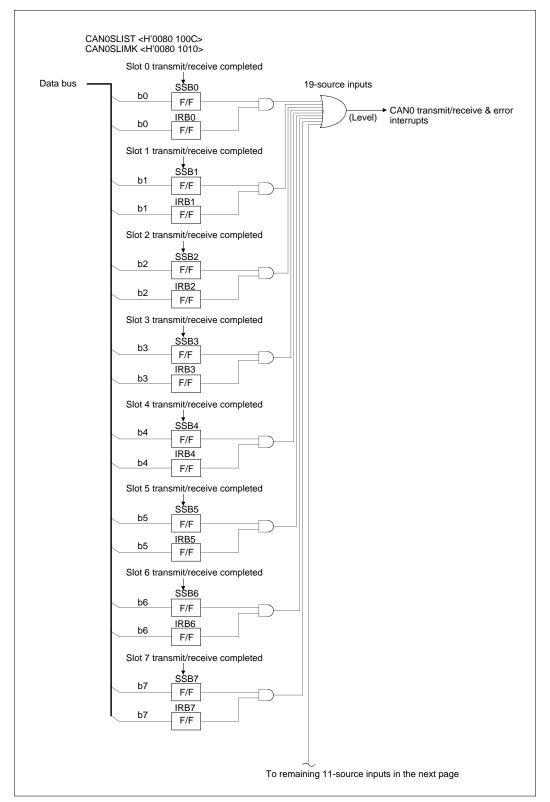

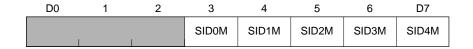

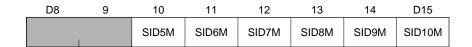

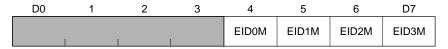

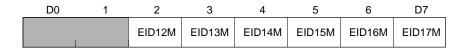

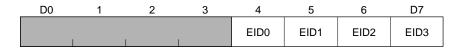

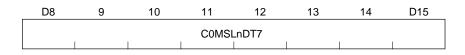

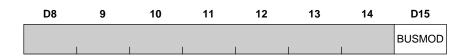

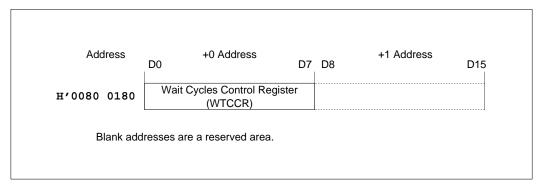

- ① Bit Numbers: Each register is connected with an internal bus of 16-bit wide, so the bit numbers of the registers located at even addresses are D0-D7, and those at odd addresses are D8-D15.

- ② State of Register at Reset: Represents the initial state of each register immediately after reset with hexadecimal numbers (undefined bits after reset are indicated each in column ③.)

3 At read:

O ... read enabled

? ... read disabled (read value invalid)

0 ... Read always as 0 1 ... Read always as 1

At write: O: Write enabled

$\Delta$ : Write enable conditionally

(include some conditions at write)

- : Write disabled (Written value invalid)

|   |               |          | 2 → <at h'04="" reset:=""></at> |   |  |

|---|---------------|----------|---------------------------------|---|--|

| D | Bit name      | Function | R                               | W |  |

| 0 | Not assigned. |          | 0                               | - |  |

| 1 | Abit          | 0:       | 0                               | 0 |  |

|   | ()            | 1:       |                                 |   |  |

| 2 | Bbit          | 0:       | 0                               | 0 |  |

|   | ()            | 1:       |                                 |   |  |

| 3 | Cbit          | 0:       | 0                               | 0 |  |

|   | ()            | 1:       | <b>†</b>                        | Ť |  |

|   |               |          | 3                               | 4 |  |

| Rev. | Date of   |         | Contents of revision                                                                                      |

|------|-----------|---------|-----------------------------------------------------------------------------------------------------------|

|      | issue     | Pages   | Points                                                                                                    |

| 0.1  | Mar.17,00 | _       | First edition issued                                                                                      |

| 2.1  | Jan.16,03 | Overall | Description of the 32174 group added                                                                      |

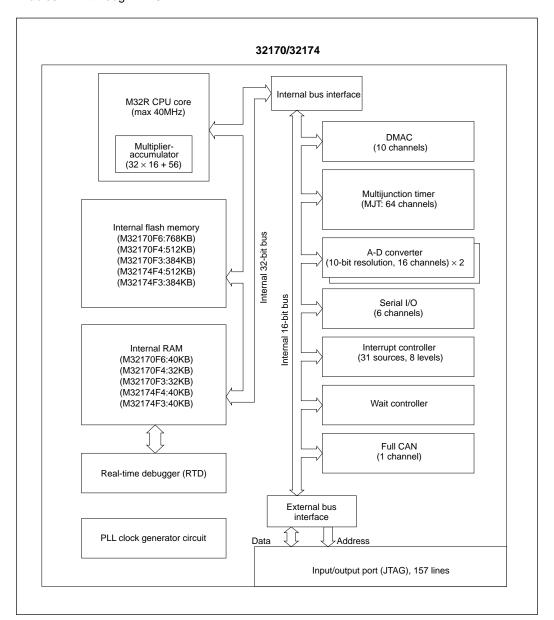

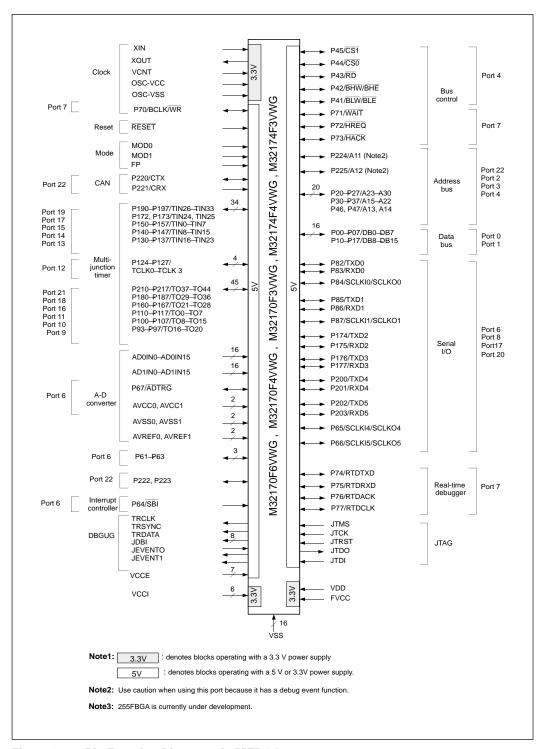

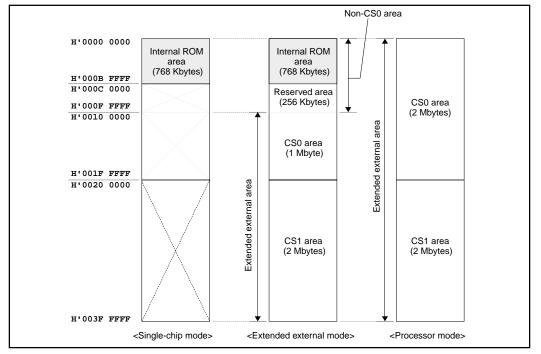

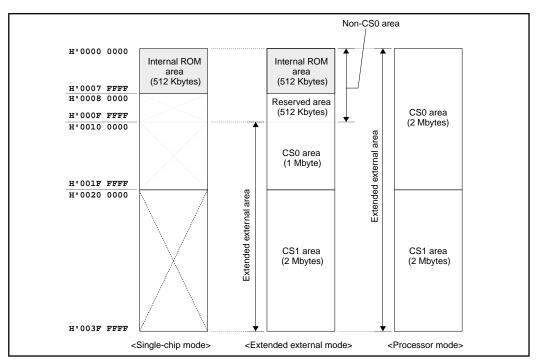

|      |           | P1-7    | M32174F4 and M32174F3 added to the internal flash memory and internal RAM in Figure 1.2.1                 |

|      |           | P1-10   | Table 1.2.4 added                                                                                         |

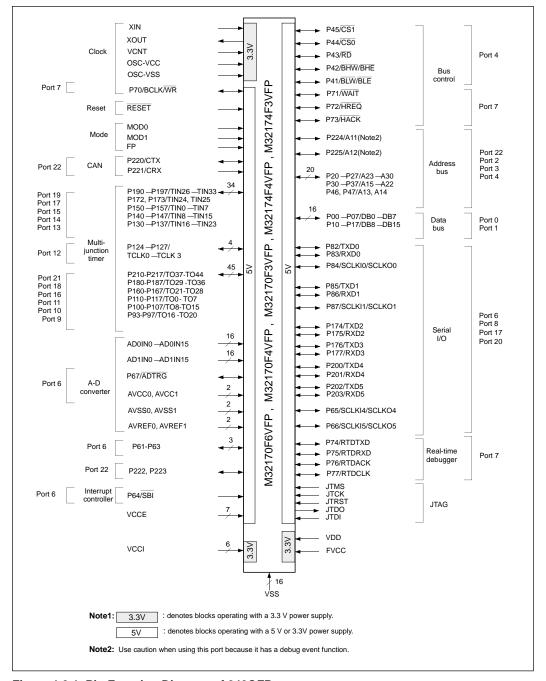

|      |           | P1-11   | Note 1 in Figure 1.3.1 corrected                                                                          |

|      |           |         | Incorrect) Operates with a 5 V power supply.                                                              |

|      |           |         | Correct) Operates with 3.3 V and 5 V power supplies.                                                      |

|      |           | P1-12   | M32174F4VWG and M32174F3VWG added to Figure 1.3.2                                                         |

|      |           |         | Note 1 corrected                                                                                          |

|      |           |         | Incorrect) Operates with a 5 V power supply.  Correct) Operates with 3.3 V and 5 V power supplies.        |

|      |           | P1-13   |                                                                                                           |

|      |           | P1-13   | Table 1.3.1, "Description of the 32170 Pin Function," corrected                                           |

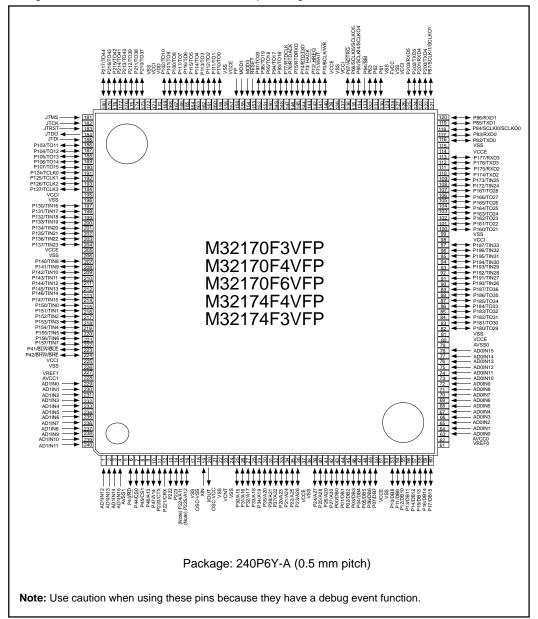

|      |           |         | M32174F4VFP and M32174F3VFP added to Figure 1.4.1                                                         |

|      |           | P1-22   | M32174F4VWG and M32174F3VWG added to Figure 1.4.2                                                         |

|      |           | P2-14   | Section 2.7, "Precautions on CPU," newly added                                                            |

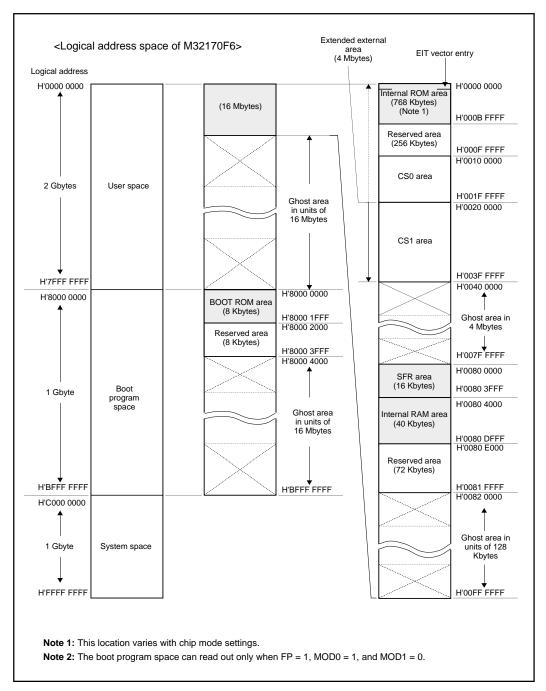

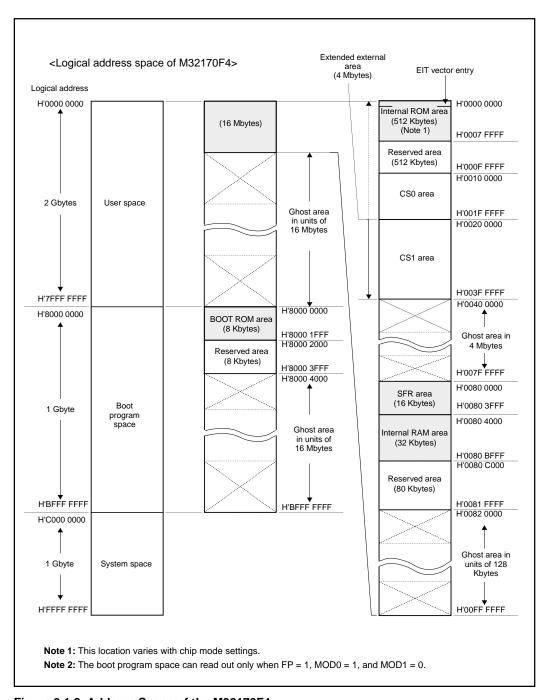

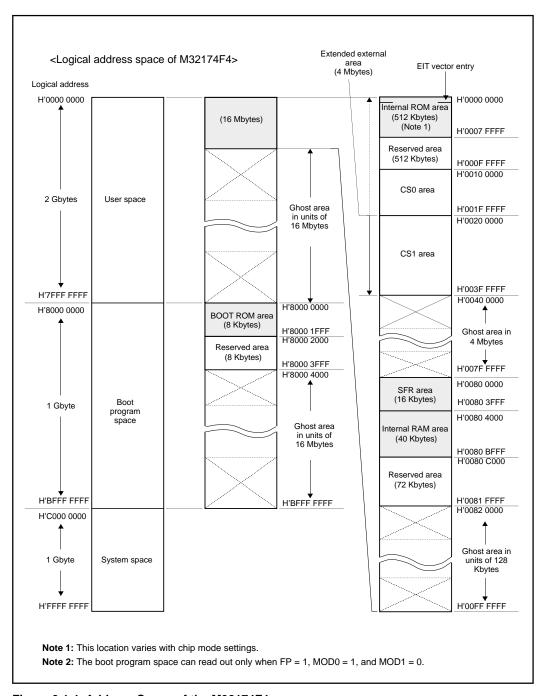

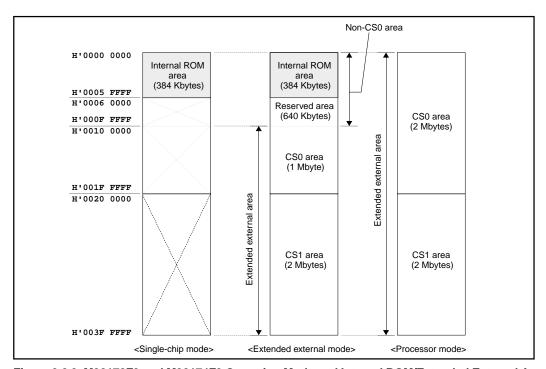

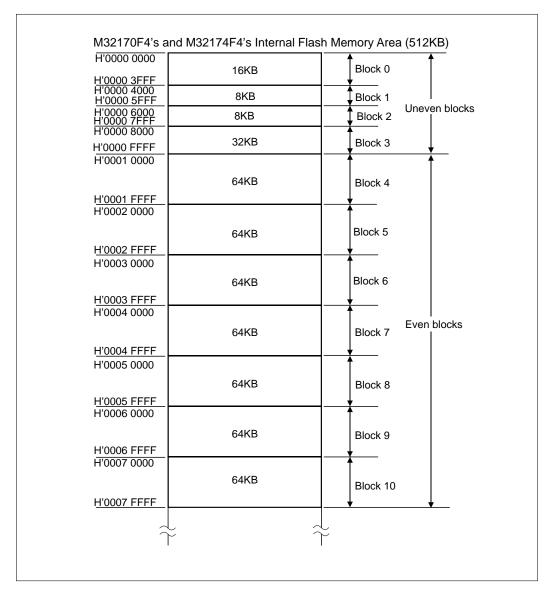

|      |           | P3-6    | Address space of the M32174F4 added to Figure 3.1.4                                                       |

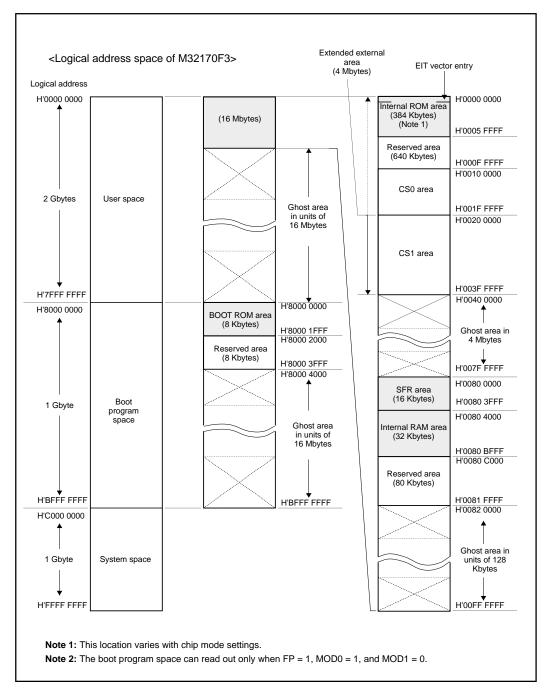

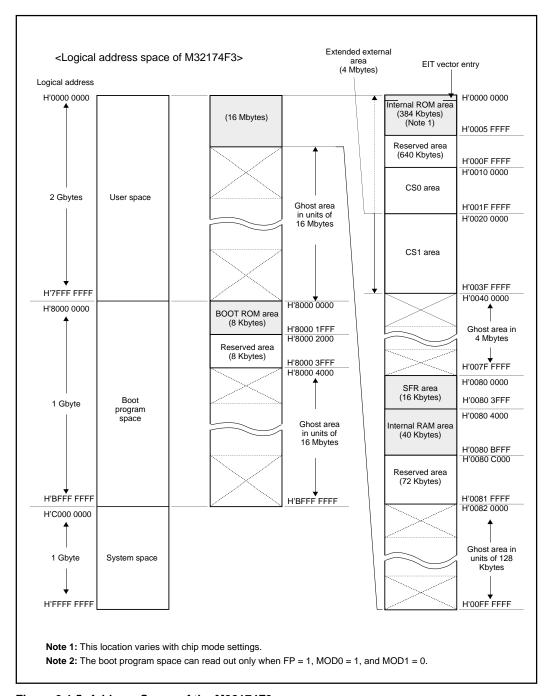

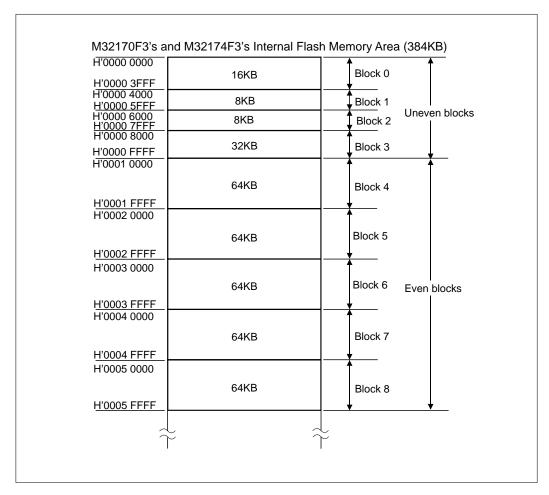

|      |           | P3-7    | Address space of the M32174F3 added to Figure 3.1.5                                                       |

|      |           | P3-10   | M32174F4 and M32174F3 added to Table 3.3.1                                                                |

|      |           | P3-11   | M32174F4 and M32174F3 added to Table 3.4.1                                                                |

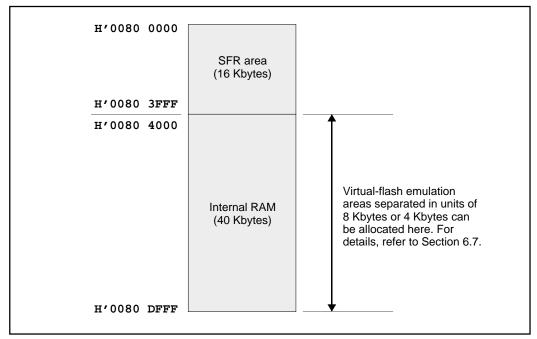

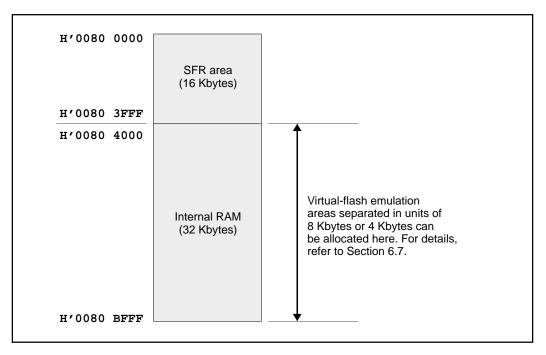

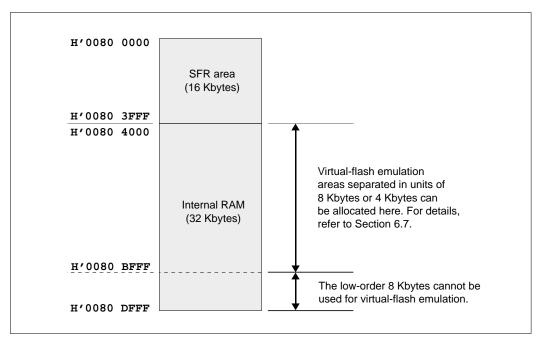

|      |           | P3-12   | Internal RAM area/SFR (Special Function Register) area of the M32174F4 and M32174F3 added to Figure 3.4.3 |

|      |           | P5-7    | Caution corrected                                                                                         |

|      |           | P5-8    | Caution corrected                                                                                         |

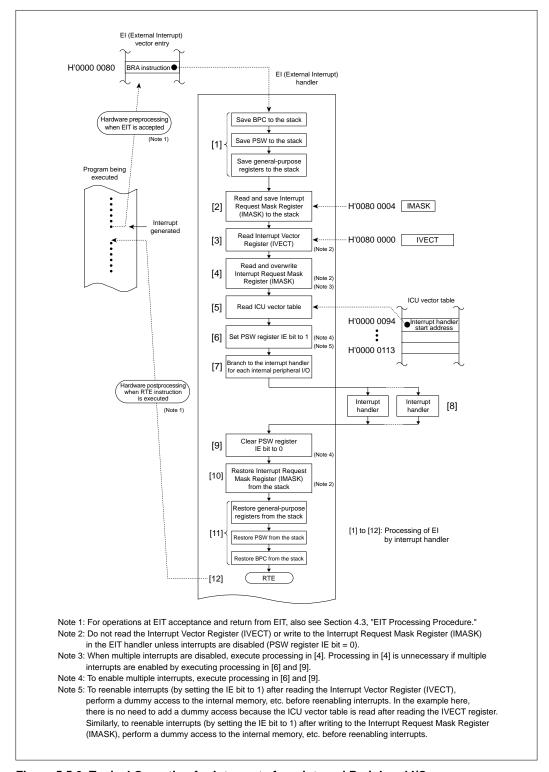

|      |           | P5-20-  | Section 5.5.2, "Processing by Internal Peripheral I/O Interrupt by Handlers," aftered                     |

|      |           | P5-21   | Figure 5.5.2 altered                                                                                      |

|      |           | P6-2    | M32174F4 and M32174F3 added to Table 6.2.1                                                                |

|      |           | P6-3    | M32174F4 and M32174F3 added to Table 6.3.1                                                                |

|      |           | P6-40   | Figure 6.5.15 corrected                                                                                   |

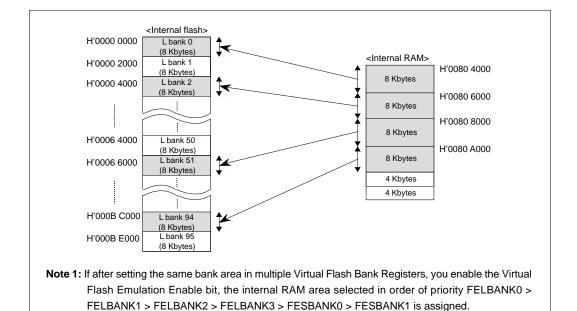

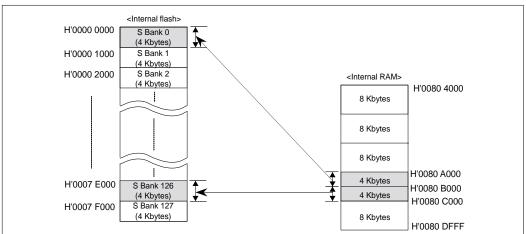

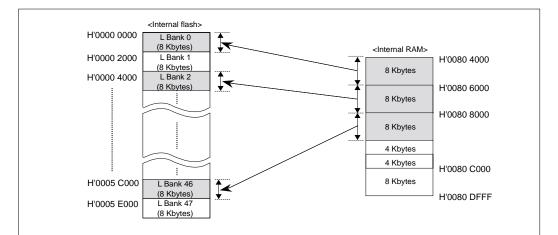

|      |           | P6-45   | Bank configuration of the M32174F4 and M32174F3's internal RAM added to Figure 6.7.3                      |

|      |           | P6-46   | Precautions in Notes 3 through 5 added                                                                    |

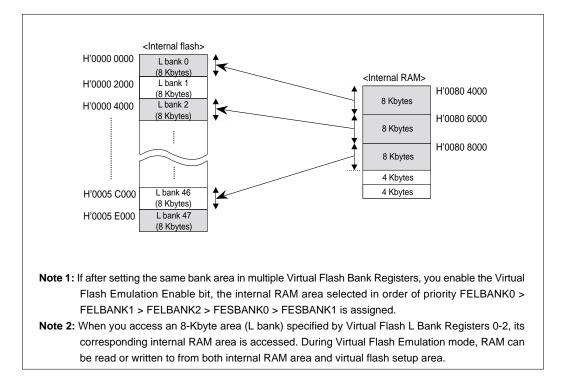

|      |           | P6-50   | M32174F4's virtual-flash emulation area divided in units of 8 Kbytes added                                |

|      |           |         | to Figure 6.7.10                                                                                          |

|      |           |         |                                                                                                           |

| Rev. | Date of   | Contents of revision |                                                                                                                                                                                                                    |

|------|-----------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | issue     | Pages                | Points                                                                                                                                                                                                             |

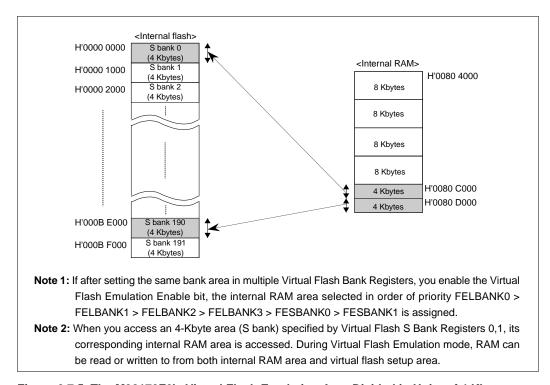

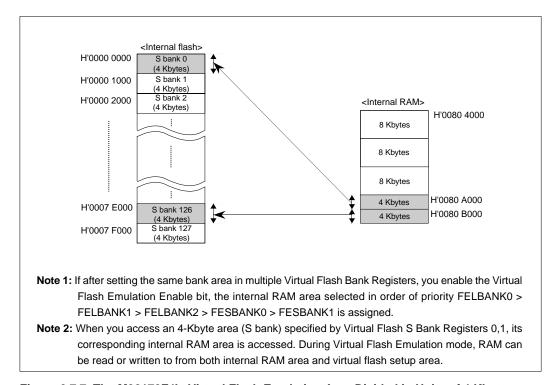

| 2.1  | Jan.16,03 | P6-50                | M32174F4's virtual-flash emulation area divided in units of 4 Kbytes added to Figure 6.7.11                                                                                                                        |

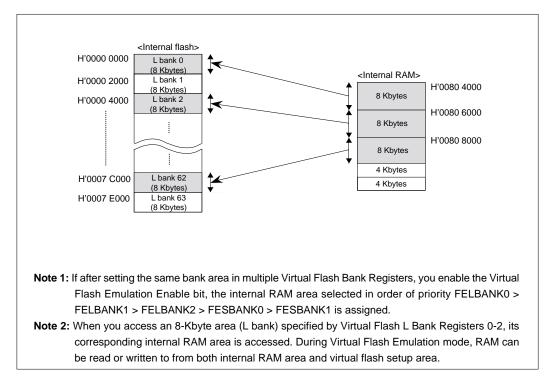

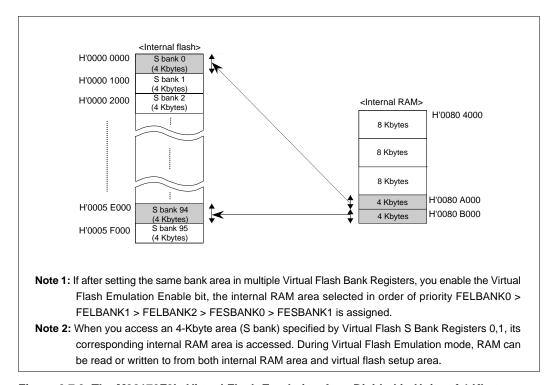

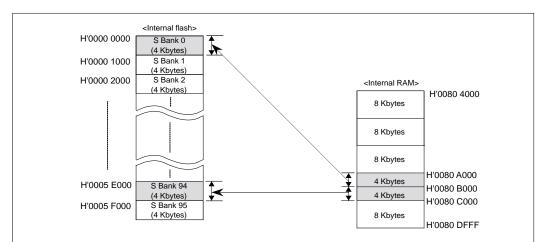

|      |           | P6-51                | M32174F3's virtual-flash emulation area divided in units of 8 Kbytes added to Figure 6.7.12                                                                                                                        |

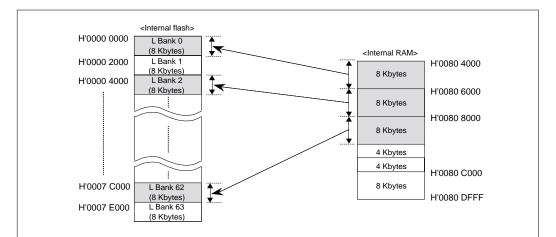

|      |           |                      | M32174F3's virtual-flash emulation area divided in units of 8 Kbytes added to Figure 6.7.13                                                                                                                        |

|      |           | P6-60                | Precautions added                                                                                                                                                                                                  |

|      |           | P7-4                 | Table 7.3.2 added                                                                                                                                                                                                  |

|      |           | P8-31-               | Figures 8.4.1 through 8.4.4 corrected                                                                                                                                                                              |

|      |           | P8-34                |                                                                                                                                                                                                                    |

|      |           | P8-35                | Section 8.5, "Precautions on Input/output Ports," newly added                                                                                                                                                      |

|      |           | P10-1–<br>P10-232    | Chapter 10 overall. Prescalers uniformly referred to as PRS                                                                                                                                                        |

|      |           | P10-83               | Figure 10.3.8 corrected                                                                                                                                                                                            |

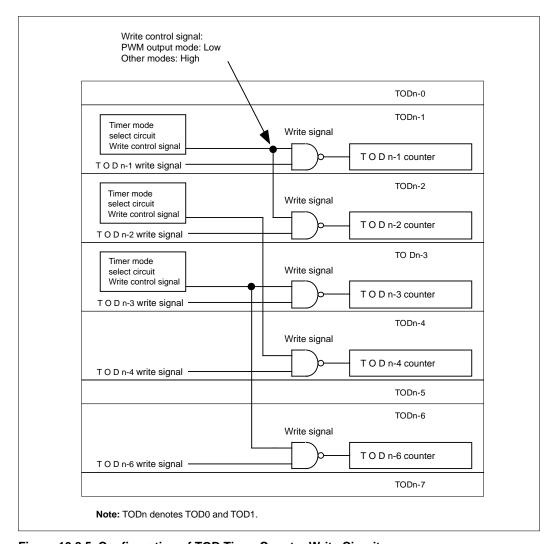

|      |           | P10-184–<br>P10-185  | (1) TOD timer counter write enable/disable conditions newly added                                                                                                                                                  |

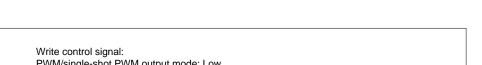

|      |           | P10-213-<br>P10-214  | (1) TOM timer counter write enable/disable conditions newly added                                                                                                                                                  |

|      |           | P11-3                | Table 11.1.1 corrected                                                                                                                                                                                             |

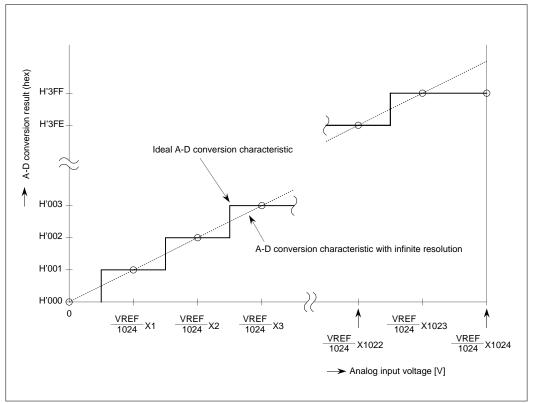

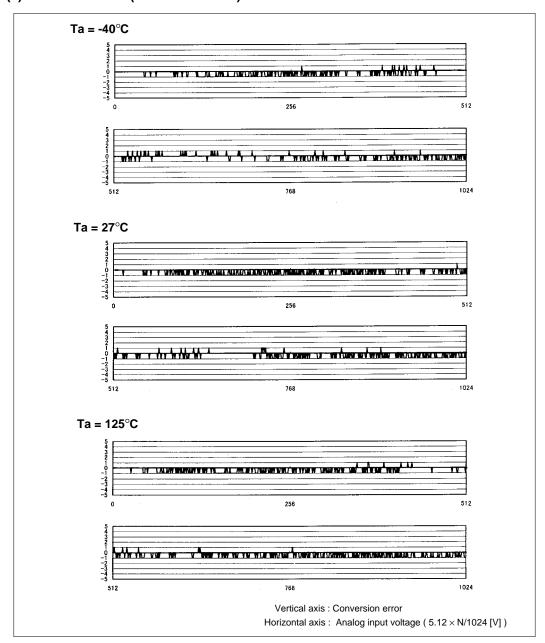

|      |           | P11-48               | Contents of description in Section 11.3.5, "Definition of A-D Conversion Accuracy," altered                                                                                                                        |

|      |           | P11-49               | Figure 11.3.5 altered Figures 11.3.6 and 11.3.7 deleted                                                                                                                                                            |

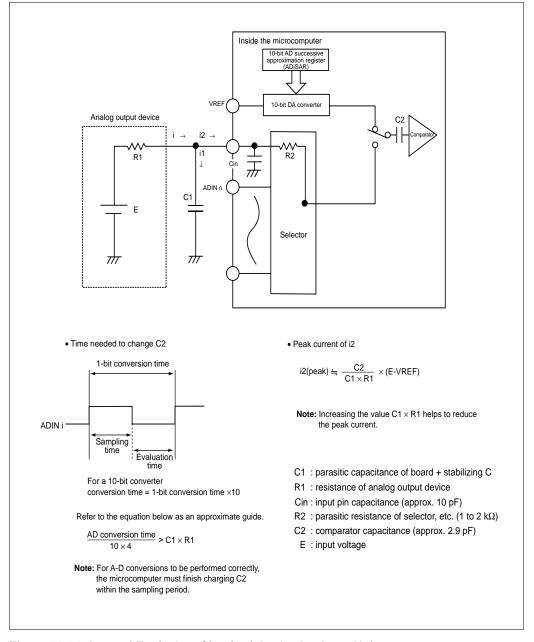

|      |           | P11-51               | Figure 11.4.1, "Internal Equivalent Circuit of the Analog Input Unit," newly added                                                                                                                                 |

|      |           | P12-27               | Description of the last line in Section 12.2.8, "SIO Baud Rate Register," corrected Incorrect) 7 or less → Correct) 7 or more                                                                                      |

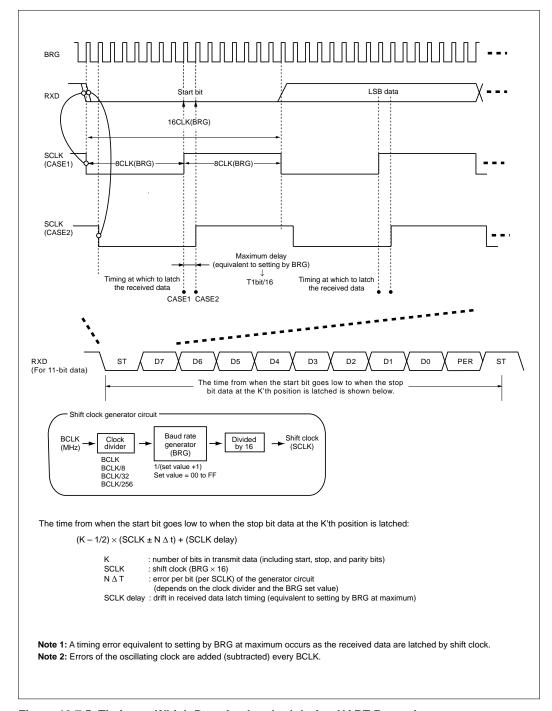

|      |           | P12-61               | Figure 12.7.5, "Timing at Which to Latch Data during UART Reception," newly added                                                                                                                                  |

|      |           | P13-2                | Description in Section 13.1, "Outline of the CAN Module," corrected Incorrect) Compliant with CAN (Controller Area Network) Specification 2.0B Correct) Compliant with CAN (Controller Area Network) Specification |

|      |           |                      | 2.0B active                                                                                                                                                                                                        |

| Rev. | Date of   |         | Contents of revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | issue     | Pages   | Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1  | Jan.16,03 | P13-2   | Contents of protocol description in Table 13.1.1 corrected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |           |         | Incorrect) CAN Specification 2.0B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |           |         | Correct) CAN Specification 2.0B active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |           |         | Precautions added to Table 13.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |           | P13-9   | Precautions added to (4) FRST (forcible reset) bit (D11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |           | P13-14  | Precautions added to (11) MSN (message slot number) bits (D12–D15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |           | P13-17  | Precautions added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |           | P13-21  | Precautions added to Note 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |           | P13-35  | Precautions added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |           | P13-37  | Precautions in Note 2 deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

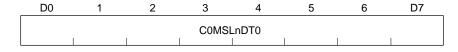

|      |           | P13-44  | Precautions added to description of CAN message slot data 0 (COMSLnDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |           | P13-59  | Section 13.4.2, "CAN Timing," newly added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |           | P13-81  | Figure 13.8.2 corrected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |           | P13-82  | Section 13.9, "Precautions about CAN Module," newly added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |           | P18-2   | Precautions added to Figure 18.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |           | P19-14  | Description of BSDL for the 32170 (Figures 19.5.1 through 19.5.19) deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |           | P19-15- | Precautions added to Figures 19.6.1 and 19.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      |           | P19-16  | , and the second |

|      |           | P19-17- | Figure 19.7.1, "Processing Pins when Not Using JTAG (for 240QFP),"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |           | P19-18  | and Figure 19.7.2, "Processing Pins when Not Using JTAG (for 255QFP)," newly added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

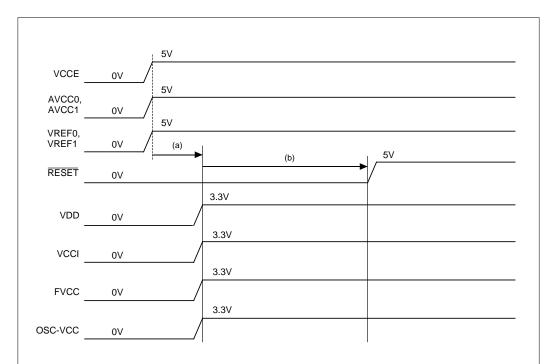

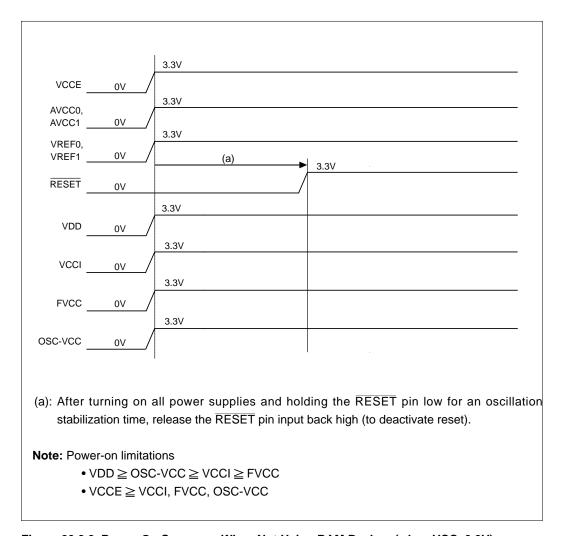

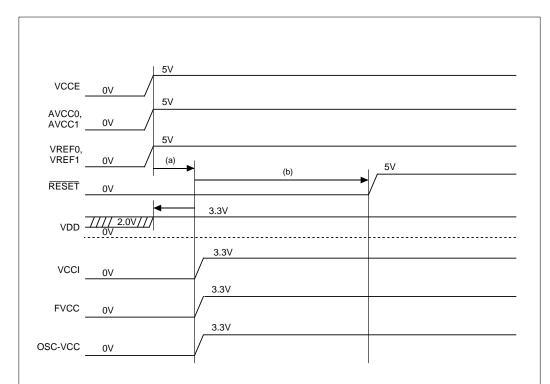

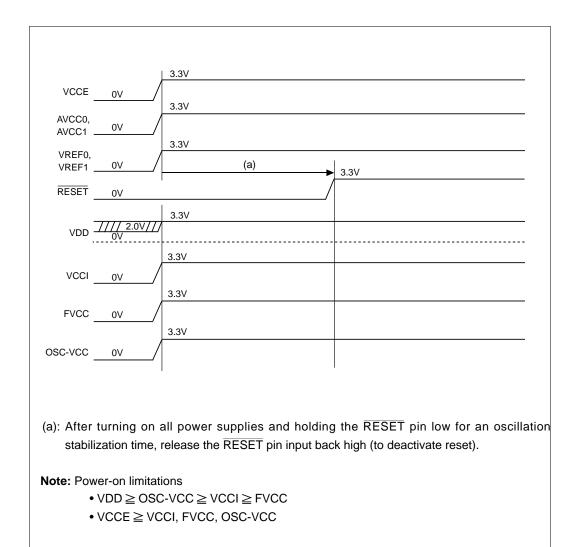

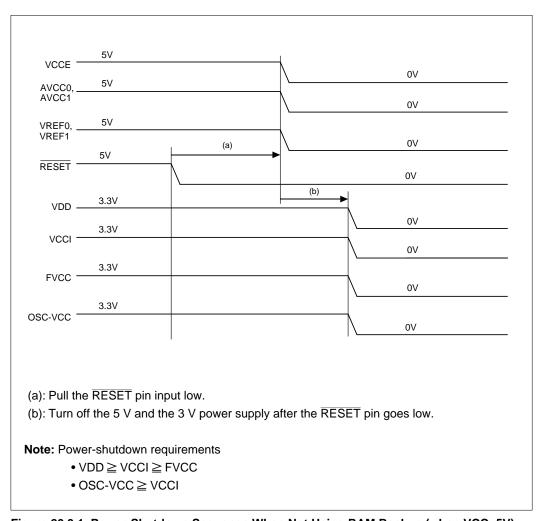

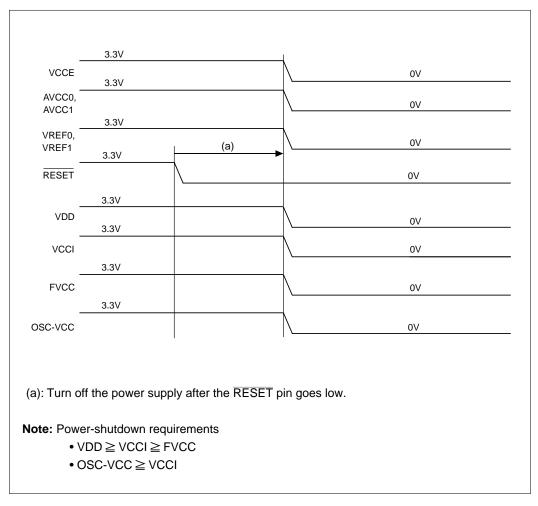

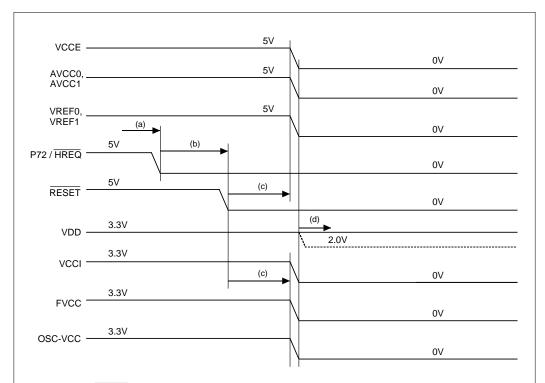

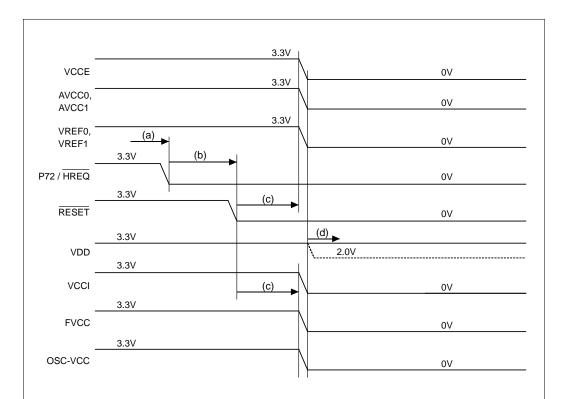

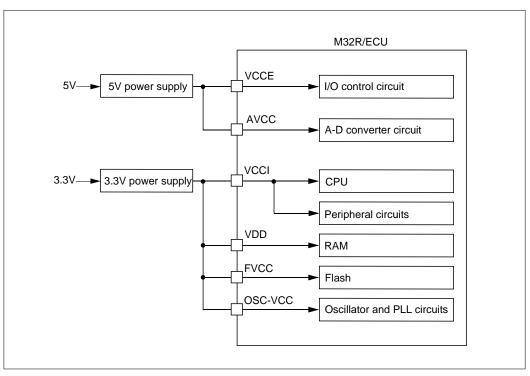

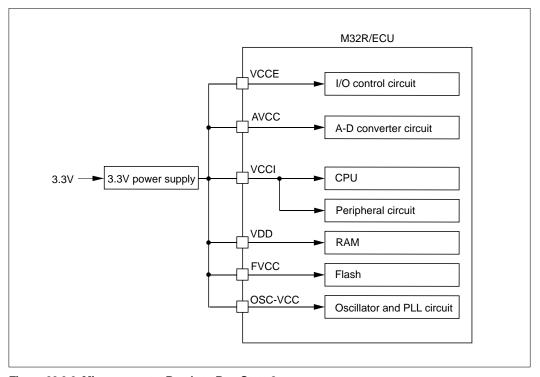

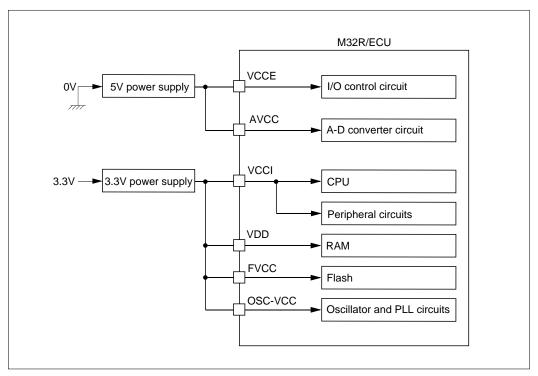

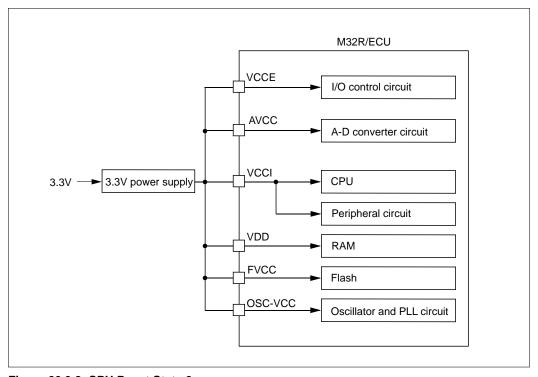

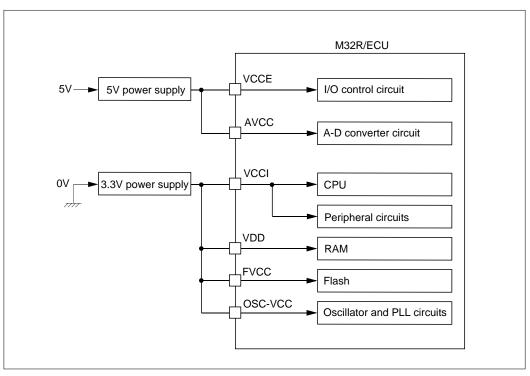

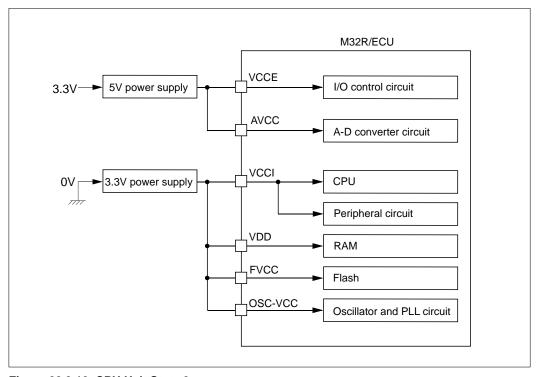

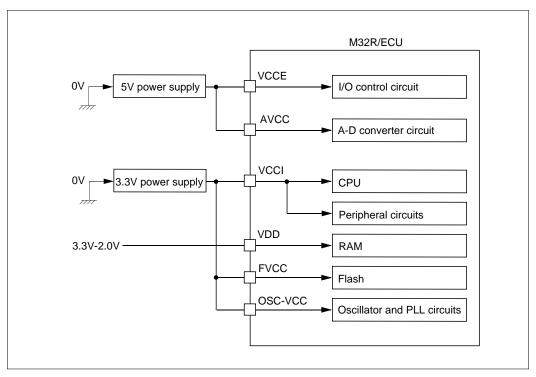

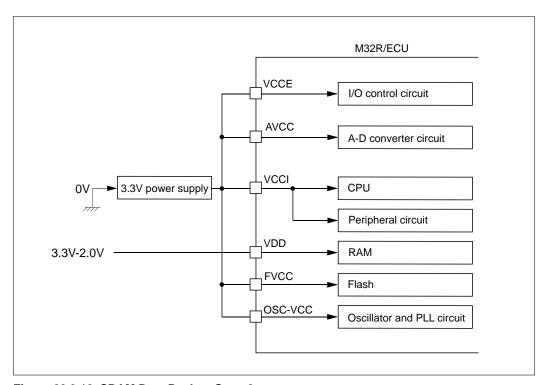

|      |           | P20-1-  | Power turn-on/turn-off sequences during VCCE = 3.3 V added to diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |           | P20-16  | in Chapter 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |           | P21-2   | Absolute maximum ratings (-40 to 125°C) corrected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |           | P21-3   | Recommended operating conditions corrected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |           | P21-5   | Electrical characteristics in (1) f = (XIN) = 10 MHz corrected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      |           | P21-7   | Electrical characteristics in (3) f = (XIN) = 8 MHz corrected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

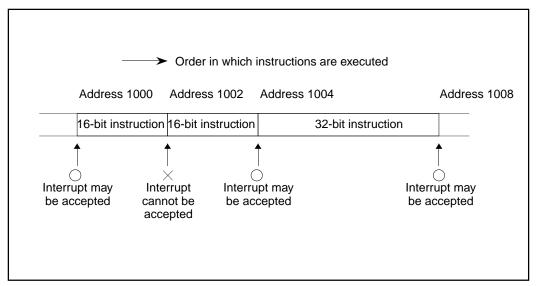

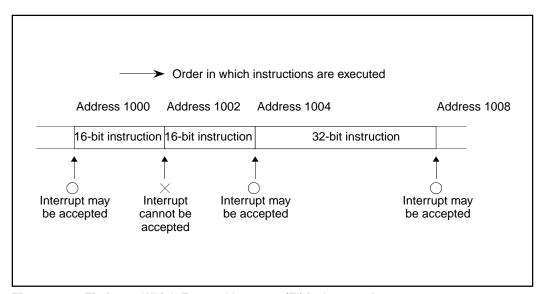

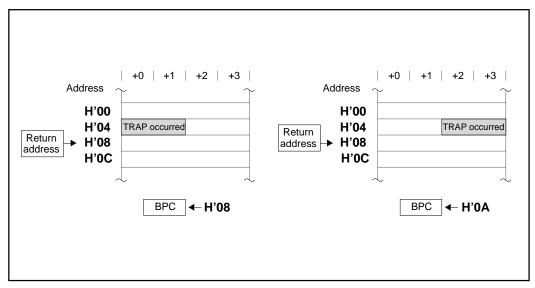

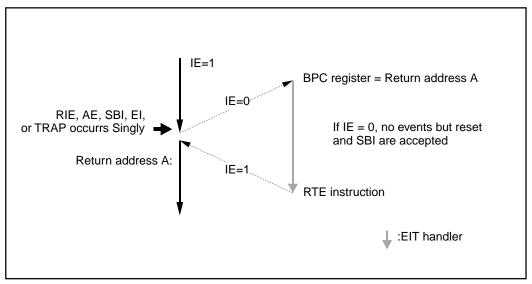

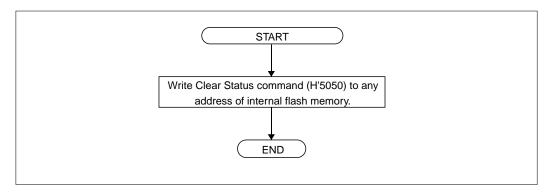

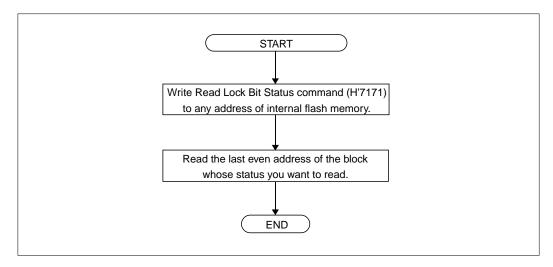

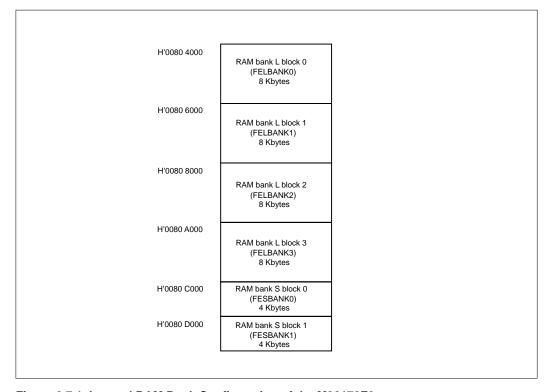

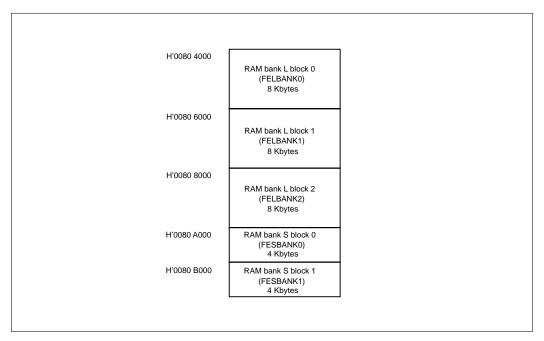

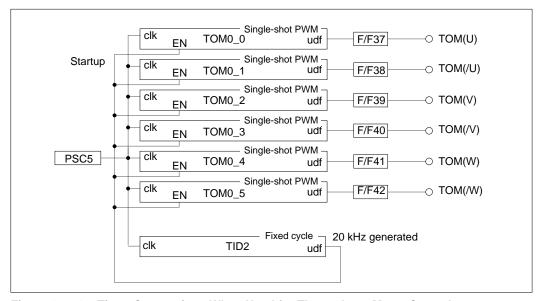

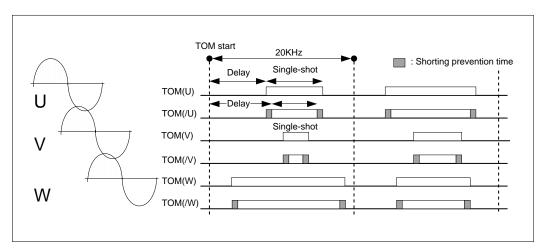

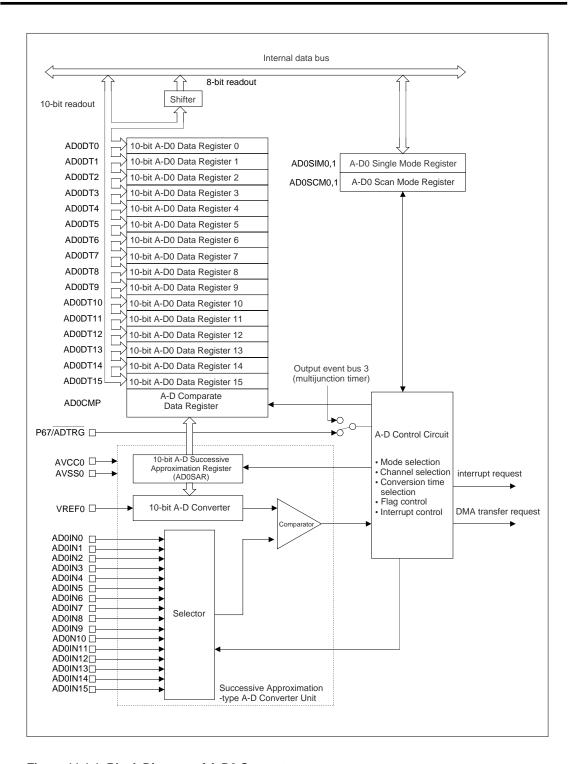

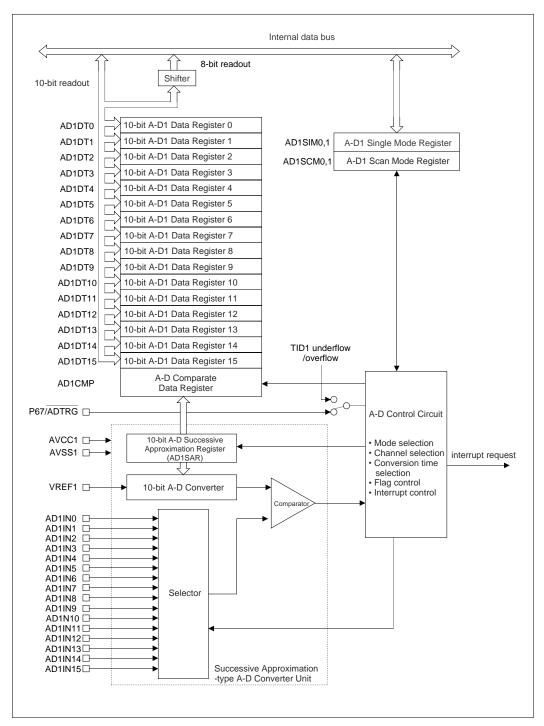

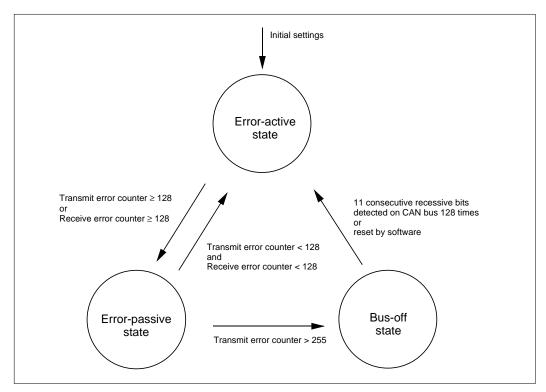

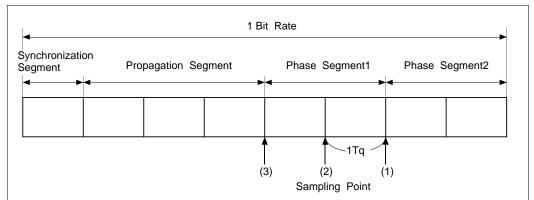

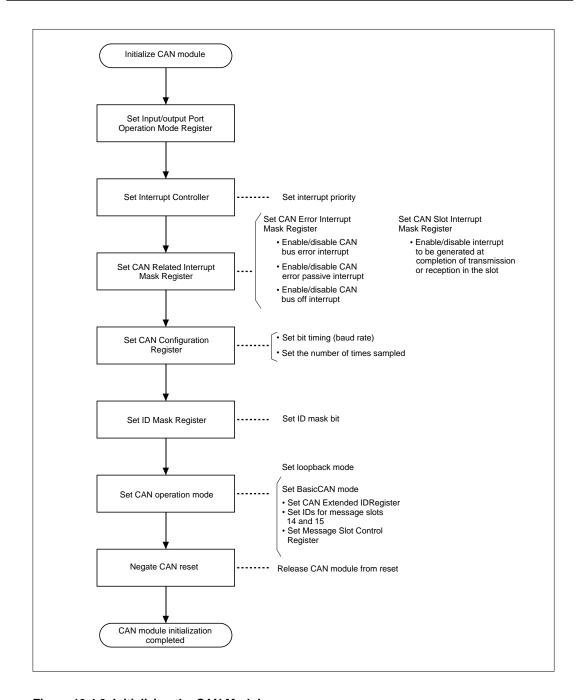

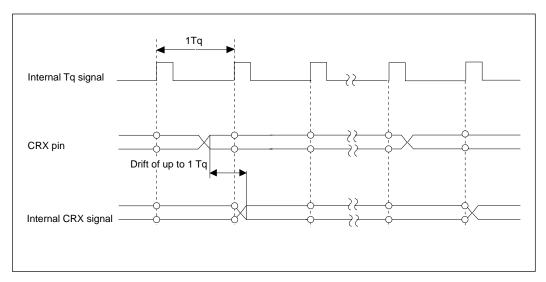

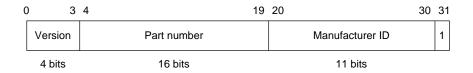

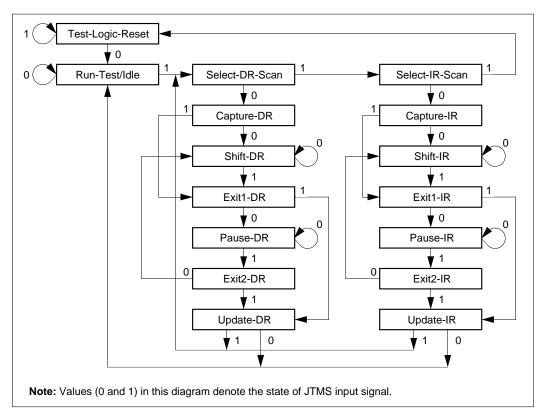

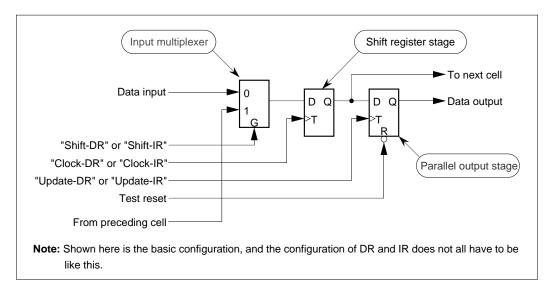

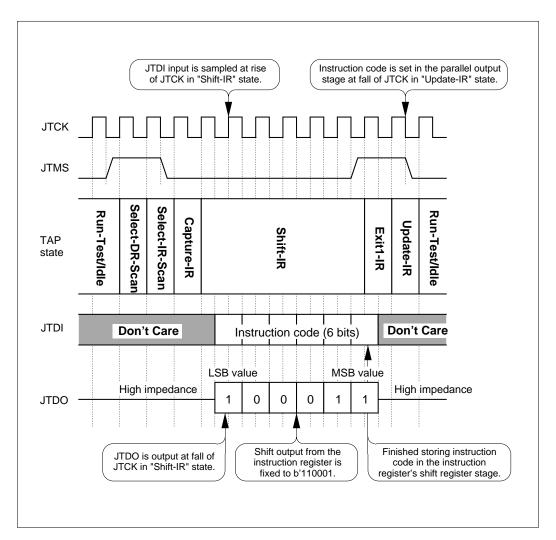

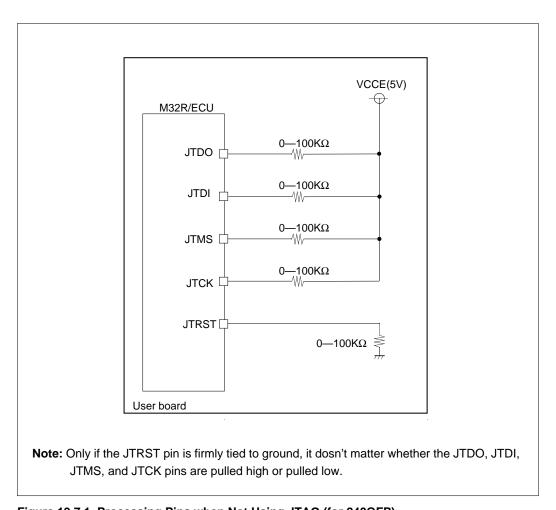

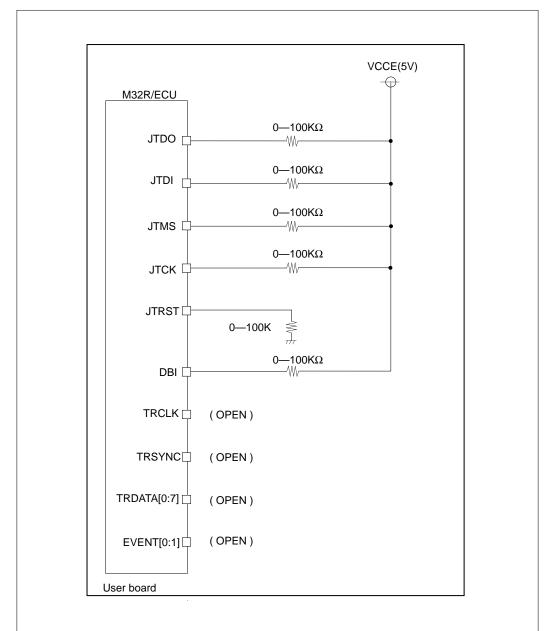

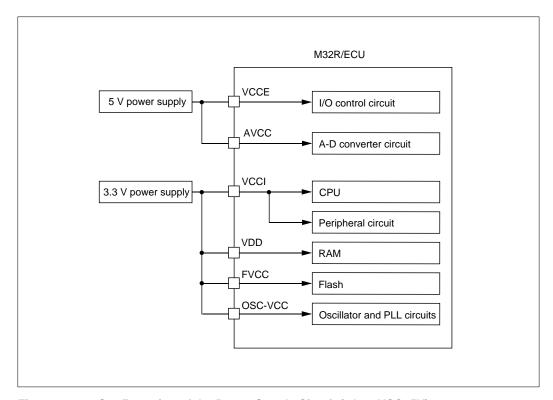

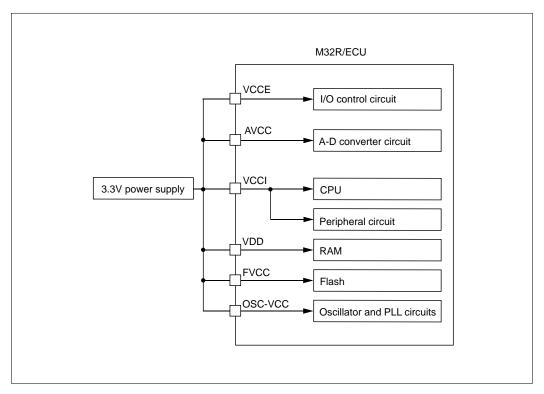

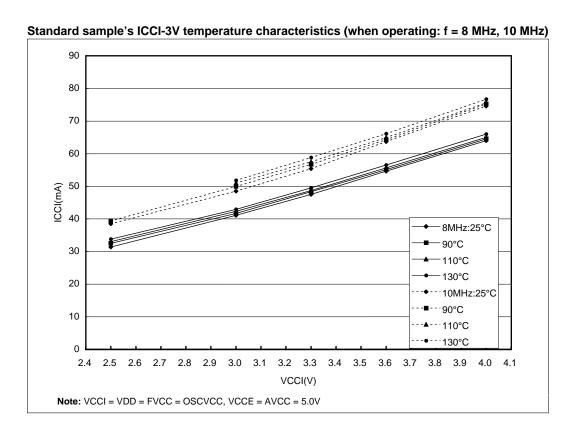

|      |           | P21-9   | Standard sample's ICCI-3V temperature characteristics (when operating:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |