# Features

- SPARC V8 High Performance Low-power 32-bit Architecture

- LEON2-FT 1.0.13 compliant

- 8 Register Windows

- Advanced Architecture:

- On-chip Amba Bus

- 5 Stage Pipeline

- 16 kbyte Multi-sets Data Cache

- 32 kbyte Multi-sets Instruction Cache

- On-chip Peripherals:

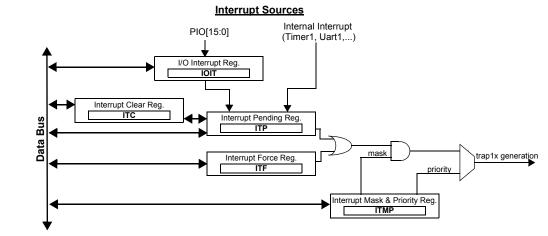

- Memory Interface

PROM Controller

SRAM Controller

SDRAM Controller

- Timers

- Two 24-bit Timers Watchdog Timer

- Two 8-bit UARTs

- Interrupt Controller with 4 External Programmable Inputs

- 32 Parallel I/O Interface

- 33MHz PCI Interface Compliant with 2.2 PCI Specification

- Integrated 32/64-bit IEEE 754 Floating-point Unit

- Fault Tolerance by Design

- Full Triple Modular Redundancy (TMR)

- EDAC Protection

- Parity Protection

- Debug and Test Facilities

- Debug Support Unit (DSU) for Trace and Debug

- IEEE 1149.1 JTAG Interface

- Four Hardware Watchpoints

- Speed Optimized Code RAM Interface

- 8, 16 and 40-bit boot-PROM (Flash) Interface Possibilities

- Operating range

- Voltages

- 3.3V +/- 0.30V for I/O

- 1.8V +/- 0.15V for Core

- Temperature

- -55°C to 125°C

- Clock: 0MHz up to 100MHz

- Power consumption: 1W at 100MHz

- Performance:

- 86MIPS (Dhrystone 2.1)

- 23MFLOPS (Whetstone)

- Radiation Performance

- Total dose radiation capability (parametric & functional): 60Krads (Si)

- SEU error rate better than 1 E-5 error/device/day

- No Single Event Latchup below a LET threshold of 70 MeV.cm<sup>2</sup>/mg

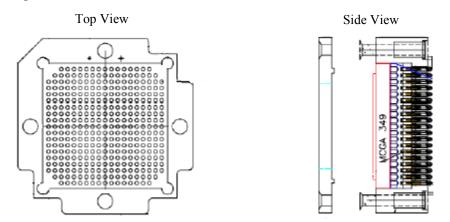

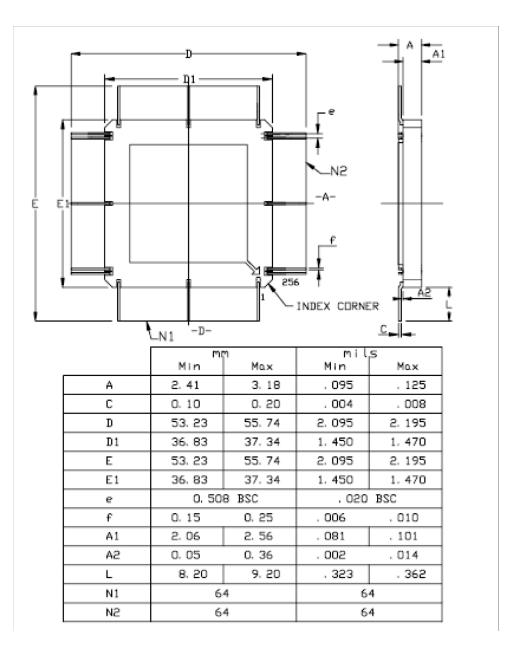

- Package MCGA 349

- Mass: 9g

- Development Kit Including

- AT697 Evaluation Board

- AT697 Sample

- GRMON Development Tool

Rad-Hard 32 bit SPARC V8 Processor

# AT697E

Rev. 4226G-AERO-05/09

# Description

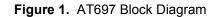

The AT697 is a highly integrated, high-performance 32-bit RISC embedded processor based on the SPARC V8 architecture. The implementation is based on the European Space Agency (ESA) LEON2 fault tolerant model. By executing powerful instructions in a single clock cycle, the AT697 achieves throughputs approaching 1MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed.

The AT697 is designed to be used as a building block in computers for on-board embedded real-time applications. It brings up-to-date functionality and performance for space application.

The AT697 only requires memory and application specific peripherals to be added to form a complete on-board computer.

The AT697 contains an on-chip Integer Unit (IU), a Floating Point Unit (FPU), separate instruction and data caches, hardware multiplier and divider, interrupt controller, debug support unit with trace buffer, two 24-bit timers, Parallel and Serial interfaces, a Watch-dog, a PCI Interface and a flexible Memory Controller. The design is highly testable with the support of a Debug Support Unit (DSU) and a boundary scan through JTAG interface.

An Idle mode holds the processor pipeline and allows Timer/Counter, Serial ports and Interrupt system to continue functioning.

The processor is manufactured using the Atmel 0.18  $\mu$ m CMOS process. It has been especially designed for space, by implementing on-chip concurrent transient and permanent error detection and correction.

The AT697E is the first version of the AT697 processor. A second version of the AT697 processor, the AT697F, is under development.

The AT697F will have improved radiation capabilities (up to 100Krad) and will correct all the bugs described in the AT697E errata sheet. The AT697F will be pinout compatible with the AT697E.

2

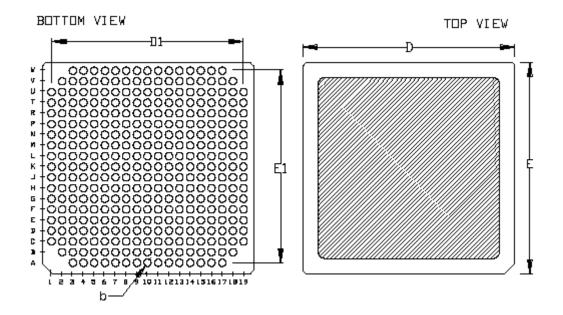

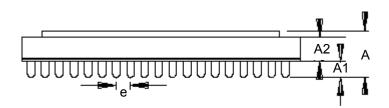

# **Pin Configuration**

# MCGA349 package

## Table 1. AT697E MCGA349 pinout

|    | А       | В       | С       | D        | E        | F       | G        |

|----|---------|---------|---------|----------|----------|---------|----------|

| 1  |         |         | VDD18   | VSS18    | PIO[6]   | PIO[1]  | RAMS[1]  |

| 2  |         | VSS18   | VDD18   | PIO[0]   | N.C.     | PIO[4]  | RAMS[2]  |

| 3  | VDD18   | VDD18   | VSS18   | VCC33    | PIO[2]   | N.C.    | RAMOE[3] |

| 4  | VSS18   | VDD18   | PIO[9]  | N.C.     | PIO[5]   | PIO[3]  | RAMS[4]  |

| 5  | N.C.    | N.C.    | PIO[11] | N.C.     | N.C.     | VSS33   | RAMOE[1] |

| 6  | PIO[13] | PIO[10] | VCC33   | Reserved | CB[0]    | N.C.    | VSS33    |

| 7  | CB[1]   | VSS33   | N.C.    | PIO[15]  | VSS33    | PIO[12] | PIO[7]   |

| 8  | CB[6]   | CB[4]   | D[2]    | VCC33    | CB[7]    | CB[2]   | PIO[8]   |

| 9  | D[3]    | N.C.    | D[1]    | VSS33    | D[6]     | VCC33   | CB[3]    |

| 10 | D[8]    | D[5]    | VCC33   | VSS33    | Reserved | D[10]   | D[4]     |

| 11 | D[12]   | VSS33   | VCC33   | D[13]    | D[7]     | D[15]   | N.C.     |

| 12 | D[17]   | D[18]   | D[11]   | VSS33    | D[14]    | D[16]   | D[19]    |

| 13 | D[21]   | D[23]   | VCC33   | VCC33    | VSS33    | VSS33   | A[1]     |

| 14 | D[25]   | N.C.    | D[22]   | D[27]    | N.C.     | VSS33   | A[3]     |

| 15 | D[30]   | N.C.    | D[26]   | D[29]    | N.C.     | N.C.    | A[12]    |

| 16 | VSS18   | VSS18   | D[28]   | VCC33    | N.C.     | N.C.    | A[6]     |

| 17 | VDD18   | VDD18   | VSS18   | D[31]    | N.C.     | A[7]    | VSS33    |

| 18 |         | VSS18   | VDD18   | VCC33    | A[0]     | A[4]    | A[8]     |

| 19 |         |         | VDD18   | VSS18    | A[2]     | VSS33   | A[9]     |

## Table 2. AT697E MCGA349 pinout (suite)

|    | Н        | j       | k     | I        | m        | n        | р       |

|----|----------|---------|-------|----------|----------|----------|---------|

| 1  | RAMOE[0] | VSS33   | READ  | DSUACT   | BEXC     | VCC33    | SDWE    |

| 2  | RAMOE[2] | ROMS[1] | ТСК   | DSURX    | SDCLK    | VSS33    | PCI_CLK |

| 3  | VCC33    | ROMS[0] | TDI   | DSUTX    | DSUBRE   | SDDQM[1] | VSS33   |

| 4  | RAMOE[4] | RWE[0]  | TDO   | DSUEN    | SDDQM[2] | N.C.     | SDCS[0] |

| 5  | RWE[1]   | WRITE   | VSS33 | TMS      | N.C.     | SDDQM[3] | SDCAS   |

| 6  | RWE[3]   | RWE[2]  | IOS   | VSS33    | VSS33    | GNT      | A/D[24] |

| 7  | RAMS[0]  | N.C.    | TRST  | SDDQM[0] | VSS33    | VCC33    | A/D[30] |

| 8  | RAMS[3]  | VCC33   | OE    | BRDY     | VCC33    | A/D[21]  | A/D[18] |

| 9  | CB[5]    | PIO[14] | VSS33 | SDRAS    | A/D[22]  | A/D[16]  | A/D[17] |

| 10 | D[9]     | D[0]    | N.C.  | A/D[14]  | VSS33    | PERR     | IRDY    |

|    | Н     | j     | k     | Ι       | m        | n       | р       |

|----|-------|-------|-------|---------|----------|---------|---------|

| 11 | D[20] | A[5]  | A[16] | N.C.    | A/D[12]  | A/D[9]  | A/D[15] |

| 12 | D[24] | A[14] | A[26] | VDD_PLL | AGNT[3]  | A/D[1]  | A/D[8]  |

| 13 | N.C.  | VCC33 | A[21] | N.C.    | N.C.     | VSS33   | A/D[5]  |

| 14 | A[10] | VCC33 | A[27] | LOCK    | SKEW[1]  | A/D[0]  | AGNT[1] |

| 15 | N.C.  | VSS33 | VCC33 | A[24]   | Reserved | BYPASS  | CLK     |

| 16 | A[11] | VSS33 | A[23] | RESET   | LFT      | AREQ[2] | VSS33   |

| 17 | A[19] | A[17] | VSS33 | VCC33   | WDOG     | N.C.    | VSS33   |

| 18 | A[13] | A[18] | A[22] | VSS33   | VSS_PLL  | AREQ[3] | N.C.    |

| 19 | A[15] | A[20] | A[25] | ERROR   | SKEW[0]  | VCC33   | AREQ[1] |

Table 3.

AT697E MCGA349 pinout (suite 2)

|    | r        | t       | u       | v       | w       |

|----|----------|---------|---------|---------|---------|

| 1  | REQ      | VSS18   | VDD18   |         |         |

| 2  | N.C.     | SDCS[1] | VDD18   | VSS18   |         |

| 3  | PCI_RST  | A/D[31] | VSS18   | VDD18   | VDD18   |

| 4  | N.C.     | A/D[29] | VCC33   | VSS18   | VSS18   |

| 5  | N.C.     | N.C.    | A/D[26] | N.C.    | A/D[28] |

| 6  | N.C.     | A/D[27] | IDSEL   | VSS33   | A/D[25] |

| 7  | SYSEN    | VSS33   | VCC33   | C/BE[3] | A/D[23] |

| 8  | VSS33    | VSS33   | FRAME   | A/D[20] | A/D[19] |

| 9  | TRDY     | VCC33   | N.C.    | C/BE[2] | VSS33   |

| 10 | PCI_LOCK | DEVSEL  | STOP    | VCC33   | VCC33   |

| 11 | VSS33    | VCC33   | VSS33   | C/BE[1] | SERR    |

| 12 | N.C.     | A/D[11] | PAR     | VSS33   | A/D[13] |

| 13 | VCC33    | A/D[7]  | A/D[10] | VSS33   | VSS33   |

| 14 | VCC33    | VSS33   | C/BE[0] | A/D[4]  | A/D[6]  |

| 15 | N.C.     | A/D[2]  | VCC33   | N.C.    | A/D[3]  |

| 16 | N.C.     | VCC33   | N.C.    | VDD18   | VSS18   |

| 17 | VCC33    | AGNT[0] | VSS18   | VDD18   | VDD18   |

| 18 | N.C.     | AGNT[2] | VDD18   | VSS18   |         |

| 19 | AREQ[0]  | VSS18   | VDD18   |         |         |

Notes: 1. 'Reserved' pins shall not be driven to any voltage 2. N.C. refers to unconnected pins

#### QFP256 Package

## Table 4. AT697E MQFP256 pinout

| pin<br>number | pin name | pin<br>number | pin name | pin<br>number | pin name |

|---------------|----------|---------------|----------|---------------|----------|

| 1             | VCC33    | 31            | тск      | 61            | PIO1     |

| 2             | PCI_REQ  | 32            | TMS      | 62            | PIO2     |

| 3             | PCI_GNT  | 33            | VSS      | 63            | PIO3     |

| 4             | PCI_CLK  | 34            | TDI      | 64            | PIO4     |

| 5             | PCI_RST  | 35            | TDO      | 65            | PIO5     |

| 6             | SDCS0    | 36            | WRITE    | 66            | PIO6     |

| 7             | VSS      | 37            | READ     | 67            | VCC33    |

| 8             | VDD18    | 38            | ŌĒ       | 68            | PIO7     |

| 9             | SDCS1    | 39            | ĪOS      | 69            | PIO8     |

| 10            | SDWE     | 40            | VCC33    | 70            | PIO9     |

| 11            | SDRAS    | 41            | ROMS0    | 71            | VSS      |

| 12            | VSS      | 42            | ROMS1    | 72            | VDD18    |

| 13            | VSS      | 43            | RWE0     | 73            | PIO10    |

| 14            | SDCAS    | 44            | RWE1     | 74            | PIO11    |

| 15            | VCC33    | 45            | RWE2     | 75            | Reserved |

| 16            | SDDQM0   | 46            | RWE3     | 76            | PIO12    |

| 17            | SDDQM1   | 47            | RAMOE0   | 77            | PIO13    |

| 18            | SDDQM2   | 48            | RAMOE1   | 78            | PIO14    |

| 19            | SDDQM3   | 49            | RAMOE2   | 79            | PIO15    |

| 20            | SDCLK    | 50            | RAMOE3   | 80            | VCC33    |

| 21            | BRDY     | 51            | RAMOE4   | 81            | CB0      |

| 22            | BEXC     | 52            | RAMS0    | 82            | CB1      |

| 23            | VSS      | 53            | VCC33    | 83            | CB2      |

| 24            | VSS      | 54            | RAMS1    | 84            | CB3      |

| 25            | DSUEN    | 55            | RAMS2    | 85            | VCC33    |

| 26            | DSUTX    | 56            | RAMS3    | 86            | CB4      |

| 27            | DSURX    | 57            | VSS      | 87            | CB5      |

| 28            | DSUBRE   | 58            | VDD18    | 88            | CB6      |

| 29            | DSUACT   | 59            | RAMS4    | 89            | CB7      |

| 30            | TRST     | 60            | PIO0     | 90            | D0       |

6

| Table 5. | AT697E I | MQFP256 | pinout ( | (suite) | ) |

|----------|----------|---------|----------|---------|---|

|----------|----------|---------|----------|---------|---|

|               |          | •             | - ()     |               |           |

|---------------|----------|---------------|----------|---------------|-----------|

| pin<br>number | pin name | pin<br>number | pin name | pin<br>number | pin name  |

| 91            | VCC33    | 124           | D25      | 157           | A19       |

| 92            | D1       | 125           | D26      | 158           | A20       |

| 93            | D2       | 126           | D27      | 159           | A21       |

| 94            | D3       | 127           | D28      | 160           | A22       |

| 95            | D4       | 128           | D29      | 161           | VSS       |

| 96            | D5       | 129           | D30      | 162           | VCC33     |

| 97            | D6       | 130           | VCC33    | 163           | A23       |

| 98            | Reserved | 131           | D31      | 164           | A24       |

| 99            | VCC33    | 132           | N.C.     | 165           | A25       |

| 100           | D7       | 133           | A0       | 166           | A26       |

| 101           | D8       | 134           | A1       | 167           | A27       |

| 102           | D9       | 135           | VSS      | 168           | WDOG      |

| 103           | D10      | 136           | VDD18    | 169           | ERROR     |

| 104           | D11      | 137           | A2       | 170           | VCC33     |

| 105           | D12      | 138           | A3       | 171           | RESET     |

| 106           | VCC33    | 139           | A4       | 172           | Reserved  |

| 107           | D13      | 140           | VCC33    | 173           | LOCK      |

| 108           | D14      | 141           | A5       | 174           | SKEW1     |

| 109           | D15      | 142           | A6       | 175           | SKEW0     |

| 110           | D16      | 143           | A7       | 176           | BYPASS    |

| 111           | D17      | 144           | A8       | 177           | VSS_PLL   |

| 112           | VSS      | 145           | A9       | 178           | FLT       |

| 113           | D18      | 146           | A10      | 179           | VDD_PLL   |

| 114           | VCC33    | 147           | VCC33    | 180           | CLK       |

| 115           | D19      | 148           | A11      | 181           | VCC33     |

| 116           | D20      | 149           | A12      | 182           | PCI_AREQ3 |

| 117           | D21      | 150           | A13      | 183           | PCI_AGNT3 |

| 118           | D22      | 151           | A14      | 184           | PCI_AREQ2 |

| 119           | D23      | 152           | A15      | 185           | VSS       |

| 120           | D24      | 153           | A16      | 186           | VDD18     |

| 121           | VSS      | 154           | VCC33    | 187           | PCI_AGNT2 |

| 122           | VDD18    | 155           | A17      | 188           | PCI_AREQ1 |

| 123           | VCC33    | 156           | A18      | 189           | VCC33     |

|               |           | •             | · · ·    |               |          |

|---------------|-----------|---------------|----------|---------------|----------|

| pin<br>number | pin name  | pin<br>number | pin name | pin<br>number | pin name |

| 190           | PCI_AGNT1 | 213           | A/D12    | 236           | A/D19    |

| 191           | PCI_AREQ0 | 214           | A/D13    | 237           | SYSEN    |

| 192           | PCI_AGNT0 | 215           | A/D14    | 238           | A/D20    |

| 193           | A/D0      | 216           | A/D15    | 239           | VCC33    |

| 194           | VCC33     | 217           | VCC33    | 240           | A/D21    |

| 195           | A/D1      | 218           | C/BE1    | 241           | A/D22    |

| 196           | A/D2      | 219           | PAR      | 242           | A/D23    |

| 197           | A/D3      | 220           | SERR     | 243           | IDSEL    |

| 198           | A/D4      | 221           | PERR     | 244           | C/BE3    |

| 199           | VSS       | 222           | VCC33    | 245           | VCC33    |

| 200           | VDD18     | 223           | PCI_LOCK | 246           | A/D24    |

| 201           | VCC33     | 224           | STOP     | 247           | A/D25    |

| 202           | A/D5      | 225           | DEVSEL   | 248           | A/D26    |

| 203           | A/D6      | 226           | TRDY     | 249           | VSS      |

| 204           | A/D7      | 227           | VCC33    | 250           | VDD18    |

| 205           | C/BE0     | 228           | IRDY     | 251           | A/D27    |

| 206           | VSS       | 229           | FRAME    | 252           | VCC33    |

| 207           | VCC33     | 230           | VSS      | 253           | A/D28    |

| 208           | A/D8      | 231           | C/BE2    | 254           | A/D29    |

| 209           | A/D9      | 232           | A/D16    | 255           | A/D30    |

| 210           | A/D10     | 233           | VCC33    | 256           | A/D31    |

| 211           | A/D11     | 234           | A/D17    |               |          |

| 212           | VCC33     | 235           | A/D18    |               |          |

Table 6. AT697E MQFP256 pinout (suite 2)

Notes: 1. 'Reserved' pins shall not be driven to any voltage

2. N.C. refers to unconnected pins

8

# **Pin Description**

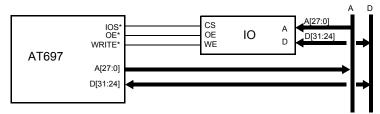

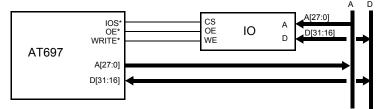

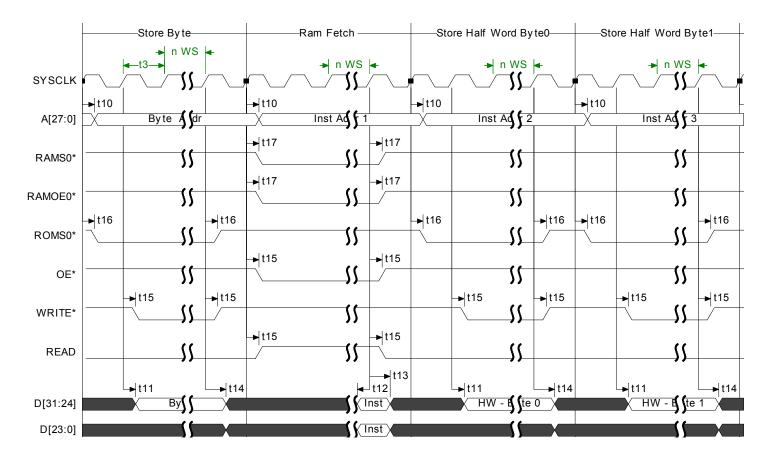

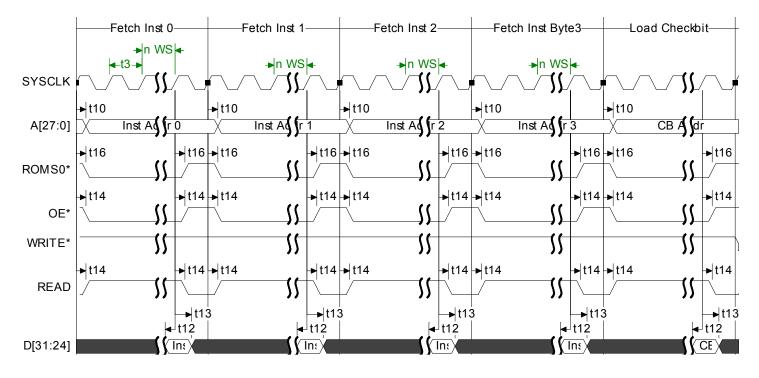

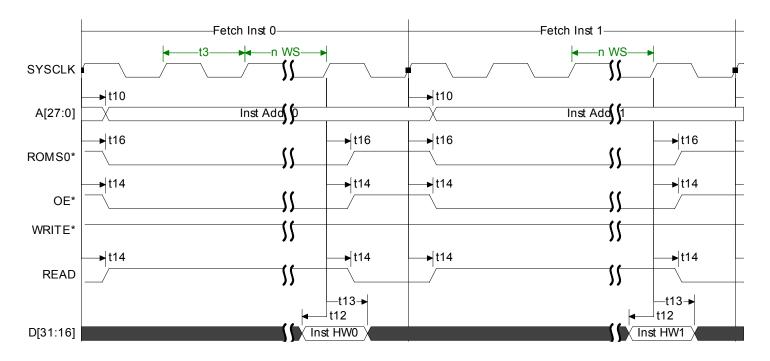

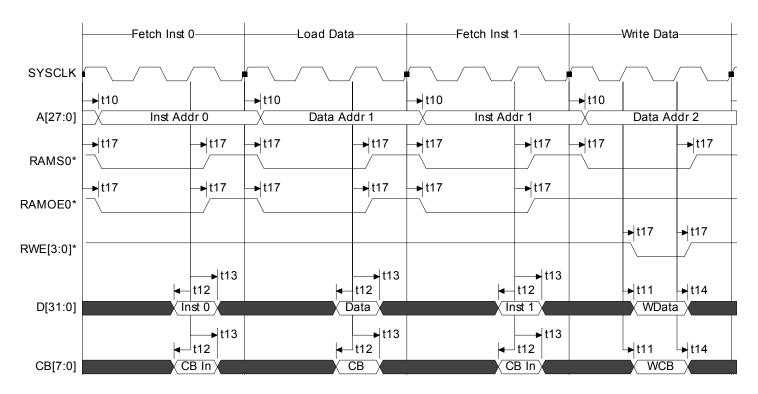

| IU and FPU Signals       | A[27:0] - Address bus (output)                                                                                                                                                                                                                                             |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | A[27:0] bus carries the addresses during accesses to external memory. When access to cache memory is performed, the address of the last external memory access remains driven on the address bus.                                                                          |

|                          | D[31:0] - Data bus (bi-directional)                                                                                                                                                                                                                                        |

|                          | D[31:0] bus carries the data during accesses to memory. The processor automatically configures the bus as output and drive the lines during write cycles. During accesses to 8-bit areas, only D[31:24] are used. During accesses to 16-bit areas, only D[31:16] are used. |

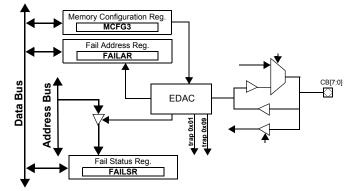

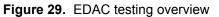

|                          | CB[7:0] - Check bits (bi-directional)                                                                                                                                                                                                                                      |

|                          | CB[6:0] bus carries the EDAC checkbits during memory accesses. CB[7] <sup>(1)</sup> takes the value of tcb[7] in the error control register. Processor only drives CB[7:0] during write cycles to areas programmed to be EDAC protected.                                   |

|                          | Note: 1. CB[7] is implemented to enable programming of flash memories. When only 7 bits are useful for EDAC protection, 8 are needed for programming.                                                                                                                      |

| Memory Interface Signals |                                                                                                                                                                                                                                                                            |

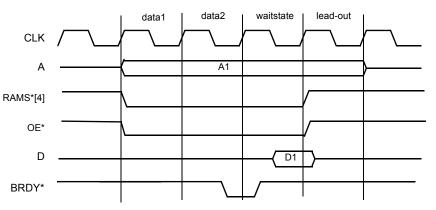

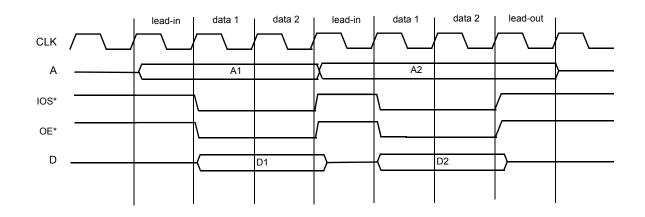

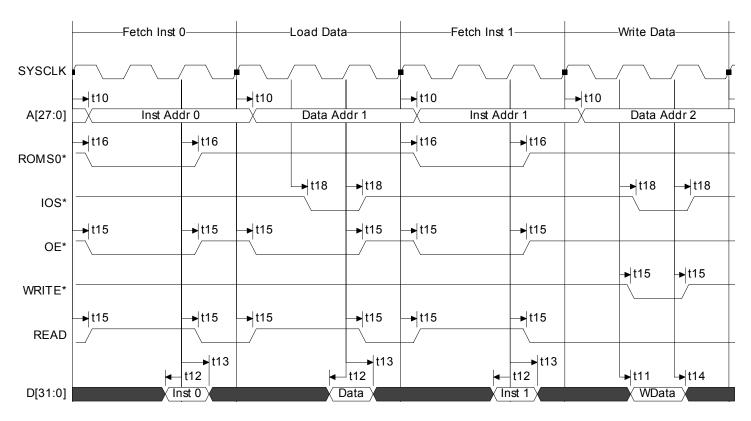

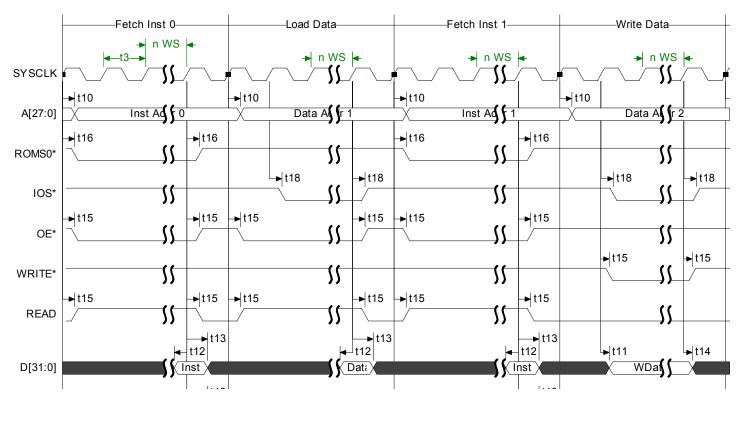

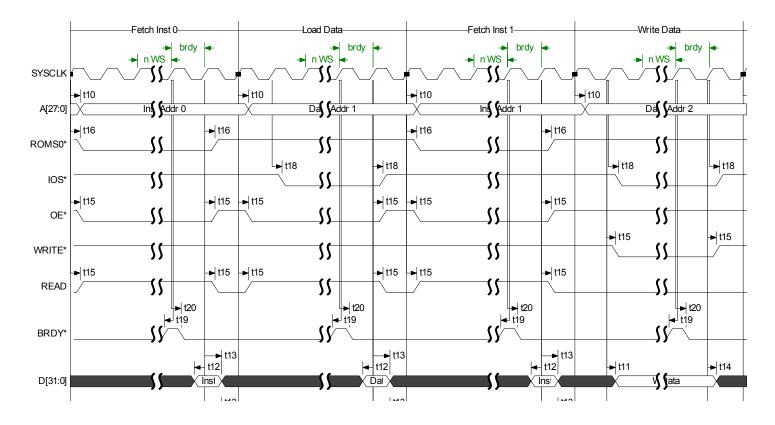

| General management       | OE* - Output enable (output)                                                                                                                                                                                                                                               |

|                          | This active low output is asserted during read cycles on the memory bus.                                                                                                                                                                                                   |

|                          | BRDY* - Bus ready (input)                                                                                                                                                                                                                                                  |

|                          | When driven low, this input indicates to the processor that the current memory access can be terminated on the next rising clock edge. When driven high, this input indicates to the processor that it must wait and not end the current access.                           |

|                          | READ - Read cycle (output)                                                                                                                                                                                                                                                 |

|                          | This active high output is asserted during read cycles on the memory bus.                                                                                                                                                                                                  |

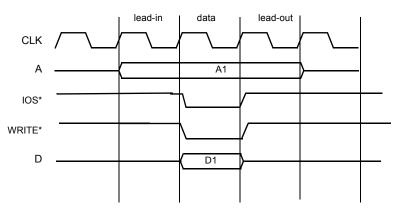

|                          | WRITE* - Write enable (output)                                                                                                                                                                                                                                             |

|                          | This active low output provides a write strobe during write cycles on the memory bus.                                                                                                                                                                                      |

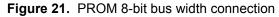

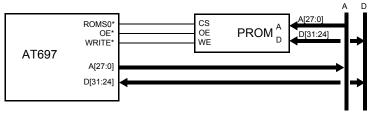

| PROM                     | ROMS*[1:0] - PROM chip-select (output)                                                                                                                                                                                                                                     |

|                          | These active low outputs provide the chip-select signal for the PROM area. ROMS*[0] is asserted when the lower half of the PROM area is accessed (0 - 0x10000000), while ROMS*[1] is asserted for the upper half.                                                          |

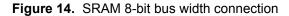

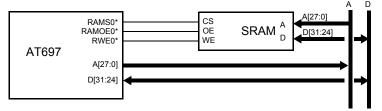

| SRAM                     | RAMOE*[4:0] - RAM output enable (output)                                                                                                                                                                                                                                   |

|                          | These active low signals provide an individual output enable for each RAM bank.                                                                                                                                                                                            |

|                          | RAMS*[4:0] - RAM chip-select (output)                                                                                                                                                                                                                                      |

|                          | These active low outputs provide the chip-select signals for each RAM bank.                                                                                                                                                                                                |

|                          | RWE* [3:0] - RAM write enable (output)                                                                                                                                                                                                                                     |

|                          | These active low outputs provide individual write strobes for each byte. RWEN[0] con-<br>trols D[31:24], RWEN[1] controls D[23:16], etc.                                                                                                                                   |

| mei |

|-----|

|     |

| B   |

| I/O             | IOS* - I/O select (output)                                                                                                                                                              |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | This active low output is the chip-select signal for the memory mapped I/O area.                                                                                                        |

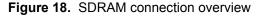

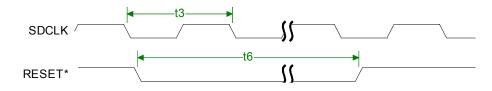

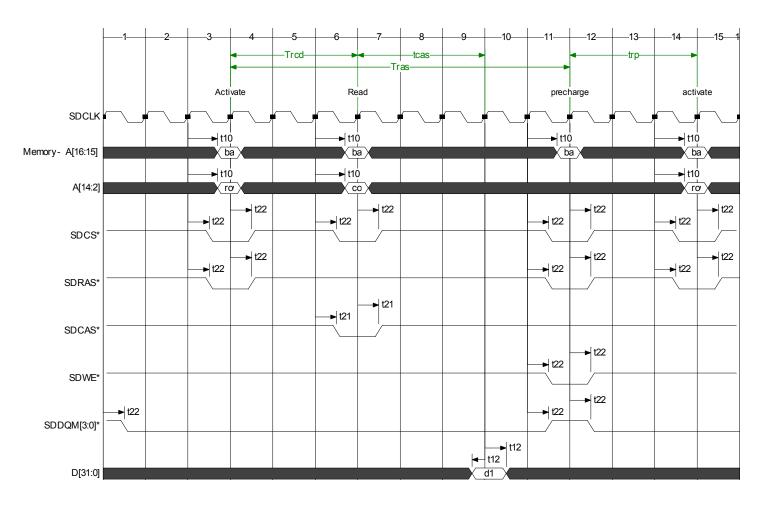

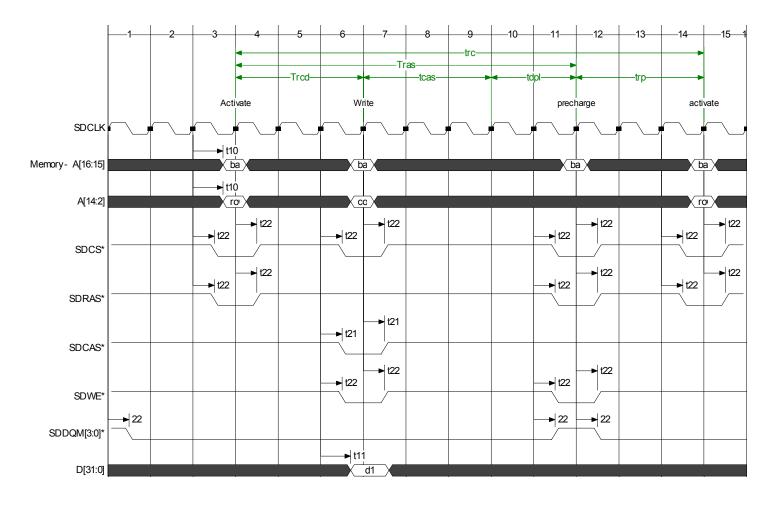

| SDRAM Interface | SDCLK - SDRAM clock (output)                                                                                                                                                            |

|                 | SDRAM clock provides the SDRAM interface clock reference.                                                                                                                               |

|                 | SDCAS* - SDRAM column address strobe (output)                                                                                                                                           |

|                 | This active low signal provides a common CAS for all SDRAM devices.                                                                                                                     |

|                 | SDCS*[1:0] - SDRAM chip select (output)                                                                                                                                                 |

|                 | These active low outputs provide the chip select signals for the two SDRAM banks.                                                                                                       |

|                 | SDDQM[3:0] - SDRAM data mask (output)                                                                                                                                                   |

|                 | These active low outputs provide the DQM signals for both SDRAM banks.                                                                                                                  |

|                 | SDRAS*- SDRAM row address strobe (output)                                                                                                                                               |

|                 | This active low signal provides a common RAS for all SDRAM devices.                                                                                                                     |

|                 | SDWEN - SDRAM write strobe (output)                                                                                                                                                     |

|                 | This active low signal provides a common write strobe for all SDRAM devices.                                                                                                            |

| System Signals  | CLK - Processor clock (input)                                                                                                                                                           |

|                 | The CLK input provides the main processor clock reference.                                                                                                                              |

|                 | RESET* - Processor reset (input)                                                                                                                                                        |

|                 | When asserted, this active low input will reset the processor and all on-chip peripherals.                                                                                              |

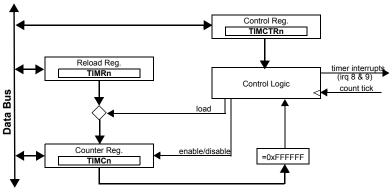

|                 | WDOG* - Watchdog time-out (open-drain output)                                                                                                                                           |

|                 | This active low output is asserted when the watchdog expires.                                                                                                                           |

|                 | BEXC* - Bus exception (input)                                                                                                                                                           |

|                 | This active low input is sampled simultaneously with the data during accesses on the memory bus. If asserted, a memory error will be generated.                                         |

|                 | ERROR* - Processor error (open-drain output)                                                                                                                                            |

|                 | This active low output is asserted when the processor has entered error state and is halted. This happens when traps are disabled and a synchronous (un-maskable) trap occurs.          |

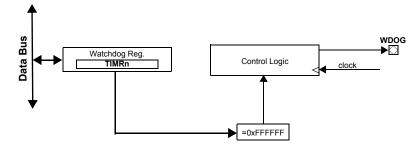

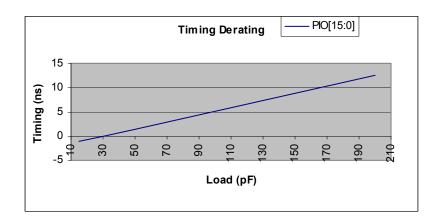

|                 | PIO[15:0] - Parallel I/O port (bi-directional)                                                                                                                                          |

|                 | These bi-directional signals can be used as inputs or outputs to control external devices.                                                                                              |

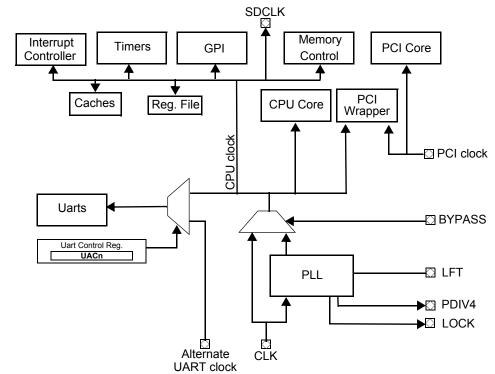

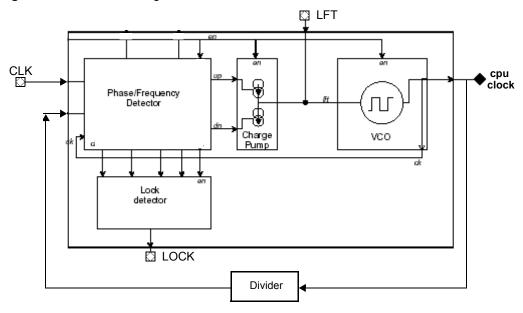

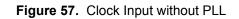

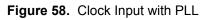

|                 | BYPASS - PLL bypass (input)                                                                                                                                                             |

|                 | When driven to VCC, this active high input set the PLL in bypass mode. The device is then directly clocked by the external clock. When grounded, the device is clocked through the PLL. |

|                 | SKEW[1:0] - Clock tree skew (input)                                                                                                                                                     |

|                 | These input signals configurate the programmable skew on the triplicated clock trees.                                                                                                   |

|                 | LOCK - PLL lock (output)                                                                                                                                                                |

This active high output is asserted when the PLL output (internal node) is locked at the frequency corresponding to four times the input command.

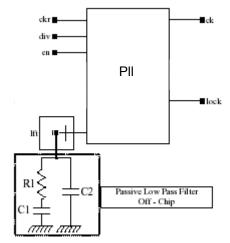

#### LFT - PLL passive low pass filter (input)

This input is used to connect the PLL passive low pass filter.

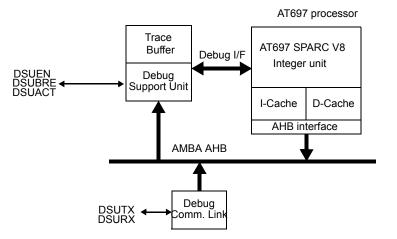

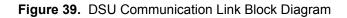

#### DSU Signals DSUACT - DSU active (output)

This active high output is asserted when the processor is in debug mode and controlled by the DSU.

#### DSUBRE - DSU break enable (input)

A low-to-high transition on this active high input will generate break condition and put the processor in debug mode.

#### **DSUEN - DSU enable (input)**

The active high input enables the DSU unit. If de-asserted, the DSU trace buffer will continue to operate but the processor will not enter debug mode.

#### **DSURX - DSU receiver (input)**

This active high input provides the data to the DSU communication link receiver

#### **DSUTX - DSU transmitter (output)**

This active high input provides the output from the DSU communication link transmitter.

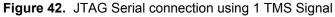

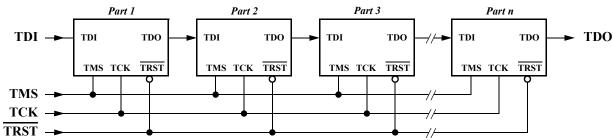

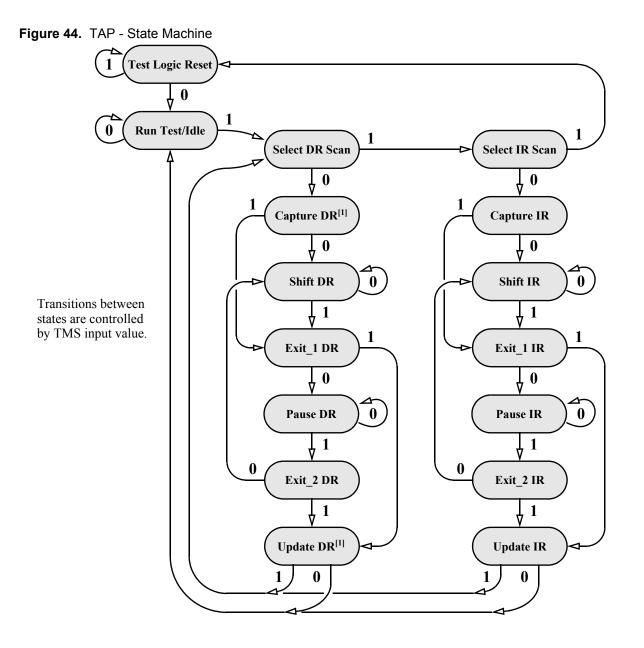

#### TCK - Test Clock (input)

Used to clock serial data into boundary scan latches and control sequence of the test state machine. TCK can be asynchronous with CLK.

#### TMS - Test Mode select (input)

Primary control signal for the state machine. Synchronous with TCK. A sequence of values on TMS adjusts the current state of the TAP.

#### TDI - Test data input (input)

Serial input data to the boundary scan latches. Synchronous with TCK

#### TDO - Test data output (output)

Serial output data from the boundary scan latches. Synchronous with TCK

#### **TRST - Test Reset (input)**

Resets the test state machine. Can be asynchronous with TCK. Shall be grounded for end application.

#### **PCI** Arbiter

**JTAG**

#### AREQ\*[3:0] - PCI bus request (Input)

When asserted, these active low inputs indicate that a PCI agent is requesting the bus.

#### AGNT\*[3:0] - PCI bus grant (Output)

When asserted, these active low outputs indicate that a PCI agent is granted the PCI bus.

#### PCI interface

#### A/D[31:0] - PCI Address Data (bi-directional)

Address and Data are multiplexed on the same PCI pins.

During the address phase, A/D[31::00] contain a physical address (32 bits). For I/O, this is a byte address; for configuration and memory, it is a DWORD address. During data phases, A/D[07::00] contain the least significant byte and A/D[31::24] contain the most significant byte.

#### C/BE[3:0]\* - PCI Bus Command and Byte Enables (bi-directional)

During the address phase of a transaction, C/BE[3::0]\* define the bus command. During the data phase, C/BE[3::0]\* are used as Byte Enables. The Byte Enables are valid for the entire data phase.

#### PAR - Parity (bi-directional)

The number of "1"s on A/D[31::00], C/BE[3::0]\*, and PAR equals an even number

#### FRAME\* - Cycle Frame (bi-directional)

It is driven by the current master to indicate the beginning and duration of an access. FRAME\* is asserted to indicate a bus transaction is beginning. While FRAME\* is asserted, data transfers continue. When FRAME\* is deasserted, the transaction is in the final data phase or has completed.

#### IRDY\* - Initiator Ready (bi-directional)

IRDY\* indicates the initiating agent's ability to complete the current data phase of the transaction. IRDY\* is used in conjunction with TRDY\*. During a write, IRDY\* indicates that valid data is present on A/D[31::00]. During a read, it indicates the master is prepared to accept data.

#### TRDY\* - Target Ready (bi-directional)

TRDY\* indicates the target agent's (selected device's) ability to complete the current data phase of the transaction. TRDY\* is used in conjunction with IRDY\*. During a read, TRDY\* indicates that valid data is present on AD[31::00]. During a write, it indicates the target is prepared to accept data.

#### STOP\* - Stop (bi-directional)

STOP\* indicates the current target is requesting the master to stop the current transaction.

#### PCI\_LOCK\* - Lock (bi-directional)

PCI\_LOCK\* indicates an atomic operation to a bridge that may require multiple transactions to complete.

#### **IDSEL** - Initialization Device Select (input)

Initialization Device Select is used as a chip select during configuration read and write transactions.

#### **DEVSEL\* - Device Select (bi-directional)**

When actively driven, indicates the driving device has decoded its address as the target of the current access. As an input, DEVSEL\* indicates whether any device on the bus has been selected.

#### **REQ\* - PCI bus request (output)**

REQ\* indicates to the arbiter that this agent desires use of the bus. This is a point-topoint signal. Every master has its own REQ\* which must be tri-stated while PCI\_RST\* is

#### **GNT\* - PCI Bus Grant (input)**

asserted.

GNT\* indicates to the agent that access to the bus has been granted. This is a point-topoint signal. Every master has its own GNT\* which must be ignored while PCI\_RST\* is asserted.

#### PCI\_CLK - PCI clock (input)

PCI\_CLK provides timing for all transactions on PCI. All other PCI signals, except PCI\_RST\*, are sampled on the rising edge of PCI\_CLK and all other timing parameters are defined with respect to this edge.

#### PCI\_RST\* - PCI Reset (input)

Reset is used to bring PCI-specific registers, sequencers, and signals to a consistent state.

#### PERR\* - Parity Error (bi-directional)

Parity Error is only for the reporting of data parity errors during all PCI transactions except a Special Cycle. The PERR\* pin is sustained tri-state and must be driven active by the agent receiving data two clocks following the data when a data parity error is detected. The minimum duration of PERR\* is one clock for each data phase that a data parity error is detected.

#### SERR\* - System Error (bi-directional)

System Error is for reporting address parity errors, data parity errors on the special cycle command, or any other system error where the result will be catastrophic. If an agent does not want a non-maskable interrupt (NMI) to be generated, a different reporting mechanism is required.

#### SYSEN\* - PCI Host (input)

This active low input specifies the configuration of the device. At boot-up time, if SYSEN\* is sampled at a low level, the device is configured as the host of the PCI bus. If SYSEN\* is sampled at a high level, the device is configured as a satellite.

# AMEL

# AT697 CPU Core

This section discusses the SPARC core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and handle interrupts.

## SPARC Architecture Overview

The AT697 CPU core is based on the LEON2 architecture.

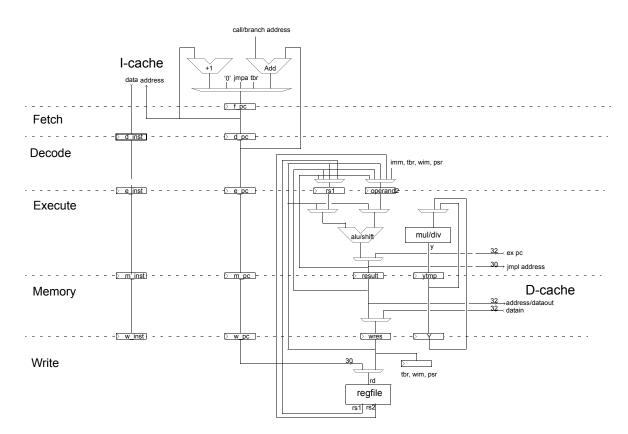

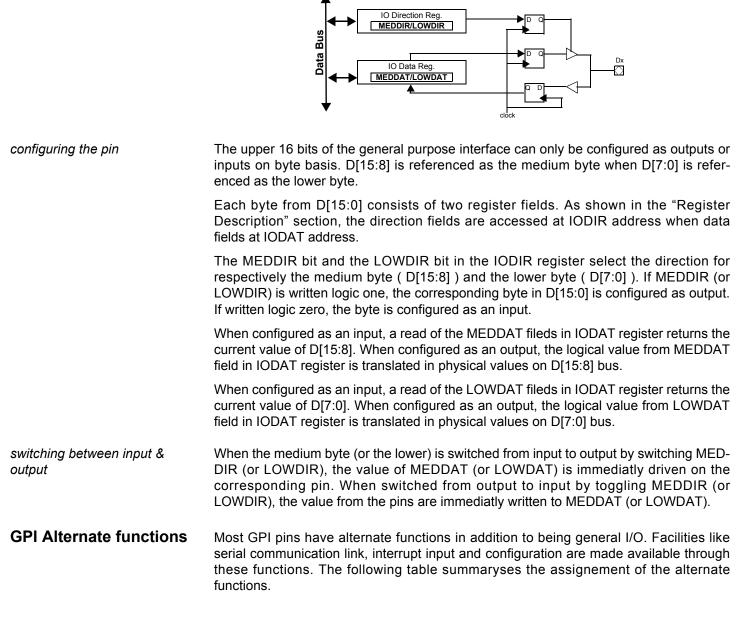

Figure 2. Block diagram of the AT697 Integer Unit architecture

The AT697 integer unit (IU) implements SPARC integer instructions as defined in SPARC Architecture Manual version 8. The IU is designed for highly dependable space and military applications by including fault tolerance features.

To execute instructions at a rate approaching one instruction per clock cycle, the IU employs a five-stage instruction pipeline that permits parallel execution of multiple instructions.

- Instruction Fetch: If the instruction cache is enabled, the instruction is fetched from the instruction cache. Otherwise, the fetch is forwarded to the memory controller. The instruction is valid at the end of this stage and is latched inside the IU.

- Decode: The instruction is decoded and the operands are read. Operands may come from the register file or from internal data bypasses. CALL and Branch target addresses are generated in this stage.

- Execute: ALU, logical, and shift operations are performed. For memory operations and for JMPL/RETT, the address is generated.

- Memory: Data cache is accessed. For cache reads, the data will be valid by the end of this stage, at which point it is aligned as appropriate. Store data read out in the Execute stage is written to the data cache at this time.

|                             | <ul> <li>Write: The result of any ALU, logical, shift, or cache read operations re written back<br/>to the register file.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | All five stages operate in parallel, working on up to five different instructions at a time. A basic 'single-cycle' instruction enters the pipeline and completes in five cycles.                                                                                                                                                                                                                                                                                                                                                              |

|                             | By the time it reaches the write stage, four more instructions have entered and are driv-<br>ing through the pipeline behind it. So, after the first five cycles, a single-cycle instruction<br>exits the pipeline and a single-cycle instruction enters the pipeline on every cycle. Of<br>course, a 'single-cycle' instruction actually takes five cycles to complete, but they are<br>called single cycle because with this type of instruction the processor can complete one<br>instruction per cycle after the initial five-cycle delay. |

|                             | In order to maximize performance and parallelism, the AT697 SPARC implementation uses<br>powerful AMBA bus. Instructions in the program memory are executed with a five level pipelin-<br>ing. While one instruction is being executed, the next instruction is pre-fetched from the program<br>memory. This concept enables instructions to be executed in every clock cycle.                                                                                                                                                                 |

| Program Counters            | Two 32-bit program counters (PC and nPC) are provided. The 32-bit PC contains the address of the instruction currently being executed by the IU. The nPC holds the address of the next instruction to be executed (assuming a trap does not occur).                                                                                                                                                                                                                                                                                            |

|                             | When a trap occurs, the PC address is saved in the local register (I1) while the nPC address is saved in the local register (I2). When returning from trap, I1 value is copied back to PC and I2 value is copied back to nPC.                                                                                                                                                                                                                                                                                                                  |

| ALU - Arithmetic Logic Unit | The high-performance ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate memory address are executed. The implementation of the architecture also provide a powerful multiplier/divider supporting both signed and unsigned multiplication/division.                                                                                                                              |

|                             | Support for high performance 64-bit operation is also provided. The 32-bit Y register con-<br>tains the most significant word of the double-precision product of an integer<br>multiplication, as a result of either an integer multiply instruction, or of a routine that uses<br>the integer multiply step instruction. The Y register also holds the most significant word<br>of the double-precision dividend for an integer divide instruction.                                                                                           |

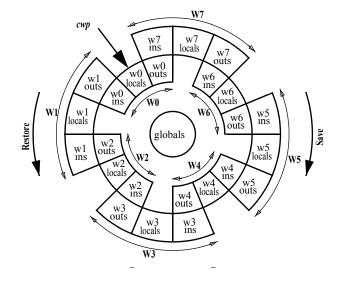

| Register File - Windows     | The fast access register file contains 8 SPARC register windows. Each window consists in a 32-register set. When a program is running, it has access to 32 32-bit processor registers which include 8 global registers plus 24 registers that belong to the current register window.                                                                                                                                                                                                                                                           |

|                             | • The first 8 registers in the window are called the in registers' ( <i>i0-i7</i> ). When a function is called, these registers may contain arguments that can be used.                                                                                                                                                                                                                                                                                                                                                                        |

|                             | <ul> <li>The next 8 are the 'local registers' (<i>I0-I7</i>) which are scratch registers that can be<br/>used for anything while the function executes.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |

|                             | <ul> <li>The last 8 registers are the 'out registers' (<i>o0-o7</i>) which the function uses to pass<br/>arguments to functions that it calls.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                      |

|                             | AT697 register file implementation is based on two dual-port rams. The first dual-port ram corresponds to %rs1 operand of a SPARC instruction while the second corresponds to %rs2 operand. The two dual-port rams contents are always equal.                                                                                                                                                                                                                                                                                                  |

|                             | When one function calls another, the calling function can choose to execute a SAVE instruction. This instruction decrements an internal counter, the current window pointer ( <i>cwp</i> ), shifting the register window downward. The caller's <i>out</i> registers then become                                                                                                                                                                                                                                                               |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

the calling function's *in* registers, and the calling function gets a new set of *local* and *out* registers for its own use. Only the pointer changes because the registers and return address do not need to be stored on a stack. The RETURN instruction acts in the opposite way

Figure 3. Overlapping Windows

The Window Invalid Mask register (WIM) is controlled by supervisor software and is used by hardware to determine whether a window overflow or underflow trap is to be generated by a SAVE, RESTORE, or RETT instruction.

When a SAVE, RESTORE, or RETT instruction is executed, the current value of the CWP is compared against the WIM register. If the SAVE, RESTORE, or RETT instruction would cause the CWP to point to an "invalid" register set, a window\_overflow or window\_underflow trap is caused.

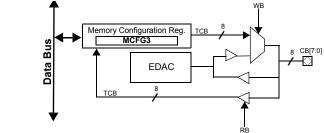

To prevent erroneous operations from SEU errors in the main register file, each word is protected with a 7-bit EDAC checksum. The EDAC checksums are checked when the register is used as operand in an instruction. Any single-bit error is corrected and written back to the register file before the instruction is executed. If an un-correctable error is detected, a register hardware error trap (trap 0x20) is generated.

The protection can be enabled/disabled by programming the 'di' bit from register file protection control register. By setting the 'te' bit, errors can be inserted in the register file to test the protection function. When the 'te' bit is set, the register checksum is combined with the 'tcb' field before being written to the register file.

Due to the presence of the two dual-port rams for register file implementation, the following rules apply to the error injection test process.

- Test checkbits TCB[2:0] is Xored with checkbit[6:4] corresponding to the %rs1 operand.

- Test checkbits TCB[5:3] is Xored with checkbit[6:4] corresponding to the %rs2 operand.

Here is a simple example for the test of a single error in register file %rs1

! 0x32 =

- ! register file test enable

- ! tcb[2:0] = 0x4

- ! tcb[5:3] = 0x1

|                     | <pre>mov 0x32, %l1 mov %l1, %asr16 ! clear %l3 ! =&gt; write 0x0 to %l3 ! forces 0x08 as checkbit for %l3 (error insertion in %rs1 dual-port ram) mov %g0, %l3 ! disable EDAC test mode mov %g0, %asr16 ! access to %l3 as %rs1 operand ! =&gt; single error detection and correction add %l3,%l2,%l1</pre>                                                                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

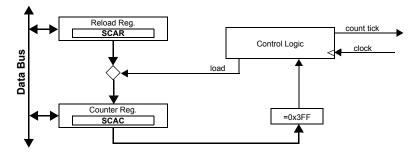

|                     | A correction counter 'cnt' is provided for error management. The 'cnt' field is incre-<br>mented each time a register correction is performed. It saturates at "111".                                                                                                                                                                                                                                                                                                             |

| State Register      | The State Register (PSR) contains information about the result of the most recently executed arithmetic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the Status Register is updated after all ALU operations, as specified in the SPARC architecture specification. This will in many cases remove the need for using the dedicated compare instructions, resulting in faster and more compact code. |

|                     | The state also provides some global information on the current window used, the autho-<br>rized interrupts and peripheral (FPU and coprocessor) presence. A global interrupt<br>management is provided through the processor state register. Trap and Interrupts can<br>be individually enabled/disables from within this register.                                                                                                                                               |

| Instruction Set     | AT697 instructions fall into six functional categories: load/store, arithmetic/logical/ shift, control transfer, read/write control register, floating-point, and miscellaneous. Please refer to SPARC V8 Architecture manual that presents all the implemented instructions.                                                                                                                                                                                                     |

| Floating Point Unit | The FPU is designed to provide execution of single and double-precision floating-point instructions. During the execution of floating-point instructions the processor pipeline is held.                                                                                                                                                                                                                                                                                          |

|                     | The FPU is designed for highly dependable space and military applications, by including fault tolerance features like error detection and correction and triple modular redundancy.                                                                                                                                                                                                                                                                                               |

|                     | The FPU depends upon the IU to access all addresses and control signals for memory access. Floating-point loads and stores are executed in conjunction with the IU, which provides addresses and control signals while the FPU supplies or stores the data. Instruction fetch for integer and floating-point instructions is provided by the IU.                                                                                                                                  |

|                     | The FPU contains 32 32-bit floating-point $f$ registers, which are numbered from f[0] to f[31]. Unlike the windowed $r$ registers, at a given time an instruction has access to any of the 32 $f$ registers. The $f$ registers can be read and written by FPop (FPop1/FPop2 format) instructions, and by load/store single/double floating-point instructions (LDF, LDDF, STF, STDF).                                                                                             |

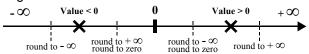

| Rounding Direction  | Rounding direction for floating point results is built according to the ANSI/IEEE Standard 754-1985.                                                                                                                                                                                                                                                                                                                                                                              |

|                     | <ul> <li>In this way,</li> <li>0 = round to nearest</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                    |

- 1 = round to zero

- 2 = round to +infinity

- 3 = round to -infinity

#### Figure 4. Rounding Direction Schematic

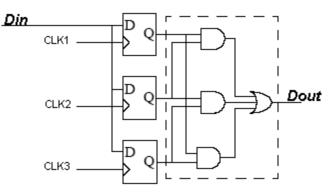

#### **Fault Tolerance** The processor has been especially designed for space application. To prevent erroneous operations from single event transient (SET) and single event upset (SEU) errors, the AT697 processor implements a set of protection features including :

• Full triple modular redundancy (TMR) architecture

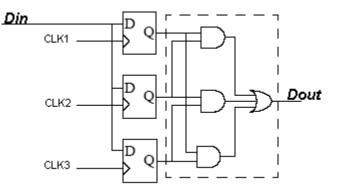

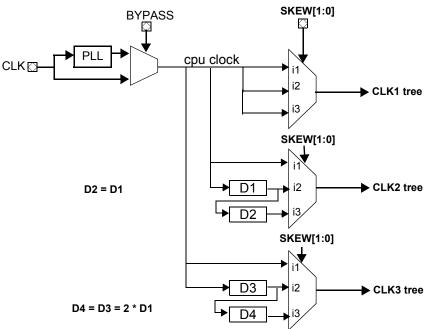

The TMR architecture is based on a fully triplicated clock distribution (CLK1, CLK2 and CLK3). The PCI clock and the CPU clock are built as three-clock trees. The same triplication is applied to the PCI reset and to the CPU reset. See figure 5 for an overview of the TMR architecture.

Programmable skews on the clock trees are also provided to prevent the processor from arbitrary single-event transient errors.

Refer to the 'clock' section for detailed information on TMR implementation and skew implementation.

- EDAC protection on Regfile

- EDAC protection on external memory interface

- Parity protection on instruction and data caches

Figure 5. TMR structure - Clock triplication principle

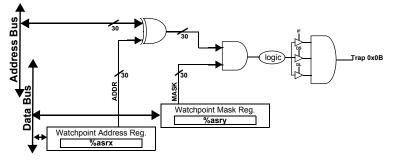

| Watch Points  | The integer unit contains four hardware watch-points allowing generation of a trap on an arbitrary memory address range. Any binary aligned address range can be watched (the two less significant bits are ignored)                                                                                                                                                         |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | <ul> <li>Each watch-point consists in a pair of application-specific registers</li> <li>break address register <ul> <li>The break address defines a reference address for testing.</li> </ul> </li> <li>mask register <ul> <li>The mask indicates which bits of the break address register are to be effectively taken in account during address test</li> </ul> </li> </ul> |

| Configuration | A watchpoint is enabled setting logical one at least one of the three bits IF, DI or DS in the watchpoint address and mask registers. When all three bits are set logical zero, the watchpoint is disabled.                                                                                                                                                                  |

|               | If the instruction fetch bit (IF) from the watchpoint address register is set logical one, any attempt to fetch an instruction from one of the address defined by ADDR and MASK results in a trap generation.                                                                                                                                                                |

|               | If the data store bit (DS) from the watchpoint address register is set logical one, any attempt to store data to one of the address defined by ADDR and MASK results in a trap generation.                                                                                                                                                                                   |

|               | If the data load bit (DL) from the watchpoint mask register is set logical one, any attempt to load a data from one of the address defined by ADDR and MASK results in a trap generation.                                                                                                                                                                                    |

| Operation     | To detect if an address is part of the memory address range that traps, address bit 31 down to bit 2 are Xored with the ADDR field from the watchpoint address register.                                                                                                                                                                                                     |

|               | This operation is based on the following segmentation of an address.                                                                                                                                                                                                                                                                                                         |

#### Table 7. Address Segmentation

| bit num. | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17  | 16   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|------|------|

| field    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Add | ress |    |    |    |    |    |    |   |   |   |   |   |   |   |   | igno | ored |

With such segmentation, it is possible to define trap segment from 4bytes up to 1Gbyte.

The result of the Xor is then Anded with the MASK field of the watchpoint mask register.

If the result is zero, this indicates that address specified is in the watched range. Then, a watchpoint hit error is generated. Trap 0x0B is generated. If result is different from zero, address is out of the watched address range.

Figure 6. Watchpoint Hit Principle

# **Traps and Interrupts**

### **Overview**

The AT697 supports two types of traps:

- synchronous traps

- asynchronous traps also called interrupts.

Synchronous traps are caused by hardware responding to a particular instruction: they occur during the instruction that caused them. Asynchronous traps occur when an external event interrupts the processor. They are not related to any particular instruction and occur between the execution of instructions.

A trap is a vectored transfer of control to the supervisor through a special trap table that contains the first four instructions of each trap handler. The trap base address (TBR) of the table is established by supervisor and the displacement, within the table, is determined by the trap type.

A trap causes the current window pointer to advance to the next register window and the hardware to write the program counters (PC & nPC) into two registers of the new window.

## Synchronous Traps

The AT697 follows the general SPARC trap model. The table below shows the implemented traps and their individual priority.

| Тгар                         | TT (trap type) | Priority | Description                                                                         |

|------------------------------|----------------|----------|-------------------------------------------------------------------------------------|

| reset                        | 0x00           | 1        | Power-on reset                                                                      |

| write error                  | 0x2b           | 2        | Write buffer error                                                                  |

| instruction_access_exception | 0x01           | 3        | Error during instruction fetch<br>Edac uncorrectable error during instruction fetch |

| illegal_instruction          | 0x02           | 5        | UNIMP or other un-implemented instruction                                           |

| privileged_instruction       | 0x03           | 4        | Execution of privileged instruction in user mode                                    |

| fp_disabled                  | 0x04           | 6        | FP instruction while FPU disabled                                                   |

| cp_disabled                  | 0x24           | 6        | co-processor instruction while co-processor disabled                                |

| watchpoint_detected          | 0x0B           | 7        | Instruction or data watchpoint match                                                |

| window_overflow              | 0x05           | 8        | SAVE into invalid window                                                            |

| window_underflow             | 0x06           | 8        | RESTORE into invalid window                                                         |

| register_hadrware_error      | 0x20           | 9        | register file uncorrectable EDAC error                                              |

| mem_address_not_aligned      | 0x07           | 10       | Memory access to un-aligned address                                                 |

| fp_exception                 | 0x08           | 11       | FPU exception                                                                       |

#### Table 8.Trap Overview

| data_access_exception | 0x09       | 13 | Access error during load or store instruction |

|-----------------------|------------|----|-----------------------------------------------|

| tag overflow          | 0x0A       | 14 | Tagged arithmetic overflow                    |

| divide_exception      | 0x2A       | 15 | Divide by zero                                |

| trap_instruction      | 0x80 -0xFF | 16 | Software trap instruction (TA)                |

Traps Description

- reset A reset trap is caused by an external reset request. It causes the processor to begin executing at virtual address 0. After a Reset Trap, no special memory states are defined exept the PSR's 'et' and 's' bits that are initialized respectively '0' and '1'.

- write error An error exception occurred on a data store to memory.

- instruction\_access\_exception A blocking error exception occurred on an instruction access.

- illegal\_instruction An attempt was made to execute an instruction with an unimplemented opcode, or an UNIMP instruction, or an instruction that would result in illegal processor state.

- privileged\_instruction An attempt was made to execute a privileged instruction while supervisor bit (s) in PSR is '0' (not in supervisor mode).

- fp\_disabled An attempt was made to execute an FPU instruction while FPU is not enabled or not present.

- cp\_disabled An attempt was made to execute a co-processor instruction while coprocessor is not enabled or not present.

- watchpoint\_detected An instruction fetch memory address or load/store data memory address matched the contents of a pre-loaded implementation-dependent "watchpoint" register.

- window\_overflow A SAVE instruction attempted to cause the current window pointer (CWP) to point to an invalid window in the WIM.

- window\_underflow A RESTORE or RETT instruction attempted to cause the current window pointer (CWP) to point to an invalid window in the WIM.

- register\_hardware\_error An error exception occurred on a read only register access.

A register file uncorrectable error was detected.

- mem\_address\_not\_aligned A load/store instruction would have generated a memory address that was not properly aligned according to the instruction, or a JMPL or RETT instruction would have generated a non-word-aligned address.

- fp\_exception An FPU instruction generated an IEEE\_754\_exception and its corresponding trap enable mask (TEM) bit was 1, or the FPU instruction was unimplemented, or the FPU instruction did not complete, or there was a sequence or hardware error in the FPU. The type of floating-point exception is encoded in the FSR's *ftt* field.

- data\_access\_exception A blocking error exception occurred on a load/store data access. EDAC uncorrectable error.

- tag\_overflow A tagged arithmetic instruction was executed, and either arithmetic overflow occurred or at least one of the tag bits of the operands was non zero.

- trap\_division\_by\_zero An integer divide instruction attempted to divide by zero.

- trap\_instruction A software instruction (Ticc) was executed and the trap condition evaluated to true.

When multiple synchronous traps occur at the same cycle (i.e hardware errors), the highest priority trap is taken, and lower priority traps are ignored.

## Asynchronous Traps / Interrupts

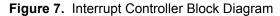

The AT697 handles 11 interrupts. Interrupts can be due to external interrupt requests not directly related to any particular instruction or can be due to exception caused by particular previously executed instruction.

#### Operation

When an interrupt is generated, the corresponding bit is set in the interrupt pending register (ITP). The pending bits are ANDed with the interrupt mask register and then forwarded to the priority selector. The highest interrupt from priority level 1 will be forwarded to the IU - if no unmasked pending interrupt exists on priority level 1, then the highest unmasked interrupt from priority level 0 is forwarded.

When the IU acknowledges the interrupt, the corresponding pending bit will automatically be cleared.

Interrupt can also be forced by setting a bit in the interrupt force register. In this case, the IU acknowledgement will clear the force bit rather than the pending bit.

After reset, the interrupt mask register is set to all zeros while the remaining control registers are undefined.

The following table presents the assignement of the interrupts.

Interrupt List

| Table 9. | Interrupt Overview |

|----------|--------------------|

|----------|--------------------|

| Interrupt | TT (Trap Type) | Source            |

|-----------|----------------|-------------------|

| 15        | 0x1F           | unused            |

| 14        | 0x1E           | PCI               |

| 13        | 0x1D           | unused            |

| 12        | 0x1C           | unused            |

| 11        | 0x1B           | DSU trace buffer  |

| 10        | 0x1A           | unused            |

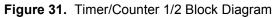

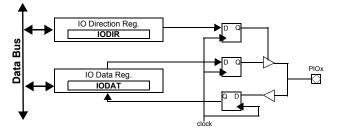

| 9         | 0x19           | Timer 2           |

| 8         | 0x18           | Timer 1           |

| 7         | 0x17           | I/O interrupt [3] |

| Interrupt | TT (Trap Type) | Source             |

|-----------|----------------|--------------------|

| 6         | 0x16           | I/O interrupt [2]  |

| 5         | 0x15           | I/O interrupt [1]  |

| 4         | 0x14           | I/O interrupt [0]  |

| 3         | 0x13           | UART 1             |

| 2         | 0x12           | UART 2             |

| 1         | 0x11           | Internal bus error |

#### I/O interrupts

As an alternate function of the general purpose interface, the AT697 allows to input interrupt from external devices. Up to four external interrupts can be programmed at the same time. The four interrupts are assigned to interrupt 4, 5, 6 and 7.

Each I/O interrupt consists of four fields in the I/O interrupt register (IOIT) : ENx, LEx, PLx and ISELx.

An I/O interrupt is enabled setting logical one the ENx bit in the IOIT register. Setting this bit logical zero disables the interrupt. The ISELx field in the IOIT register defines which port of the general purpose interface should generate I/O interrupt x. The port can be selected from within PIO[15:0] and D[15:0]\*.

Each I/O interrupt can have its trigger mode and its polarity individually configured. When the LEx bit is set logical one, the corresponding I/O interrupt is edge triggered. If the polarity bit (PLx) is driven logical one the interrupt triggers when a rising edge is applied on the pin. If the polarity bit is driven logical zero the interrupt triggers when a falling edge is applied on the pin.

When the LEx bit is set logical zero, the corresponding I/O interrupt is level sensitive. If the polarity bit (PLx) is driven logical one the interrupt triggers when a high level is applied on the pin. If the polarity bit is driven logical zero the interrupt triggers when a low level is applied on the pin.

The following table summarizes the I/O interrupt configurations.

| LEx | PLx | Trigger      |

|-----|-----|--------------|

| 0   | 0   | low level    |

| 0   | 1   | high level   |

| 1   | 0   | falling edge |

| 1   | 1   | rising edge  |

Table 10.

I/O Interrupt Configuration

#### Interrupt Priority

The 15 interrupts handled by the AT697 are prioritised, with interrupt 15 (TT = 0x1F) having the highest priority and interrupt 1 (TT = 0x11) the lowest.

It is possible to change the priority level of an interrupt using the two priority levels from the interrupt mask and priority register (ITMP). Each interrupt can be assigned to one of two levels as programmed in the Interrupt mask and priority register. Level 1 has higher priority than level 0. Within each level the interrupts are prioritised.

# **Cache Memories**

## Overview

The AT697 processor implements a Harvard architecture with separate instruction and data buses, connected to two independent cache controllers. In order to improve the speed performance of the cpu core, multi-set-caches are used for both instruction and data caches.

The cache replacement policy used for both instruction and data caches is based on the LRU algorithm. The least recently used (LRU) set of the cache is replaced when new data need to be stored in cache.

Cache mappingMost of the main memory areas can be cached. The cacheable areas are the PROM<br/>and RAM areas. The following table presents the caching capabilities of the processor.

Table 11. Cache Capability List

| Address Range           | Area     | Cache status  |

|-------------------------|----------|---------------|

| 0x00000000 - 0x1FFFFFFF | PROM     | Cached        |

| 0x20000000 - 0x3FFFFFFF | I/O      | Non-cacheable |

| 0x40000000 -0x7FFFFFFF  | RAM      | Cached        |

| 0x80000000 -0xFFFFFFFF  | Internal | Non-cacheable |

Operation

During normal operation, the processor accesses instructions and data using ASI 0x8 - 0xB as defined in the SPARC standard.

Using the LDA/STA instructions, alternative address spaces as caches can be accessed. ASI[3:0] are used for the mapping when ASI[7:4] have no influence on operation.

- Access with ASI 0 3 will force a cache miss, update the cache if the data was

previously cached or allocate a new line if the data was not in the cache and the

address refers to a cacheable location.

- Access to ASI 4 and 7 will force a cache miss and update the cache if the data was previously cached.

The following table shows the ASI implementation on the AT697.

| ASI                | Usage                                       |  |

|--------------------|---------------------------------------------|--|

| 0x0, 0x1, 0x2, 0x3 | Forced cache miss (replace if cacheable)    |  |

| 0x4, 0x7           | Forced cache miss (update on hit)           |  |

| 0x5                | Flush instruction cache                     |  |

| 0x6                | Flush data cache                            |  |

| 0x8, 0x9, 0xA, 0xB | Normal cached access (replace if cacheable) |  |

| 0xC                | Instruction cache tags                      |  |

| 0xD                | Instruction cache data                      |  |

| 0xE                | Data cache tags                             |  |

| 0xF                | Data cache data                             |  |

#### Table 12. ASI Usage

Note: Please refer to the SPARC v8 specification for detailed information on ASI usage.

#### Instruction Cache Overview The AT697 instruction cache is a multi-set cache of 32 kbyte divided in 4 memory sets. Multi-set-cache use improves speed performance of the core. The instruction cache is divided into cache lines with 32 bytes of data. Each line has a cache tag associated with it consisting of a tag field and one valid bit per 4-byte sub-block. Cache Control The instruction cache operations are controled with the cache control register (CCR). Operation On an instruction cache miss to a cachable location, the instruction is fetched and the corresponding tag and data line updated. The instruction cache always works in one of three modes: disabled. • enabled or frozen. The instruction cache current state is reported in the instruction cache state field (ICS) of the cache controler register (CCR). Disabled mode If disabled, no cache operation is performed and load and store requests are passed directly to the memory controller. Enabled mode If enabled, the cache operates as described above. In the frozen state, the cache is accessed and kept in synchronisation with the main memory as if it was enabled, but no new lines are allocated on read misses. Freeze mode If the freeze on interrupt bit (IF) bit is set logical one on the cache control register (CCR), the instruction cache is frozen when an asynchronous interrupt is taken. This can be beneficial in real-time system to allow a more accurate calculation of worst-case execution time for a code segment. The execution of the interrupt handler will not evict any cache lines and when control is returned to the interrupted task, the cache state is identical to what it was before the interrupt.

| IIIEL |

|-------|

|       |

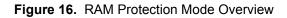

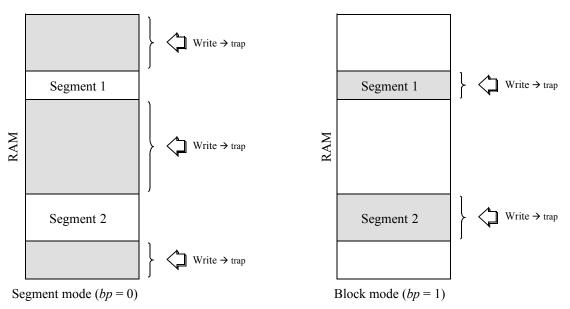

| R     |